# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 120                                                                    |

| Program Memory Size        | 4MB (4M × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 192K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                          |

| Data Converters            | A/D 40x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 208-BGA                                                                |

| Supplier Device Package    | 208-BGA (17x17)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5644af0mmg2 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1.3** Device comparison

Table 1 summarizes the MPC5644A and compares it to the MPC5634M.

Table 1. MPC5644A, MPC5634M and MPC5642A comparison

| Feature                      | MPC5644A                   | MPC5634M                        | MPC5642A                   |  |  |  |  |

|------------------------------|----------------------------|---------------------------------|----------------------------|--|--|--|--|

| Process                      |                            | 90 nm                           |                            |  |  |  |  |

| Core                         | e200z4                     | e200z4                          |                            |  |  |  |  |

| SIMD                         |                            | Yes                             |                            |  |  |  |  |

| VLE                          |                            | Yes                             |                            |  |  |  |  |

| Cache                        | 8 KB instruction           | No                              | 8 KB instruction           |  |  |  |  |

| Non-Maskable Interrupt (NMI) |                            | NMI & Critical Interrupt        |                            |  |  |  |  |

| MMU                          | 24 entry                   | 16 entry                        | 24 entry                   |  |  |  |  |

| MPU                          | 16 entry                   | No                              | 16 entry                   |  |  |  |  |

| Crossbar switch              | 5 × 4                      | $3 \times 4$                    | 4 × 4                      |  |  |  |  |

| Core performance             | 0–150 MHz                  | 0–80 MHz                        | 0–150 MHz                  |  |  |  |  |

| Windowing software watchdog  |                            | Yes                             |                            |  |  |  |  |

| Core Nexus                   | Class 3+                   | Class 2+                        | Class 3+                   |  |  |  |  |

| SRAM                         | 192 KB                     | 94 KB                           | 128 KB                     |  |  |  |  |

| Flash                        | 4 MB                       | 1.5 MB                          | 2 MB                       |  |  |  |  |

| Flash fetch accelerator      | 4 × 256-bit 4 × 128-bit    |                                 |                            |  |  |  |  |

| External bus                 | 16-bit (incl 32-bit muxed) | 16-bit (incl 32-bit muxed) None |                            |  |  |  |  |

| Calibration bus              | 16-bit (incl 32-bit muxed) | 16-bit                          | 16-bit (incl 32-bit muxed) |  |  |  |  |

| DMA                          | 64 ch.                     | 32 ch.                          | 64 ch.                     |  |  |  |  |

| DMA Nexus                    |                            | None                            |                            |  |  |  |  |

| Serial                       | 3                          | 2                               | 3                          |  |  |  |  |

| eSCI_A                       |                            | Yes (MSC Uplink)                |                            |  |  |  |  |

| eSCI_B                       |                            | Yes (MSC Uplink)                |                            |  |  |  |  |

| eSCI_C                       | Yes                        | No                              | Yes                        |  |  |  |  |

| CAN                          | 3                          | 2                               | 3                          |  |  |  |  |

| CAN_A                        |                            | 64 buf                          | •                          |  |  |  |  |

| CAN_B                        | 64 buf                     | No                              | 64 buf                     |  |  |  |  |

| CAN_C                        | 64 buf                     | 32 buf                          | 64 buf                     |  |  |  |  |

| SPI                          | 3                          | 2                               | 3                          |  |  |  |  |

The eTPU2 includes these distinctive features:

- 32 channels; each channel associated with one input and one output signal

- Enhanced input digital filters on the input pins for improved noise immunity

- Identical, orthogonal channels: each channel can perform any time function. Each time function can be assigned to more than one channel at a given time, so each signal can have any functionality.

- Each channel has an event mechanism which supports single and double action functionality in various combinations. It includes two 24-bit capture registers, two 24-bit match registers, 24-bit greater-equal and equal-only comparators.

- Input and output signal states visible from the host

- 2 independent 24-bit time bases for channel synchronization:

- First time base clocked by system clock with programmable prescale division from 2 to 512 (in steps of 2), or by output of second time base prescaler

- Second time base counter can work as a continuous angle counter, enabling angle based applications to match angle instead of time

- Both time bases can be exported to the eMIOS timer module

- Both time bases visible from the host

- Event-triggered microengine:

- Fixed-length instruction execution in two-system-clock microcycle

- 14 KB of code memory (SCM)

- 3 KB of parameter (data) RAM (SPRAM)

- Parallel execution of data memory, ALU, channel control and flow control sub-instructions in selected combinations

- 32-bit microengine registers and 24-bit wide ALU, with 1 microcycle addition and subtraction, absolute value, bitwise logical operations on 24-bit, 16-bit, or byte operands, single-bit manipulation, shift operations, sign extension and conditional execution

- Additional 24-bit Multiply/MAC/Divide unit which supports all signed/unsigned Multiply/MAC combinations, and unsigned 24-bit divide. The MAC/Divide unit works in parallel with the regular microcode commands.

- Resource sharing features support channel use of common channel registers, memory and microengine time:

- Hardware scheduler works as a "task management" unit, dispatching event service routines by predefined, host-configured priority

- Automatic channel context switch when a "task switch" occurs, that is, one function thread ends and another begins to service a request from other channel: channel-specific registers, flags and parameter base address are automatically loaded for the next serviced channel

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of four semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to two parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test (MISC multiple input signature calculator), runs concurrently

with eTPU2 normal operation

# 1.4.12 Reaction module

The reaction module provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The reaction module has the following features:

- Six reaction channels

- Each channel output is a bus of three signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions

# 1.4.13 eQADC

The enhanced queued analog to digital converter (eQADC) block provides accurate and fast conversions for a wide range of applications. The eQADC provides a parallel interface to two on-chip analog to digital converters (ADC), and a single master to single slave serial interface to an off-chip external device. Both on-chip ADCs have access to all the analog channels.

The eQADC prioritizes and transfers commands from six command conversion command 'queues' to the on-chip ADCs or to the external device. The block can also receive data from the on-chip ADCs or from an off-chip external device into the six result queues, in parallel, independently of the command queues. The six command queues are prioritized with Queue\_0 having the highest priority and Queue\_5 the lowest. Queue\_0 also has the added ability to bypass all buffering and queuing and abort a currently running conversion on either ADC and start a Queue\_0 conversion. This means that Queue\_0 will always have a deterministic time from trigger to start of conversion, irrespective of what tasks the ADCs were performing when the trigger occurred. The eQADC supports software and external hardware triggers from other blocks to initiate transfers of commands from the queues to the on-chip ADCs or to the external device. It also monitors the fullness of command queues and result queues, and accordingly generates DMA or interrupt requests to control data movement between the queues and the system memory, which is external to the eQADC.

The ADCs also support features designed to allow the direct connection of high impedance acoustic sensors that might be used in a system for detecting engine knock. These features include differential inputs; integrated variable gain amplifiers for increasing the dynamic range; programmable pull-up and pull-down resistors for biasing and sensor diagnostics.

The eQADC also integrates a programmable decimation filter capable of taking in ADC conversion results at a high rate, passing them through a hardware low pass filter, then down-sampling the output of the filter and feeding the lower sample rate results to the result FIFOs. This allows the ADCs to sample the sensor at a rate high enough to avoid aliasing of out-of-band noise; while providing a reduced sample rate output to minimize the amount DSP processing bandwidth required to fully process the digitized waveform.

The eQADC provides the following features:

- Dual on-chip ADCs

- 2 × 12-bit ADC resolution

- Programmable resolution for increased conversion speed (12-bit, 10-bit, 8-bit)

- 12-bit conversion time: 938 ns (1 M sample/sec)

- 10-bit conversion time: 813 ns (1.2 M sample/second)

- 8-bit conversion time: 688 ns (1.4 M sample/second)

- Up to 10-bit accuracy at 500 KSample/s and 8-bit accuracy at 1 MSample/s

- Differential conversions

- Single-ended signal range from 0 to 5 V

- Variable gain amplifiers on differential inputs  $(\times 1, \times 2, \times 4)$

- Sample times of 2 (default), 8, 64 or 128 ADC clock cycles

### Table 3. MPC5644A signal properties (continued)

|                                                              |                                                                                                          | Р                        | PCR                                  |                  | I/O                  | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup> | Sta          | Package pin #        |     |     |      |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------|----------------------|-------------------------------------------------|--------------|----------------------|-----|-----|------|

| Name                                                         | Function <sup>1</sup>                                                                                    | A<br>G <sup>2</sup>      | PA<br>Field <sup>3</sup>             | PCR <sup>4</sup> | Туре                 |                                                 | During Reset | After<br>Reset       | 176 | 208 | 324  |

| BOOTCFG[1]<br>IRQ[3]<br>ETRIG3<br>GPIO[212]                  | Boot Config. Input<br>External Interrupt Request<br>eQADC Trigger Input<br>GPIO                          | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 212              | <br> <br> /0         | VDDEH6<br>Slow                                  | — / Down     | BOOTCFG[1] /<br>Down | 85  | M15 | U21  |

| WKPCFG<br>NMI<br>DSPI_B_SOUT<br>GPIO[213]                    | Weak Pull Config. Input<br>Non-Maskable Interrupt<br>DSPI D data output<br>GPIO                          | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 213              | <br> <br> /0         | VDDEH6<br>Medium                                | — / Up       | WKPCFG / Up          | 86  | L15 | AA20 |

|                                                              |                                                                                                          |                          |                                      | Ext              | ernal B              | us Interface                                    |              |                      |     |     | •    |

| CS[0]<br>ADDR[8]<br>GPIO[0]                                  | External chip selects<br>External address bus<br>GPIO                                                    | P<br>A1<br>G             | 01<br>10<br>00                       | 0                | 0<br>I/O<br>I/O      | VDDE2<br>Fast                                   | — / Up       | — / Up               | _   | _   | G1   |

| CS[1]<br>ADDR9<br>GPIO[1]                                    | External chip selects<br>External address bus<br>GPIO                                                    | P<br>A1<br>G             | 01<br>10<br>00                       | 1                | 0<br>I/O<br>I/O      | VDDE2<br>Fast                                   | — / Up       | — / Up               | -   | -   | H1   |

| CS[2]<br>ADDR10<br>WE[2]/BE[2]<br>CAL_WE[2]/BE[2]<br>GPI0[2] | External chip selects<br>External address bus<br>Write/byte enable<br>Cal. bus write/byte enable<br>GPIO | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 2                | 0<br>I/O<br>0<br>I/O | VDDE2<br>Fast                                   | — / Up       | — / Up               | -   |     | H2   |

| CS[3]<br>ADDR11<br>WE[3]/BE[3]<br>CAL_WE[3]/BE[3]<br>GPI0[3] | External chip selects<br>External address bus<br>Write/byte enable<br>Cal bus write/byte enable<br>GPIO  | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 3                | 0<br>I/O<br>0<br>I/O | VDDE2<br>Fast                                   | — / Up       | — / Up               | -   | _   | H4   |

| ADDR12<br>GPIO[8]                                            | External address bus<br>GPIO                                                                             | P<br>G                   | 01<br>00                             | 8                | I/O<br>I/O           | VDDE3<br>Fast                                   | — / Up       | — / Up               | —   | —   | N2   |

| ADDR13<br>WE[2]<br>GPIO[9]                                   | External address bus<br>Write/byte enable<br>GPIO                                                        | P<br>A2<br>G             | 001<br>100<br>000                    | 9                | I/O<br>O<br>I/O      | VDDE3<br>Fast                                   | — / Up       | — / Up               | _   | —   | N1   |

| ADDR14<br>WE[3]<br>GPIO[10]                                  | External address bus<br>Write/byte enables<br>GPIO                                                       | P<br>A2<br>G             | 001<br>100<br>000                    | 10               | I/O<br>O<br>I/O      | VDDE3<br>Fast                                   | — / Up       | — / Up               | _   | _   | P1   |

| ADDR15<br>GPIO[11]                                           | External address bus<br>GPIO                                                                             | P<br>G                   | 01<br>00                             | 11               | I/O<br>I/O           | VDDE3<br>Fast                                   | — / Up       | — / Up               | —   | —   | P2   |

| Symbo               | Symbol |   | Parameter                                               | Conditions                                | Value | Unit |

|---------------------|--------|---|---------------------------------------------------------|-------------------------------------------|-------|------|

| $R_{\thetaJA}$      | CC     | D | Junction-to-Ambient, Natural Convection <sup>2,3</sup>  | One layer board - 1s                      | 39    | °C/W |

| $R_{\thetaJA}$      | CC     | D | Junction-to-Ambient, Natural Convection <sup>2,4</sup>  | Four layer board - 2s2p                   | 24    | °C/W |

| R <sub>θJMA</sub>   | CC     | D | Junction-to-Moving-Air, Ambient <sup>2,4</sup>          | at 200 ft./min., one layer<br>board       | 31    | °C/W |

| R <sub>θJMA</sub>   | CC     | D | Junction-to-Moving-Air, Ambient <sup>2,4</sup>          | at 200 ft./min., four layer<br>board 2s2p | 20    | °C/W |

| $R_{\theta JB}$     | CC     | D | Junction-to-board <sup>5</sup>                          | Four layer board - 2s2p                   | 13    | °C/W |

| $R_{	ext{	heta}JC}$ | CC     | D | Junction-to-case <sup>6</sup>                           |                                           | 6     | °C/W |

| $\Psi_{JT}$         | CC     | D | Junction-to-package top natural convection <sup>7</sup> |                                           | 2     | °C/W |

Table 10. Thermal characteristics for 208-pin MAPBGA<sup>1</sup>

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- <sup>3</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- <sup>4</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>5</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>6</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

- <sup>7</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

| Symbo               | Symbol C |   | Parameter                                                   | Conditions                                | Value | Unit |

|---------------------|----------|---|-------------------------------------------------------------|-------------------------------------------|-------|------|

| $R_{\thetaJA}$      | CC       | D | Junction-to-Ambient, Natural Convection <sup>2</sup>        | Single layer board - 1s                   | 29    | °C/W |

| $R_{\theta JA}$     | СС       | D | Junction-to-Ambient, Natural Convection <sup>2</sup>        | Four layer board - 2s2p                   | 19    | °C/W |

| R <sub>θJMA</sub>   | CC       | D | Junction-to-Moving-Air, Ambient <sup>2</sup>                | at 200 ft./min., single layer<br>board    | 23    | °C/W |

| R <sub>0JMA</sub>   | CC       | D | Junction-to-Moving-Air, Ambient <sup>2</sup>                | at 200 ft./min., four layer<br>board 2s2p | 16    | °C/W |

| R <sub>0JB</sub>    | CC       | D | Junction-to-Board <sup>3</sup>                              |                                           | 10    | °C/W |

| R <sub>0JCtop</sub> | CC       | D | Junction-to-Case <sup>4</sup>                               |                                           | 7     | °C/W |

| Ψ <sub>JT</sub>     | CC       | D | Junction-to-Package Top, Natural<br>Convection <sup>5</sup> |                                           | 2     | °C/W |

### Table 11. Thermal characteristics for 324-pin TEPBGA<sup>1</sup>

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>3</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>4</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer. <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 3.3.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>I</sub>, can be obtained from the equation:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D}) \qquad \qquad Eqn. 1$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal resistance values used are based on the JEDEC JESD51 series of standards to provide consistent values for estimations and comparisons. The difference between the values determined for the single-layer (1s) board compared to a four-layer board that has two signal layers, a power and a ground plane (2s2p), demonstrate that the effective thermal resistance is not a constant. The thermal resistance depends on the:

- Construction of the application board (number of planes)

- Effective size of the board which cools the component

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

As a general rule, the value obtained on a single-layer board is within the normal range for the tightly packed printed circuit board. The value obtained on a board with the internal planes is usually within the normal range if the application board has:

- One oz. (35 micron nominal thickness) internal planes

- Components are well separated

- Overall power dissipation on the board is less than 0.02 W/cm<sup>2</sup>

The thermal performance of any component depends on the power dissipation of the surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} * P_{D}) \qquad \qquad Eqn. 2$$

where:

$T_B$  = board temperature for the package perimeter (<sup>o</sup>C)

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W) per JESD51-8S

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air does not factor into the calculation, an acceptable value for the junction temperature is predictable. Ensure the application board is similar to the thermal test condition, with the component soldered to a board with internal planes.

| ID | Nam       | Name |   | Parameter                                                                                                               | Min                    | Тур       | Мах                | Unit       | Notes                 |

|----|-----------|------|---|-------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|--------------------|------------|-----------------------|

| 1  | VBG       | СС   | С | Nominal bandgap voltage reference                                                                                       | _                      | 1.219     | _                  | V          |                       |

| 1a | _         | СС   | Ρ | Untrimmed bandgap<br>reference voltage                                                                                  | VBG - 7%               | VBG       | Vbg + 6%           | V          |                       |

| 1b | _         | CC   | Ρ | Trimmed bandgap<br>reference voltage (5 V,<br>27 °C)                                                                    | VBG<br>-10mV           | VBG       | VBG +<br>10mV      | V          |                       |

| 1c | _         | СС   | С | Bandgap reference<br>temperature variation                                                                              | _                      | 100       | —                  | ppm<br>/°C |                       |

| 1d | _         | СС   | С | Bandgap reference supply voltage variation                                                                              |                        | 3000      | _                  | ppm<br>/V  |                       |

| 2  | Vdd       | СС   | С | Nominal V <sub>DD</sub> core supply<br>internal regulator target DC<br>output voltage <sup>1</sup>                      | _                      | 1.28      | _                  | V          |                       |

| 2a | _         | CC   | Ρ | Nominal V <sub>DD</sub> core supply<br>internal regulator target DC<br>output voltage variation at<br>power-on reset    | Vdd - 6%               | Vdd       | Vdd + 10%          | V          |                       |

| 2b | _         | CC   | Ρ | Nominal V <sub>DD</sub> core supply<br>internal regulator target DC<br>output voltage variation<br>after power-on reset | Vdd - 10% <sup>2</sup> | Vdd       | Vdd + 3%           | V          |                       |

| 2c | _         | CC   | С | Trimming step Vdd                                                                                                       | —                      | 20        | _                  | mV         |                       |

| 2d | lvrcctl   | СС   | С | Voltage regulator controller<br>for core supply maximum<br>DC output current                                            | 20                     | _         | _                  | mA         |                       |

| 3  | Lvi1p2    | СС   | С | Nominal LVI for rising core supply <sup>3</sup>                                                                         | _                      | 1.160     | _                  | V          |                       |

| 3а | _         | СС   | С | Variation of LVI for rising<br>core supply at power-on<br>reset                                                         | 1.120                  | 1.200     | 1.280              | V          | See note <sup>4</sup> |

| 3b | _         | СС   | С | Variation of LVI for rising<br>core supply after power-on<br>reset                                                      | Lvi1p2 -<br>3%         | Lvi1p2    | Lvi1p2 +<br>3%     | V          | See note 4            |

| 3c | _         | СС   | С | Trimming step LVI core<br>supply                                                                                        | —                      | 20        | —                  | mV         |                       |

| 3d | Lvi1p2_h  | СС   | С | LVI core supply hysteresis                                                                                              |                        | 40        |                    | mV         |                       |

| 4  | Por1.2V_r | CC   | С | POR 1.2 V rising                                                                                                        | —                      | 0.709     | —                  | V          |                       |

| 4a |           | СС   | С | POR 1.2 V rising variation                                                                                              | Por1.2V_r-<br>35%      | Por1.2V_r | Por1.2V_r<br>+ 35% | V          |                       |

| 4b | Por1.2V_f | СС   | С | POR 1.2 V falling                                                                                                       | —                      | 0.638     | _                  | V          |                       |

| 4c | _         | СС   | С | POR 1.2 V falling variation                                                                                             | Por1.2V_f-<br>35%      | Por1.2V_f | Por1.2V_f+<br>35%  | V          |                       |

### Table 15. PMC Electrical Characteristics

| Symbol                                     |    | с | _                                                   |                                                           |     | Value |                        |      |

|--------------------------------------------|----|---|-----------------------------------------------------|-----------------------------------------------------------|-----|-------|------------------------|------|

| Symbol                                     |    |   | Parameter                                           | Conditions                                                | min | typ   | max                    | Unit |

| IDDSTBY                                    | СС | Т | Operating current<br>0.95-1.2 V                     | V <sub>STBY</sub> at<br>55 °C                             | —   | 35    | 100                    | μΑ   |

|                                            |    | Т | Operating current<br>2–5.5 V                        | V <sub>STBY</sub> at<br>55 °C                             | _   | 45    | 110                    | μA   |

| I <sub>DDSTBY27</sub>                      | СС | Ρ | Operating current<br>0.95-1.2 V                     | V <sub>STBY</sub> 27 <sup>o</sup> C                       |     | 25    | 90                     | μΑ   |

|                                            |    | Ρ | Operating current<br>2-5.5 V                        | V <sub>STBY</sub> 27 °C                                   |     | 35    | 100                    | μΑ   |

| IDDSTBY150                                 | СС | Р | Operating current<br>0.95-1.2 V                     | V <sub>STBY</sub><br>150 <sup>o</sup> C                   | _   | 790   | 2000                   | μΑ   |

|                                            |    | Ρ | Operating current<br>2–5.5 V                        | V <sub>STBY</sub> at<br>150 <sup>o</sup> C                | _   | 760   | 2000                   | μA   |

| I <sub>DDPLL</sub>                         | СС | Р | Operating current<br>1.2 V supplies                 | V <sub>DDPLL</sub> ,<br>80 MHz,<br>V <sub>DD</sub> =1.2 V | _   |       | 15                     | mA   |

| I <sub>DDSLOW</sub><br>I <sub>DDSTOP</sub> | СС | Ρ | V <sub>DD</sub> low-power mode operating current at | Slow<br>mode <sup>10</sup>                                | _   |       | 90                     | mA   |

|                                            |    | Р | 1.32 V                                              | Stop mode <sup>11</sup>                                   | _   |       | 75                     |      |

| I <sub>DD33</sub>                          | СС | С | Operating current<br>3.3 V supplies                 | V <sub>RC33</sub> <sup>1,12</sup>                         | _   |       | 60                     | mA   |

| I <sub>DDA</sub>                           | СС | Ρ | Operating current                                   | V <sub>DDA</sub>                                          | _   | —     | 30.0                   | mA   |

| I <sub>REF</sub><br>I <sub>DDREG</sub>     |    | Ρ | 5.0 V supplies                                      | Analog<br>reference<br>supply<br>current<br>(transient)   | _   | _     | 1.0                    |      |

|                                            |    | С |                                                     | V <sub>DDREG</sub>                                        | _   | —     | 70 <sup>13</sup>       |      |

| I <sub>DDH1</sub>                          | СС | D | Operating current                                   | V <sub>DDEH1</sub>                                        | _   | —     | See note <sup>14</sup> | mA   |

| I <sub>DDH4</sub><br>I <sub>DDH6</sub>     |    | D | V <sub>DDE</sub> <sup>14</sup> supplies             | V <sub>DDEH4</sub>                                        | _   | —     |                        |      |

| I <sub>DDH7</sub><br>I <sub>DD7</sub>      |    | D |                                                     | V <sub>DDEH6</sub>                                        |     |       |                        |      |

| I <sub>DDH9</sub>                          |    | D |                                                     | V <sub>DDEH7</sub>                                        | _   |       |                        |      |

| I <sub>DD12</sub>                          |    | D |                                                     | V <sub>DDE7</sub>                                         |     |       |                        |      |

|                                            |    | D |                                                     | V <sub>DDEH9</sub>                                        |     |       |                        |      |

|                                            |    | D |                                                     | V <sub>DDE12</sub>                                        |     | _     |                        |      |

| Table 21. DC electrical specifications (c | continued) |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

- <sup>4</sup> V<sub>FLASH</sub> is only available in the calibration package.

- <sup>5</sup> Power supply for multi-voltage pads cannot be below 4.5 V when in low-swing mode.

- <sup>6</sup> The slew rate (SRC) setting must be 0b11 when in low-swing mode.

- <sup>7</sup> While in low-swing mode there are no restrictions in transitioning to high-swing mode.

- <sup>8</sup> Pin in low-swing mode can accept a 5 V input.

- $^9~$  All V\_OL/V\_OH values 100% tested with ± 2 mA load except where noted.

- <sup>10</sup> Bypass mode, system clock at 1 MHz (using system clock divider), PLL shut down, CPU running simple executive code, 4 x ADC conversion every 10 ms, 2 x PWM channels 1 kHz, all other modules stopped.

- <sup>11</sup> Bypass mode, system clock at 1 MHz (using system clock divider), CPU stopped, PIT running, all other modules stopped.

- <sup>12</sup> This current will be consumed for external regulation and internal regulation, when 3.3V regulator is switched off by shadow flash

- $^{13}$  If 1.2V and 3.3V internal regulators are on,then iddreg=70mA

- If supply is external that is 3.3V internal regulator is off, then iddreg=15mA

- <sup>14</sup> Power requirements for each I/O segment are dependent on the frequency of operation and load of the I/O pins on a particular I/O segment, and the voltage of the I/O segment. See Table 22 for values to calculate power dissipation for specific operation. The total power consumption of an I/O segment is the sum of the individual power consumptions for each pin on the segment.

- $^{15}$  Absolute value of current, measured at  $V_{\text{IL}}$  and  $V_{\text{IH}}.$

- <sup>16</sup> Weak pull up/down inactive. Measured at  $V_{DDE}$  = 3.6 V and  $V_{DDEH}$  = 5.25 V. Applies to fast, slow, and medium pads. <sup>17</sup> Maximum leakage occurs at maximum operating temperature. Leakage current decreases by approximately one-half

- for each 8 to 12 °C, in the ambient temperature range of 50 to 125 °C. Applies to analog pads.

- <sup>18</sup> Applies to CLKOUT, external bus pins, and Nexus pins.

- $^{19}$  Applies to the FCK, SDI, SDO, and  $\overline{\text{SDS}}$  pins.

- <sup>20</sup> This programmable option applies only to eQADC differential input channels and is used for biasing and sensor diagnostics.

| Symp                  |    | с        | Paramete                                                                       |                                 | Va                                          | lue                                         | Unit   |  |  |  |

|-----------------------|----|----------|--------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|---------------------------------------------|--------|--|--|--|

|                       |    | Paramete | er.                                                                            | min                             | max                                         | Unit                                        |        |  |  |  |

| GAINVGA21             | CC | _        | Variable gain amplifier accuracy (gain=2) <sup>2</sup>                         |                                 |                                             |                                             |        |  |  |  |

|                       | CC | D        | INL                                                                            | 8 MHz<br>ADC                    | -5                                          | 5                                           | Counts |  |  |  |

|                       | CC | D        | -                                                                              | 16 MHz<br>ADC                   | -8                                          | 8                                           | Counts |  |  |  |

|                       | CC | D        | DNL                                                                            | 8 MHz<br>ADC                    | -3                                          | 3                                           | Counts |  |  |  |

| -                     | CC | D        | -                                                                              | 16 MHz<br>ADC                   | -3                                          | 3                                           | Counts |  |  |  |

| GAINVGA4 <sup>1</sup> | CC | -        | Variable gain amplifier accuracy (gain=4) <sup>2</sup>                         |                                 |                                             |                                             |        |  |  |  |

|                       | CC | D        | INL                                                                            | 8 MHz<br>ADC                    | -7                                          | 7                                           | Counts |  |  |  |

|                       | CC | D        | -                                                                              | 16 MHz<br>ADC                   | -8                                          | 8                                           | Counts |  |  |  |

|                       | CC | D        | DNL                                                                            | 8 MHz<br>ADC                    | -4                                          | 4                                           | Counts |  |  |  |

|                       | CC | D        |                                                                                | 16 MHz<br>ADC                   | _4                                          | 4                                           | Counts |  |  |  |

| DIFF <sub>max</sub>   | CC | С        | Maximum<br>differential voltage<br>(DANx+ - DANx-) or                          | PREGAIN<br>set to 1X<br>setting | _                                           | (VRH - VRL)/2                               | V      |  |  |  |

| DIFF <sub>max2</sub>  | CC | С        | (DANx DANx+) <sup>5</sup>                                                      | PREGAIN<br>set to 2X<br>setting | _                                           | (VRH - VRL)/4                               | V      |  |  |  |

| DIFF <sub>max4</sub>  | СС | С        |                                                                                | PREGAIN<br>set to 4X<br>setting | _                                           | (VRH - VRL)/8                               | V      |  |  |  |

| DIFF <sub>cmv</sub>   | CC | С        | Differential input<br>Common mode<br>voltage (DANx- +<br>DANx+)/2 <sup>5</sup> | _                               | (V <sub>RH</sub> + V <sub>RL</sub> )/2 - 5% | (V <sub>RH</sub> + V <sub>RL</sub> )/2 + 5% | V      |  |  |  |

### Table 30. eQADC differential ended conversion specifications (operating) (continued)

Applies only to differential channels.

<sup>2</sup> Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed by as indicated.

<sup>3</sup> At  $V_{RH} - V_{RL}$  = 5.12 V, one LSB = 1.25 mV.

<sup>4</sup> Guaranteed 10-bit mono tonicity.

<sup>5</sup> Voltages between VRL and VRH will not cause damage to the pins. However, they may not be converted accurately if the differential voltage is above the maximum differential voltage. In addition, conversion errors may occur if the common mode voltage of the differential signal violates the Differential Input common mode voltage specification.

1

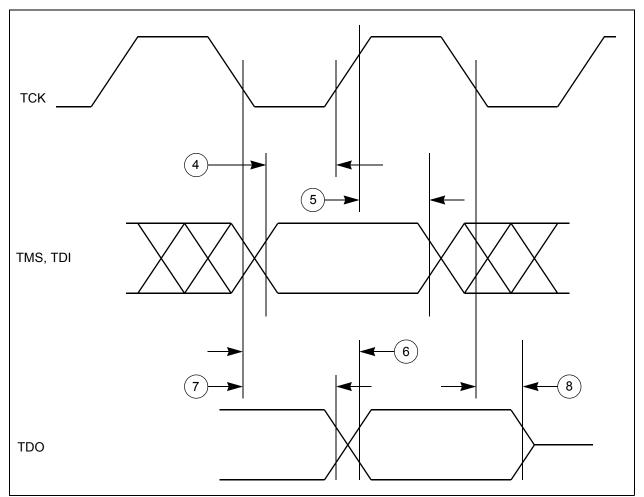

Figure 12. JTAG test access port timing

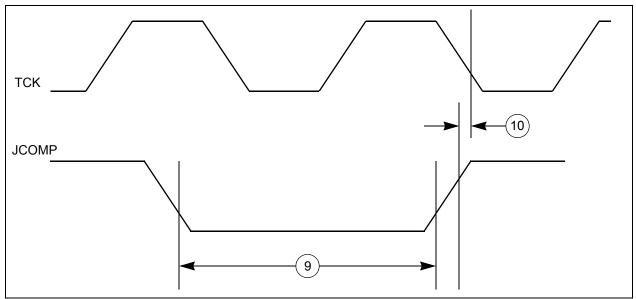

Figure 13. JTAG JCOMP timing

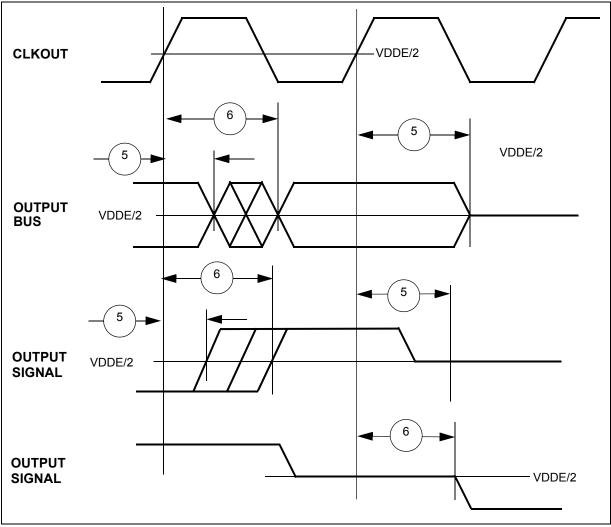

Figure 19. Synchronous output timing

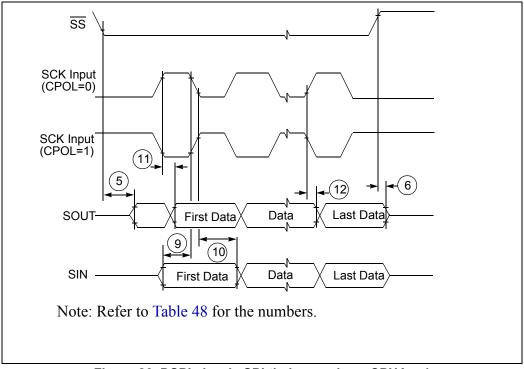

Figure 26. DSPI classic SPI timing — slave, CPHA = 1

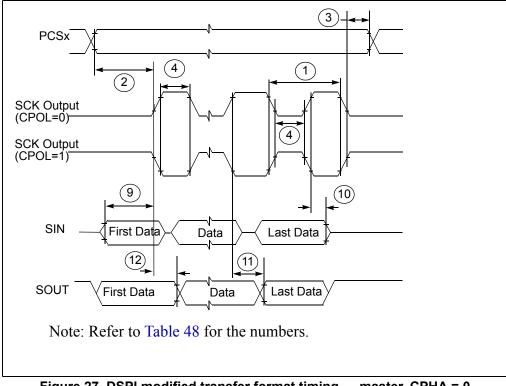

Figure 27. DSPI modified transfer format timing — master, CPHA = 0

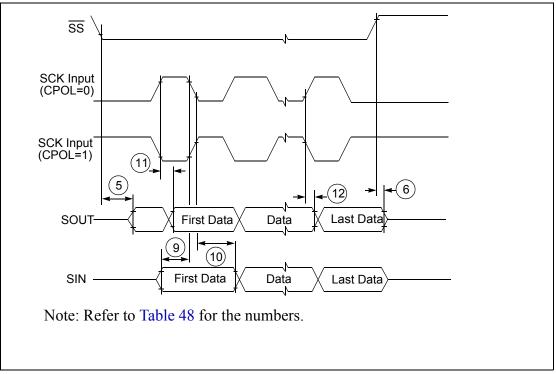

Figure 30. DSPI modified transfer format timing — slave, CPHA =1

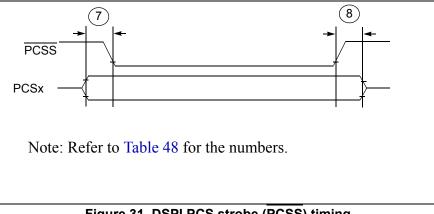

Figure 31. DSPI PCS strobe (PCSS) timing

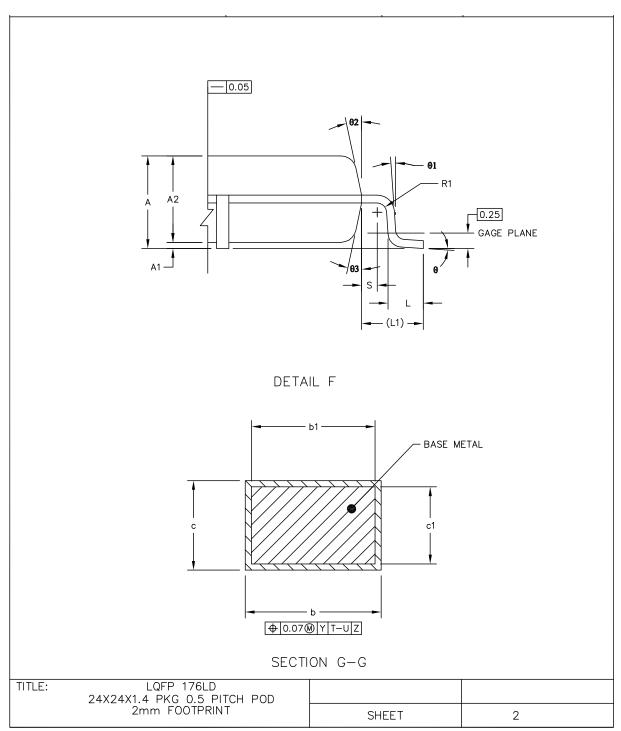

Figure 33. 176 LQFP package mechanical drawing (part 1)

Figure 34. 176 LQFP package mechanical drawing (part 2)

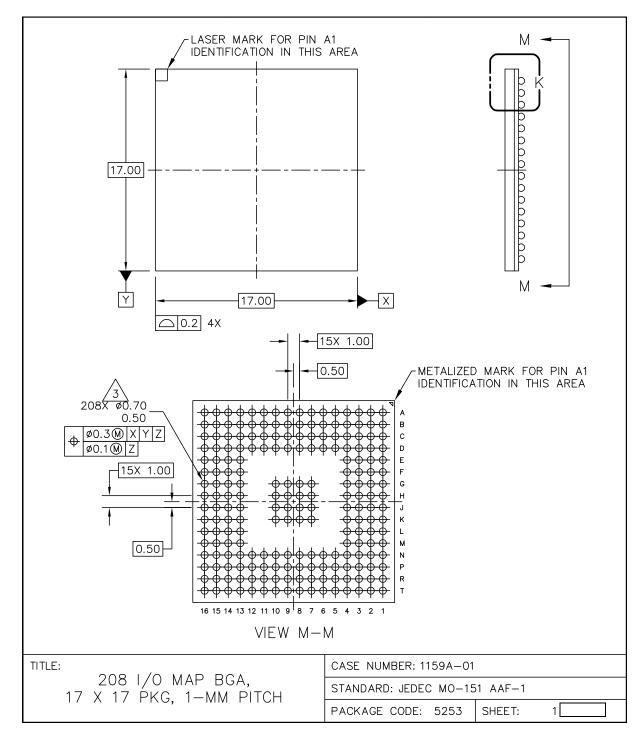

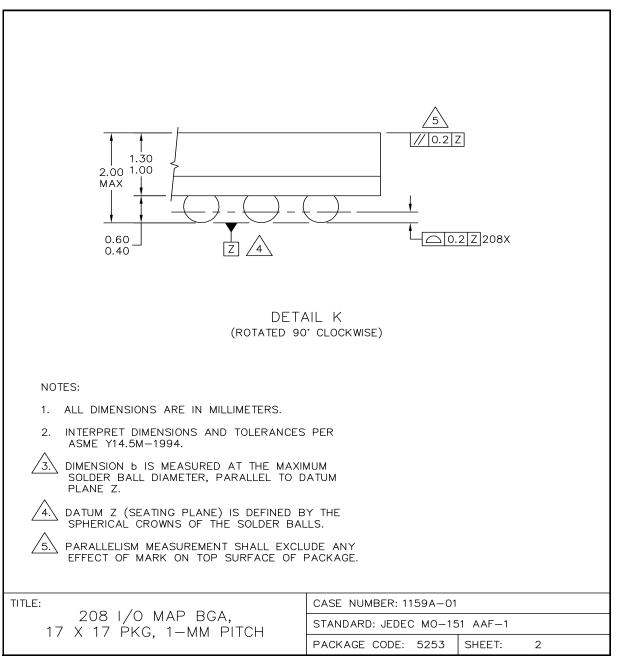

# 4.1.2 208 MAPBGA

Figure 36. 208 MAPBGA package mechanical drawing (part 1)

Figure 37. 208 MAPBGA package mechanical drawing (part 2)

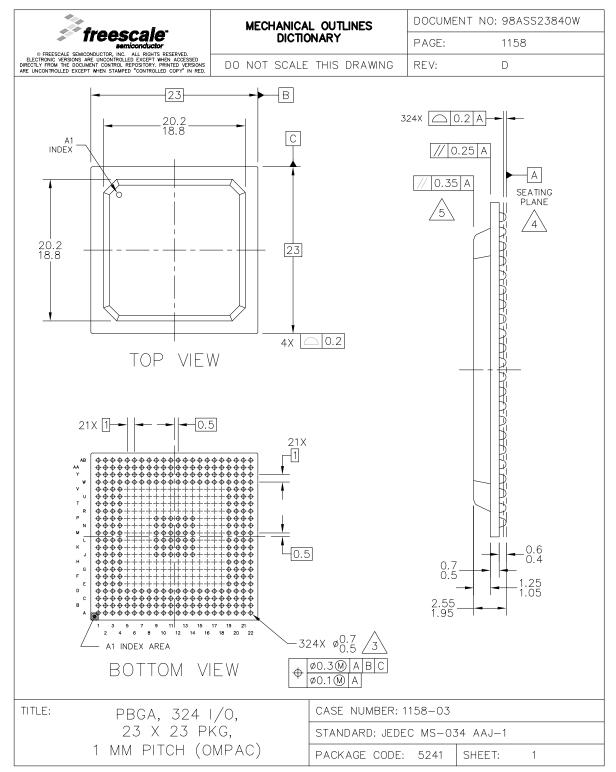

# 4.1.3 324 TEPBGA

Figure 38. 324 BGA package mechanical drawing (part 1)

# 5 Ordering information

Table 52 shows the orderable part numbers for the MPC5644A series.

| Table 52. | Orderable | part number | summary |

|-----------|-----------|-------------|---------|

|-----------|-----------|-------------|---------|

| Part number    | Flash/SRAM  | Package              | Speed<br>(MHz) |

|----------------|-------------|----------------------|----------------|

| SPC5643AF0MLU3 | 3 MB/192 KB | 176LQFP (Pb free)    | 80             |

| SPC5643AF0MMG3 | 3 MB/192 KB | 208MAPBGA(Pb free)   | 80             |

| SPC5643AF0MVZ3 | 3 MB/192 KB | 324PBGA (Pb free)    | 80             |

| SPC5643AF0MLU2 | 3 MB/192 KB | 176LQFP (Pb free)    | 120            |

| SPC5643AF0MMG2 | 3 MB/192 KB | 208MAPBGA (Pb free)  | 120            |

| SPC5643AF0MVZ2 | 3 MB/192 KB | 324PBGA (Pb free)    | 120            |

| SPC5643AF0MLU1 | 3 MB/192 KB | 176LQFP (Pb free)    | 150            |

| SPC5643AF0MMG1 | 3 MB/192 KB | 208MAPBGA (Pb free)  | 150            |

| SPC5643AF0MVZ1 | 3 MB/192 KB | 324PBGA (Pb free)    | 150            |

| SPC5644AF0MLU3 | 4 MB/192 KB | 176 LQFP (Pb free)   | 80             |

| SPC5644AF0MMG3 | 4 MB/192 KB | 208 MAPBGA (Pb free) | 80             |

| SPC5644AF0MVZ3 | 4 MB/192 KB | 324 TEPBGA (Pb free) | 80             |

| SPC5644AF0MLU2 | 4 MB/192 KB | 176 LQFP (Pb free)   | 120            |

| SPC5644AF0MMG2 | 4 MB/192 KB | 208 MAPBGA (Pb free) | 120            |

| SPC5644AF0MVZ2 | 4 MB/192 KB | 324 TEPBGA (Pb free) | 120            |

| SPC5644AF0MLU1 | 4 MB/192 KB | 176 LQFP (Pb free)   | 150            |

| SPC5644AF0MMG1 | 4 MB/192 KB | 208 MAPBGA (Pb free) | 150            |

| SPC5644AF0MVZ1 | 4 MB/192 KB | 324 TEPBGA (Pb free) | 150            |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MPC5644A Rev. 7 Jan 2012 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2009–2012. All rights reserved.