#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 150MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 151                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                           |

| Data Converters            | A/D 40x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 324-BBGA                                                                |

| Supplier Device Package    | 324-PBGA (23x23)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5644af0mvz1r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

## 1.1 Document Overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5644A series of microcontroller units (MCUs). For functional characteristics, refer to the MPC5644A Microcontroller Reference Manual.

## 1.2 Description

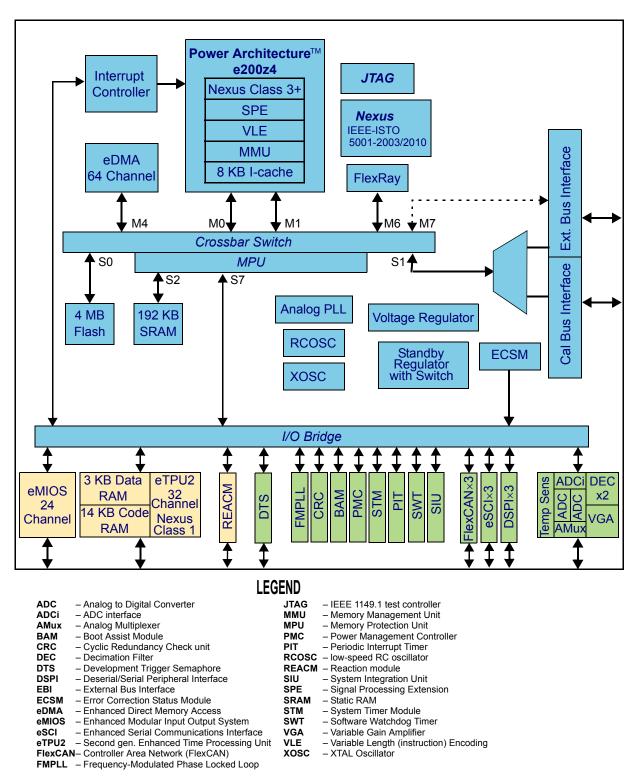

The microcontroller's e200z4 host processor core is built on Power Architecture<sup>®</sup> technology and designed specifically for embedded applications. In addition to the Power Architecture technology, this core supports instructions for digital signal processing (DSP).

The MPC5644A has two levels of memory hierarchy consisting of 8 KB of instruction cache, backed by 192 KB on-chip SRAM and 4 MB of internal flash memory. The MPC5644A includes an external bus interface, and also a calibration bus that is only accessible when using the Freescale VertiCal Calibration System.

This document describes the features of the MPC5644A and highlights important electrical and physical characteristics of the device.

etc. Each bit in the frame may be configured to serialize either eTPU channels, eMIOS channels or GPIO signals. The DSPI can be configured to serialize data to an external device that implements the Microsecond Bus protocol. There are three identical DSPI blocks on the MPC5644A MCU. The DSPI pins support 5 V logic levels or Low Voltage Differential Signalling (LVDS) to improve high speed operation.

DSPI module features include:

- Selectable LVDS pads working at 40 MHZ for SOUT and SCK pins for DSPI\_B and DSPI\_C

- 3 sources of serialized data: eTPU\_A, eMIOS output channels and memory-mapped register in the DSPI

- 4 destinations for deserialized data: eTPU\_A and eMIOS input channels, SIU external Interrupt input request, memory-mapped register in the DSPI

- 32-bit DSI and TSB modes require 32 PCR registers, 32 GPO and GPI registers in the SIU to select either GPIO, eTPU or eMIOS bits for serialization

- The DSPI Module can generate and check parity in a serial frame

### 1.4.15 eSCI

Three enhanced serial communications interface (eSCI) modules provide asynchronous serial communications with peripheral devices and other MCUs, and include support to interface to Local Interconnect Network (LIN) slave devices. Each eSCI block provides the following features:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit, data format

- Programmable 12-bit or 13-bit data format for Timed Serial Bus (TSB) configuration to support the Microsecond bus standard

- Automatic parity generation

- LIN support

- Autonomous transmission of entire frames

- Configurable to support all revisions of the LIN standard

- Automatic parity bit generation

- Double stop bit after bit error

- 10- or 13-bit break support

- Separately enabled transmitter and receiver

- Programmable transmitter output parity

- 2 receiver wake-up methods:

- Idle line wake-up

- Address mark wake-up

- Interrupt-driven operation with flags

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

- DMA support for both transmit and receive data

- Global error bit stored with receive data in system RAM to allow post processing of errors

### 1.4.16 FlexCAN

The MPC5644A MCU includes three controller area network (FlexCAN) blocks. The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to

- 1 receive FIFO per channel

- Up to 255 entries for each FIFO

- ECC support

### 1.4.18 System timers

The system timers include two distinct types of system timer:

- Periodic interrupts/triggers using the Periodic Interrupt Timer (PIT)

- Operating system task monitors using the System Timer Module (STM)

### 1.4.18.1 Periodic interrupt timer (PIT)

The PIT provides five independent timer channels, capable of producing periodic interrupts and periodic triggers. The PIT has no external input or output pins and is intended to provide system 'tick' signals to the operating system, as well as periodic triggers for eQADC queues. Of the five channels in the PIT, four are clocked by the system clock and one is clocked by the crystal clock. This one channel is also referred to as Real-Time Interrupt (RTI) and is used to wake up the device from low power stop mode.

The following features are implemented in the PIT:

- 5 independent timer channels

- Each channel includes 32-bit wide down counter with automatic reload

- 4 channels clocked from system clock

- 1 channel clocked from crystal clock (wake-up timer)

- Wake-up timer remains active when System STOP mode is entered; used to restart system clock after predefined time-out period

- Each channel optionally able to generate an interrupt request or a trigger event (to trigger eQADC queues) when timer reaches zero

### 1.4.18.2 System timer module (STM)

The System Timer Module (STM) is designed to implement the software task monitor as defined by AUTOSAR<sup>1</sup>. It consists of a single 32-bit counter, clocked by the system clock, and four independent timer comparators. These comparators produce a CPU interrupt when the timer exceeds the programmed value.

The following features are implemented in the STM:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

### 1.4.19 Software watchdog timer (SWT)

The Software Watchdog Timer (SWT) is a second watchdog module to complement the standard Power Architecture watchdog integrated in the CPU core. The SWT is a 32-bit modulus counter, clocked by the system clock or the crystal clock, that can provide a system reset or interrupt request when the correct software key is not written within the required time window.

The following features are implemented:

- 32-bit modulus counter

- Clocked by system clock or crystal clock

1.AUTOSAR: AUTomotive Open System ARchitecture (see http://www.autosar.org)

# 2 Pinout and signal description

This section contains the pinouts for all production packages for the MPC5644A family of devices.

#### CAUTION

Any pins labeled "NC" are to be left unconnected. Any connection to an external circuit or voltage may cause unpredictable device behavior or damage.

| М  | VDDEH6AB | NC               | NC       | VRC33    |         |         |         |         | VSS      | VSS    | VSS     |

|----|----------|------------------|----------|----------|---------|---------|---------|---------|----------|--------|---------|

| Ν  | NC       | VSS              | SCI_A_TX | NC       |         |         |         |         | VSS      | VSS    | VSS     |

| Ρ  | RSTCFG   | RSTOUT           | SCI_A_RX | CAN_C_TX |         |         |         |         | VSS      | VSS    | VSS     |

| R  | RESET    | NC               | NC       | NC       |         |         |         |         |          |        |         |

| т  | VSS      | VSS <sup>1</sup> | BOOTCFG0 | VSS      |         |         |         |         |          |        |         |

| U  | EXTAL    | BOOTCFG1         | PLLCFG1  | VDDEH6AB |         |         |         |         |          |        |         |

| V  | XTAL     | PLLREF           | CAN_C_RX | SCI_C_RX |         |         |         |         |          |        |         |

| w  | VDDPLL   | CAN_B_RX         | VDD      | SCI_C_TX | EMIOS23 | EMIOS16 | EMIOS15 | EMIOS8  | VDDEH4AB | EMIOS1 | ETPUA1  |

| Y  | CAN_B_TX | VDD              | VSS      | CAN_A_RX | EMIOS22 | EMIOS17 | EMIOS14 | EMIOS9  | EMIOS5   | EMIOS2 | ETPUA0  |

| AA | VDD      | VSS              | WKPCFG   | VDDEH4AB | EMIOS21 | EMIOS18 | EMIOS13 | EMIOS10 | EMIOS6   | EMIOS3 | EMIOS0  |

| AB | VSS      | SCI_B_TX         | SCI_B_RX | CAN_A_TX | EMIOS20 | EMIOS19 | EMIOS12 | EMIOS11 | EMIOS7   | EMIOS4 | TCRCLKA |

|    | 22       | 21               | 20       | 19       | 18      | 17      | 16      | 15      | 14       | 13     | 12      |

<sup>1</sup> This pin (T21) should be tied low.

Figure 7. 324-pin TEPBGA package ballmap (southeast, viewed from above)

### Table 3. MPC5644A signal properties (continued)

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                    | Р                        | PCR                                  |                  | I/O                  | Voltage <sup>5</sup> / | Sta          | itus <sup>7</sup>    | Package pin # |     |      |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------|----------------------|------------------------|--------------|----------------------|---------------|-----|------|

| Name                                                         | Function <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                              | A<br>G <sup>2</sup>      | PA<br>Field <sup>3</sup>             | PCR <sup>4</sup> | 1/О<br>Туре          | Pad Type <sup>6</sup>  | During Reset | After<br>Reset       | 176           | 208 | 324  |

| BOOTCFG[1]<br>IRQ[3]<br>ETRIG3<br>GPIO[212]                  | Boot Config. Input<br>External Interrupt Request<br>eQADC Trigger Input<br>GPIO                                                                                                                                                                                                                                                                                                    | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 212              | <br> <br> /0         | VDDEH6<br>Slow         | — / Down     | BOOTCFG[1] /<br>Down | 85            | M15 | U21  |

| WKPCFG<br>NMI<br>DSPI_B_SOUT<br>GPIO[213]                    | Weak Pull Config. Input<br>Non-Maskable Interrupt<br>DSPI D data output<br>GPIO                                                                                                                                                                                                                                                                                                    | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 213              | <br> <br> /0         | VDDEH6<br>Medium       | — / Up       | WKPCFG / Up          | 86            | L15 | AA20 |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                    |                          |                                      | Ext              | ernal B              | us Interface           |              |                      |               |     | •    |

| CS[0]<br>ADDR[8]<br>GPIO[0]                                  | External chip selects<br>External address bus<br>GPIO                                                                                                                                                                                                                                                                                                                              | P<br>A1<br>G             | 01<br>10<br>00                       | 0                | 0<br>I/O<br>I/O      | VDDE2<br>Fast          | — / Up       | — / Up               | _             | _   | G1   |

| CS[1]<br>ADDR9<br>GPIO[1]                                    | External chip selectsP011External address busA110GPIOG00                                                                                                                                                                                                                                                                                                                           |                          | 1                                    | 0<br>I/O<br>I/O  | VDDE2<br>Fast        | — / Up                 | — / Up       | -                    | -             | H1  |      |

| CS[2]<br>ADDR10<br>WE[2]/BE[2]<br>CAL_WE[2]/BE[2]<br>GPI0[2] | External chip selects<br>External address bus<br>Write/byte enable<br>Cal. bus write/byte enable<br>GPIO                                                                                                                                                                                                                                                                           | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 2                | 0<br>I/O<br>0<br>I/O | VDDE2<br>Fast          | — / Up       | — / Up               | -             | _   | H2   |

| CS[3]<br>ADDR11<br>WE[3]/BE[3]<br>CAL_WE[3]/BE[3]<br>GPI0[3] | External chip selects         P         0001         3         O         VDDE2         — / Up           External address bus         A1         0010         I/O         Fast         — / Up           Write/byte enable         A2         0100         O         O         — / Up           Cal bus write/byte enable         A3         1000         O         —         — / Up |                          | — / Up                               | — / Up           | -                    | _                      | H4           |                      |               |     |      |

| ADDR12<br>GPIO[8]                                            | External address bus<br>GPIO                                                                                                                                                                                                                                                                                                                                                       | P<br>G                   | 01<br>00                             | 8                | I/O<br>I/O           | VDDE3<br>Fast          | — / Up       | — / Up               | —             | —   | N2   |

| ADDR13<br>WE[2]<br>GPIO[9]                                   | External address bus F<br>Write/byte enable A<br>GPIO C                                                                                                                                                                                                                                                                                                                            |                          | 001<br>100<br>000                    | 9                | I/O<br>O<br>I/O      | VDDE3<br>Fast          | — / Up       | — / Up               | _             | —   | N1   |

| ADDR14<br>WE[3]<br>GPIO[10]                                  | External address bus<br>Write/byte enables<br>GPIO                                                                                                                                                                                                                                                                                                                                 | P<br>A2<br>G             | 001<br>100<br>000                    | 10               | I/O<br>O<br>I/O      | VDDE3<br>Fast          | — / Up       | — / Up               | _             | _   | P1   |

| ADDR15<br>GPIO[11]                                           | External address bus<br>GPIO                                                                                                                                                                                                                                                                                                                                                       | P<br>G                   | 01<br>00                             | 11               | I/O<br>I/O           | VDDE3<br>Fast          | — / Up       | — / Up               | —             | —   | P2   |

### Table 3. MPC5644A signal properties (continued)

|                                            |                                                                                       |                     | PCR                      |                  | I/O                    | Voltage <sup>5</sup> / | Sta          | tus <sup>7</sup> | Package pin # |     |     |

|--------------------------------------------|---------------------------------------------------------------------------------------|---------------------|--------------------------|------------------|------------------------|------------------------|--------------|------------------|---------------|-----|-----|

| Name                                       | Function <sup>1</sup>                                                                 | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | і/О<br>Туре            | Pad Type <sup>6</sup>  | During Reset | After<br>Reset   | 176           | 208 | 324 |

| ADDR16<br>FR_A_TX<br>DATA16<br>GPIO[12]    | External address bus<br>Flexray TX data channel A<br>External data bus<br>GPIO        | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 12               | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | -   | P3  |

| ADDR17<br>FR_A_TX_EN<br>DATA17<br>GPIO[13] | External address bus<br>FlexRay ch. A TX data enable<br>External data bus<br>GPIO     | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 13               | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | _   | P4  |

| ADDR18<br>FR_A_RX<br>DATA18<br>GPIO[14]    | External address bus<br>Flexray RX data ch. A<br>External data bus<br>GPIO            | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 14               | I/O<br>I<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | _   | R1  |

| ADDR19<br>FR_B_TX<br>DATA19<br>GPIO[15]    | External address bus<br>Flexray TX data ch. B<br>External data bus<br>GPIO            | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 15               | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | _   | R2  |

| ADDR20<br>FR_B_TX_EN<br>DATA20<br>GPIO[16] | External address bus<br>Flexray TX data enable for ch. B<br>External data bus<br>GPIO | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 16               | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | _   | R4  |

| ADDR21<br>FR_B_RX<br>DATA21<br>GPIO[17]    | External address bus<br>Flexray RX data channel B<br>External data bus<br>GPIO        | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 17               | I/O<br>I<br>I/O<br>I/O | VDDE-EH<br>Medium      | — / Up       | — / Up           | -             | _   | T1  |

| ADDR22<br>DATA22<br>GPIO[18]               | External address bus<br>External data bus<br>GPIO                                     | P<br>A2<br>G        | 001<br>100<br>000        | 18               | 1/0<br>1/0<br>1/0      | VDDE-EH<br>Medium      | — / Up       | — / Up           | —             | —   | T2  |

| ADDR23<br>DATA23<br>GPIO[19]               | External address bus<br>External data bus<br>GPIO                                     |                     | 001<br>100<br>000        | 19               | I/O<br>I/O<br>I/O      | VDDE-EH<br>Medium      | — / Up       | — / Up           | —             | —   | Т3  |

| ADDR24<br>DATA24<br>GPIO[20]               | External address bus<br>External data bus<br>GPIO                                     | P<br>A2<br>G        | 001<br>100<br>000        | 20               | I/O<br>I/O<br>I/O      | VDDE-EH<br>Medium      | — / Up       | — / Up           | —             | _   | T4  |

| ADDR25<br>DATA25<br>GPIO[21]               | External address bus<br>External data bus<br>GPIO                                     | P<br>A2<br>G        | 001<br>100<br>000        | 21               | I/O<br>I/O<br>I/O      | VDDE-EH<br>Medium      | — / Up       | — / Up           | —             | _   | U1  |

### Table 3. MPC5644A signal properties (continued)

|                                                    |                                                                                                                                                           | Р                   | PCR                      |                  | I/O          | Voltage <sup>5</sup> /         | Sta          | tus <sup>7</sup> | Package pin # |     |     |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|------------------|--------------|--------------------------------|--------------|------------------|---------------|-----|-----|

| Name                                               | Function <sup>1</sup>                                                                                                                                     | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | 7уре         | Pad Type <sup>6</sup>          | During Reset | After<br>Reset   | 176           | 208 | 324 |

|                                                    |                                                                                                                                                           |                     |                          |                  | eQ           | ADC                            | ·            |                  |               |     |     |

| AN0 <sup>18</sup><br>DAN0+                         | Single Ended Analog Input<br>Positive Terminal Diff. Input                                                                                                | Р                   | _                        | _                | l            | VDDA<br>Analog                 | I / —        | AN[0] / —        | 172           | B5  | C6  |

| AN1 <sup>18</sup><br>DAN0-                         | Single Ended Analog Input<br>Negative Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I/—          | AN[1] / —        | 171           | A6  | C7  |

| AN2 <sup>18</sup><br>DAN1+                         | Single Ended Analog Input<br>Positive Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I / —        | AN[2] / —        | 170           | D6  | D7  |

| AN3 <sup>18</sup><br>DAN1-                         | Single Ended Analog Input<br>Negative Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I / —        | AN[3] / —        | 169           | C7  | D8  |

| AN4 <sup>18</sup><br>DAN2+                         | Single Ended Analog Input     P     —     I     VDDA     I / —     AN[4] / —       Positive Terminal Diff. Input     I     I     Analog     I     I     I |                     | AN[4] / —                | 168              | B6           | B7                             |              |                  |               |     |     |

| AN5 <sup>18</sup><br>DAN2-                         | Single Ended Analog Input<br>Negative Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I / —        | AN[5] / —        | 167           | A7  | B8  |

| AN6 <sup>18</sup><br>DAN3+                         | Single Ended Analog Input<br>Positive Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I / —        | AN[6] / —        | 166           | D7  | C8  |

| AN7 <sup>18</sup><br>DAN3-                         | Single Ended Analog Input<br>Negative Terminal Diff. Input                                                                                                | Р                   | —                        | —                | l            | VDDA<br>Analog                 | I / —        | AN[7] / —        | 165           | C8  | C9  |

| AN8<br>ANW                                         | Single-ended Analog Input<br>Multiplexed Analog Input                                                                                                     | Р                   | 01                       | _                | I            | VDDA<br>Analog                 | I/—          | AN[8] / —        | 9             | B3  | E1  |

| AN9<br>ANX                                         | Single-ended Analog Input<br>External Multiplexed Analog<br>Input                                                                                         | Р                   | 01                       | _                | l            | VDDA<br>Analog                 | I / —        | AN[9] / —        | 5             | A2  | C2  |

| AN10<br>ANY                                        | Single-ended Analog Input<br>Multiplexed Analog Input                                                                                                     | Р                   | 01                       | _                | I            | VDDA<br>Analog                 | I <i>/</i> — | AN[10] / —       | -             | _   | D1  |

| AN11<br>ANZ                                        | Single-ended Analog Input<br>Multiplexed Analog Input                                                                                                     | Р                   | 01                       | —                | I            | VDDA<br>Analog                 | I/—          | AN[11] / —       | 4             | A3  | C1  |

| AN12 - SDS<br>MA0<br>ETPUA19_O <sup>8</sup><br>SDS | Single-ended Analog Input<br>MUX Address 0<br>eTPU A channel (output only)<br>eQADC Serial Data Select                                                    | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 215              | <br>0<br> /0 | VDDEH7 <sup>19</sup><br>Medium | I / —        | AN[12] / —       | 148           | A12 | C13 |

| AN13 - SDO<br>MA1<br>ETPUA21_O <sup>8</sup><br>SDO | Single-ended Analog Input<br>MUX Address 1<br>eTPU A channel (output only)<br>eQADC Serial Data Out                                                       | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 216              | <br>0<br>0   | VDDEH7 <sup>19</sup><br>Medium | 1/—          | AN[13] / —       | 147           | B12 | B13 |

#### Table 4. Pad types

| Pad Type              | Name         | I/O Voltage Range                                                 |

|-----------------------|--------------|-------------------------------------------------------------------|

| Slow                  | pad_ssr_hv   | 3.0V - 5.5 V                                                      |

| Medium                | pad_msr_hv   | 3.0 V - 5.5 V                                                     |

| Fast                  | pad_fc       | 3.0 V - 3.6 V                                                     |

| MultiV <sup>1,2</sup> | pad_multv_hv | 3.0 V - 5.5 V (high swing mode)<br>3.0 V - 3.6 V (low swing mode) |

| Analog                | pad_ae_hv    | 0.0 - 5.5 V                                                       |

| LVDS                  | pad_lo_lv    | —                                                                 |

<sup>1</sup> Multivoltage pads are automatically configured in low swing mode when a JTAG or Nexus function is selected, otherwise they are high swing.

<sup>2</sup> VDDEH7 supply cannot be below 4.5 V when in low-swing mode.

## 2.5 Signal details

| Signal                                 | Module or Function                      | Description                                                                                                                                                                                                                                                            |

|----------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT                                 | Clock Generation                        | MPC5644A clock output for the external/calibration bus interface                                                                                                                                                                                                       |

| ENGCLK                                 | Clock Generation                        | Clock for external ASIC devices                                                                                                                                                                                                                                        |

| EXTAL                                  | Clock Generation                        | Input pin for an external crystal oscillator or an external clock source based on the value driven on the PLLREF pin at reset.                                                                                                                                         |

| PLLREF                                 | Clock Generation<br>Reset/Configuration | PLLREF is used to select whether the oscillator operates in xtal mode or external reference mode from reset. PLLREF=0 selects external reference mode. On the 324BGA package, PLLREF is bonded to the ball used for PLLCFG[0] for compatibility with MPC55xx devices . |

|                                        |                                         | For the 176-pin QFP and 208-ball BGA packages:<br>0: External reference clock is selected.<br>1: XTAL oscillator mode is selected                                                                                                                                      |

|                                        |                                         | For the 324 ball BGA package:<br>If RSTCFG is 0:<br>0: External reference clock is selected.<br>1: XTAL oscillator mode is selected.                                                                                                                                   |

|                                        |                                         | If RSTCFG is 1, XTAL oscillator mode is selected.                                                                                                                                                                                                                      |

| XTAL                                   | Clock Generation                        | Crystal oscillator input                                                                                                                                                                                                                                               |

| DSPI_B_SCK_LVDS-<br>DSPI_B_SCK_LVDS+   | DSPI                                    | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                                                                        |

| DSPI_B_SOUT_LVDS-<br>DSPI_B_SOUT_LVDS+ | DSPI                                    | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                                                                        |

| DSPI_C_SCK_LVDS-<br>DSPI_C_SCK_LVDS+   | DSPI                                    | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                                                                        |

#### Table 5. Signal details

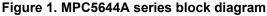

- <sup>2</sup> BETA represents the worst-case external transistor. It is measured on a per-part basis and calculated as  $(I_{DD} \div I_{VRCCTL})$ .

- <sup>3</sup> Refer to Table 52 for the maximum operating frequency.

- $^4$  Values are based on I<sub>DD</sub> from high-use applications as explained in the I<sub>DD</sub> Electrical Specification.

### 3.6.2 Regulator Example

In designs where the MPC5644A microcontroller's internal regulators are used, a ballast is required for generation of the 1.2 V internal supply. No ballast is required when an external 1.2 V supply is used.

VRCCTL capacitor and resistor is required

Figure 8. Core voltage regulator controller external components preferred configuration

Table 17. MPC5644A External network specification

| External Network<br>Parameter      | Min          | Тур          | Мах             | Comment                  |

|------------------------------------|--------------|--------------|-----------------|--------------------------|

| T1                                 |              |              |                 | NJD2873 or BCP68<br>only |

| Cb                                 | 1.1 μF       | 2.2µF        | 2.97μF          | X7R,-50%/+35%            |

| Се                                 | 3*2.35μF+5μF | 3*4.7μF+10μF | 3*6.35μF+13.5μF | X7R, -50%/+35%           |

| Equivalent ESR of<br>Ce capacitors | 5mΩ          |              | 50mΩ            |                          |

| Cd                                 | 4*50nF       | 4*100nF      | 4*135nF         | X7R, -50%/+35%           |

| Rb                                 | 9Ω           | 10Ω          | 11Ω             | +/-10%                   |

| V <sub>DDEH</sub> | V <sub>DD</sub> | Pad State      |

|-------------------|-----------------|----------------|

| LOW               | Х               | LOW            |

| V <sub>DDEH</sub> | LOW             | HIGH IMPEDANCE |

| V <sub>DDEH</sub> | V <sub>DD</sub> | FUNCTIONAL     |

Table 20. Power sequence pin states (medium, slow, and multi-voltage pads)

## 3.8 DC electrical specifications

| Cumhal                             | 1  | с | Parameter                             | Conditions       |                       | Value |                       | Unit |

|------------------------------------|----|---|---------------------------------------|------------------|-----------------------|-------|-----------------------|------|

| Symbol                             |    | C | Parameter                             | Conditions       | min                   | typ   | max                   | Onit |

| V <sub>DD</sub>                    | SR |   | Core supply voltage                   | _                | 1.14                  |       | 1.32                  | V    |

| V <sub>DDE</sub>                   | SR | _ | I/O supply voltage                    | _                | 1.62                  |       | 3.6                   | V    |

| V <sub>DDEH</sub>                  | SR | _ | I/O supply voltage                    | _                | 3.0                   |       | 5.25                  | V    |

| V <sub>DDE-EH</sub>                | SR | _ | I/O supply voltage                    | _                | 3.0                   |       | 5.25                  | V    |

| V <sub>RC33</sub>                  | SR |   | 3.3 V regulated voltage <sup>1</sup>  | _                | 3.0                   | _     | 3.6                   | V    |

| V <sub>DDA</sub>                   | SR | _ | Analog supply voltage                 | _                | 4.75 <sup>2</sup>     |       | 5.25                  | V    |

| V <sub>INDC</sub>                  | SR | _ | Analog input voltage                  | _                | V <sub>SSA</sub> -0.3 | _     | V <sub>DDA</sub> +0.3 | V    |

| $V_{SS} - V_{SSA}$                 | SR |   | V <sub>SS</sub> differential voltage  | —                | -100                  | _     | 100                   | mV   |

| V <sub>RL</sub>                    | SR |   | Analog reference low voltage          | —                | V <sub>SSA</sub>      | _     | V <sub>SSA</sub> +0.1 | V    |

| V <sub>RL</sub> – V <sub>SSA</sub> | SR | _ | VRL differential voltage              | _                | -100                  |       | 100                   | mV   |

| V <sub>RH</sub>                    | SR | _ | Analog reference high voltage         | _                | V <sub>DDA</sub> -0.1 |       | V <sub>DDA</sub>      | V    |

| V <sub>RH</sub> – V <sub>RL</sub>  | SR | _ | V <sub>REF</sub> differential voltage | _                | 4.75                  |       | 5.25                  | V    |

| V <sub>DDF</sub>                   | SR |   | Flash operating voltage <sup>3</sup>  | _                | 1.14                  |       | 1.32                  | V    |

| V <sub>FLASH</sub> <sup>4</sup>    | SR | _ | Flash read voltage                    | _                | 3.0                   |       | 3.6                   | V    |

| V <sub>STBY</sub>                  | SR | _ | SRAM standby voltage                  | Unregulated mode | 0.95                  | _     | 1.2                   | V    |

|                                    |    |   | Keep-out Range:<br>1.2V–2V            | Regulated mode   | 2.0                   | _     | 5.5                   |      |

| #  | Symb               | ol | С | Characteristic                                                                 | Min. Value | Max. Value | Unit |

|----|--------------------|----|---|--------------------------------------------------------------------------------|------------|------------|------|

| 11 | t <sub>NTDIS</sub> | CC | D | TDI Data Setup Time                                                            | 5          | —          | ns   |

| 12 | t <sub>NTDIH</sub> | CC | D | TDI Data Hold Time                                                             | 25         | —          | ns   |

| 13 | t <sub>NTMSS</sub> | CC | D | TMS Data Setup Time                                                            | 5          | —          | ns   |

| 14 | t <sub>NTMSH</sub> | CC | D | TMS Data Hold Time                                                             | 25         | —          | ns   |

| 15 | _                  | CC | D | TDO propagation delay from falling<br>edge of TCK                              | _          | 19.5       | ns   |

| 16 | —                  | CC | D | TDO hold time with respect to TCK falling edge (minimum TDO propagation delay) | 5.25       | _          | ns   |

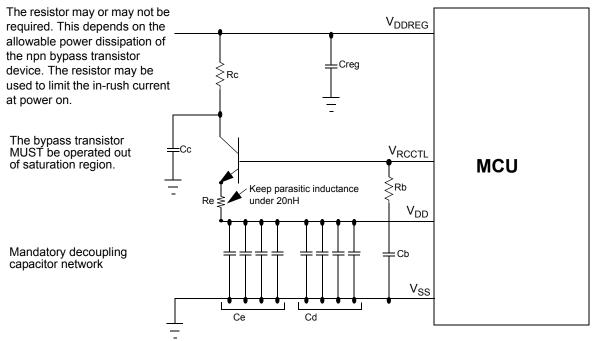

Table 39. Nexus debug port timing<sup>1</sup> (continued)

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V with multi-voltage pads programmed to Low-Swing mode,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

<sup>2</sup> Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

<sup>3</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

<sup>4</sup> This may require setting the MCO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

<sup>5</sup> MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

<sup>6</sup> Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

<sup>7</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

<sup>8</sup> This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 15. Nexus output timing

|                     |                                | Nexus Routing                    | I                           | Max. Operating           |                              |                       |

|---------------------|--------------------------------|----------------------------------|-----------------------------|--------------------------|------------------------------|-----------------------|

| Package             | Nexus Width                    |                                  | MDO[0:3]                    | MDO[4:11]                | CAL_MDO[4:1<br>1]            | Frequency             |

| 176 LQFP<br>208 BGA | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

| 324 BGA             | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

| 496 CSP             | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

|                     | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

|                     |                                | Route to<br>CAL_MDO <sup>7</sup> | Cal Nexus Data<br>Out [0:3] | GPIO                     | Cal Nexus Data<br>Out [4:11] | 40 MHz <sup>3</sup>   |

#### Table 40. Nexus debug port operating frequency

<sup>1</sup> NPC\_PCR[FPM] = 0

<sup>2</sup> NPC\_PCR[NEXCFG] = 0

<sup>3</sup> The Nexus AUX port runs up to 40 MHz. Set NPC\_PCR[MCKO\_DIV] to divide-by-two if the system frequency is greater than 40 MHz.

<sup>4</sup> NPC\_PCR[FPM] = 1

<sup>5</sup> Set the NPC\_PCR[MCKO\_DIV] to divide by two if the system frequency is between 40 MHz and 80 MHz inclusive. Set the NPC\_PCR[MCKO\_DIV] to divide by four if the system frequency is greater than 80 MHz.

<sup>6</sup> Pad restrictions limit the Maximum Operation Frequency in these configurations

<sup>7</sup> NPC\_PCR[NEXCFG] = 1

| "  |                  |                                                     | ~ |                                                                                                                                        | 66 MHz ( | ext. bus) <sup>2</sup> | l lucit | Netze |  |

|----|------------------|-----------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|---------|-------|--|

| #  | Symb             | bol C                                               |   | Characteristic                                                                                                                         | Min      | Max                    | Unit    | Notes |  |

| 6  | t <sub>cov</sub> | COV CC E                                            |   | CLKOUT Posedge to Output Signal Valid<br>(Output Delay)<br>ADDR[8:31]<br>CS[0:3]<br>DATA[0:31]<br>OE<br>RD_WR<br>TS<br>WE[0:3]/BE[0:3] | _        | 9                      | ns      |       |  |

| 7  | t <sub>CIS</sub> | СС                                                  | D | Input Signal Valid to CLKOUT Posedge<br>(Setup Time)<br>DATA[0:31]                                                                     | 6.0      |                        | ns      |       |  |

| 8  | t <sub>CIH</sub> | CC                                                  | D | CLKOUT Posedge to Input Signal Invalid<br>(Hold Time)<br>DATA[0:31]                                                                    | 1.0      | _                      | ns      |       |  |

| 9  | t <sub>APW</sub> | CC                                                  | D | ALE Pulse Width <sup>4</sup>                                                                                                           | 6.5      | —                      | ns      |       |  |

| 10 | t <sub>AAI</sub> | AI CC D ALE Negated to Address Invalid <sup>4</sup> |   | 1.5 <sup>5</sup>                                                                                                                       |          | ns                     |         |       |  |

### Table 43. External bus interface (EBI) and calibration bus operation timing <sup>1</sup> (continued)

<sup>1</sup> External Bus and Calibration bus timing specified at  $f_{SYS}$  = 150 MHz and 100 MHz,  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDE}$  = 3 V to 3.6 V (unless stated otherwise),  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

<sup>2</sup> The external bus is limited to half the speed of the internal bus. The maximum external bus frequency is 66 MHz for 16-bit muxed mode and 33 MHz for non-muxed mode. For The EBI division factor should be set accordingly based on the internal frequency being used.

<sup>3</sup> Refer to Fast Pad timing in Table 35 and Table 36 (different values for 1.8 V vs. 3.3 V).

<sup>4</sup> Measured at 50% of ALE.

<sup>5</sup> When CAL\_TS pad is used for CAL\_ALE function the hold time is 1 ns instead of 1.5 ns.

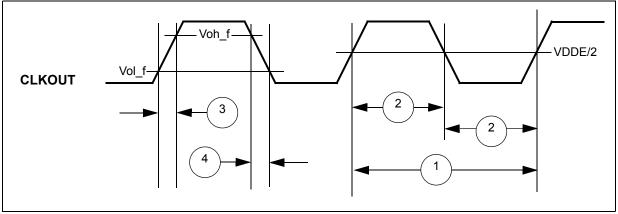

Figure 18. CLKOUT timing

| #  | Syml             | bol | С                           | Characteristic                               | Condition                    | Min. | Max. | Unit |

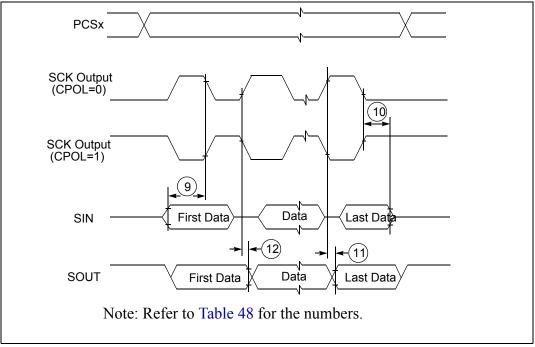

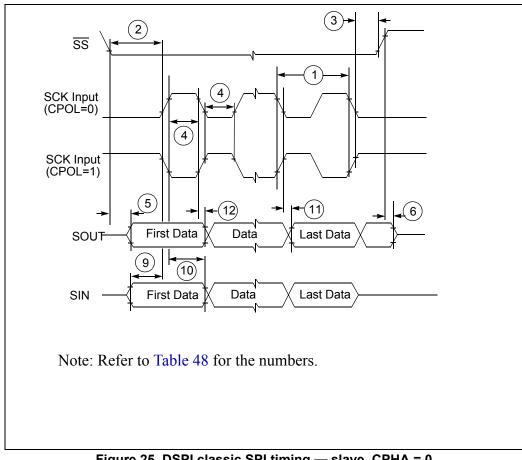

|----|------------------|-----|-----------------------------|----------------------------------------------|------------------------------|------|------|------|

| 9  |                  |     |                             | Data                                         | Setup Time for Inputs        |      |      |      |

|    |                  |     | D                           | Master (MTFE = 0)                            | V <sub>DDEH</sub> =4.5–5.5 V | 20   |      | ns   |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | 23.5 | _    |      |

|    |                  |     | D                           | Slave                                        |                              | 2    | _    |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = $0$ ) <sup>12</sup> |                              | 8    | _    |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 1)                  | V <sub>DDEH</sub> =4.5–5.5 V | 20   | _    |      |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | 23.5 | _    |      |

| 10 | t <sub>HI</sub>  | СС  |                             | Data                                         | Hold Time for Inputs         |      |      |      |

|    |                  |     | D                           | Master (MTFE = 0)                            |                              | -4   |      | ns   |

|    |                  |     | D                           | Slave                                        |                              | 7    | _    |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = $0$ ) <sup>12</sup> |                              | 21   | _    |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 1)                  |                              | -4   | _    |      |

| 11 | t <sub>suo</sub> | CC  | Data Valid (after SCK edge) |                                              |                              |      |      |      |

|    |                  |     | D                           | Master (MTFE = 0)                            | V <sub>DDEH</sub> =4.5–5.5 V | _    | 5    | ns   |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | _    | 6.3  |      |

|    |                  |     | D                           | Slave                                        | V <sub>DDEH</sub> =4.5–5.5 V | _    | 25   |      |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | _    | 27   |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 0)                  |                              | _    | 21   |      |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 1)                  | V <sub>DDEH</sub> =4.5–5.5 V | _    | 5    |      |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | _    | 6.3  |      |

| 12 | t <sub>HO</sub>  | CC  |                             | Data H                                       | lold Time for Outputs        |      |      |      |

|    |                  |     | D                           | Master (MTFE = 0)                            | V <sub>DDEH</sub> =4.5–5.5 V | -5   |      | ns   |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3 –3.6 V  | -7.5 | _    | 1    |

|    |                  |     | D                           | Slave                                        |                              | 5.5  | _    | 1    |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 0)                  |                              | 3    | —    | 1    |

|    |                  |     | D                           | Master (MTFE = 1, CPHA = 1)                  | V <sub>DDEH</sub> =4.5–5.5 V | -5   |      | 1    |

|    |                  |     | D                           |                                              | V <sub>DDEH</sub> =3–3.6 V   | -7.5 | —    | 1    |

| Table 48. | DSPI | timing <sup>1,2</sup> | (continued) |

|-----------|------|-----------------------|-------------|

|-----------|------|-----------------------|-------------|

<sup>1</sup> All DSPI timing specifications use the fastest slew rate (SRC = 0b11) on medium-speed pads. DSPI signals using slow pads have an additional delay based on the slew rate. DSPI timing is specified at  $V_{DDEH}$  = 3 to 3.6 V and  $V_{DDEH}$  = 4.5 to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 50 pF with SRC = 0b11.

<sup>2</sup> Data is verified at  $f_{SYS}$  = 102 MHz and 153 MHz (100 MHz and 150 MHz + 2% frequency modulation).

<sup>3</sup> The minimum DSPI Cycle Time restricts the baud rate selection for given system clock rate. These numbers are calculated based on two MPC5644A devices communicating over a DSPI link.

Figure 24. DSPI classic SPI timing — master, CPHA = 1

Figure 25. DSPI classic SPI timing — slave, CPHA = 0

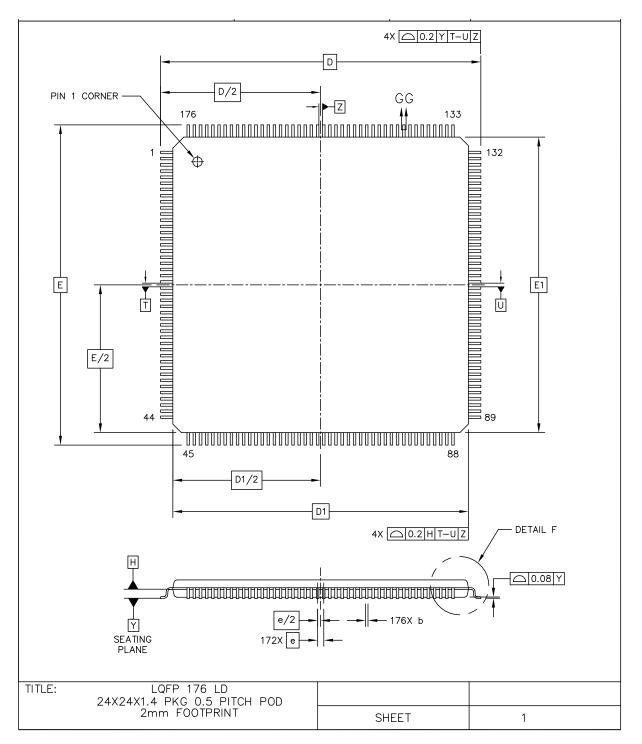

# 4 Packages

## 4.1 Package mechanical data

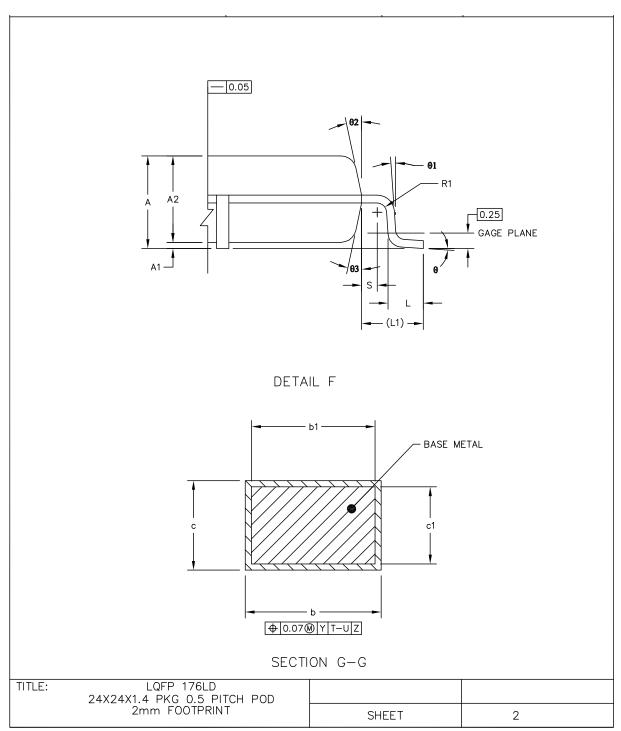

### 4.1.1 176 LQFP

Figure 33. 176 LQFP package mechanical drawing (part 1)

Figure 34. 176 LQFP package mechanical drawing (part 2)

|                                                                                                                                                                                                                                                       | MECHANICAL     | L OUTLINES                   | DOCUMENT NO: 98ASS23840W |        |   |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|--------------------------|--------|---|--|--|--|--|

|                                                                                                                                                                                                                                                       |                | NARY                         | PAGE:                    | 1158   |   |  |  |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRCTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE   | THIS DRAWING                 | REV:                     | D      |   |  |  |  |  |

| NOTES:<br>1. ALL DIMENSIONS IN MILLIME<br>2. DIMENSIONING AND TOLERAI<br>3. MAXIMUM SOLDER BALL DIA                                                                                                                                                   | NCING PER ASME |                              | ATUM A.                  |        |   |  |  |  |  |

| 4. DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.                                                                                                                                                             |                |                              |                          |        |   |  |  |  |  |

| OF PACKAGE.                                                                                                                                                                                                                                           |                |                              |                          |        |   |  |  |  |  |

| TITLE: PBGA, 324                                                                                                                                                                                                                                      | 1/0,           | CASE NUMBER: 1               | 158-03                   | -03    |   |  |  |  |  |

| 23 X 23 P                                                                                                                                                                                                                                             | KG,            | STANDARD: JEDEC MS-034 AAJ-1 |                          |        |   |  |  |  |  |

| 1 MM PITCH (C                                                                                                                                                                                                                                         | MPAC)          | PACKAGE CODE:                | 5241                     | SHEET: | 2 |  |  |  |  |

Figure 39. 324 BGA package mechanical drawing (part 2)