Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2331-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| in Bu  | Buffer                                                                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ре Ту  | Type Description                                                                                                                                             |

|        | PORTB is a bidirectional I/O port. PORTB can be softw<br>programmed for internal weak pull-ups on all inputs.                                                |

|        | TTL Digital I/O.<br>TTL PWM Output 0.                                                                                                                        |

|        | TTL Digital I/O.<br>TTL PWM Output 1.                                                                                                                        |

|        | TTL Digital I/O.<br>TTL PWM Output 2.                                                                                                                        |

| -      | TTL Digital I/O.<br>TTL PWM Output 3.                                                                                                                        |

| T      | TTL Digital I/O.<br>TTL Interrupt-on-change pin.<br>TTL PWM Output 5.                                                                                        |

| T<br>T | <ul> <li>TTL Digital I/O.</li> <li>TTL Interrupt-on-change pin.</li> <li>TTL PWM Output 4.</li> <li>ST Single-Supply ICSP™ Programming entry pin.</li> </ul> |

| Τ-     | TTL       Digital I/O.         TTL       Interrupt-on-change pin.         ST       In-Circuit Debugger and ICSP programming clock p                          |

| T      | TTLDigital I/O.TTLInterrupt-on-change pin.STIn-Circuit Debugger and ICSP programming data pi                                                                 |

|        | 0                                                                                                                                                            |

| TABLE 1-3: | PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------------|

|            |                                                     |

ST = Schmitt Trigger input with CMOS levels 0 = Output

Ρ = Power

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL; RC7 is the alternate pin for SDO.

2: RD4 is the alternate pin for FLTA.

3: RD5 is the alternate pin for PWM4.

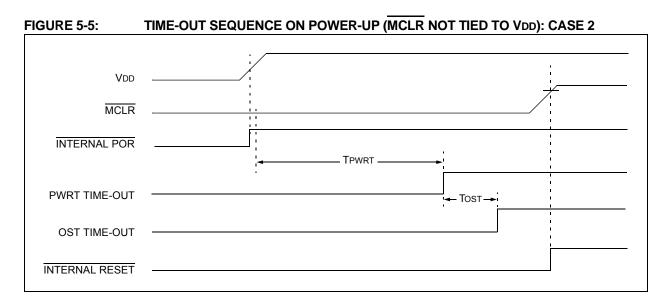

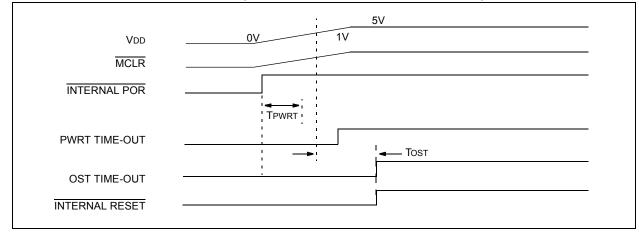

### FIGURE 5-6: SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 6.7.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contain FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

| U-0           | U-0         | U-0                                 | R/W-0            | R/W-0             | R/W-0                        | R/W-0           | R/W-0          |

|---------------|-------------|-------------------------------------|------------------|-------------------|------------------------------|-----------------|----------------|

| _             | _           | _                                   | PTIF             | IC3DRIF           | IC2QEIF                      | IC1IF           | TMR5IF         |

| bit 7         |             |                                     |                  |                   |                              |                 | bit (          |

|               |             |                                     |                  |                   |                              |                 |                |

| Legend:       |             |                                     |                  |                   |                              |                 |                |

| R = Reada     |             | W = Writable                        |                  | •                 | nented bit, read             |                 |                |

| -n = Value    | at POR      | '1' = Bit is set                    |                  | '0' = Bit is clea | ared                         | x = Bit is unk  | nown           |

| bit 7-5       | Unimpleme   | nted: Read as '                     | 0'               |                   |                              |                 |                |

| bit 4         | •           | Time Base Inter                     |                  |                   |                              |                 |                |

|               |             | me base match                       | •                | n the PTPER re    | egisters. Interru            | pt is issued a  | ccording to th |

|               | postsca     | ler settings. PTI                   | F must be clea   | ared in software  |                              |                 | 0              |

|               | 0 = PWM tir | ne base has no                      | t matched the    | value in the PTI  | PER registers                |                 |                |

| bit 3         | IC3DRIF: IC | 3 Interrupt Flag                    | Direction Cha    | nge Interrupt Fla | ag bit                       |                 |                |

|               |             | (CAP3CON<3:                         |                  |                   |                              |                 |                |

|               |             | alue was captui<br>apture has not o |                  | ve edge on CAF    | <sup>2</sup> 3 input (must t | be cleared in s | oftware)       |

|               |             | apture nas not (<br>1 (QEIM<2:0>):  | Julieu           |                   |                              |                 |                |

|               |             | n of rotation has                   | s changed (mu    | st be cleared in  | software)                    |                 |                |

|               |             | n of rotation has                   |                  |                   | ,                            |                 |                |

| bit 2         | IC2QEIF: IC | 2 Interrupt Flag                    | /QEI Interrupt   | Flag bit          |                              |                 |                |

|               |             | (CAP2CON<3:                         |                  |                   |                              |                 |                |

|               |             | alue was captur<br>apture has not o |                  | ve edge on CAF    | 2 input (must t              | be cleared in s | oftware)       |

|               |             | <u>I (QEIM&lt;2:0&gt;):</u>         |                  |                   |                              |                 |                |

|               |             | I position count                    |                  |                   |                              |                 |                |

|               |             | d. Depends on t<br>I position count |                  |                   |                              |                 |                |

|               | detected    |                                     |                  |                   |                              |                 |                |

| bit 1         | IC1 Enabled | (CAP1CON<3:                         | 0>):             |                   |                              |                 |                |

|               | 1 = TMR5 v  | alue was captu                      | red by the activ | ve edge on CAF    | P1 input (must b             | e cleared in s  | oftware)       |

|               |             | apture has not                      |                  |                   |                              |                 |                |

|               |             | <u>(QEIM&lt;2:0&gt;), ∖</u>         |                  |                   |                              |                 |                |

|               |             | value was captu<br>be set in CAP1   |                  |                   |                              |                 | out). CAP1REI  |

|               |             | value was not c                     |                  |                   |                              | are.            |                |

| <b>h</b> :+ 0 | TMR5IF: Tin |                                     |                  |                   | - 3-                         |                 |                |

| bit 0         |             |                                     |                  |                   |                              |                 |                |

| DIEU          |             | time base matcl                     | -                | alue (must be cl  | eared in softwa              | are)            |                |

### REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

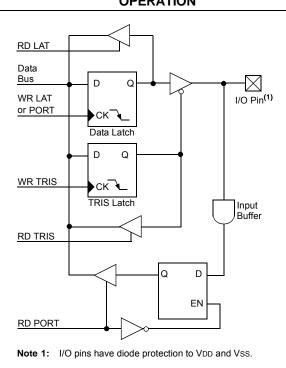

## 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port without the interfaces to other peripherals is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

### 11.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA<4:2> pins are multiplexed with three input capture pins and Quadrature Encoder Interface pins. Pins, RA6 and RA7, are multiplexed with the main oscillator pins. They are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see Section 23.1 "Configuration Bits" for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D Converter inputs is selected by clearing/setting the control bits in the ANSEL0 and ANSEL1 registers.

| Note 1: | On   | а   | Powe   | er-on | Rese    | et, R/  | ٩<5:( | 0> are           |

|---------|------|-----|--------|-------|---------|---------|-------|------------------|

|         | conf | īgu | red as | analo | og inpi | uts and | d rea | <b>d as</b> '0'. |

| 2:      |      |     |        |       |         | ,       | on    | 40-pin           |

|         | devi | ice | s (PIC | 18F4  | 331/4   | 431).   |       |                  |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| ł | EXAMPL | E 11-1: | INITIALIZING PORTA      |

|---|--------|---------|-------------------------|

|   | CLRF   | PORTA   | ; Initialize PORTA by   |

|   |        |         | ; clearing output       |

|   |        |         | ; data latches          |

|   | CLRF   | LATA    | ; Alternate method      |

|   |        |         | ; to clear output       |

|   |        |         | ; data latches          |

|   | MOVLW  | 0x3F    | ; Configure A/D         |

|   | MOVWF  | ANSEL0  | ; for digital inputs    |

|   | MOVLW  | 0xCF    | ; Value used to         |

|   |        |         | ; initialize data       |

|   |        |         | ; direction             |

|   | MOVWF  | TRISA   | ; Set RA<3:0> as inputs |

|   |        |         | ; RA<5:4> as outputs    |

When in Counter mode, the counter must be configured as the synchronous counter only (T5SYNC = 0). When configured in Asynchronous mode, the IC module will not work properly.

- Note 1: Input capture prescalers are reset (cleared) when the input capture module is disabled (CAPxM = 0000).

- 2: When the Input Capture mode is changed, without first disabling the module and entering the new Input Capture mode, a false interrupt (or Special Event Trigger on IC1) may be generated. The user should either: (1) disable the input capture before entering another mode, or (2) disable IC interrupts to avoid false interrupts during IC mode changes.

- **3:** During IC mode changes, the prescaler count will not be cleared, therefore, the first capture in the new IC mode may be from the non-zero prescaler.

EDGE CAPTURE MODE TIMING

### 17.1.1 EDGE CAPTURE MODE

In this mode, the value of the time base is captured either on every rising edge, every falling edge, every 4th rising edge, or every 16th rising edge. The edge present on the input capture pin (CAP1, CAP2 or CAP3) is sampled by the synchronizing latch. The signal is used to load the Input Capture Buffer (ICxBUF register) on the following Q1 clock (see Figure 17-4). Consequently, Timer5 is either reset to '0' (Q1 immediately following the capture event) or left free running, depending on the setting of the Capture Reset Enable bit, CAPxREN, in the CAPxCON register.

Note: On the first capture edge following the setting of the Input Capture mode (i.e., MOVWF CAP1CON), Timer5 contents are always captured into the corresponding Input Capture Buffer (i.e., CAPxBUF). Timer5 can optionally be reset; however, this is dependent on the setting of the Capture Reset Enable bit, CAPxREN (see Figure 17-4).

| 090                                                  |              |               | edezledada<br>VVVVV |             |             |           |           | i ci i i | 14 1 1 1                   |              |                |

|------------------------------------------------------|--------------|---------------|---------------------|-------------|-------------|-----------|-----------|----------|----------------------------|--------------|----------------|

| GMR6 <sup>(1)</sup>                                  | X            | 0013          | Q034X               | 0015        | ()          |           | QQQQ      |          | 10 x 000                   |              | 0062           |

| 04F1 Pin <sup>(2)</sup>                              |              | 2<br>2<br>2   |                     | ,<br>,      | ٦           | 3<br>     |           |          |                            |              |                |

| ]AP1EUF <sup>(3)</sup>                               |              | ABC           | 33                  |             |             | 0016      |           |          |                            |              | 9002<br>3015 S |

| MRC Reset <sup>(4)</sup><br>natruction <sub>MO</sub> | 26F CAP1COR) |               |                     |             | ••••••      | i<br>SCF  | CAPICON   | CVARIE:  | 227X                       |              | - COCLOP N     |

| inecution Mot                                        |              | sus time br   | ase innet tr        | ste input o | splure; pre |           |           |          | ····, <sup>\$</sup> ,····· | <br>21 ristr | ig edi         |

|                                                      |              | n Maharan Man | ntimo mara          | (CAP138<    | 3rd≫ ∝ 63   | भारत स्वर | h the fim | a hasa   | reset ura                  | vn edc       | e cas          |

3: TRRS value is talched by CAP1BUF on Yoy. In the event that a write to TMRS coincides with an input casture event, the write will always take precedence. All input Capture Buffers, CAP1BUF, CAP2BUF and CAP3BUF, are updated with the incremented value of the time base on the next Yoy clock edge when the capture event takes place (see Note 4 when Reset occurs).

4: TMPS Reset is normally an asynchronous Reset signal to TMR5. When used with the input capture, it is active immediately after the time base value is captured.

5: TMP5 Reset pulse is disabled by clearing the CAPTREM bit (e.g., BOF CAPTCON, CAPTREM).

**FIGURE 17-4:**

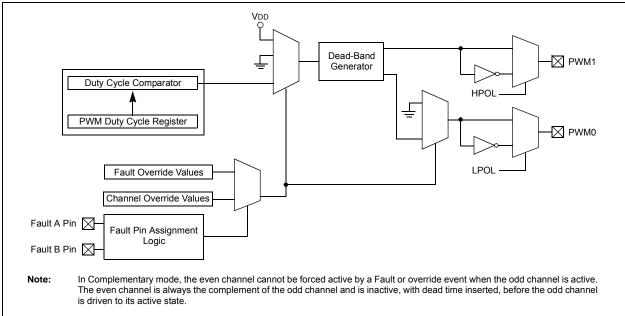

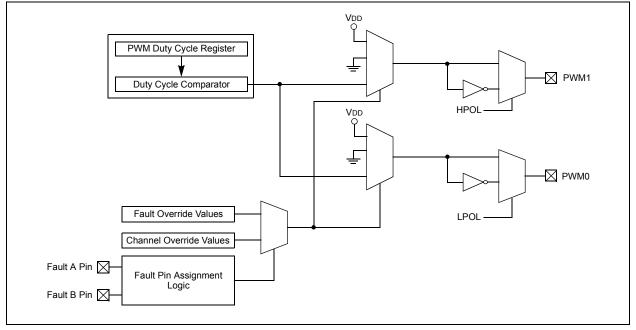

This module contains four duty cycle generators, numbered 0 through 3. The module has eight PWM output pins, numbered 0 through 7. The eight PWM outputs are grouped into output pairs of even and odd numbered outputs. In Complementary modes, the even PWM pins must always be the complement of the corresponding odd PWM pin. For example, PWM0 will be the complement of PWM1, PWM2 will be the complement of PWM3 and so on. The dead-time generator inserts an OFF period called "dead time" between the going OFF of one pin to the going ON of the complementary pin of the paired pins. This is to prevent damage to the power switching devices that will be connected to the PWM output pins.

The time base for the PWM module is provided by its own 12-bit timer, which also incorporates selectable prescaler and postscaler options.

<sup>© 2010</sup> Microchip Technology Inc.

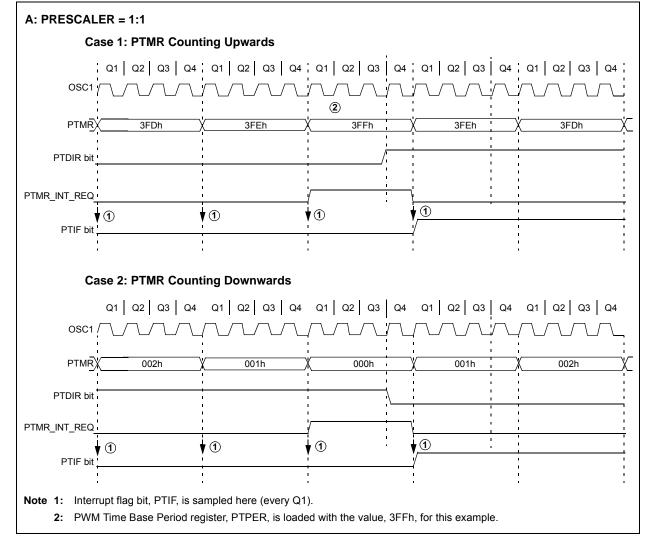

#### 18.4.4 INTERRUPTS IN DOUBLE UPDATE MODE

This mode is available in Continuous Up/Down Count mode. In the Double Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero and each time the PTMR matches with PTPER register. Figure 18-8 shows the interrupts in Continuous Up/Down Count mode with double updates.

The Double Update mode provides two additional functions to the user in Center-Aligned mode.

- The control loop bandwidth is doubled because the PWM duty cycles can be updated twice per period.

- Asymmetrical center-aligned PWM waveforms can be generated, which are useful for minimizing output waveform distortion in certain motor control applications.

Note: Do not change the PTMOD bits while PTEN is active; it will yield unexpected results. To change the PWM Timer mode of operation, first clear the PTEN bit, load the PTMOD bits with the required data and then set PTEN.

## FIGURE 18-8: PWM TIME BASE INTERRUPT, CONTINUOUS UP/DOWN COUNT MODE WITH DOUBLE UPDATES

## 18.12.3 PWM OUTPUTS WHILE IN FAULT CONDITION

While in the Fault state (i.e., one or both FLTA and FLTB inputs are active), the PWM output signals are driven into their inactive states. The selection of which PWM outputs are deactivated (while in the Fault state) is determined by the FLTCON bit in the FLTCONFIG register as follows:

- FLTCON = 1: When FLTA or FLTB is asserted, the PWM outputs (i.e., PWM<7:0>) are driven into their inactive state.

- FLTCON = 0: When FLTA or FLTB is asserted, only PWM<5:0> outputs are driven inactive, leaving PWM<7:6> activated.

- Note: Disabling only three PWM channels and leaving one PWM channel enabled when in the Fault state, allows the flexibility to have at least one PWM channel enabled. None of the PWM outputs can be enabled (driven with the PWM Duty Cycle registers) while FLTCON = 1 and the Fault condition is present.

### 18.12.4 PWM OUTPUTS IN DEBUG MODE

The BRFEN bit in the FLTCONFIG register controls the simulation of a Fault condition, when a breakpoint is hit, while debugging the application using an In-Circuit Emulator (ICE) or an In-Circuit Debugger (ICD). Setting the BRFEN to high, enables the Fault condition on breakpoint, thus driving the PWM outputs to the inactive state. This is done to avoid any continuous keeping of status on the PWM pin, which may result in damage of the power devices connected to the PWM outputs.

If BRFEN = 0, the Fault condition on breakpoint is disabled.

Note: It is highly recommended to enable the Fault condition on breakpoint if a debugging tool is used while developing the firmware and high-power circuitry. When the device is ready to program after debugging the firmware, the BRFEN bit can be disabled.

| Name                    | Bit 7                                             | Bit 6                                               | Bit 5                  | Bit 4                 | Bit 3                       | Bit 2        | Bit 1         | Bit 0  | Reset<br>Values<br>on Page: |  |

|-------------------------|---------------------------------------------------|-----------------------------------------------------|------------------------|-----------------------|-----------------------------|--------------|---------------|--------|-----------------------------|--|

| INTCON                  | GIE/GIEH                                          | PEIE/GIEL                                           | TMR0IE                 | INT0IE                | RBIE                        | TMR0IF       | INT0IF        | RBIF   | 54                          |  |

| IPR3                    | _                                                 | _                                                   | _                      | PTIP                  | IC3DRIP                     | IC2QEIP      | IC1IP         | TMR5IP | 56                          |  |

| PIE3                    | _                                                 | _                                                   | _                      | PTIE                  | IC3DRIE                     | IC2QEIE      | IC1IE         | TMR5IE | 56                          |  |

| PIR3                    | —                                                 | _                                                   | _                      | PTIF                  | IC3DRIF                     | IC2QEIF      | IC1IF         | TMR5IF | 56                          |  |

| PTCON0                  | PTOPS3                                            | PTOPS2                                              | PTOPS1                 | PTOPS0                | PTCKPS1                     | PTCKPS0      | PTMOD1        | PTMOD0 | 58                          |  |

| PTCON1                  | PTEN                                              | PTDIR                                               | _                      | _                     | _                           | _            | _             | _      | 58                          |  |

| PTMRL <sup>(1)</sup>    | PWM Time                                          | Base Registe                                        | er (lower 8 bits)      |                       |                             |              |               |        | 58                          |  |

| PTMRH <sup>(1)</sup>    |                                                   | UN                                                  | USED                   |                       | PWM Time                    | Base Registe | er (upper 4 b | oits)  | 58                          |  |

| PTPERL <sup>(1)</sup>   | PWM Time                                          | Base Period                                         | Register (lowe         | r 8 bits)             |                             |              |               |        | 58                          |  |

| PTPERH <sup>(1)</sup>   |                                                   | UNUSED PWM Time Base Period Register (upper 4 bits) |                        |                       |                             |              |               |        |                             |  |

| SEVTCMPL <sup>(1)</sup> | PWM Special Event Compare Register (lower 8 bits) |                                                     |                        |                       |                             |              |               |        |                             |  |

| SEVTCMPH <sup>(1)</sup> |                                                   | UN                                                  | USED                   |                       | PWM Specia<br>(upper 4 bits | 58           |               |        |                             |  |

| PWMCON0                 | —                                                 | PWMEN2                                              | PWMEN1                 | PWMEN0                | PMOD3 <sup>(2)</sup>        | PMOD2        | PMOD1         | PMOD0  | 58                          |  |

| PWMCON1                 | SEVOPS3                                           | SEVOPS2                                             | SEVOPS1                | SEVOPS0               | SEVTDIR                     | —            | UDIS          | OSYNC  | 58                          |  |

| DTCON                   | DTPS1                                             | DTPS0                                               | DT5                    | DT4                   | DT3                         | DT2          | DT1           | DT0    | 58                          |  |

| FLTCONFIG               | BRFEN                                             | FLTBS <sup>(2)</sup>                                | FLTBMOD <sup>(2)</sup> | FLTBEN <sup>(2)</sup> | FLTCON                      | FLTAS        | FLTAMOD       | FLTAEN | 58                          |  |

| OVDCOND                 | POVD7 <sup>(2)</sup>                              | POVD6 <sup>(2)</sup>                                | POVD5                  | POVD4                 | POVD3                       | POVD2        | POVD1         | POVD0  | 58                          |  |

| OVDCONS                 | POUT7 <sup>(2)</sup>                              | POUT6 <sup>(2)</sup>                                | POUT5                  | POUT4                 | POUT3                       | POUT2        | POUT1         | POUT0  | 58                          |  |

| PDC0L <sup>(1)</sup>    | PWM Duty                                          | Cycle #0L Re                                        | gister (lower 8        | bits)                 |                             |              |               |        | 58                          |  |

| PDC0H <sup>(1)</sup>    | UNU                                               | ISED                                                | PWM Duty Cy            | /cle #0H Regi         | ster (upper 6               | bits)        |               |        | 58                          |  |

| PDC1L <sup>(1)</sup>    | PWM Duty                                          | Cycle #1L reo                                       | gister (lower 8 l      | bits)                 |                             |              |               |        | 58                          |  |

| PDC1H <sup>(1)</sup>    | UNU                                               | ISED                                                | PWM Duty Cy            | /cle #1H Regi         | ster (upper 6               | bits)        |               |        | 58                          |  |

| PDC2L <sup>(1)</sup>    | PWM Duty                                          | Cycle #2L Re                                        | gister (lower 8        | bits)                 |                             |              |               |        | 58                          |  |

| PDC2H <sup>(1)</sup>    | UNU                                               | ISED                                                | PWM Duty Cy            | cle #2H Regi          | ster (upper 6               | bits)        |               |        | 58                          |  |

| PDC3L <sup>(1,2)</sup>  | PWM Duty                                          | Cycle #3L Re                                        | gister (lower 8        | bits)                 |                             |              |               |        | 58                          |  |

| PDC3H <sup>(1,2)</sup>  | UNU                                               | ISED                                                | PWM Duty Cy            | cle #3H Regi          | ster (upper 6               | bits)        |               |        | 58                          |  |

#### TABLE 18-6: REGISTERS ASSOCIATED WITH THE POWER CONTROL PWM MODULE

Legend: — = Unimplemented, read as '0'. Shaded cells are not used with the power control PWM.

Note 1: Double-buffered register pairs. Refer to text for explanation of how these registers are read and written to.

2: Unimplemented in PIC18F2331/2431 devices; maintain these bits clear. Reset values shown are for PIC18F4331/4431 devices.

NOTES:

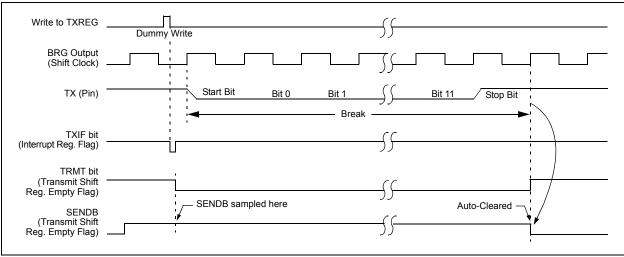

### 20.3.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-9 for the timing of the Break character sequence.

#### 20.3.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to setup the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 20.3.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 of the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 20.3.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit before placing the EUSART in its Sleep mode.

#### FIGURE 20-9: SEND BREAK CHARACTER SEQUENCE

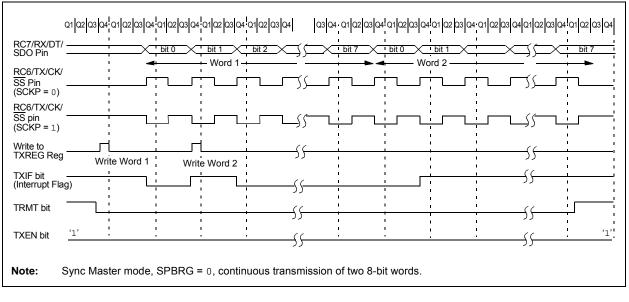

#### 20.4 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/ CK/SS and RC7/RX/DT/SDO I/O pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit, sets the Idle state low. This option is provided to support Microwire devices with this module.

#### 20.4.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-2. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit, TXIF, will be set, regardless of the state of enable bit, TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-10: SYNCHRONOUS TRANSMISSION

### 21.9 A/D Conversions

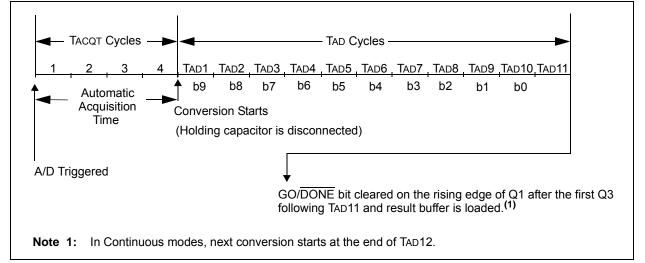

Figure 21-3 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins. The internal A/D RC oscillator must be selected to perform a conversion in Sleep.

Figure 21-4 shows the operation of the A/D Converter after the GO/DONE bit has been set, the ACQT<3:0> bits are set to '010' and a 4 TAD acquisition time is selected before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The resulting buffer location will contain the partially completed A/D conversion sample. This will not set the ADIF flag, therefore, the user must read the buffer location before a conversion sequence overwrites it.

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### FIGURE 21-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, Tacq = 0)

| GO/DONE bit is                       | TAD1        | TAD2    | TAD3   | TAD4    | TAD5    | TAD6      | TAD7    | TAD8     | TAD9    | TAD10  | TAD11   |                 |

|--------------------------------------|-------------|---------|--------|---------|---------|-----------|---------|----------|---------|--------|---------|-----------------|

| set and holding<br>cap is            | <b>♦</b> b9 | b8      | b7     | b6      | b5      | b4        | b3      | b2       | b1      | b0     |         |                 |

| disconnected<br>from analog<br>input | l<br>Conver | sion St | arts   |         |         |           |         |          |         |        |         |                 |

|                                      |             |         |        | GC      | )/DONE  | E bit cle | eared c | on the r | ising e | dge of | Q1 afte | er the first Q3 |

|                                      |             |         |        | 1011    | owing   | IADII     |         |          |         | Jaueu. |         |                 |

| Note 1: Conve                        | ersion tin  | ne is a | minimu | um of 1 | 1 TAD + | 2 TCY     | and a   | maxim    | um of   | 11 Tad | + 6 TC  | Υ.              |

#### FIGURE 21-4: A/D CONVERSION TAD CYCLES (ACQT<3:0> = 0010, TACQ = 4 TAD)

| RRNCF                 | Rotate Ri                                                | ght f (No Ca                                                 | arry)                                                    | SETF                     | Set f                                       |                                                                                                                                                                       |                      |  |  |  |

|-----------------------|----------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|--------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:               |                                                          | RNCF f[,d                                                    |                                                          | Syntax:                  |                                             | TF f[a]                                                                                                                                                               |                      |  |  |  |

| Operands:             | [/dd/df ] 14                                             | _                                                            | [,6]]                                                    | Operands:                | [ <i>label</i> ] SETF f [,a]<br>0 ≤ f ≤ 255 |                                                                                                                                                                       |                      |  |  |  |

| operando.             | d ∈ [0,1]                                                |                                                              |                                                          | operando.                | a ∈ [0,1]                                   |                                                                                                                                                                       |                      |  |  |  |

|                       | a ∈ [0,1]                                                |                                                              |                                                          | Operation:               | $FFh\tof$                                   |                                                                                                                                                                       |                      |  |  |  |

| Operation:            | $(f < n >) \rightarrow de$<br>$(f < 0 >) \rightarrow de$ | est <n 1="" –="">,<br/>est&lt;7&gt;</n>                      |                                                          | Status Affected:         | None                                        |                                                                                                                                                                       |                      |  |  |  |

| Status Affected:      | N, Z                                                     |                                                              |                                                          | Encoding:                | 0110                                        | 100a ff                                                                                                                                                               | ff fffi              |  |  |  |

| Encoding:             | 0100                                                     | 00da ff                                                      | ff ffff                                                  | Description:             |                                             | ts of the speci                                                                                                                                                       | -                    |  |  |  |

| Description:          | one bit to th<br>is placed in                            | nts of register,<br>he right. If 'd' is<br>hW. If 'd' is '1' | 'f', are rotated<br>s '0', the result<br>, the result is |                          | Bank will be<br>BSR value.                  | are set to FFh. If 'a' is '0', the Access<br>Bank will be selected, overriding the<br>BSR value. If 'a' is '1', then the bank wi<br>be selected as per the BSR value. |                      |  |  |  |

|                       |                                                          | k in register, 'f                                            | ". If 'a' is '0', selected, over-                        | Words:                   | 1                                           |                                                                                                                                                                       |                      |  |  |  |

|                       |                                                          | SR value. If 'a                                              |                                                          | Cycles:                  | 1                                           |                                                                                                                                                                       |                      |  |  |  |

|                       | the bank w<br>BSR value                                  | ill be selected                                              | as per the                                               | Q Cycle Activity:        |                                             |                                                                                                                                                                       |                      |  |  |  |

|                       | BSR value.                                               |                                                              | <u> </u>                                                 | Q1                       | Q2                                          | Q3                                                                                                                                                                    | Q4                   |  |  |  |

|                       |                                                          | <ul> <li>registe</li> </ul>                                  |                                                          | Decode                   | Read<br>register 'f'                        | Process<br>Data                                                                                                                                                       | Write<br>register 'f |  |  |  |

| Words:                | 1                                                        |                                                              |                                                          | L                        |                                             |                                                                                                                                                                       |                      |  |  |  |

| Cycles:               | 1                                                        |                                                              |                                                          | Example:                 | SETF F                                      | REG                                                                                                                                                                   |                      |  |  |  |

| Q Cycle Activity:     |                                                          |                                                              |                                                          | Before Instruc           |                                             |                                                                                                                                                                       |                      |  |  |  |

| Q1                    | Q2                                                       | Q3                                                           | Q4                                                       | REG                      |                                             | 5A                                                                                                                                                                    |                      |  |  |  |

| Decode                | Read<br>register 'f'                                     | Process<br>Data                                              | Write to destination                                     | After Instruction<br>REG | on<br>= 0x                                  | FF                                                                                                                                                                    |                      |  |  |  |

| Example 1:            | RRNCF                                                    | REG, 1, 0                                                    |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| Before Instruc<br>REG | tion<br>= 1101 (                                         | 0111                                                         |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| After Instruction     | on                                                       |                                                              |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| REG                   | = 1110 1                                                 | 1011                                                         |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| Example 2:            | RRNCF                                                    | REG, W                                                       |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| Before Instruc        |                                                          |                                                              |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| W<br>REG              | = ?<br>= 1101 (                                          | 0111                                                         |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| After Instructio      | 1101                                                     | ~ -                                                          |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| W                     | = 1110 1                                                 |                                                              |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| REG                   | = 1101 (                                                 | )111                                                         |                                                          |                          |                                             |                                                                                                                                                                       |                      |  |  |  |

| XORWF Exclusive OR W with f                     |                                                                                                                                                                                                                                                                                                                                 |                        |                      |  |  |  |  |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|--|--|--|--|--|--|--|

| Syntax:                                         | [label] >                                                                                                                                                                                                                                                                                                                       | KORWF f[,c             | l [,a]]              |  |  |  |  |  |  |  |

| Operands:                                       | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                             |                        |                      |  |  |  |  |  |  |  |

| Operation:                                      | (W) .XOR.                                                                                                                                                                                                                                                                                                                       | (f) $\rightarrow$ dest |                      |  |  |  |  |  |  |  |

| Status Affected:                                | N, Z                                                                                                                                                                                                                                                                                                                            | N, Z                   |                      |  |  |  |  |  |  |  |

| Encoding:                                       | 0001                                                                                                                                                                                                                                                                                                                            | 10da ff:               | ff ffff              |  |  |  |  |  |  |  |

| Description:                                    | Exclusive OR the contents of W with<br>register, 'f'. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in the register, 'f'. If 'a' is<br>'0', the Access Bank will be selected,<br>overriding the BSR value. If 'a' is '1',<br>then the bank will be selected as per<br>the BSR value. |                        |                      |  |  |  |  |  |  |  |

| Words:                                          | 1                                                                                                                                                                                                                                                                                                                               |                        |                      |  |  |  |  |  |  |  |

| Cycles:                                         | 1                                                                                                                                                                                                                                                                                                                               |                        |                      |  |  |  |  |  |  |  |

| Q Cycle Activity:                               |                                                                                                                                                                                                                                                                                                                                 |                        |                      |  |  |  |  |  |  |  |

| Q1                                              | Q2                                                                                                                                                                                                                                                                                                                              | Q3                     | Q4                   |  |  |  |  |  |  |  |

| Decode                                          | Read<br>register 'f'                                                                                                                                                                                                                                                                                                            | Process<br>Data        | Write to destination |  |  |  |  |  |  |  |

| Example:                                        | XORWF                                                                                                                                                                                                                                                                                                                           | REG                    |                      |  |  |  |  |  |  |  |

| Before Instruct<br>REG<br>W<br>After Instructio | = 0xAF<br>= 0xB5                                                                                                                                                                                                                                                                                                                |                        |                      |  |  |  |  |  |  |  |

| REG<br>W                                        | = 0x1A<br>= 0xB5                                                                                                                                                                                                                                                                                                                |                        |                      |  |  |  |  |  |  |  |

## TABLE 26-8:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                              | Min       | Тур  | Мах       | Units | Conditions                |

|---------------|--------|-------------------------------------------------------------|-----------|------|-----------|-------|---------------------------|

| 30            | TMCL   | MCLR Pulse Width (low)                                      | 2         |      | _         | μS    |                           |

| 31            | Twdt   | Watchdog Timer Time-out Period<br>(no postscaler)           | —         | 4.00 | —         | ms    |                           |

| 32            | Tost   | Oscillation Start-up Timer Period                           | 1024 Tosc | _    | 1024 Tosc | —     | Tosc = OSC1 period        |

| 33            | TPWRT  | Power-up Timer Period                                       | —         | 65.5 | —         | ms    |                           |

| 34            | Tıoz   | I/O High-impedance from MCLR<br>Low or Watchdog Timer Reset | —         | 2    | —         | μS    |                           |

| 35            | TBOR   | Brown-out Reset Pulse Width                                 | 200       |      | _         | μS    | $VDD \le BVDD$ (see D005) |

| 36            | TIRVST | Time for Internal Reference<br>Voltage to become Stable     | —         | 20   | 50        | μS    |                           |

| 37            | Tlvd   | Low-Voltage Detect Pulse Width                              | 200       |      | _         | μS    | $VDD \leq VLVD$           |

| 38            | TCSD   | CPU Start-up Time                                           | —         | 10   | —         | μS    |                           |

| 39            | TIOBST | Time for INTOSC to Stabilize                                | —         | 1    | —         | ms    |                           |

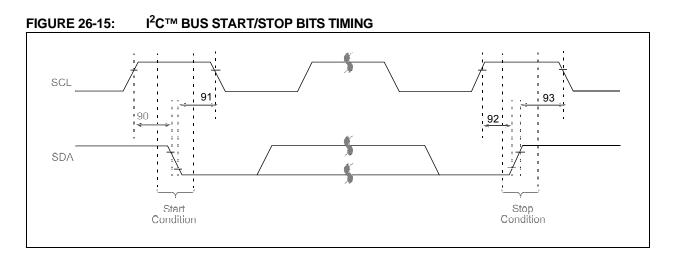

## TABLE 26-15: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic  |              | Min  | Max | Units | Conditions                                            |  |

|---------------|---------|-----------------|--------------|------|-----|-------|-------------------------------------------------------|--|

| 90            | Tsu:sta | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for repeated                            |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition                                       |  |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first clock pulse is generated |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                                                       |  |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                                                       |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                                                       |  |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                                                       |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                                                       |  |

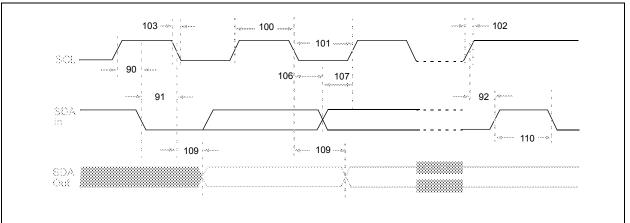

#### FIGURE 26-16: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

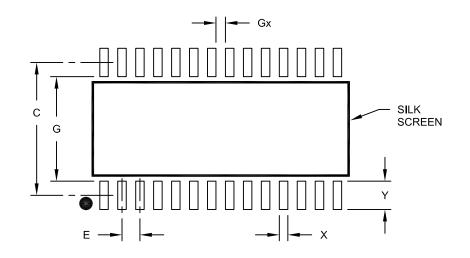

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### **RECOMMENDED LAND PATTERN**

|                          | MILLIMETERS |               |          |      |  |  |

|--------------------------|-------------|---------------|----------|------|--|--|

| Dimension                | MIN         | NOM           | MAX      |      |  |  |

| Contact Pitch            | E           |               | 1.27 BSC |      |  |  |

| Contact Pad Spacing      | С           |               | 9.40     |      |  |  |

| Contact Pad Width (X28)  | X           |               |          | 0.60 |  |  |

| Contact Pad Length (X28) | Y           |               |          | 2.00 |  |  |

| Distance Between Pads    | Gx          | 0.67          |          |      |  |  |

| Distance Between Pads    | G           | 7 <u>.</u> 40 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

### APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN716, "Migrating Designs from PIC16C74A/74B to PIC18F442." The changes discussed, while device-specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available on Microchip's web site: www.Microchip.com.

## APPENDIX F: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN726, "PIC17CXXX to PIC18FXXX Migration."

This Application Note is available on Microchip's web site: www.Microchip.com.