Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2331-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

PIC18LF2431

- PIC18F2331 PIC18LF2331

- PIC18F2431

- PIC18F4331 PIC18LF4331

- PIC18F4431 PIC18LF4431

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price, with the addition of high-endurance enhanced Flash program memory and a high-speed 10-bit A/D Converter. On top of these features, the PIC18F2331/2431/4331/4431 family introduces design enhancements that make these micro-controllers a logical choice for many high-performance, power control and motor control applications. These special peripherals include:

- 14-Bit Resolution Power Control PWM module (PCPWM) with Programmable Dead-Time Insertion

- Motion Feedback Module (MFM), including a 3-Channel Input Capture (IC) module and Quadrature Encoder Interface (QEI)

- High-Speed 10-Bit A/D Converter (HSADC)

The PCPWM can generate up to eight complementary PWM outputs with dead-band time insertion. Overdrive current is detected by off-chip analog comparators or the digital Fault inputs (FLTA, FLTB).

The MFM Quadrature Encoder Interface provides precise rotor position feedback and/or velocity measurement. The MFM 3x input capture or external interrupts can be used to detect the rotor state for electrically commutated motor applications using Hall sensor feedback, such as BLDC motor drives.

PIC18F2331/2431/4331/4431 devices also feature Flash program memory and an internal RC oscillator with built-in LP modes.

## 1.1 New Core Features

#### 1.1.1 nanoWatt Technology

All of the devices in the PIC18F2331/2431/4331/4431 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled, but the peripherals are still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Lower Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer have been reduced by up to 80%, with typical values of 1.1 and 2.1  $\mu$ A, respectively.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2331/2431/4331/4431 family offer nine different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes, with the same pin options as the External Clock modes.

- An internal oscillator block, which provides an 8 MHz clock and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of 6 user-selectable clock frequencies (from 125 kHz to 4 MHz) for a total of 8 clock frequencies.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

#### 6.5.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 6-1 and Table 6-2.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's.

#### TABLE 6-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2331/2431/4331/4431 DEVICES

| Address | Name                    | Address | Name                    | Address | Name    | Address | Name                 | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|---------|---------|----------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H  | F9Fh    | IPR1                 | F7Fh    | PTCON0               |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L  | F9Eh    | PIR1                 | F7Eh    | PTCON1               |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)             | FBDh    | CCP1CON | F9Dh    | PIE1                 | F7Dh    | PTMRL                |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H  | F9Ch    | (2)                  | F7Ch    | PTMRH                |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L  | F9Bh    | OSCTUNE              | F7Bh    | PTPERL               |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON | F9Ah    | ADCON3               | F7Ah    | PTPERH               |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | ANSEL1  | F99h    | ADCHS                | F79h    | PDC0L                |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ANSEL0  | F98h    | (2)                  | F78h    | PDC0H                |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | T5CON   | F97h    | (2)                  | F77h    | PDC1L                |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | QEICON  | F96h    | TRISE <sup>(3)</sup> | F76h    | PDC1H                |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | (2)     | F95h    | TRISD <sup>(3)</sup> | F75h    | PDC2L                |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | (2)     | F94h    | TRISC                | F74h    | PDC2H                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)     | F93h    | TRISB                | F73h    | PDC3L <sup>(3)</sup> |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | (2)     | F92h    | TRISA                | F72h    | PDC3H <sup>(3)</sup> |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | _(2)    | F91h    | PR5H                 | F71h    | SEVTCMPL             |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH  | F90h    | PR5L                 | F70h    | SEVTCMPH             |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG   | F8Fh    | (2)                  | F6Fh    | PWMCON0              |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG   | F8Eh    | (2)                  | F6Eh    | PWMCON1              |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG   | F8Dh    | LATE <sup>(3)</sup>  | F6Dh    | DTCON                |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA   | F8Ch    | LATD <sup>(3)</sup>  | F6Ch    | FLTCONFIG            |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA   | F8Bh    | LATC                 | F6Bh    | OVDCOND              |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | BAUDCON | F8Ah    | LATB                 | F6Ah    | OVDCONS              |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR   | F89h    | LATA                 | F69h    | CAP1BUFH             |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA  | F88h    | TMR5H                | F68h    | CAP1BUFL             |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2  | F87h    | TMR5L                | F67h    | CAP2BUFH             |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSPCON                  | FA6h    | EECON1  | F86h    | (2)                  | F66h    | CAP2BUFL             |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | (2)                     | FA5h    | IPR3    | F85h    | (2)                  | F65h    | CAP3BUFH             |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3    | F84h    | PORTE                | F64h    | CAP3BUFL             |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3    | F83h    | PORTD <sup>(3)</sup> | F63h    | CAP1CON              |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2    | F82h    | PORTC                | F62h    | CAP2CON              |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2    | F81h    | PORTB                | F61h    | CAP3CON              |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2    | F80h    | PORTA                | F60h    | DFLTCON              |

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available on 28-pin devices.

| U-0           | U-0         | U-0                                 | R/W-0            | R/W-0             | R/W-0                        | R/W-0           | R/W-0          |

|---------------|-------------|-------------------------------------|------------------|-------------------|------------------------------|-----------------|----------------|

| _             | _           | _                                   | PTIF             | IC3DRIF           | IC2QEIF                      | IC1IF           | TMR5IF         |

| bit 7         |             |                                     |                  |                   |                              |                 | bit (          |

|               |             |                                     |                  |                   |                              |                 |                |

| Legend:       |             |                                     |                  |                   |                              |                 |                |

| R = Reada     |             | W = Writable                        |                  | •                 | nented bit, read             |                 |                |

| -n = Value    | at POR      | '1' = Bit is set                    |                  | '0' = Bit is clea | ared                         | x = Bit is unk  | nown           |

| bit 7-5       | Unimpleme   | nted: Read as '                     | 0'               |                   |                              |                 |                |

| bit 4         | •           | Time Base Inter                     |                  |                   |                              |                 |                |

|               |             | me base match                       | •                | n the PTPER re    | egisters. Interru            | pt is issued a  | ccording to th |

|               | postsca     | ler settings. PTI                   | F must be clea   | ared in software  |                              |                 | 0              |

|               | 0 = PWM tir | ne base has no                      | t matched the    | value in the PTI  | PER registers                |                 |                |

| bit 3         | IC3DRIF: IC | 3 Interrupt Flag                    | Direction Cha    | nge Interrupt Fla | ag bit                       |                 |                |

|               |             | (CAP3CON<3:                         |                  |                   |                              |                 |                |

|               |             | alue was captui<br>apture has not o |                  | ve edge on CAF    | <sup>2</sup> 3 input (must t | be cleared in s | oftware)       |

|               |             | apture nas not (<br>1 (QEIM<2:0>):  | Julieu           |                   |                              |                 |                |

|               |             | n of rotation has                   | s changed (mu    | st be cleared in  | software)                    |                 |                |

|               |             | n of rotation has                   |                  |                   | ,                            |                 |                |

| bit 2         | IC2QEIF: IC | 2 Interrupt Flag                    | /QEI Interrupt   | Flag bit          |                              |                 |                |

|               |             | (CAP2CON<3:                         |                  |                   |                              |                 |                |

|               |             | alue was captur<br>apture has not o |                  | ve edge on CAF    | 2 input (must t              | be cleared in s | oftware)       |

|               |             | <u>I (QEIM&lt;2:0&gt;):</u>         |                  |                   |                              |                 |                |

|               |             | I position count                    |                  |                   |                              |                 |                |

|               |             | d. Depends on t<br>I position count |                  |                   |                              |                 |                |

|               | detected    |                                     |                  |                   |                              |                 |                |

| bit 1         | IC1 Enabled | (CAP1CON<3:                         | 0>):             |                   |                              |                 |                |

|               | 1 = TMR5 v  | alue was captu                      | red by the activ | ve edge on CAF    | P1 input (must b             | e cleared in s  | oftware)       |

|               |             | apture has not                      |                  |                   |                              |                 |                |

|               |             | <u>(QEIM&lt;2:0&gt;), ∖</u>         |                  |                   |                              |                 |                |

|               |             | value was captu<br>be set in CAP1   |                  |                   |                              |                 | out). CAP1REI  |

|               |             | value was not c                     |                  |                   |                              | are.            |                |

| <b>h</b> :+ 0 | TMR5IF: Tin |                                     |                  |                   | - 3-                         |                 |                |

| bit 0         |             |                                     |                  |                   |                              |                 |                |

| DIEU          |             | time base matcl                     | -                | alue (must be cl  | eared in softwa              | are)            |                |

## REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| Pin           | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                            |

|---------------|---------------------|-----------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/PWM0      | RB0                 | 0               | 0   | DIG         | LATB<0> data output; not affected by analog input.                                                                     |

|               |                     | 1               | I   | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input is enabled.                  |

|               | PWM0                | 0               | 0   | DIG         | PWM Output 0.                                                                                                          |

| RB1/PWM1      | RB1                 | 0               | 0   | DIG         | LATB<1> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<1> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM1                | 0               | 0   | DIG         | PWM Output 1.                                                                                                          |

| RB2/PWM2      | RB2                 | 0               | 0   | DIG         | LATB<2> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<2> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM2                | 0               | 0   | DIG         | PWM Output 2.                                                                                                          |

| RB3/PWM3      | RB3                 | 0               | 0   | DIG         | LATB<3> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<3> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM3                | 0               | 0   | DIG         | PWM Output 3.                                                                                                          |

| RB4/KBI0/PWM5 | RB4                 | 0               | 0   | DIG         | LATB<4> data output; not affected by analog input.                                                                     |

| RB4/KBI0/PWM5 |                     | 1               | Ι   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared. Disabled when analog input is enabled.                     |

|               | KBI0                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PWM5                | 0               | 0   | DIG         | PWM Output 5.                                                                                                          |

| RB5/KBI1/     | RB5                 | 0               | 0   | DIG         | LATB<5> data output.                                                                                                   |

| PWM4/PGM      |                     | 1               | Ι   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI1                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PWM4 <sup>(3)</sup> | 0               | 0   | DIG         | PWM Output 4; takes priority over port data.                                                                           |

|               | PGM <sup>(2)</sup>  | х               | I   | ST          | Single-Supply Programming mode entry (ICSP™). Enabled by LVP Configuration bit; all other pin functions are disabled.  |

| RB6/KBI2/PGC  | RB6                 | 0               | 0   | DIG         | LATB<6> data output.                                                                                                   |

|               |                     | 1               | Ι   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI2                | 1               | I   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PGC                 | x               | Ι   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operation. <sup>(1)</sup>                                        |

| RB7/KBI3/PGD  | RB7                 | 0               | 0   | DIG         | LATB<7> data output.                                                                                                   |

|               |                     | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI3                | 1               | I   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PGD                 | x               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(1)</sup>                                                |

|               |                     | x               | Ι   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(1)</sup>                                                 |

## TABLE 11-3: PORTB I/O SUMMARY

Legend:DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;<br/>x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: All other pin functions are disabled when ICSP or ICD is enabled.

2: Single-Supply Programming must be enabled.

3: RD5 is the alternate pin for PWM4.

NOTES:

### 16.5 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

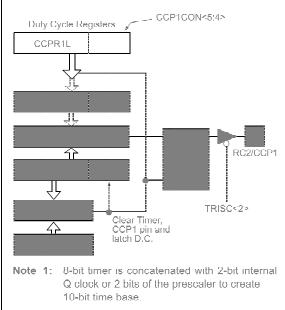

Figure 16-3 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP1 module for PWM operation, see Section 16.5.3 "Setup for PWM Operation".

## FIGURE 16-3: SIMPLIFIED PWM BLOCK DIAGRAM

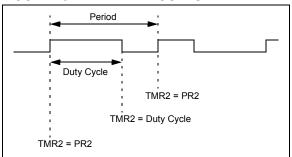

A PWM output (Figure 16-4) has a time base (period) and a time that the output is high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 16.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation:

#### EQUATION 16-1:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 14.0   |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | "Timer2 Module") is not used in the       |  |  |  |  |  |  |  |  |  |

|       | determination of the PWM frequency. The   |  |  |  |  |  |  |  |  |  |

|       | postscaler could be used to have a servo  |  |  |  |  |  |  |  |  |  |

|       | update rate at a different frequency than |  |  |  |  |  |  |  |  |  |

|       | the PWM output.                           |  |  |  |  |  |  |  |  |  |

#### 16.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation:

#### **EQUATION 16-2:**

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

| R/W-0        | R/W-0                                      | R/W-0                | R/W-0           | R/W-0                                               | U-0              | R/W-0           | R/W-0 |

|--------------|--------------------------------------------|----------------------|-----------------|-----------------------------------------------------|------------------|-----------------|-------|

| SEVOPS3      | SEVOPS2                                    | SEVOPS1              | SEVOPS0         | SEVTDIR                                             | —                | UDIS            | OSYNC |

| bit 7        |                                            |                      |                 |                                                     |                  |                 | bit 0 |

| Legend:      |                                            |                      |                 |                                                     |                  |                 |       |

| R = Readab   | le bit                                     | W = Writable I       | bit             | U = Unimplem                                        | nented bit, read | as '0'          |       |

| -n = Value a | t POR                                      | '1' = Bit is set     |                 | '0' = Bit is clea                                   | ared             | x = Bit is unkn | own   |

| bit 7-4      | SEVOPS<3:0<br>0000 = 1:1 P<br>0001 = 1:2 P | ostscale<br>ostscale | n Event mgge    | r Output Postsc                                     |                  |                 |       |

| bit 3        | 1 = A Special                              | ••                   | will occur wher | e Direction bit<br>I the PWM time<br>I the PWM time |                  | •               |       |

| bit 2        | Unimplement                                | ted: Read as '0      | ,               |                                                     |                  |                 |       |

| bit 1        | UDIS: PWM L                                | Jpdate Disable       | bit             |                                                     |                  |                 |       |

|              | •                                          |                      |                 | uffer registers a<br>uffer registers a              |                  |                 |       |

| bit 0        | OSYNC: PWN                                 | / Output Overri      | de Synchroniz   | ation bit                                           |                  |                 |       |

|              |                                            |                      | 0               | ster are synchro<br>ster are asynch                 |                  | WM time base    |       |

#### REGISTER 18-4: PWMCON1: PWM CONTROL REGISTER 1

18.3.1 FREE-RUNNING MODE

In the Free-Running mode, the PWM Time Base registers (PTMRL and PTMRH) will begin counting upwards until the value in the PWM Time Base Period register, PTPER (PTPERL and PTPERH), is matched. The PTMR registers will be reset on the following input clock edge and the time base will continue counting upwards as long as the PTEN bit remains set.

#### 18.3.2 SINGLE-SHOT MODE

In the Single-Shot mode, the PWM time base will begin counting upwards when the PTEN bit is set. When the value in the PTMR register matches the PTPER register, the PTMR register will be reset on the following input clock edge and the PTEN bit will be cleared by the hardware to halt the time base.

#### 18.3.3 CONTINUOUS UP/DOWN COUNT MODES

In Continuous Up/Down Count modes, the PWM time base counts upwards until the value in the PTPER register matches with the PTMR register. On the following input clock edge, the timer counts downwards. The PTDIR bit in the PTCON1 register is read-only and indicates the counting direction. The PTDIR bit is set when the timer counts downwards. Note: Since the PWM compare outputs are driven to the active state when the PWM time base is counting downwards and matches the duty cycle value, the PWM outputs are held inactive during the first half of the first period of the Continuous Up/Down Count mode until PTMR begins to count down from the PTPER value.

### 18.3.4 PWM TIME BASE PRESCALER

The input clock to PTMR (Fosc/4) has prescaler options of 1:1, 1:4, 1:16 or 1:64. These are selected by control bits, PTCKPS<1:0>, in the PTCON0 register. The prescaler counter is cleared when any of the following occurs:

- · Write to the PTMR register

- Write to the PTCON (PTCON0 or PTCON1)

register

- Any device Reset

Note: The PTMR register is not cleared when PTCONx is written.

## 19.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 19.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

Refer to application note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

#### 19.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- · Serial Data Out (SDO)

- · Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON (SSPCON<5:0>) and SSPSTAT<7:6> registers. These control bits allow the following to be specified:

- · Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock rate (Master mode only)

- Slave Select mode (Slave mode only)

| R/W-0        | R/W-0                              | R/W-0                                                                       | R/W-0                                | R/W-0             | R-0              | R-0               | R-x     |

|--------------|------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|-------------------|------------------|-------------------|---------|

| SPEN         | RX9                                | SREN                                                                        | CREN                                 | ADDEN             | FERR             | OERR              | RX9D    |

| bit 7        | •                                  |                                                                             | •                                    | ·                 |                  |                   | bit     |

| Legend:      |                                    |                                                                             |                                      |                   |                  |                   |         |

| R = Readab   | ole bit                            | W = Writable                                                                | bit                                  | U = Unimplem      | nented bit, read | l as '0'          |         |

| -n = Value a | at POR                             | '1' = Bit is set                                                            |                                      | '0' = Bit is clea | ared             | x = Bit is unkn   | own     |

| bit 7        | SPEN: Serial                       | Port Enable bi                                                              | t                                    |                   |                  |                   |         |

|              | 1 = Serial por<br>0 = Serial por   |                                                                             |                                      |                   |                  |                   |         |

| bit 6        | <b>RX9:</b> 9-Bit Re               | ceive Enable b                                                              | bit                                  |                   |                  |                   |         |

|              | 1 = Selects 9<br>0 = Selects 8     | •                                                                           |                                      |                   |                  |                   |         |

| bit 5        | SREN: Single                       | Receive Enab                                                                | ole bit                              |                   |                  |                   |         |

|              | <u>Asynchronous</u><br>Don't care. | <u>s mode</u> :                                                             |                                      |                   |                  |                   |         |

|              | 1 = Enables s<br>0 = Disables      | <u>mode – Maste</u><br>single receive<br>single receive<br>ared after recej |                                      | ete.              |                  |                   |         |

|              |                                    | mode – Slave:                                                               | -                                    |                   |                  |                   |         |

| bit 4        | CREN: Contir                       | nuous Receive                                                               | Enable bit                           |                   |                  |                   |         |

|              | Asynchronous                       |                                                                             |                                      |                   |                  |                   |         |

|              | 1 = Enables r                      |                                                                             |                                      |                   |                  |                   |         |

|              | 0 = Disables<br>Synchronous        |                                                                             |                                      |                   |                  |                   |         |

|              | 1 = Enables                        |                                                                             |                                      | le bit, CREN, is  | cleared (CREI    | N overrides SR    | EN)     |

| bit 3        | ADDEN: Add                         | ress Detect En                                                              | able bit                             |                   |                  |                   |         |

|              | 1 = Enables a<br>0 = Disables      |                                                                             | ion, enables ir<br>tion, all bytes a | nterrupt and load |                  |                   |         |

| bit 2        | FERR: Framir                       | na Error bit                                                                |                                      |                   |                  |                   |         |

|              |                                    | error (can be c                                                             | leared by reac                       | ling RCREGx re    | gister and rece  | eiving next valio | l byte) |

| bit 1        | OERR: Overr                        | 0                                                                           |                                      |                   |                  |                   |         |

|              |                                    | error (can be c                                                             | leared by clea                       | ring bit, CREN)   |                  |                   |         |

| bit 0        |                                    | of Received D                                                               | ata                                  |                   |                  |                   |         |

|              | <u> </u>                           | ddress/data bit                                                             |                                      |                   |                  |                   |         |

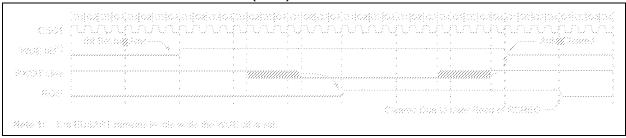

#### 20.3.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line, while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 20-7), and asynchronously if the device is in Sleep mode (Figure 20-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

## 20.3.4.1 Special Considerations Using Auto-Wake-up

Since Auto-Wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character

and cause data or framing errors. To work properly, therefore, the initial characters in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices, or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 20.3.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/ DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set), and the RCIF flag is set, should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### FIGURE 20-7: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

#### FIGURE 20-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

## 21.4 A/D Voltage References

If external voltage references are used instead of the internal AVDD and AVSS sources, the source impedance of the VREF+ and VREF- voltage sources must be considered. During acquisition, currents supplied by these sources are insignificant. However, during conversion, the A/D module sinks and sources current through the reference sources.

In order to maintain the A/D accuracy, the voltage reference source impedances should be kept low to reduce voltage changes. These voltage changes occur as reference currents flow through the reference source impedance.

**Note:** When using external references, the source impedance of the external voltage references must be less than  $75\Omega$  in order to achieve the specified ADC resolution. A higher reference source impedance will increase the ADC offset and gain errors. Resistive voltage dividers will not provide a low enough source impedance. To ensure the best possible ADC performance, external VREF inputs should be buffered with an op amp or other low-impedance circuit.

## 21.5 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time an A/D conversion is triggered.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and the start of conversion. This occurs when the ACQT<3:0> bits (ADCON2<6:3>) remain in their Reset state ('0000'). If desired, the ACQT bits can be set to select a programmable acquisition time for the A/D module. When triggered, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and triggering the A/D. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

### 21.6 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are eight possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

- Internal RC Oscillator/4

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (approximately 416 ns, see parameter A11 for more information).

Table 21-2 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock Sc         | ource (TAD)          | Maximum Device Frequency |                            |  |  |  |

|---------------------|----------------------|--------------------------|----------------------------|--|--|--|

| Operation           | peration ADCS<2:0> P |                          | PIC18LFXX31 <sup>(4)</sup> |  |  |  |

| 2 Tosc              | 000                  | 4.8 MHz                  | 666 kHz                    |  |  |  |

| 4 Tosc              | 100                  | 9.6 MHz                  | 1.33 MHz                   |  |  |  |

| 8 Tosc              | 001                  | 19.2 MHz                 | 2.66 MHz                   |  |  |  |

| 16 Tosc             | 101                  | 38.4 MHz                 | 5.33 MHz                   |  |  |  |

| 32 Tosc             | 010                  | 40.0 MHz                 | 10.65 MHz                  |  |  |  |

| 64 Tosc             | 110                  | 40.0 MHz                 | 21.33 MHz                  |  |  |  |

| RC/4 <sup>(3)</sup> | 011                  | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>    |  |  |  |

| RC <sup>(3)</sup>   | 111                  | 4.0 MHz <sup>(2)</sup>   | 4.0 MHz <sup>(2)</sup>     |  |  |  |

TABLE 21-2: TAD VS. DEVICE OPERATING FREQUENCIES

Note 1: The RC source has a typical TAD time of 2-6  $\mu$ s.

**2:** The RC source has a typical TAD time of 0.5-1.5 μs.

**3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification unless in Single-Shot mode.

4: Low-power devices only.

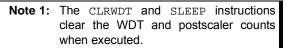

## 23.2 Watchdog Timer (WDT)

For PIC18F2331/2431/4331/4431 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H (see Register 23-3). Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: execute a SLEEP or CLRWDT instruction, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred (see Section 23.4.1 "FSCM and the Watchdog Timer").

Adjustments to the internal oscillator clock period using the OSCTUNE register also affect the period of the WDT by the same factor. For example, if the INTRC period is increased by 3%, then the WDT period is increased by 3%.

#### FIGURE 23-1: WDT BLOCK DIAGRAM

- Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

- 4: If WINEN = 0, then CLRWDT must be executed only when WDTW = 1; otherwise, a device Reset will result.

### 23.2.1 CONTROL REGISTER

Register 23-15 shows the WDTCON register. This is a readable and writable register. The SWDTEN bit allows software to enable or disable the WDT, but only if the Configuration bit has disabled the WDT. The WDTW bit is a read-only bit that indicates when the WDT count is in the fourth quadrant (i.e., when the 8-bit WDT value is b'11000000' or greater).

### TABLE 24-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                   |  |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| a               | RAM access bit:                                                                                                                               |  |  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                   |  |  |  |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                  |  |  |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                           |  |  |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                    |  |  |  |  |  |  |  |

| d               | Destination select bit:                                                                                                                       |  |  |  |  |  |  |  |

|                 | d = 0: store result in WREG<br>d = 1: store result in file register f                                                                         |  |  |  |  |  |  |  |

| J t.            |                                                                                                                                               |  |  |  |  |  |  |  |

| dest            | Destination either the WREG register or the specified register file locations.<br>8-bit register file address (0x00 to 0xFF).                 |  |  |  |  |  |  |  |

| f               |                                                                                                                                               |  |  |  |  |  |  |  |

| fs              | 12-bit register file address (0x000 to 0xFFF). This is the source address.                                                                    |  |  |  |  |  |  |  |

| fd              | 12-bit register file address (0x000 to 0xFFF). This is the destination address.                                                               |  |  |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                     |  |  |  |  |  |  |  |

| label           | Label name.                                                                                                                                   |  |  |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:   |  |  |  |  |  |  |  |

| *               | No Change to register (such as TBLPTR with table reads and writes).                                                                           |  |  |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes).                                                                         |  |  |  |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes).                                                                         |  |  |  |  |  |  |  |

| +*              |                                                                                                                                               |  |  |  |  |  |  |  |

|                 | Pre-Increment register (such as TBLPTR with table reads and writes).                                                                          |  |  |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for Call/Branch and Return instructions. |  |  |  |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                |  |  |  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                 |  |  |  |  |  |  |  |

| s               | Fast Call/Return Mode Select bit:                                                                                                             |  |  |  |  |  |  |  |

| 2               | s = 0: do not update into/from Shadow registers                                                                                               |  |  |  |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                        |  |  |  |  |  |  |  |

| u               | Unused or Unchanged.                                                                                                                          |  |  |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                               |  |  |  |  |  |  |  |

| x               | Don't care ('0' or '1').                                                                                                                      |  |  |  |  |  |  |  |

|                 | The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all                                     |  |  |  |  |  |  |  |

|                 | Microchip software tools.                                                                                                                     |  |  |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                   |  |  |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                            |  |  |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                 |  |  |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                              |  |  |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                     |  |  |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                    |  |  |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                              |  |  |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                             |  |  |  |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                  |  |  |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                               |  |  |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                 |  |  |  |  |  |  |  |

| PD              | Power-Down bit.                                                                                                                               |  |  |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                |  |  |  |  |  |  |  |

| [ ]             | Optional.                                                                                                                                     |  |  |  |  |  |  |  |

| ( )             | Contents.                                                                                                                                     |  |  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                  |  |  |  |  |  |  |  |

| < >             | Register bit field.                                                                                                                           |  |  |  |  |  |  |  |

| E               | In the set of.                                                                                                                                |  |  |  |  |  |  |  |

| italics         | User-defined term (font is Courier New).                                                                                                      |  |  |  |  |  |  |  |

| Mnemonic, |      |                                |        | 16-1 | Bit Instr | uction V | Vord | Status                 |       |

|-----------|------|--------------------------------|--------|------|-----------|----------|------|------------------------|-------|

| Operands  |      | Description                    | Cycles | MSb  |           |          | LSb  | Affected               | Notes |

| CONTROL   | OPER | ATIONS                         |        | •    |           |          |      | ·                      |       |

| BC        | n    | Branch if Carry                | 1 (2)  | 1110 | 0010      | nnnn     | nnnn | None                   |       |

| BN        | n    | Branch if Negative             | 1 (2)  | 1110 | 0110      | nnnn     | nnnn | None                   |       |

| BNC       | n    | Branch if Not Carry            | 1 (2)  | 1110 | 0011      | nnnn     | nnnn | None                   |       |

| BNN       | n    | Branch if Not Negative         | 1 (2)  | 1110 | 0111      | nnnn     | nnnn | None                   |       |

| BNOV      | n    | Branch if Not Overflow         | 1 (2)  | 1110 | 0101      | nnnn     | nnnn | None                   |       |

| BNZ       | n    | Branch if Not Zero             | 2      | 1110 | 0001      | nnnn     | nnnn | None                   |       |

| BOV       | n    | Branch if Overflow             | 1 (2)  | 1110 | 0100      | nnnn     | nnnn | None                   |       |

| BRA       | n    | Branch Unconditionally         | 1 (2)  | 1101 | 0nnn      | nnnn     | nnnn | None                   |       |

| BZ        | n    | Branch if Zero                 | 1 (2)  | 1110 | 0000      | nnnn     | nnnn | None                   |       |

| CALL      | n, s | Call Subroutine 1st word       | 2      | 1110 | 110s      | kkkk     | kkkk | None                   |       |

|           |      | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |                        |       |

| CLRWDT    | _    | Clear Watchdog Timer           | 1      | 0000 | 0000      | 0000     | 0100 | TO, PD                 |       |

| DAW       | —    | Decimal Adjust WREG            | 1      | 0000 | 0000      | 0000     | 0111 | C, DC                  |       |

| GOTO      | n    | Go to Address 1st word         | 2      | 1110 | 1111      | kkkk     | kkkk | None                   |       |

|           |      | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |                        |       |

| NOP       | _    | No Operation                   | 1      | 0000 | 0000      | 0000     | 0000 | None                   |       |

| NOP       | —    | No Operation                   | 1      | 1111 | xxxx      | xxxx     | xxxx | None                   | 4     |

| POP       | _    | Pop Top of Return Stack (TOS)  | 1      | 0000 | 0000      | 0000     | 0110 | None                   |       |

| PUSH      | —    | Push Top of Return Stack (TOS) | 1      | 0000 | 0000      | 0000     | 0101 | None                   |       |

| RCALL     | n    | Relative Call                  | 2      | 1101 | 1nnn      | nnnn     | nnnn | None                   |       |

| RESET     |      | Software Device Reset          | 1      | 0000 | 0000      | 1111     | 1111 | All                    |       |

| RETFIE    | S    | Return from Interrupt Enable   | 2      | 0000 | 0000      | 0001     | 000s | GIE/GIEH,<br>PEIE/GIEL |       |

| RETLW     | k    | Return with Literal in WREG    | 2      | 0000 | 1100      | kkkk     | kkkk | None                   |       |

| RETURN    | S    | Return from Subroutine         | 2      | 0000 | 0000      | 0001     | 001s | None                   |       |

| SLEEP     | _    | Go into Standby mode           | 1      | 0000 | 0000      | 0000     | 0011 | TO, PD                 |       |

### TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**4:** Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| LFS   | R                                   | Load FSR                                                                    | ł                                    |               | MO                                                                                                        | /F                           | Move f                             |                                   |          |            |  |

|-------|-------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------|-----------------------------------|----------|------------|--|

| Synta | ax:                                 | [label] L                                                                   | FSR f,k                              |               | Synta                                                                                                     | ax:                          | [label] M                          | [ <i>label</i> ] MOVF f [,d [,a]] |          |            |  |

| Oper  | ands:                               | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 409 \end{array}$         | 5                                    |               | Oper                                                                                                      | ands:                        | $0 \le f \le 255$<br>$d \in [0,1]$ | d ∈ [0,1]                         |          |            |  |

| Oper  | ation:                              | $k \rightarrow FSRf$                                                        | $k \rightarrow FSRf$                 |               |                                                                                                           | -ti                          | a ∈ [0,1]                          |                                   |          |            |  |

| Statu | s Affected:                         | None                                                                        |                                      |               |                                                                                                           | ation:                       | $f \rightarrow dest$               |                                   |          |            |  |

| Enco  | ding:                               | 1110<br>1111                                                                | 11                                   |               |                                                                                                           | s Affected:<br>ding:         | N, Z                               | 00da                              | ffff     | ffff       |  |

| Desc  | ription:                            |                                                                             | iteral 'k' is loa<br>egister pointeo |               | Desc                                                                                                      | ription:                     | The content<br>to a destina        | •                                 |          |            |  |

| Word  | s:                                  | 2                                                                           |                                      |               |                                                                                                           |                              | status of 'd'                      |                                   | ,        |            |  |

| Cycle | es:                                 | 2                                                                           |                                      |               |                                                                                                           |                              | placed in W<br>placed back         |                                   |          |            |  |

| QC    | ycle Activity:                      |                                                                             |                                      |               |                                                                                                           |                              | can be any                         | where in th                       | ne 256-b | yte bank.  |  |

|       | Q1                                  | Q2                                                                          | Q3                                   | Q4            |                                                                                                           |                              | If 'a' is '0', t                   |                                   |          |            |  |

|       | Decode                              | Read literal  Process  Write    'k' MSB  Data  literal 'k'    MSB to  FSRfH |                                      |               | selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected a<br>per the BSR value. |                              |                                    |                                   |          |            |  |

|       | Decode                              | Read literal                                                                | Process                              | Write literal | Word                                                                                                      | ls:                          | 1                                  |                                   |          |            |  |

|       |                                     | ʻk' LSB                                                                     | Data                                 | 'k' to FSRfL  | Cycle                                                                                                     | es:                          | 1                                  |                                   |          |            |  |

| _     |                                     |                                                                             |                                      |               | QC                                                                                                        | ycle Activity:               |                                    |                                   |          |            |  |

| Exan  |                                     | LFSR 2,                                                                     | 0x3AB                                |               |                                                                                                           | Q1                           | Q2                                 | Q3                                |          | Q4         |  |

|       | After Instruction<br>FSR2H<br>FSR2L | on<br>= 0xi<br>= 0xi                                                        |                                      |               |                                                                                                           | Decode                       | Read<br>register 'f'               | Process<br>Data                   | 6        | Write<br>W |  |

|       |                                     |                                                                             |                                      |               | Exan                                                                                                      | nple:                        | MOVF RI                            | EG, W                             |          |            |  |

|       |                                     |                                                                             |                                      |               |                                                                                                           | Before Instruc<br>REG<br>W   | tion<br>= 0x2<br>= 0x1             |                                   |          |            |  |

|       |                                     |                                                                             |                                      |               |                                                                                                           | After Instructio<br>REG<br>W | on<br>= 0x2<br>= 0x2               |                                   |          |            |  |

| RETF               | E                                         | Return fro                                                                                                             | om Interrupt                                                                                                                                                                             | :                                                                                                          |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Syntax             | :                                         | [label] R                                                                                                              | ETFIE [s]                                                                                                                                                                                |                                                                                                            |

| Operar             | nds:                                      | $s \in [0,1]$                                                                                                          |                                                                                                                                                                                          |                                                                                                            |