Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT          |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2331t-e-sog |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 28/40/44-Pin Enhanced Flash Microcontrollers with nanoWatt Technology, High-Performance PWM and A/D

#### **14-Bit Power Control PWM Module:**

- · Up to 4 Channels with Complementary Outputs

- Edge or Center-Aligned Operation

- Flexible Dead-Band Generator

- Hardware Fault Protection Inputs

- Simultaneous Update of Duty Cycle and Period:

- Flexible Special Event Trigger output

### **Motion Feedback Module:**

- Three Independent Input Capture Channels:

- Flexible operating modes for period and pulse-width measurement

- Special Hall sensor interface module

- Special Event Trigger output to other modules

- Quadrature Encoder Interface:

- 2-phase inputs and one index input from encoder

- High and low position tracking with direction status and change of direction interrupt

- Velocity measurement

#### High-Speed, 200 ksps 10-Bit A/D Converter:

- Up to 9 Channels

- Simultaneous, Two-Channel Sampling

- · Sequential Sampling: 1, 2 or 4 Selected Channels

- Auto-Conversion Capability

- 4-Word FIFO with Selectable Interrupt Frequency

- Selectable External Conversion Triggers

- Programmable Acquisition Time

### Flexible Oscillator Structure:

- · Four Crystal modes up to 40 MHz

- Two External Clock modes up to 40 MHz

- · Internal Oscillator Block:

- 8 user-selectable frequencies: 31 kHz to 8 MHz

- OSCTUNE can compensate for frequency drift

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown of device if clock fails

#### **Power-Managed Modes:**

- Run: CPU on, Peripherals on

- Idle: CPU off, Peripherals on

- Sleep: CPU off, Peripherals off

- Ultra Low, 50 nA Input Leakage

- Idle mode Currents Down to 5.8 μA, Typical

- Sleep Current Down to 0.1 μA, Typical

- Timer1 Oscillator, 1.8 μA, Typical, 32 kHz, 2V

- Watchdog Timer (WDT), 2.1 μA, typical

- Oscillator Two-Speed Start-up

- Fast wake from Sleep and Idle, 1 µs, typical

### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three External Interrupts

- Two Capture/Compare/PWM (CCP) modules

- Enhanced USART module:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect

### **Special Microcontroller Features:**

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory, Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory, Typical

- Flash/Data EEPROM Retention: 100 Years

- Self-Programmable under Software Control

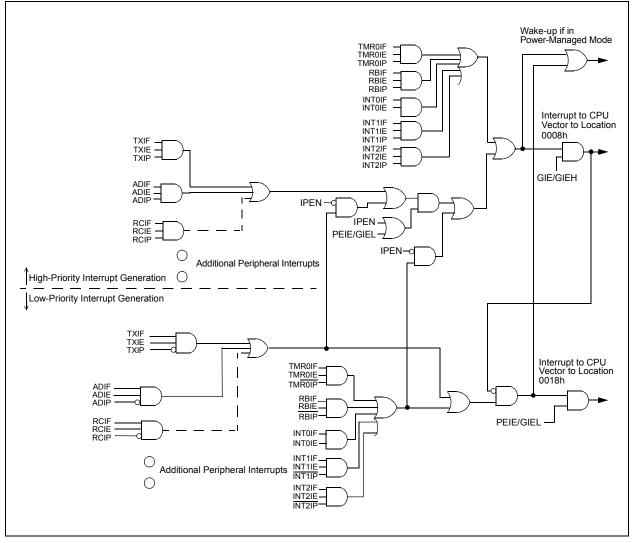

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

Programmable period from 41 ms to 131s

- Single-Supply In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) via Two Pins:

- Drives PWM outputs safely when debugging

|            | Prog             | ram Memory                   | Data            | Memory            |     |                    |     | SSP |                            |        | ure<br>er            |                       |                    |

|------------|------------------|------------------------------|-----------------|-------------------|-----|--------------------|-----|-----|----------------------------|--------|----------------------|-----------------------|--------------------|

| Device     | Flash<br>(bytes) | #Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | 10-Bit<br>A/D (ch) | ССР | SPI | Slave<br>I <sup>2</sup> C™ | EUSART | Quadratur<br>Encoder | 14-Bit<br>PWM<br>(ch) | Timers<br>8/16-Bit |

| PIC18F2331 | 8192             | 4096                         | 768             | 256               | 24  | 5                  | 2   | Y   | Y                          | Y      | Y                    | 6                     | 1/3                |

| PIC18F2431 | 16384            | 8192                         | 768             | 256               | 24  | 5                  | 2   | Y   | Y                          | Y      | Y                    | 6                     | 1/3                |

| PIC18F4331 | 8192             | 4096                         | 768             | 256               | 36  | 9                  | 2   | Y   | Y                          | Y      | Y                    | 8                     | 1/3                |

| PIC18F4431 | 16384            | 8192                         | 768             | 256               | 36  | 9                  | 2   | Y   | Y                          | Y      | Y                    | 8                     | 1/3                |

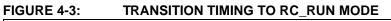

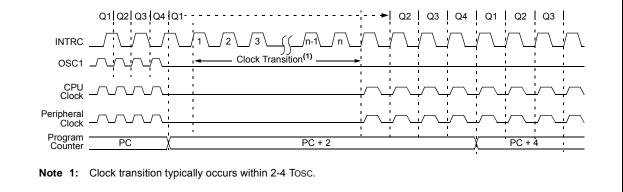

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes, after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

# TABLE 5-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                                    | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|--------------------------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                               | 0000h                 | 01 1100          | 1  | 1  | 1  | 0   | 0   | 0      | 0      |

| RESET Instruction                                            | 0000h                 | 00 uuuu          | 0  | u  | u  | u   | u   | u      | u      |

| Brown-out                                                    | 0000h                 | 01 11u-          | 1  | 1  | 1  | u   | 0   | u      | u      |

| MCLR Reset during power-managed Run modes                    | 0000h                 | 0u luuu          | u  | 1  | u  | u   | u   | u      | u      |

| MCLR Reset during power-managed Idle and Sleep modes         | 0000h                 | 0u 10uu          | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Time-out during full power or<br>power-managed Run modes | 0000h                 | 0u Ouuu          | u  | 0  | u  | u   | u   | u      | u      |

| MCLR Reset during full-power execution                       |                       |                  |    |    |    |     |     | u      | u      |

| Stack Full Reset (STVREN = 1)                                | 0000h                 | 0u uuuu          | u  | u  | u  | u   | u   | 1      | u      |

| Stack Underflow Reset (STVREN = 1)                           |                       |                  |    |    |    |     |     | u      | 1      |

| Stack Underflow Error (not an actual Reset, STVREN = 0)      | 0000h                 | uu uuuu          | u  | u  | u  | u   | u   | u      | 1      |

| WDT time-out during power-managed Idle or Sleep modes        | PC + 2                | uu 00uu          | u  | 0  | 0  | u   | u   | u      | u      |

| Interrupt exit from power-managed modes                      | PC + 2 <sup>(1)</sup> | uu u0uu          | u  | u  | 0  | u   | u   | u      | u      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (0x000008h or 0x000018h).

| TABLE 5-3:           | INITIALIZATION CONDITION |      |                                    | <u>N CO</u>                                                   | NDITIONS FOR AL                 | DNS FOR ALL REGISTERS (CONTINUED) |                  |  |  |  |  |  |

|----------------------|--------------------------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|-----------------------------------|------------------|--|--|--|--|--|

| Register             | ster Applicable Devices  |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |                                   |                  |  |  |  |  |  |

| PTCON0               | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | uuuu uuuu                         | uuuu uuuu        |  |  |  |  |  |

| PTCON1               | 2331                     | 2431 | 4331                               | 4431                                                          | 00                              | 00                                | uu               |  |  |  |  |  |

| PTMRL                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| PTMRH                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000                            | 0000                              | uuuu             |  |  |  |  |  |

| PTPERL               | 2331                     | 2431 | 4331                               | 4431                                                          | 1111 1111                       | 1111 1111                         | uuuu uuuu        |  |  |  |  |  |

| PTPERH               | 2331                     | 2431 | 4331                               | 4431                                                          | 1111                            | 1111                              | uuuu             |  |  |  |  |  |

| PDC0L                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| PDC0H                | 2331                     | 2431 | 4331                               | 4431                                                          | 00 0000                         | 00 0000                           | uu uuuu          |  |  |  |  |  |

| PDC1L                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| PDC1H                | 2331                     | 2431 | 4331                               | 4431                                                          | 00 0000                         | 00 0000                           | uu uuuu          |  |  |  |  |  |

| PDC2L                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| PDC2H                | 2331                     | 2431 | 4331                               | 4431                                                          | 00 0000                         | 00 0000                           | uu uuuu          |  |  |  |  |  |

| PDC3L                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| PDC3H                | 2331                     | 2431 | 4331                               | 4431                                                          | 00 0000                         | 00 0000                           | uu uuuu          |  |  |  |  |  |

| SEVTCMPL             | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| SEVTCMPH             | 2331                     | 2431 | 4331                               | 4431                                                          | 0000                            | 0000                              | uuuu             |  |  |  |  |  |

| PWMCON0              | 2331                     | 2431 | 4331                               | 4431                                                          | -111 0000                       | -111 0000                         | -uuu uuuu        |  |  |  |  |  |

| PWMCON1              | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0-00                       | 0000 0-00                         | uuuu u-uu        |  |  |  |  |  |

| DTCON                | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| FLTCONFIG            | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| OVDCOND              | 2331                     | 2431 | 4331                               | 4431                                                          | 1111 1111                       | 1111 1111                         | uuuu uuuu        |  |  |  |  |  |

| OVDCONS              | 2331                     | 2431 | 4331                               | 4431                                                          | 0000 0000                       | 0000 0000                         | uuuu uuuu        |  |  |  |  |  |

| CAP1BUFH/<br>VELRH   | 2331                     | 2431 | 4331                               | 4431                                                          | XXXX XXXX                       | սսսս սսսս                         | սսսս սսսս        |  |  |  |  |  |

| CAP1BUFL/<br>VELRL   | 2331                     | 2431 | 4331                               | 4431                                                          | XXXX XXXX                       | սսսս սսսս                         | սսսս սսսս        |  |  |  |  |  |

| CAP2BUFH/<br>POSCNTH | 2331                     | 2431 | 4331                               | 4431                                                          | XXXX XXXX                       | սսսս սսսս                         | <u>uuuu</u> uuuu |  |  |  |  |  |

| CAP2BUFL/<br>POSCNTL | 2331                     | 2431 | 4331                               | 4431                                                          | XXXX XXXX                       | uuuu uuuu                         | <u>uuuu</u> uuuu |  |  |  |  |  |

| CAP3BUFH/<br>MAXCNTH | 2331                     | 2431 | 4331                               | 4431                                                          | XXXX XXXX                       | uuuu uuuu                         | uuuu uuuu        |  |  |  |  |  |

### TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-2 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** Bit 3 of PORTE and LATE are enabled if MCLR functionality is disabled. When not enabled as the PORTE pin, they are disabled and read as '0'. The 28-pin devices do not have only RE3 implemented.

| R/W-0                                                                | U-0                         | U-0                        | R/W-0          | U-0               | R/W-0 | U-0             | R/W-0  |  |

|----------------------------------------------------------------------|-----------------------------|----------------------------|----------------|-------------------|-------|-----------------|--------|--|

| OSCFIE                                                               | —                           | —                          | EEIE           | —                 | LVDIE | —               | CCP2IE |  |

| bit 7                                                                |                             |                            |                |                   |       |                 | bit 0  |  |

|                                                                      |                             |                            |                |                   |       |                 |        |  |

| Legend:                                                              |                             |                            |                |                   |       |                 |        |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                             |                            |                |                   |       |                 |        |  |

| -n = Value a                                                         | It POR                      | '1' = Bit is set           |                | '0' = Bit is clea | ared  | x = Bit is unkn | iown   |  |

|                                                                      |                             |                            |                |                   |       |                 |        |  |

| bit 7                                                                | OSCFIE: Osc                 | illator Fail Inter         | rupt Enable bi | t                 |       |                 |        |  |

| 1 = Enabled                                                          |                             |                            |                |                   |       |                 |        |  |

|                                                                      |                             | 0 = Disabled               |                |                   |       |                 |        |  |

| bit 6-5                                                              | Unimplement                 | ted: Read as '             | )'             |                   |       |                 |        |  |

| bit 4                                                                | EEIE: Interrup              | ot Enable bit              |                |                   |       |                 |        |  |

|                                                                      | 1 = Enabled<br>0 = Disabled |                            |                |                   |       |                 |        |  |

| bit 3                                                                | Unimplement                 | ted: Read as '             | )'             |                   |       |                 |        |  |

| bit 2                                                                |                             |                            |                |                   |       |                 |        |  |

| 1 = Enabled                                                          |                             |                            |                |                   |       |                 |        |  |

|                                                                      | 0 = Disabled                |                            |                |                   |       |                 |        |  |

| bit 1                                                                | Unimplement                 | Unimplemented: Read as '0' |                |                   |       |                 |        |  |

| bit 0                                                                | CCP2IE: CCF                 | 2 Interrupt Ena            | able bit       |                   |       |                 |        |  |

|                                                                      | 1 = Enabled                 |                            |                |                   |       |                 |        |  |

|                                                                      | 0 = Disabled                |                            |                |                   |       |                 |        |  |

#### REGISTER 10-8: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| Name    | Bit 7     | Bit 6                         | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset Values<br>on Page: |

|---------|-----------|-------------------------------|---------|---------|--------|--------|---------------|--------|--------------------------|

| PORTB   | RB7       | RB6                           | RB5     | RB4     | RB3    | RB2    | RB1           | RB0    | 57                       |

| LATB    | LATB Data | ATB Data Output Register      |         |         |        |        |               |        | 57                       |

| TRISB   | PORTB Dat | PORTB Data Direction Register |         |         |        |        |               |        | 57                       |

| INTCON  | GIE/GIEH  | PEIE/GIEL                     | TMR0IE  | INT0IE  | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 54                       |

| INTCON2 | RBPU      | INTEDG0                       | INTEDG1 | INTEDG2 | _      | TMR0IP |               | RBIP   | 54                       |

| INTCON3 | INT2IP    | INT1IP                        | _       | INT2IE  | INT1IE | _      | INT2IF        | INT1IF | 54                       |

### TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

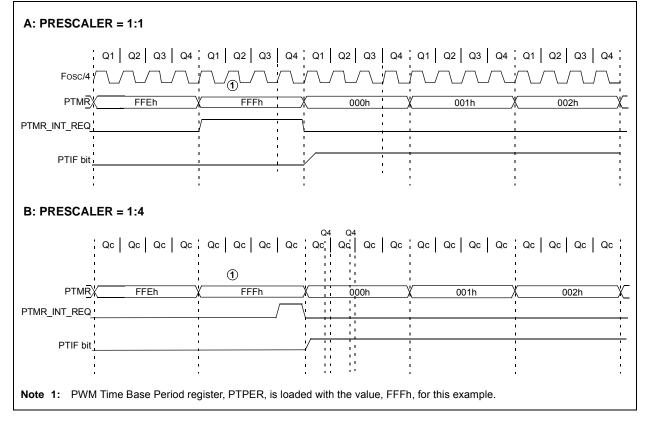

Table 18-1 shows the minimum PWM frequencies that can be generated with the PWM time base and the prescaler. An operating frequency of 40 MHz (FCYC = 10 MHz) and PTPER = 0xFFF is assumed in the table. The PWM module must be capable of generating PWM signals at the line frequency (50 Hz or 60 Hz) for certain power control applications.

| Minimum PWM Frequencies vs. Prescaler Value<br>for Fcyc = 10 MIPS (PTPER = 0FFFh) |                               |                                 |  |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------|---------------------------------|--|--|--|--|

| Prescale                                                                          | PWM Frequency<br>Edge-Aligned | PWM Frequency<br>Center-Aligned |  |  |  |  |

| 1:1                                                                               | 2441 Hz                       | 1221 Hz                         |  |  |  |  |

| 1:4                                                                               | 610 Hz                        | 305 Hz                          |  |  |  |  |

| 1:16                                                                              | 153 Hz                        | 76 Hz                           |  |  |  |  |

| 1:64                                                                              | 38 Hz                         | 19 Hz                           |  |  |  |  |

#### TABLE 18-1: MINIMUM PWM FREQUENCY

#### 18.3.5 PWM TIME BASE POSTSCALER

The match output of PTMR can optionally be postscaled through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate an interrupt. The postscaler counter is cleared when any of the following occurs:

- Write to the PTMR register

- Write to the PTCON register

- Any device Reset

The PTMR register is not cleared when PTCON is written.

#### 18.4 PWM Time Base Interrupts

The PWM timer can generate interrupts based on the modes of operation selected by the PTMOD<1:0> bits and the postscaler bits (PTOPS<3:0>).

#### 18.4.1 INTERRUPTS IN FREE-RUNNING MODE

When the PWM time base is in the Free-Running mode (PTMOD<1:0> = 00), an interrupt event is generated each time a match with the PTPER register occurs. The PTMR register is reset to zero in the following clock edge.

Using a postscaler selection other than 1:1 will reduce the frequency of interrupt events.

#### FIGURE 18-5: PWM TIME BASE INTERRUPT TIMING, FREE-RUNNING MODE

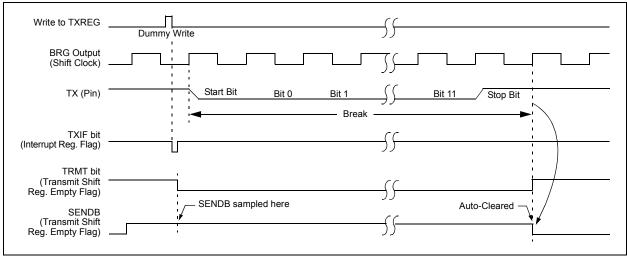

### 20.3.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-9 for the timing of the Break character sequence.

#### 20.3.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to setup the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 20.3.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 of the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 20.3.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit before placing the EUSART in its Sleep mode.

#### FIGURE 20-9: SEND BREAK CHARACTER SEQUENCE

#### REGISTER 21-2: ADCON1: A/D CONTROL REGISTER 1

| R/W-0 | R/W-0 | U-0 | R/W-0  | R-0   | R-0   | R-0    | R-0    |

|-------|-------|-----|--------|-------|-------|--------|--------|

| VCFG1 | VCFG0 | _   | FIFOEN | BFEMT | BFOVL | ADPNT1 | ADPNT0 |

| bit 7 |       |     |        |       |       |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | VCFG<1:0>: A/D VREF+ and A/D VREF- Source Selection bits<br>00 = VREF+ = AVDD, VREF- = AVSS (AN2 and AN3 are analog inputs or digital I/O)<br>01 = VREF+ = External VREF+, VREF- = AVSS (AN2 is an analog input or digital I/O)<br>10 = VREF+ = AVDD, VREF- = External VREF- (AN3 is an analog input or digital I/O)<br>11 = VREF+ = External VREF-, VREF- = External VREF- |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                  |

| bit 4   | FIFOEN: FIFO Buffer Enable bit                                                                                                                                                                                                                                                                                                                                              |

|         | <ul><li>1 = FIFO is enabled</li><li>0 = FIFO is disabled</li></ul>                                                                                                                                                                                                                                                                                                          |

| bit 3   | BFEMT: Buffer Empty bit                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = FIFO is empty</li> <li>0 = FIFO is not empty (at least one of four locations has unread A/D result data)</li> </ul>                                                                                                                                                                                                                                            |

| bit 2   | BFOVFL: Buffer Overflow bit                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = A/D result has overwritten a buffer location that has unread data</li> <li>0 = A/D result has not overflowed</li> </ul>                                                                                                                                                                                                                                        |

| bit 1-0 | ADPNT<1:0>: Buffer Read Pointer Location bits                                                                                                                                                                                                                                                                                                                               |

|         | Designates the location to be read next.<br>00 = Buffer Address 0<br>01 = Buffer Address 1<br>10 = Buffer Address 2<br>11 = Buffer Address 3                                                                                                                                                                                                                                |

| R/W-0        | R/W-0                                                                                                                 | R/W-0                                                                         | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0 |

|--------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------|------------------|-----------------|------------------|-------|

| ADFM         | ACQT3                                                                                                                 | ACQT2                                                                         | ACQT1         | ACQT0            | ADCS2           | ADCS1            | ADCS0 |

| bit 7        |                                                                                                                       |                                                                               |               |                  |                 |                  | bit ( |

| Legend:      |                                                                                                                       |                                                                               |               |                  |                 |                  |       |

| R = Readab   | le bit                                                                                                                | W = Writable                                                                  | bit           | U = Unimplen     | nented bit, rea | d as '0'         |       |

| -n = Value a | t POR                                                                                                                 | '1' = Bit is set                                                              |               | '0' = Bit is cle | ared            | x = Bit is unkr  | nown  |

| bit 7        | <b>ADFM:</b> A/D I<br>1 = Right jus<br>0 = Left justit                                                                |                                                                               | Select bit    |                  |                 |                  |       |

| bit 6-3      |                                                                                                                       | D<br>D<br>D<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD<br>AD |               |                  | )/DONE is set   | <sub>)</sub> (1) |       |

| bit 2-0      | ADCS<2:0>                                                                                                             | : A/D Conversio                                                               | n Clock Selec | t bits           |                 |                  |       |

|              | 000 = Fosc/<br>001 = Fosc/<br>010 = Fosc/<br>011 = Frc/4<br>100 = Fosc/<br>101 = Fosc/<br>110 = Fosc/<br>111 = Frc (I | 8<br>32<br>4<br>16                                                            | Oscillator)   |                  |                 |                  |       |

#### REGISTER 21-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D RC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

#### 23.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 23.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

### 23.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

## 23.7 In-Circuit Serial Programming

PIC18F2331/2431/4331/4431 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 23.8 In-Circuit Debugger

When the DEBUG bit in the CONFIG4L Configuration register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 23-4 shows which resources are required by the background debugger.

| TABLE 23-4: | DEBUGGER RESOURCES |

|-------------|--------------------|

|-------------|--------------------|

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | <1 Kbytes |

| Data Memory:    | 16 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to  $\overline{\text{MCLR}/\text{VPP}}$ , VDD, VSS, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

### 23.9 Single-Supply ICSP™ Programming

The LVP bit in Configuration Register 4L (CONFIG4L<2>) enables Single-Supply ICSP Programming. When LVP is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP pin, but the RB5/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

LVP is enabled in erased devices.

While programming, using Single-Supply Programming, VDD is applied to the MCLR/VPP pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: When Single-Supply Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- 3: When LVP is enabled externally, pull the PGM pin to Vss to allow normal program execution.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared and RB5/PGM becomes available as the digital I/O pin RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/ VPP pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Single-Supply Programming, the device must be supplied with VDD of 4.5V to 5.5V.

| ADD     | OWFC                                      | AD                          | D W ar                                              | nd Carry                                                                                | bit                                | to f                                   |                                    |  |

|---------|-------------------------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|----------------------------------------|------------------------------------|--|

| Synta   | ax:                                       | [ lat                       | bel] ADI                                            | DWFC                                                                                    | f[,d                               | [,a]]                                  |                                    |  |

| Oper    | ands:                                     | d ∈                         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                                                                         |                                    |                                        |                                    |  |

| Oper    | ation:                                    | (W)                         | + (f) + (                                           | $C) \rightarrow des$                                                                    | st                                 |                                        |                                    |  |

| Statu   | s Affected:                               | Ν, Ο                        | DV, C, D                                            | C, Z                                                                                    |                                    |                                        |                                    |  |

| Enco    | oding:                                    | (                           | 010                                                 | 00da                                                                                    | ff                                 | ff                                     | ffff                               |  |

| Desc    | ription:                                  | loca<br>in V<br>data<br>Acc | ation, 'f'.<br>V. If 'd' is<br>a memori<br>ess Bar  | Carry flag<br>If 'd' is '0'<br>s '1', the r<br>ry location<br>k will be s<br>I not be o | , the<br>esult<br>n, 'f'.<br>selec | result<br>is pla<br>If 'a' i<br>ted. I | is placed<br>aced in<br>s '0', the |  |

| Word    | ls:                                       | 1                           | 1                                                   |                                                                                         |                                    |                                        |                                    |  |

| Cycles: |                                           | 1                           |                                                     |                                                                                         |                                    |                                        |                                    |  |

| QC      | ycle Activity:                            |                             |                                                     |                                                                                         |                                    |                                        |                                    |  |

|         | Q1                                        | (                           | ີ 22                                                | Q3                                                                                      |                                    |                                        | Q4                                 |  |

|         | Decode                                    |                             | ead<br>ster 'f'                                     | Proces<br>Data                                                                          | S                                  |                                        | ite to<br>ination                  |  |

| Exan    | nple:                                     | ADI                         | DWFC                                                | REG,                                                                                    | W                                  |                                        |                                    |  |

|         | Before Instruc<br>Carry bit<br>REG<br>W   | =                           | 1<br>0x02<br>0x4D                                   |                                                                                         |                                    |                                        |                                    |  |

|         | After Instructic<br>Carry bit<br>REG<br>W | =                           | 0<br>0x02<br>0x50                                   |                                                                                         |                                    |                                        |                                    |  |

|              | W AND Literal with W |           |                   |                          |     |   |                     |

|--------------|----------------------|-----------|-------------------|--------------------------|-----|---|---------------------|

| Syntax:      |                      | [ /       | abel] Al          | NDLW                     | k   |   |                     |

| Operand      | ds:                  | 0         | $0 \le k \le 255$ |                          |     |   |                     |

| Operatio     | on:                  | (V        | /) .AND.          | $k \rightarrow W$        |     |   |                     |

| Status A     | Affected:            | N, Z      |                   |                          |     |   |                     |

| Encodin      | ıg:                  |           | 0000              | 1011                     | kkk | k | kkkk                |

| Description: |                      |           |                   | nts of W a<br>'k'. The r |     |   | with the aced in W. |

| Words:       |                      | 1         |                   |                          |     |   |                     |

| Cycles:      |                      | 1         |                   |                          |     |   |                     |

| Q Cycle      | e Activity:          |           |                   |                          |     |   |                     |

|              | Q1                   |           | Q2                | Q3                       | 1   |   | Q4                  |

|              | Decode               | Rea       | id literal<br>'k' | Proce<br>Data            |     | V | /rite to<br>W       |

|              |                      |           |                   |                          |     |   |                     |

| Example      | <u>e:</u>            | A         | JDLW              | 0x5F                     |     |   |                     |

| Be           | fore Instruc<br>W    | tion<br>= | 0xA3              |                          |     |   |                     |

0x03

=

After Instruction

W

| BNO         | 3                                                     | Branch if                                                                  | Not Carry                                                                               |                                                        | BNN                   |                                | Branch if                                                              | Not Nega                                                                    | tive                                                |         |  |

|-------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|--------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|---------|--|

| Synt        | ax:                                                   | [ <i>label</i> ] BN                                                        | IC n                                                                                    |                                                        | Syntax:               | Syntax:                        |                                                                        | [ <i>label</i> ] BNN n                                                      |                                                     |         |  |

| Ope         | rands:                                                | -128 ≤ n ≤ 1                                                               | 127                                                                                     |                                                        | Operands:             | Operands:                      |                                                                        | 127                                                                         |                                                     |         |  |

| Ope         | ration:                                               | if Carry bit is '0',<br>(PC) + 2 + 2n → PC                                 |                                                                                         | Operation:                                             | Operation:            |                                | if Negative bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC              |                                                                             |                                                     |         |  |

| Statu       | us Affected:                                          | None                                                                       |                                                                                         |                                                        | Status Affeo          | cted:                          | None                                                                   |                                                                             |                                                     |         |  |

| Enco        | oding:                                                | 1110                                                                       | 0011 nni                                                                                | nn nnnn                                                | Encoding:             |                                | 1110                                                                   | 0111 r                                                                      | innn r                                              | nnn     |  |

| Desc        | cription:                                             | will branch.<br>The 2's con<br>added to the<br>incrementer<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the r<br>the new addre<br>n. This instruct | ber, '2n', is<br>e PC will have<br>next<br>ess will be | Description           | :                              | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement nu<br>e PC. Since<br>d to fetch th<br>the new ad<br>n. This instru | imber, '2n'<br>the PC wil<br>e next<br>dress will t | ll have |  |

| Wor         | ds:                                                   | 1                                                                          |                                                                                         |                                                        | Words:                |                                | 1                                                                      |                                                                             |                                                     |         |  |

| Cycl        | es:                                                   | 1(2)                                                                       |                                                                                         |                                                        | Cycles:               |                                | 1(2)                                                                   |                                                                             |                                                     |         |  |

|             | cycle Activity:<br>ump:                               |                                                                            |                                                                                         |                                                        | Q Cycle A<br>If Jump: | ctivity:                       |                                                                        |                                                                             |                                                     |         |  |

|             | Q1                                                    | Q2                                                                         | Q3                                                                                      | Q4                                                     | (                     | Q1                             | Q2                                                                     | Q3                                                                          | Q                                                   | 4       |  |

|             | Decode                                                | Read literal<br>'n'                                                        | Process<br>Data                                                                         | Write to<br>PC                                         | Dec                   | code                           | Read literal<br>'n'                                                    | Process<br>Data                                                             | Write<br>PC                                         |         |  |

|             | No<br>operation                                       | No<br>operation                                                            | No<br>operation                                                                         | No<br>operation                                        | -                     | lo<br>ation                    | No<br>operation                                                        | No<br>operation                                                             | No<br>opera                                         | -       |  |

| lf N        | o Jump:                                               |                                                                            |                                                                                         |                                                        | If No Jump            | ):                             |                                                                        |                                                                             |                                                     |         |  |

|             | Q1                                                    | Q2                                                                         | Q3                                                                                      | Q4                                                     | (                     | Q1                             | Q2                                                                     | Q3                                                                          | Q                                                   | 4       |  |

|             | Decode                                                | Read literal<br>'n'                                                        | Process<br>Data                                                                         | No<br>operation                                        | Dec                   | code                           | Read literal<br>'n'                                                    | Process<br>Data                                                             | No<br>opera                                         | -       |  |

| <u>Exar</u> | <u>mple:</u>                                          | HERE                                                                       | BNC Jump                                                                                |                                                        | Example:              |                                | HERE                                                                   | BNN Jut                                                                     | np                                                  |         |  |

|             | Before Instruc<br>PC                                  |                                                                            | dress (here                                                                             | :)                                                     |                       | Instruc<br>C                   |                                                                        | dress (HEF                                                                  | RE)                                                 |         |  |

|             | After Instruction<br>If Carry<br>PC<br>If Carry<br>PC | = 0;<br>= adv<br>= 1;                                                      | dress (Jump<br>dress (HERE                                                              |                                                        | If                    | Negativ<br>PC<br>Negativ<br>PC | on<br>/e = 0;<br>= ad<br>/e = 1;                                       | dress (Jur<br>dress (HEF                                                    | י<br>קוו                                            |         |  |

| RETURN Return from Subroutine |                |                                                                                                                                                               |                                                                              |                                                         |                                                                          |  |  |

|-------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| Synta                         | ax:            | [label] R                                                                                                                                                     | ETURN                                                                        | [s]                                                     |                                                                          |  |  |

| Oper                          | ands:          | $s \in \left[0,1\right]$                                                                                                                                      |                                                                              |                                                         |                                                                          |  |  |

| Oper                          | ation:         | $(TOS) \rightarrow PC;$<br>if s = 1:<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |                                                                              |                                                         |                                                                          |  |  |

| Status Affected: None         |                |                                                                                                                                                               |                                                                              |                                                         |                                                                          |  |  |

| Enco                          | ding:          | 0000                                                                                                                                                          | 0000                                                                         | 000                                                     | 1 001s                                                                   |  |  |

| Desc                          | ription:       | Return from<br>popped and<br>is loaded in<br>'s'= 1, the of<br>registers, V<br>are loaded<br>registers, V<br>'s' = 0, no to<br>occurs.                        | d the top<br>to the pro-<br>contents o<br>VS, STAT<br>into their<br>V, STATU | of the sogram<br>of the so<br>USS a<br>corres<br>IS and | stack (TOS)<br>counter. If<br>shadow<br>and BSRS,<br>sponding<br>BSR. If |  |  |

| Word                          | ls:            | 1                                                                                                                                                             |                                                                              |                                                         |                                                                          |  |  |

| Cycle                         | es:            | 2                                                                                                                                                             |                                                                              |                                                         |                                                                          |  |  |

| QC                            | ycle Activity: |                                                                                                                                                               |                                                                              |                                                         |                                                                          |  |  |

|                               | Q1             | Q2                                                                                                                                                            | Q3                                                                           |                                                         | Q4                                                                       |  |  |

|                               | Decode         | No<br>operation                                                                                                                                               | Proce<br>Data                                                                |                                                         | POP PC<br>from stack                                                     |  |  |

|                               | No             | No                                                                                                                                                            | No                                                                           |                                                         | No                                                                       |  |  |

|                               | operation      | operation                                                                                                                                                     | operat                                                                       | ion                                                     | operation                                                                |  |  |

|                               |                |                                                                                                                                                               |                                                                              |                                                         |                                                                          |  |  |

| Example: | RETURN |

|----------|--------|

|----------|--------|

After Interrupt

PC = TOS

| RLCF                              | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] RLCF f [,d [,a]]                                                                                                                                                                                                                                                                                                                              |

| Operands:                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                             |

| Operation:                        | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow C,$<br>$(C) \rightarrow dest < 0 >$                                                                                                                                                                                                                                                          |

| Status Affected:                  | C, N, Z                                                                                                                                                                                                                                                                                                                                                        |

| Encoding:                         | 0011 01da ffff ffff                                                                                                                                                                                                                                                                                                                                            |

| Description:<br>Words:<br>Cycles: | The contents of register, 'f', are rotated<br>one bit to the left through the Carry flag.<br>If 'd' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in regis-<br>ter, 'f'. If 'a' is '0', the Access Bank will<br>be selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be selected<br>as per the BSR value. |

| Q Cycle Activity:                 |                                                                                                                                                                                                                                                                                                                                                                |

| Q1                                | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                       |

| Decode                            | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                                                 |

| Example:                          | RLCF REG, W                                                                                                                                                                                                                                                                                                                                                    |

| Before Instruc<br>REG<br>C        | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                             |

| After Instructio<br>REG<br>W<br>C | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                                                                                                                                                              |

| RLNCF                   | Rotate L                                                             | eft f (No                                                                                                                                                                                                                                                                                                                                  | Carry)      |                    |  |  |  |

|-------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|--|--|--|

| Syntax:                 | [ label ]                                                            | RLNCF                                                                                                                                                                                                                                                                                                                                      | f [,d [,a]] |                    |  |  |  |

| Operands:               | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                | ;                                                                                                                                                                                                                                                                                                                                          |             |                    |  |  |  |