Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

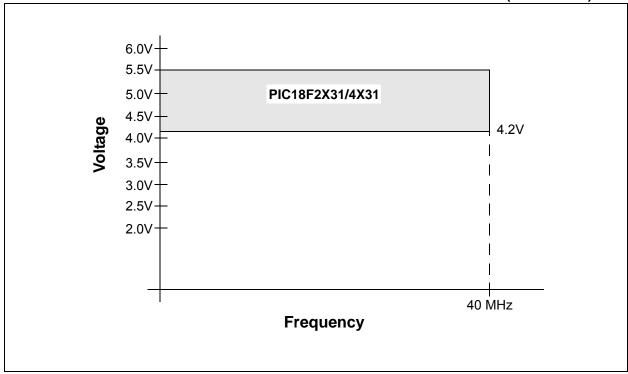

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2331t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F2331/2431/4331/4431

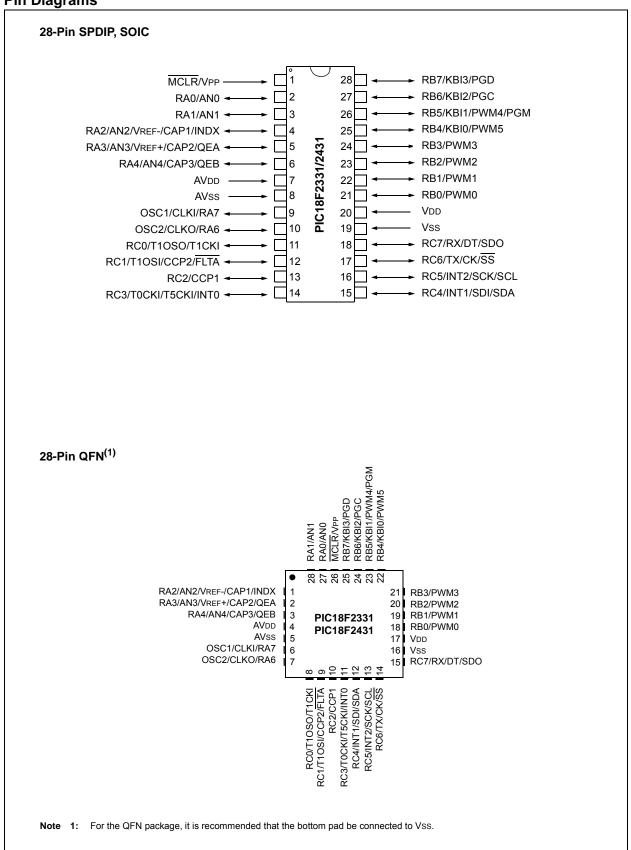

# **Pin Diagrams**

# PIC18F2331/2431/4331/4431

NOTES:

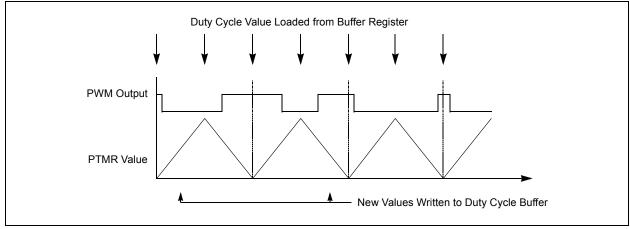

FIGURE 18-14: DUTY CYCLE UPDATE TIMES IN CONTINUOUS UP/DOWN COUNT MODE WITH DOUBLE UPDATES

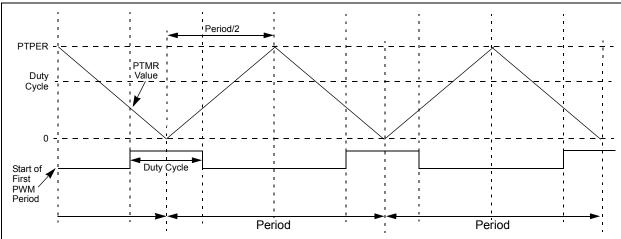

#### 18.6.4 CENTER-ALIGNED PWM

Center-aligned PWM signals are produced by the module when the PWM time base is configured in a Continuous Up/Down Count mode (see Figure 18-15). The PWM compare output is driven to the active state when the value of the Duty Cycle register matches the value of PTMR and the PWM time base is counting downwards (PTDIR = 1). The PWM compare output will be driven to the inactive state when the PWM time base is counting upwards (PTDIR = 0) and the value in the PTMR register matches the duty cycle value. If the value in a particular Duty Cycle register is zero, then the output on the corresponding PWM pin will be

inactive for the entire PWM period. In addition, the output on the PWM pin will be active for the entire PWM period if the value in the Duty Cycle register is equal to or greater than the value in the PTPER register.

Note: When the PWM is started in Center-Aligned mode, the PWM Time Base Period register (PTPER) is loaded into the PWM Time Base register (PTMR) and the PTMR is configured automatically to start down counting. This is done to ensure that all the PWM signals don't start at the same time.

FIGURE 18-15: START OF CENTER-ALIGNED PWM

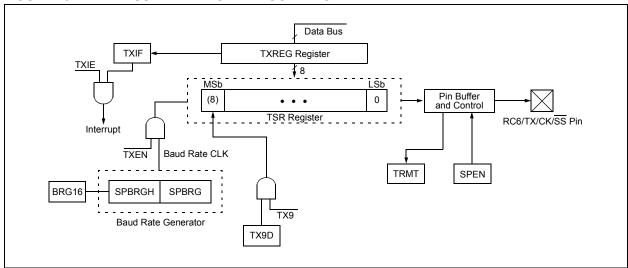

## FIGURE 20-2: EUSART TRANSMIT BLOCK DIAGRAM

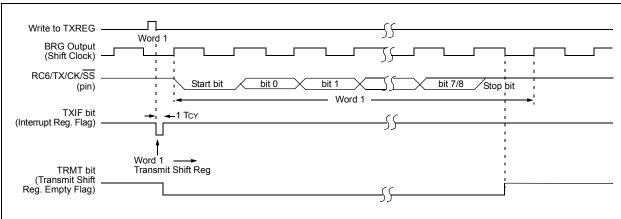

### FIGURE 20-3: ASYNCHRONOUS TRANSMISSION

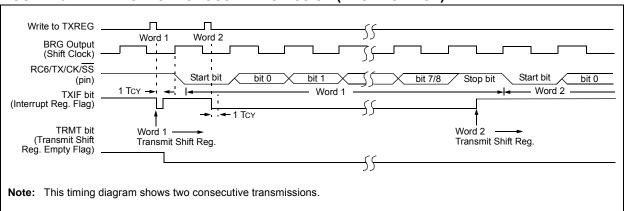

#### FIGURE 20-4: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### 21.2 A/D Result Buffer

The A/D module has a 4-level result buffer with an address range of 0 to 3, enabled by setting the FIFOEN bit in the ADCON1 register. This buffer is implemented in a circular fashion, where the A/D result is stored in one location and the address is incremented. If the address is greater than 3, the pointer is wrapped back around to 0. The result buffer has a Buffer Empty Flag, BFEMT, indicating when any data is in the buffer. It also has a Buffer Overflow Flag, BFOVFL, which indicates when a new sample has overwritten a location that was not previously read.

Associated with the buffer is a pointer to the address for the next read operation. The ADPNT<1:0> bits configure the address for the next read operation. These bits are read-only.

The Result Buffer also has a configurable interrupt trigger level that is configured by the ADRS<1:0> bits. The user has three selections: interrupt flag set on every write to the buffer, interrupt on every second write to the buffer, or interrupt on every fourth write to the buffer. ADPNT<1:0> are reset to '00' every time a conversion sequence is started (either by setting the GO/DONE bit or on a trigger).

Note: When right justified, reading ADRESL increments the ADPNT<1:0> bits. When left justified, reading ADRESH increments the ADPNT<1:0> bits.

### 21.3 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 21-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 21-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 21-1 shows the calculation of the minimum required acquisition time TACQ. In this case, the converter module is fully powered up at the outset and therefore, the amplifier settling time, TAMP, is negligible. This calculation is based on the following application system assumptions:

$\begin{array}{lll} \text{CHOLD} & = & 9 \text{ pF} \\ \text{Rs} & = & 100\Omega \\ \text{Conversion Error} & \leq & 1/2 \text{ LSb} \end{array}$

VDD = 5V → Rss = 6 kΩ Temperature = 50°C (system max.) VHOLD = 0V @ time = 0

#### **EQUATION 21-1: ACQUISITION TIME**

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

#### **EQUATION 21-2: MINIMUM A/D HOLDING CAPACITOR CHARGING TIME**

```

\begin{array}{lll} V_{HOLD} & = & (V_{REF} - (V_{REF}/2048)) \bullet (1 - e^{(-T_{C}/C_{HOLD}(R_{IC} + R_{SS} + R_{S}))}) \\ \text{or} \\ T_{C} & = & -(C_{HOLD})(R_{IC} + R_{SS} + R_{S}) \ln(1/2048) \end{array}

```

# PIC18F2331/2431/4331/4431

| MO\          | OVLW Move Literal to W |                                           |               |     |   |              |

|--------------|------------------------|-------------------------------------------|---------------|-----|---|--------------|

| Synta        | ax:                    | [label] I                                 | MOVLW         | k   |   |              |

| Oper         | ands:                  | $0 \le k \le 25$                          | 5             |     |   |              |

| Operation:   |                        | $k\toW$                                   |               |     |   |              |

| Statu        | s Affected:            | None                                      |               |     |   |              |

| Enco         | ding:                  | 0000                                      | 1110          | kkk | k | kkkk         |

| Description: |                        | The 8-bit literal, 'k', is loaded into W. |               |     |   |              |

| Word         | ls:                    | 1                                         |               |     |   |              |

| Cycle        | es:                    | 1                                         |               |     |   |              |

| QC           | ycle Activity:         |                                           |               |     |   |              |

|              | Q1                     | Q2                                        | Q3            | 3   |   | Q4           |

|              | Decode                 | Read<br>literal 'k'                       | Proce<br>Data |     | V | rite to<br>W |

Example: MOVLW 0x5A

> After Instruction 0x5A

| Move W to f                                                                                                                                                                                      |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [label] M                                                                                                                                                                                        | IOVWF                                            | f [,a]                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                               |

| $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                                                                  |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| $(W) \rightarrow f$                                                                                                                                                                              |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| None                                                                                                                                                                                             |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| 0110                                                                                                                                                                                             | 111a                                             | ffff                                                                                                                                                                                                                                 | ffff                                                                                                                                                                                                                                                                                                                                          |

| Location, 'f', can be anywhere in the 256-byte bank. If 'a' is '0', the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value. |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| 1                                                                                                                                                                                                |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| 1                                                                                                                                                                                                |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                  |                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                               |

| Q2                                                                                                                                                                                               | Q3                                               | 1                                                                                                                                                                                                                                    | Q4                                                                                                                                                                                                                                                                                                                                            |

| Read<br>register 'f'                                                                                                                                                                             | Proce<br>Data                                    |                                                                                                                                                                                                                                      | Write<br>gister 'f'                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                  | [ label ] $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ | [ label ] MOVWF $0 \le f \le 255$ $a \in [0,1]$ (W) → f  None $0110$ $111a$ Move data from W to Location, 'f', can be 256-byte bank. If 'a' Bank will be selecte BSR value. If 'a' = 1 be selected as per to 1  1  Q2 Q3  Read Proce | [label] MOVWF $f[,a]$ $0 \le f \le 255$ $a \in [0,1]$ (W) $\rightarrow f$ None  0110 111a fffff  Move data from W to register, Location, 'f', can be anywhere 256-byte bank. If 'a' is '0', the Bank will be selected, overridi BSR value. If 'a' = 1, then the be selected as per the BSR value. If 'a' = 1, then the be selected as Process |

Example: MOVWF REG

Before Instruction

0x4F 0xFF W REG

After Instruction

W REG 0x4F 0x4F

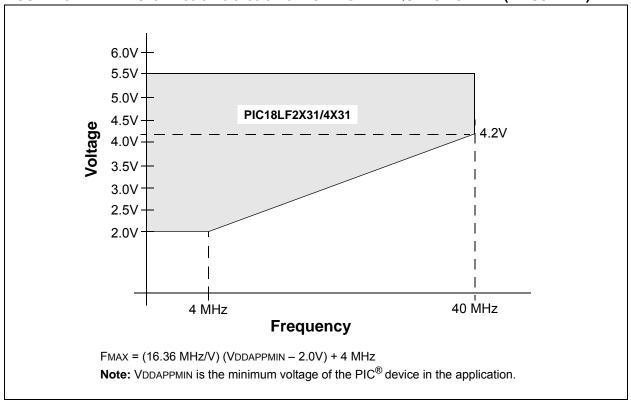

FIGURE 26-2: PIC18LF2331/2431/4331/4431 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

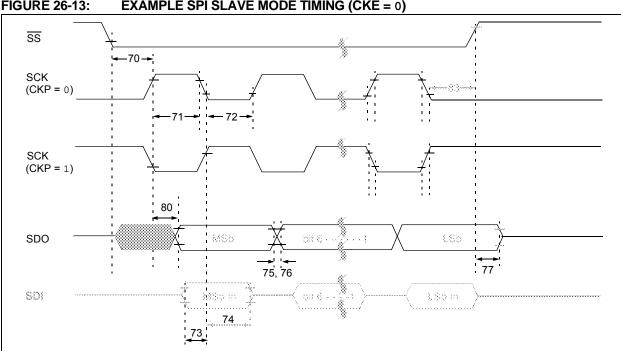

FIGURE 26-13: **EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)**

TABLE 26-13: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                              |             | Min           | Max | Units | Conditions |

|--------------|-----------------------|-------------------------------------------------------------|-------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS ↓ to SCK ↓ or SCK ↑ Input                                |             | Tcy           | _   | ns    |            |

| 71           | TscH                  | SCK Input High Time                                         | Continuous  | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       |                                                             | Single byte | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                                          | Continuous  | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       |                                                             | Single byte | 40            | _   | ns    | (Note 1)   |

| 73           | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SCK Edge                    |             | 20            | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First Clock Edge of Byte 2 |             | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                     |             | 40            | _   | ns    |            |

| 75           | TdoR                  | SDO Data Output Rise Time                                   | PIC18FXX31  | _             | 25  | ns    |            |

|              |                       |                                                             | PIC18LFXX31 | _             | 45  | ns    | 1          |

| 76           | TdoF                  | SDO Data Output Fall Time                                   |             | _             | 25  | ns    |            |

| 77           | TssH2doZ              | SS ↑ to SDO Output High-Impedance                           |             | 10            | 50  | ns    |            |

| 80           | TscH2doV,             | SDO Data Output Valid after SCK Edge PIC18FXX31             |             | _             | 50  | ns    |            |

|              | TscL2doV              |                                                             | PIC18LFXX31 | _             | 100 | ns    | ]          |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                         |             | 1.5 Tcy + 40  | _   | ns    |            |

Requires the use of Parameter 73A. Note 1:

2: Only if Parameter 71A and 72A are used.