Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2431-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

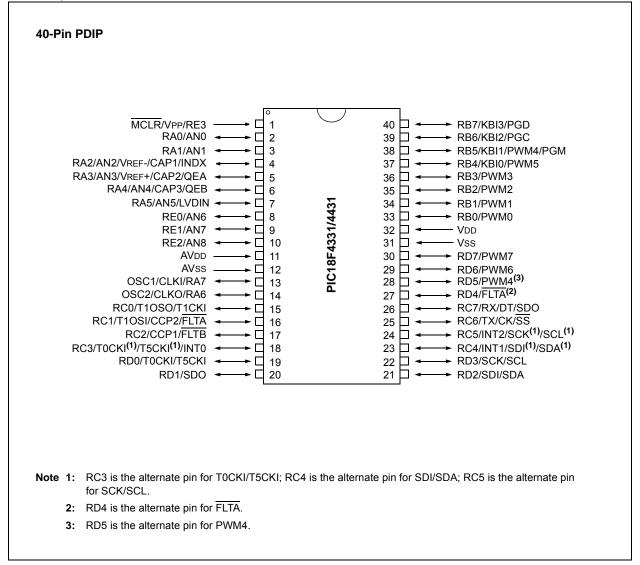

#### **Pin Diagrams (Continued)**

| Pin Name                                                                    | Pin Number Pi |                        |     | Pin                    | Buffer                             | Description                                                                                                                                                      |

|-----------------------------------------------------------------------------|---------------|------------------------|-----|------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                    | PDIP          | TQFP                   | QFN | Туре                   | Туре                               | Description                                                                                                                                                      |

|                                                                             |               |                        |     |                        |                                    | PORTC is a bidirectional I/O port.                                                                                                                               |

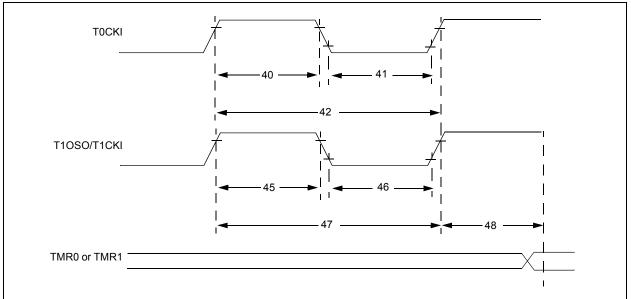

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI                                    | 15            | 32                     | 34  | I/O<br>O<br>I          | ST<br>—<br>ST                      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.                                                                                        |

| RC1/T1OSI/CCP2/<br>FLTA                                                     | 16            | 35                     | 35  |                        | -                                  |                                                                                                                                                                  |

| RC1<br>T1OSI<br><u>CCP2</u><br>FLTA                                         |               |                        |     | I/O<br>I<br>I/O<br>I   | ST<br>CMOS<br>ST<br>ST             | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input, Compare 2 output, PWM2 output.<br>Fault interrupt input pin.                                        |

| RC2/CCP1/FLTB<br>RC2<br>CCP1<br>FLTB                                        | 17            | 36                     | 36  | I/O<br>I/O<br>I        | ST<br>ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Fault interrupt input pin.                                                                      |

| RC3/T0CKI/T5CKI/<br>INT0                                                    | 18            | 37                     | 37  |                        |                                    |                                                                                                                                                                  |

| RC3<br>T0CKI <sup>(1)</sup><br>T5CKI <sup>(1)</sup><br>INT0                 |               |                        |     | I/O<br>I<br>I          | ST<br>ST<br>ST<br>ST               | Digital I/O.<br>Timer0 alternate clock input.<br>Timer5 alternate clock input.<br>External Interrupt 0.                                                          |

| RC4/INT1/SDI/SDA<br>RC4<br>INT1<br>SDI <sup>(1)</sup><br>SDA <sup>(1)</sup> | 23            | 42                     | 42  | I/O<br>I<br>I<br>I/O   | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 1.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |

| RC5/INT2/SCK/SCL<br>RC5<br>INT2<br>SCK <sup>(1)</sup><br>SCL <sup>(1)</sup> | 24            | 43                     | 43  | I/O<br>I<br>I/O<br>I/O | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 2.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |

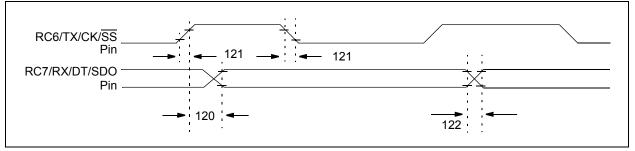

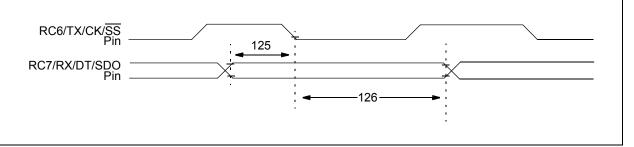

| RC6/TX/CK/ <del>SS</del><br>RC6<br>TX<br><u>CK</u><br>SS                    | 25            | 44                     | 44  | I/O<br>O<br>I/O<br>I   | ST<br>—<br>ST<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>SPI slave select input.                                        |

| RC7/RX/DT/SDO<br>RC7<br>RX<br>DT<br>SDO <sup>(1)</sup>                      | 26            | 1                      | 1   | I/O<br>I<br>I/O<br>O   | ST<br>ST<br>ST                     | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>SPI data out.                                                    |

| Legend: TTL = TTL<br>ST = Schi<br>O = Outp                                  | mitt Tri      | atible inp<br>gger inp |     | CMOS                   | levels                             | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |

#### **TABLE 1-3:** PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED)

for SCK/SCL; RC7 is the alternate pin for SDO.

**2:** RD4 is the alternate pin for  $\overline{FLTA}$ .

3: RD5 is the alternate pin for PWM4.

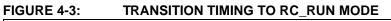

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes, after an interval of TIOBST.

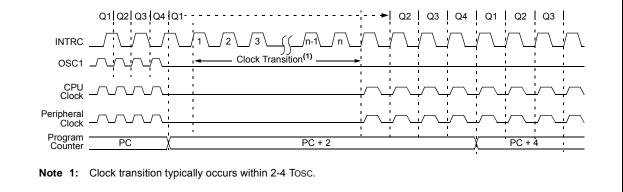

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

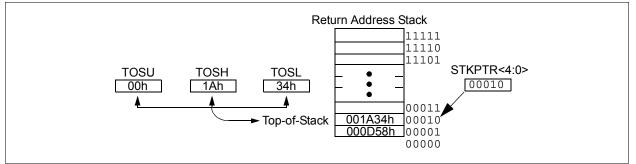

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset as the contents of the SFRs are not affected.

## FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| R/C-0                 | R/C-0                 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------------------|-----------------------|-----|-------|-------|-------|-------|-------|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —   | SP4   | SP3   | SP2   | SP1   | SP0   |

| bit 7                 |                       |     |       |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack became full or overflowed</li> <li>0 = Stack has not become full or overflowed</li> </ul> |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                                              |

|         | 1 = Stack underflow occurred                                                                                 |

|         | 0 = Stack underflow did not occur                                                                            |

| bit 5   | Unimplemented: Read as '0'                                                                                   |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                                                         |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

| R/W-1                 | R/W-1         | R/W-1                             | R/W-1             | U-0                               | R/W-1            | U-0            | R/W-1  |

|-----------------------|---------------|-----------------------------------|-------------------|-----------------------------------|------------------|----------------|--------|

| RBPU                  | INTEDG0       | INTEDG1                           | INTEDG2           | _                                 | TMR0IP           | _              | RBIP   |

| bit 7                 |               |                                   |                   |                                   |                  |                | bit C  |

| Levende               |               |                                   |                   |                                   |                  |                |        |

| Legend:<br>R = Readab | la hit        | W = Writable                      | hit               | II – Unimplon                     | nented bit, read | 1 00 '0'       |        |

| -n = Value at         |               | '1' = Bit is set                  |                   | $0^{\circ} = \text{Bit is clear}$ |                  | x = Bit is unk | 2014/2 |

| -n = value a          | IPUR          | I = DILIS SEL                     |                   |                                   | areu             | x = bit is unk | nown   |

| bit 7                 | RBPU: PORT    | B Pull-up Enal                    | ole bit           |                                   |                  |                |        |

|                       |               | B pull-ups are                    |                   |                                   |                  |                |        |

|                       | 0 = PORTB p   | oull-ups are ena                  | abled by individ  | lual port latch v                 | /alues           |                |        |

| bit 6                 | INTEDG0: Ex   | ternal Interrupt                  | 0 Edge Select     | bit                               |                  |                |        |

|                       |               | on rising edge                    |                   |                                   |                  |                |        |

|                       | -             | on falling edge                   |                   |                                   |                  |                |        |

| bit 5                 |               | ternal Interrupt                  | 1 Edge Select     | bit                               |                  |                |        |

|                       |               | on rising edge<br>on falling edge |                   |                                   |                  |                |        |

| bit 4                 | •             | •••                               |                   |                                   |                  |                |        |

| DIL 4                 |               | ternal Interrupt                  | 2 Euge Select     | DIL                               |                  |                |        |

|                       |               | on rising edge<br>on falling edge |                   |                                   |                  |                |        |

| bit 3                 | •             | ted: Read as '                    |                   |                                   |                  |                |        |

| bit 2                 | •             | R0 Overflow Int                   |                   | bit                               |                  |                |        |

|                       | 1 = High prio |                                   |                   |                                   |                  |                |        |

|                       | 0 = Low prior | •                                 |                   |                                   |                  |                |        |

| bit 1                 | Unimplemen    | ted: Read as '                    | י)                |                                   |                  |                |        |

| bit 0                 | RBIP: RB Po   | rt Change Inter                   | rupt Priority bit |                                   |                  |                |        |

|                       | 1 = High prio | rity                              |                   |                                   |                  |                |        |

|                       | 0 = Low prior | city.                             |                   |                                   |                  |                |        |

#### REGISTER 10-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## 11.5 PORTE, TRISE and LATE Registers

| Note: | PORTE is only available on PIC18F4331/ |

|-------|----------------------------------------|

|       | 4431 devices.                          |

PORTE is a 4-bit wide, bidirectional port. Three pins (RE0/AN6, RE1/AN7 and RE2/AN8) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On  | а    | Power-on     | Reset,   | RE<2:0> | are |

|-------|-----|------|--------------|----------|---------|-----|

|       | con | figu | ired as anal | og input | S.      |     |

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input only pin available for PIC18F4331/4431 devices. Its operation is controlled by the MCLRE Configuration bit

### REGISTER 11-1: TRISE REGISTER

in Configuration Register 3H (CONFIG3H<7>). When selected as a port pin (MCLRE = 0), it functions as a digital input-only pin. As such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's master clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as a<br>digital input only if Master Clear functionality |

|-------|----------------------------------------------------------------------------------------------|

|       | is disabled.                                                                                 |

| CLRF  | PORTE     | ; Initialize PORTE by |

|-------|-----------|-----------------------|

|       |           | ; clearing output     |

|       |           | ; data latches        |

| CLRF  | LATE      | ; Alternate method    |

|       |           | ; to clear output     |

|       |           | ; data latches        |

| MOVLW | 0x3F      | ; Configure A/D       |

| MOVWF | ANSEL0    | ; for digital inputs  |

| BCF   | ANSEL1, 0 | ;                     |

| MOVLW | 0x03      | ; Value used to       |

|       |           | ; initialize data     |

|       |           | ; direction           |

| MOVWF | TRISE     | ; Set RE<0> as input  |

|       |           | ; RE<1> as output     |

|       |           | ; RE<2> as input      |

| 1     |           |                       |

## 11.5.1 PORTE IN 28-PIN DEVICES

For PIC18F2331/2431 devices, PORTE is not available. It is only available for PIC18F4331/4431 devices.

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | _   | _   | _   | _   | TRISE2 | TRISE1 | TRISE0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'        |

|---------|-----------------------------------|

| bit 2   | TRISE2: RE2 Direction Control bit |

|         | 1 = Input                         |

|         | 0 = Output                        |

| bit 1   | TRISE1: RE1 Direction Control bit |

|         | 1 = Input                         |

|         | 0 = Output                        |

| bit 0   | TRISE0: RE0 Direction Control bit |

|         | 1 = Input                         |

|         | 0 = Output                        |

|         |                                   |

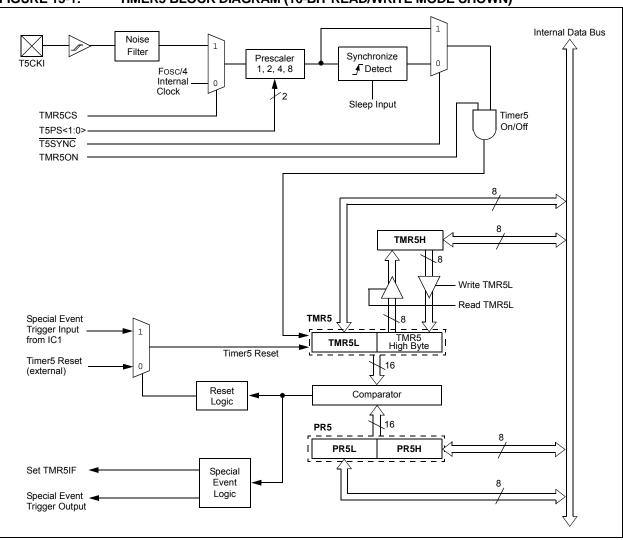

## 15.0 TIMER5 MODULE

The Timer5 module implements these features:

- 16-bit timer/counter operation

- Synchronous and Asynchronous Counter modes

- Continuous Count and Single-Shot Operating modes

- Four programmable prescaler values (1:1 to 1:8)

- · Interrupt generated on period match

- Special Event Trigger Reset function

- Double-buffered registers

- Operation during Sleep

- · CPU wake-up from Sleep

- Selectable hardware Reset input with a wake-up feature

Timer5 is a general purpose timer/counter that incorporates additional features for use with the Motion Feedback Module (see **Section 17.0 "Motion Feedback Module**"). It may also be used as a general purpose timer or a Special Event Trigger delay timer. When used as a general purpose timer, it can be configured to generate a delayed Special Event Trigger (e.g., an ADC Special Event Trigger) using a preprogrammed period delay.

Timer5 is controlled through the Timer5 Control register (T5CON), shown in Register 15-1. The timer can be enabled or disabled by setting or clearing the control bit TMR5ON (T5CON<0>).

A block diagram of Timer5 is shown in Figure 15-1.

## REGISTER 15-1: T5CON: TIMER5 CONTROL REGISTER

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0  | R/W-0  |

|-------|----------------------|-------|-------|-------|-----------------------|--------|--------|

| T5SEN | RESEN <sup>(1)</sup> | T5MOD | T5PS1 | T5PS0 | T5SYNC <sup>(2)</sup> | TMR5CS | TMR5ON |

| bit 7 |                      |       |       |       |                       |        | bit 0  |

| R = Readable b  | bit W = Writable bit                                                                          | U = Unimplemented bit,        | read as '0'        |

|-----------------|-----------------------------------------------------------------------------------------------|-------------------------------|--------------------|

| -n = Value at P | OR '1' = Bit is set                                                                           | '0' = Bit is cleared          | x = Bit is unknowr |

| bit 7           | <b>15SEN:</b> Timer5 Sleep Enable bit                                                         |                               |                    |

|                 | <ul> <li>Timer5 is enabled during Sleep</li> <li>Timer5 is disabled during Sleep</li> </ul>   |                               |                    |

| bit 6           | RESEN: Special Event Trigger Reset E                                                          | Enable bit <sup>(1)</sup>     |                    |

|                 | L = Special Event Trigger Reset is dis<br>D = Special Event Trigger Reset is ena              |                               |                    |

| bit 5           | <b>[5MOD:</b> Timer5 Mode bit                                                                 |                               |                    |

|                 | <ul><li>L = Single-Shot mode is enabled</li><li>D = Continuous Count mode is enable</li></ul> | d                             |                    |

| bit 4-3         | <b>[5PS&lt;1:0&gt;:</b> Timer5 Input Clock Presc                                              | ale Select bits               |                    |

|                 | 11 = 1:8<br>10 = 1:4<br>01 = 1:2                                                              |                               |                    |

| -               | 00 = 1:1<br><b>F5SYNC:</b> Timer5 External Clock Input                                        | Synchronization Salact hit(2) |                    |

|                 | When TMR5CS = 1:                                                                              | Synchronization Select bit.   |                    |

|                 | L = Do not synchronize external clock                                                         | input                         |                    |

| (               | = Synchronize external clock input                                                            |                               |                    |

|                 | When TMR5CS = 0:                                                                              |                               | _                  |

|                 | This bit is ignored. Timer5 uses the inter-                                                   |                               | ).                 |

|                 | <b>TMR5CS:</b> Timer5 Clock Source Select                                                     |                               |                    |

|                 | <ul> <li>External clock from the T5CKI pin</li> <li>Internal clock (TCY)</li> </ul>           |                               |                    |

| bit 0           | FMR5ON: Timer5 On bit                                                                         |                               |                    |

|                 | <ul><li>L = Timer5 is enabled</li><li>D = Timer5 is disabled</li></ul>                        |                               |                    |

| Note 1: The     | se bits are not implemented on PIC18                                                          | F2331/2431 devices and read   | <b>as</b> '0'.     |

| <b>2:</b> For   | Timer5 to operate during Sleep mode.                                                          | T5SYNC must be set.           |                    |

2: For Timer5 to operate during Sleep mode, T5SYNC must be set.

## FIGURE 15-1: TIMER5 BLOCK DIAGRAM (16-BIT READ/WRITE MODE SHOWN)

## 15.1 Timer5 Operation

Timer5 combines two 8-bit registers to function as a 16-bit timer. The TMR5L register is the actual low byte of the timer; it can be read and written to directly. The high byte is contained in an unmapped register; it is read and written to through TMR5H, which serves as a buffer. Each register increments from 00h to FFh.

A second register pair, PR5H and PR5L, serves as the Period register; it sets the maximum count for the TMR5 register pair. When TMR5 reaches the value of PR5, the timer rolls over to 00h and sets the TMR5IF interrupt flag. A simplified block diagram of the Timer5 module is shown in Figure 2-1.

| Note: | The Timer5 may be used as a general pur-    |        |          |        |        |  |  |

|-------|---------------------------------------------|--------|----------|--------|--------|--|--|

|       | pose timer and as the time base resource to |        |          |        |        |  |  |

|       | the                                         | Motion | Feedback | Module | (Input |  |  |

|       | Capture or Quadrature Encoder Interface).   |        |          |        |        |  |  |

Timer5 supports three configurations:

- 16-Bit Synchronous Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

In Synchronous Timer configuration, the timer is clocked by the internal device clock. The optional Timer5 prescaler divides the input by 2, 4, 8 or not at all (1:1). The TMR5 register pair increments on Q1. Clearing TMR5CS (= 0) selects the internal device clock as the timer sampling clock.

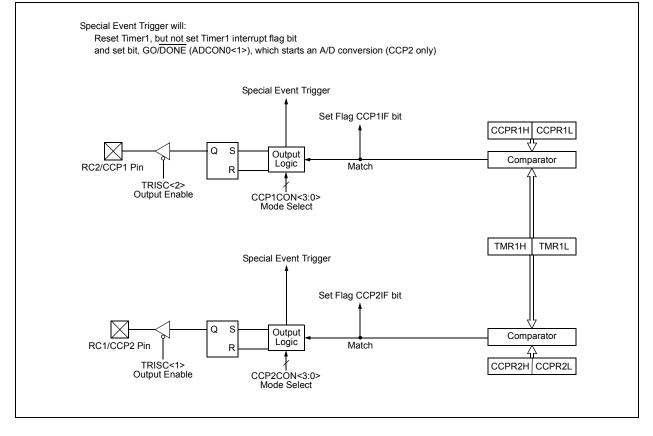

## 16.4 Compare Mode

In Compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 (RC1/CCP2) pin:

- is driven high

- is driven low

- toggles output (high-to-low or low-to-high)

- remains unchanged (interrupt only)

The action on the pin is based on the value of control bits, CCP1M<3:0> (CCP2M<3:0>). At the same time, interrupt flag bit CCP1IF (CCP2IF) is set.

#### 16.4.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISC bit.

Note: Clearing the CCPxCON register will force the RC1 or RC2 compare output latch to the default low level. This is not the PORTC I/O data latch.

### 16.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.4.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 16.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP2 resets the TMR1 register pair. Additionally, the CCP2 Special Event Trigger will start an A/D conversion if the A/D module is enabled.

Note: The Special Event Trigger from the CCP2 module will not set the Timer1 interrupt flag bit.

### FIGURE 16-2: COMPARE MODE OPERATION BLOCK DIAGRAM

| BRFEN<br>bit 7<br>Legend:<br>R = Readab<br>-n = Value a<br>bit 7<br>bit 6<br>bit 5<br>bit 5 | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | OD = 0, cleared<br>OD = 1, cleared                                                                                                                                                                                                               | ble bit<br>a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive | '0' = Bit is cle<br>(i.e., only when<br>at beginning o<br>e for the remain | The new period<br>f the new period | x = Bit is unkn                    | deasserted        |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------|------------------------------------|-------------------|

| Legend:<br>R = Readab<br>-n = Value a<br>bit 7<br>bit 6<br>bit 5                            | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | '1' = Bit is set<br>akpoint Fault Ena<br>fault condition on<br>Fault condition<br>t B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c | ble bit<br>a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive | '0' = Bit is cle<br>(i.e., only when<br>at beginning o<br>e for the remain | n PWMPIN = 1<br>f the new perio    | x = Bit is unkn                    | own<br>deasserted |

| R = Readab<br>-n = Value a<br>bit 7<br>bit 6<br>bit 5                                       | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | '1' = Bit is set<br>akpoint Fault Ena<br>fault condition on<br>Fault condition<br>t B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c | ble bit<br>a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive | '0' = Bit is cle<br>(i.e., only when<br>at beginning o<br>e for the remain | n PWMPIN = 1<br>f the new perio    | x = Bit is unkn                    | deasserted        |

| R = Readab<br>-n = Value a<br>bit 7<br>bit 6<br>bit 5                                       | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | '1' = Bit is set<br>akpoint Fault Ena<br>fault condition on<br>Fault condition<br>t B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c | ble bit<br>a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive | '0' = Bit is cle<br>(i.e., only when<br>at beginning o<br>e for the remain | n PWMPIN = 1<br>f the new perio    | x = Bit is unkn                    | deasserted        |

| <u>-n = Value a</u><br>bit 7<br>bit 6<br>bit 5                                              | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | '1' = Bit is set<br>akpoint Fault Ena<br>fault condition on<br>Fault condition<br>t B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c | ble bit<br>a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive | '0' = Bit is cle<br>(i.e., only when<br>at beginning o<br>e for the remain | n PWMPIN = 1<br>f the new perio    | x = Bit is unkn                    | deasserted        |

| bit 7<br>bit 6<br>bit 5                                                                     | BRFEN: Brea<br>1 = Enable F<br>0 = Disable F<br>FLTBS: Fault<br>1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                | akpoint Fault Ena<br>Fault condition on<br>Fault condition<br>t B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                      | a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive            | (i.e., only when<br>at beginning o<br>e for the remain                     | The new period<br>f the new period | L)<br>od when $\overline{FLTB}$ is | deasserted        |

| bit 6<br>bit 5                                                                              | <ul> <li>1 = Enable F</li> <li>0 = Disable F</li> <li>FLTBS: Fault</li> <li>1 = FLTB is a if FLTBM</li> <li>if FLTBM</li> <li>0 = No Fault</li> <li>FLTBMOD: F</li> <li>1 = Cycle-by is deasse</li> <li>0 = Inactive</li> </ul> | ault condition on<br>Fault condition<br>B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                             | a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive            | at beginning o<br>e for the remain                                         | f the new perio                    | od when $\overline{FLTB}$ is       |                   |

| bit 5                                                                                       | <ul> <li>1 = Enable F</li> <li>0 = Disable F</li> <li>FLTBS: Fault</li> <li>1 = FLTB is a if FLTBM</li> <li>if FLTBM</li> <li>0 = No Fault</li> <li>FLTBMOD: F</li> <li>1 = Cycle-by is deasse</li> <li>0 = Inactive</li> </ul> | ault condition on<br>Fault condition<br>B Status bit <sup>(1)</sup><br>asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1)</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                             | a breakpoint<br>by the user;<br>automatically<br>)<br>ns are inactive            | at beginning o<br>e for the remain                                         | f the new perio                    | od when $\overline{FLTB}$ is       |                   |

| bit 5                                                                                       | 1 = FLTB is a<br>if FLTBM<br>if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                                                                                | asserted:<br>IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                                                                                                     | automatically<br>)<br>ns are inactive                                            | e for the remain                                                           | nder of the cur                    |                                    |                   |

|                                                                                             | if FLTBM<br>if FLTBM<br>0 = No Fault<br><b>FLTBMOD:</b> F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                                                                                          | IOD = 0, cleared<br>IOD = 1, cleared<br>Fault B Mode bit <sup>(1</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                                                                                                                  | automatically<br>)<br>ns are inactive                                            | e for the remain                                                           | nder of the cur                    |                                    |                   |

|                                                                                             | if FLTBM<br>0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                                                                                                             | IOD = 1, cleared<br>Fault B Mode bit <sup>(1</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                                                                                                                                      | automatically<br>)<br>ns are inactive                                            | e for the rema <u>i</u> r                                                  | nder of the cur                    |                                    |                   |

|                                                                                             | 0 = No Fault<br>FLTBMOD: F<br>1 = Cycle-by<br>is deasse<br>0 = Inactive                                                                                                                                                         | ault B Mode bit <sup>(1</sup><br>-Cycle mode: Pir<br>erted; FLTBS is c                                                                                                                                                                           | )<br>ns are inactiv                                                              | e for the rema <u>i</u> r                                                  | nder of the cur                    |                                    |                   |

|                                                                                             | 1 = Cycle-by<br>is deasse<br>0 = Inactive                                                                                                                                                                                       | -Cycle mode: Pir<br>erted; FLTBS is c                                                                                                                                                                                                            | ns are inactiv                                                                   |                                                                            |                                    | rrent PWM period                   | វ or until FLTB   |

| bit 4                                                                                       | is deasse<br>0 = Inactive                                                                                                                                                                                                       | erted; FLTBS is c                                                                                                                                                                                                                                |                                                                                  |                                                                            |                                    | rrent PWM period                   | d or until FLTB   |

| bit 4                                                                                       | 0 = Inactive                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                  | leared autom                                                                     | atically when E                                                            | ·                                  |                                    |                   |

| bit 4                                                                                       |                                                                                                                                                                                                                                 | mode: Pins are o                                                                                                                                                                                                                                 |                                                                                  |                                                                            |                                    |                                    |                   |

| bit 4                                                                                       |                                                                                                                                                                                                                                 | by the user only                                                                                                                                                                                                                                 | deactivated (                                                                    | catastrophic fai                                                           | lure) until FLI                    | B is deasserted                    | and FLIBS is      |

|                                                                                             |                                                                                                                                                                                                                                 | ult B Enable bit <sup>(1)</sup>                                                                                                                                                                                                                  | 1                                                                                |                                                                            |                                    |                                    |                   |

|                                                                                             | 1 = Enable F                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                  |                                                                            |                                    |                                    |                   |

|                                                                                             | 0 = Disable F                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                  |                                                                                  |                                                                            |                                    |                                    |                   |

| bit 3                                                                                       |                                                                                                                                                                                                                                 | ult Configuration                                                                                                                                                                                                                                |                                                                                  |                                                                            |                                    |                                    |                   |

|                                                                                             |                                                                                                                                                                                                                                 | TB or both deact                                                                                                                                                                                                                                 |                                                                                  | M outputs                                                                  |                                    |                                    |                   |

| bit 2                                                                                       | 0 = FLIA or I                                                                                                                                                                                                                   | FLTB deactivates                                                                                                                                                                                                                                 | 5 PVVIVI<5:0>                                                                    |                                                                            |                                    |                                    |                   |

| DILZ                                                                                        | 1 = FLTA is a                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                  |                                                                                  |                                                                            |                                    |                                    |                   |

|                                                                                             |                                                                                                                                                                                                                                 | OD = 0, cleared                                                                                                                                                                                                                                  | by the user;                                                                     |                                                                            |                                    |                                    |                   |

|                                                                                             |                                                                                                                                                                                                                                 | OD = 1, cleared                                                                                                                                                                                                                                  | automatically                                                                    | at beginning o                                                             | f the new perio                    | od when FLTA is                    | deasserted        |

|                                                                                             | 0 = No Fault                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                  |                                                                            |                                    |                                    |                   |

| bit 1                                                                                       | -                                                                                                                                                                                                                               | ault A Mode bit                                                                                                                                                                                                                                  | a ara ina ativ                                                                   | for the remain                                                             | day of the aver                    | ant DW/M namiad                    |                   |

|                                                                                             |                                                                                                                                                                                                                                 | -Cycle mode: Pin<br>ed; FLTAS is clea                                                                                                                                                                                                            |                                                                                  |                                                                            | der of the curre                   | ent Prvivi period d                |                   |

|                                                                                             | 0 = Inactive                                                                                                                                                                                                                    | mode: Pins are only                                                                                                                                                                                                                              |                                                                                  |                                                                            | lure) until FLT                    | A is deasserted                    | and FLTAS is      |

| bit 0                                                                                       |                                                                                                                                                                                                                                 | ult A Enable bit                                                                                                                                                                                                                                 |                                                                                  |                                                                            |                                    |                                    |                   |

|                                                                                             | 1 = Enable F<br>0 = Disable F                                                                                                                                                                                                   |                                                                                                                                                                                                                                                  |                                                                                  |                                                                            |                                    |                                    |                   |

| Note 1: U                                                                                   | Jnimplemented                                                                                                                                                                                                                   | l in PIC18F2331/2                                                                                                                                                                                                                                | 2431 devices                                                                     | : maintain these                                                           | e bits clear.                      |                                    |                   |

| <b>2:</b> P                                                                                 | PWM<7:6> are                                                                                                                                                                                                                    | implemented only<br>N has no effect.                                                                                                                                                                                                             |                                                                                  |                                                                            |                                    | F2331/2431 devi                    | ces, setting or   |

## REGISTER 18-8: FLTCONFIG: FAULT CONFIGURATION REGISTER

## 18.13 PWM Update Lockout

For a complex PWM application, the user may need to write up to four Duty Cycle registers and the PWM Time Base Period register, PTPER, at a given time. In some applications, it is important that all buffer registers be written before the new duty cycle and period values are loaded for use by the module.

A PWM update lockout feature may optionally be enabled so the user may specify when new duty cycle buffer values are valid. The PWM update lockout feature is enabled by setting the control bit, UDIS, in the PWMCON1 register. This bit affects all Duty Cycle Buffer registers and the PWM Time Base Period register, PTPER.

To perform a PWM update lockout:

- 1. Set the UDIS bit.

- 2. Write all Duty Cycle registers and PTPER, if applicable.

- 3. Clear the UDIS bit to re-enable updates.

- 4. With this, when UDIS bit is cleared, the buffer values will be loaded to the actual registers. This makes a synchronous loading of the registers.

## 18.14 PWM Special Event Trigger

The PWM module has a Special Event Trigger capability that allows A/D conversions to be synchronized to the PWM time base. The A/D sampling and conversion time may be programmed to occur at any point within the PWM period. The Special Event Trigger allows the user to minimize the delay between the time when A/D conversion results are acquired and the time when the duty cycle value is updated.

The PWM 16-bit Special Event Trigger register, SEVTCMP (high and low), and five control bits in the PWMCON1 register are used to control its operation.

The PTMR value for which a Special Event Trigger should occur is loaded into the SEVTCMP register pair. The SEVTDIR bit in the PWMCON1 register specifies the counting phase when the PWM time base is in a Continuous Up/Down Count mode.

If the SEVTDIR bit is cleared, the Special Event Trigger will occur on the upward counting cycle of the PWM time base. If SEVTDIR is set, the Special Event Trigger will occur on the downward count cycle of the PWM time base. The SEVTDIR bit has effect only when the PWM timer is in the Continuous Up/Down Count mode.

## 18.14.1 SPECIAL EVENT TRIGGER ENABLE

The PWM module will always produce Special Event Trigger pulses. This signal may optionally be used by the A/D module. Refer to **Section 21.0 "10-Bit High-Speed Analog-to-Digital Converter (A/D) Module"** for details.

#### 18.14.2 SPECIAL EVENT TRIGGER POSTSCALER

The PWM Special Event Trigger has a postscaler that allows a 1:1 to 1:16 postscale ratio. The postscaler is configured by writing the SEVOPS<3:0> control bits in the PWMCON1 register.

The Special Event Trigger output postscaler is cleared on any write to the SEVTCMP register pair, or on any device Reset.

| Name                    | Bit 7                                               | Bit 6                                 | Bit 5                  | Bit 4                 | Bit 3                                                | Bit 2        | Bit 1         | Bit 0  | Reset<br>Values<br>on Page: |

|-------------------------|-----------------------------------------------------|---------------------------------------|------------------------|-----------------------|------------------------------------------------------|--------------|---------------|--------|-----------------------------|

| INTCON                  | GIE/GIEH                                            | PEIE/GIEL                             | TMR0IE                 | INT0IE                | RBIE                                                 | TMR0IF       | INT0IF        | RBIF   | 54                          |

| IPR3                    | _                                                   | _                                     | _                      | PTIP                  | IC3DRIP                                              | IC2QEIP      | IC1IP         | TMR5IP | 56                          |

| PIE3                    | _                                                   | _                                     | _                      | PTIE                  | IC3DRIE                                              | IC2QEIE      | IC1IE         | TMR5IE | 56                          |

| PIR3                    | —                                                   | _                                     | _                      | PTIF                  | IC3DRIF                                              | IC2QEIF      | IC1IF         | TMR5IF | 56                          |

| PTCON0                  | PTOPS3                                              | PTOPS2                                | PTOPS1                 | PTOPS0                | PTCKPS1                                              | PTCKPS0      | PTMOD1        | PTMOD0 | 58                          |

| PTCON1                  | PTEN                                                | PTDIR                                 | _                      | _                     | _                                                    | _            | _             | _      | 58                          |

| PTMRL <sup>(1)</sup>    | PWM Time                                            | PWM Time Base Register (lower 8 bits) |                        |                       |                                                      |              |               |        | 58                          |

| PTMRH <sup>(1)</sup>    |                                                     | UN                                    | USED                   |                       | PWM Time                                             | Base Registe | er (upper 4 b | oits)  | 58                          |

| PTPERL <sup>(1)</sup>   | PWM Time Base Period Register (lower 8 bits)        |                                       |                        |                       |                                                      |              |               | 58     |                             |

| PTPERH <sup>(1)</sup>   | UNUSED PWM Time Base Period Register (upper 4 bits) |                                       |                        |                       |                                                      |              | 58            |        |                             |

| SEVTCMPL <sup>(1)</sup> | PWM Special Event Compare Register (lower 8 bits)   |                                       |                        |                       |                                                      |              |               | 58     |                             |

| SEVTCMPH <sup>(1)</sup> | UNUSED                                              |                                       |                        |                       | PWM Special Event Compare Register<br>(upper 4 bits) |              |               |        | 58                          |

| PWMCON0                 | —                                                   | PWMEN2                                | PWMEN1                 | PWMEN0                | PMOD3 <sup>(2)</sup>                                 | PMOD2        | PMOD1         | PMOD0  | 58                          |

| PWMCON1                 | SEVOPS3                                             | SEVOPS2                               | SEVOPS1                | SEVOPS0               | SEVTDIR                                              | —            | UDIS          | OSYNC  | 58                          |

| DTCON                   | DTPS1                                               | DTPS0                                 | DT5                    | DT4                   | DT3                                                  | DT2          | DT1           | DT0    | 58                          |

| FLTCONFIG               | BRFEN                                               | FLTBS <sup>(2)</sup>                  | FLTBMOD <sup>(2)</sup> | FLTBEN <sup>(2)</sup> | FLTCON                                               | FLTAS        | FLTAMOD       | FLTAEN | 58                          |

| OVDCOND                 | POVD7 <sup>(2)</sup>                                | POVD6 <sup>(2)</sup>                  | POVD5                  | POVD4                 | POVD3                                                | POVD2        | POVD1         | POVD0  | 58                          |

| OVDCONS                 | POUT7 <sup>(2)</sup>                                | POUT6 <sup>(2)</sup>                  | POUT5                  | POUT4                 | POUT3                                                | POUT2        | POUT1         | POUT0  | 58                          |

| PDC0L <sup>(1)</sup>    | PWM Duty                                            | Cycle #0L Re                          | gister (lower 8        | bits)                 |                                                      |              |               |        | 58                          |

| PDC0H <sup>(1)</sup>    | UNU                                                 | ISED                                  | PWM Duty Cy            | /cle #0H Regi         | ster (upper 6                                        | bits)        |               |        | 58                          |

| PDC1L <sup>(1)</sup>    | PWM Duty                                            | Cycle #1L rec                         | gister (lower 8 l      | bits)                 |                                                      |              |               |        | 58                          |

| PDC1H <sup>(1)</sup>    | UNU                                                 | ISED                                  | PWM Duty Cy            | /cle #1H Regi         | ster (upper 6                                        | bits)        |               |        | 58                          |

| PDC2L <sup>(1)</sup>    | PWM Duty                                            | Cycle #2L Re                          | gister (lower 8        | bits)                 |                                                      |              |               |        | 58                          |

| PDC2H <sup>(1)</sup>    | UNU                                                 | ISED                                  | PWM Duty Cy            | cle #2H Regi          | ster (upper 6                                        | bits)        |               |        | 58                          |

| PDC3L <sup>(1,2)</sup>  | PWM Duty                                            | Cycle #3L Re                          | gister (lower 8        | bits)                 |                                                      |              |               |        | 58                          |

| PDC3H <sup>(1,2)</sup>  | UNU                                                 | ISED                                  | PWM Duty Cy            | cle #3H Regi          | ster (upper 6                                        | bits)        |               |        | 58                          |

#### TABLE 18-6: REGISTERS ASSOCIATED WITH THE POWER CONTROL PWM MODULE

Legend: — = Unimplemented, read as '0'. Shaded cells are not used with the power control PWM.

Note 1: Double-buffered register pairs. Refer to text for explanation of how these registers are read and written to.

2: Unimplemented in PIC18F2331/2431 devices; maintain these bits clear. Reset values shown are for PIC18F4331/4431 devices.

#### REGISTER 19-2: SSPCON: SYNCHRONOUS SERIAL PORT CONTROL REGISTER (CONTINUED)

- bit 3-0 SSPM<3:0>: Synchronous Serial Port Mode Select bits<sup>(3)</sup>

- 0000 = SPI Master mode, Clock = Fosc/4

- 0001 = SPI Master mode, Clock = Fosc/16

- 0010 = SPI Master mode, Clock = Fosc/64

- 0011 = SPI Master mode, Clock = TMR2 output/2

- 0100 = SPI Slave mode, Clock = SCK pin,  $\overline{SS}$  pin control enabled

- 0101 = SPI Slave mode, Clock = SCK pin, SS pin control disabled, SS can be used as I/O pin

- 0110 =  $I^2C$  Slave mode, 7-bit address

- 0111 =  $I^2C$  Slave mode, 10-bit address

- $1011 = I^2_{C}$  Firmware Controlled Master mode (slave Idle)

- 1110 =  $I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- 1111 =  $I^2C$  Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- **Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{\text{TM}}$  mode only.

## 20.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules available in the PIC18F2331/ 2431/4331/4431 family of microcontrollers. EUSART is also known as a Serial Communications Interface or SCI.

The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The EUSART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These features make it ideally suited for use in Local Interconnect Network (LIN/J2602) bus systems.

The EUSART can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

In order to configure pins, TX and RX, as the Enhanced Universal Synchronous Asynchronous Receiver Transmitter:

- SPEN (RCSTA<7>) bit must be set ( = 1),

- TRISC<6> bit must be set ( = 1), and

- TRISC<7> bit must be set ( = 1).

| Note: | The EUSART control will automatically       |

|-------|---------------------------------------------|

|       | reconfigure the pin from input to output as |

|       | needed.                                     |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 20-1, Register 20-2 and Register 20-3, respectively.

## 20.1 Asynchronous Operation in Power-Managed Modes

The EUSART may operate in Asynchronous mode while the peripheral clocks are being provided by the internal oscillator block. This makes it possible to remove the crystal or resonator that is commonly connected as the primary clock on the OSC1 and OSC2 pins.

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz (see Table 26-6). However, this frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output back to 8 MHz. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source (see **Section 3.6.4 "INTOSC Frequency Drift"** for more information).

The other method adjusts the value in the Baud Rate Generator (BRG). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

## 21.1 Configuring the A/D Converter

The A/D Converter has two types of conversions, two modes of operation and eight different Sequencing modes. These features are controlled by the ACONV bit (ADCON0<5>), ACSCH bit (ADCON0<4>) and ACMOD<1:0> bits (ADCON0<3:2>). In addition, the A/D channels are divided into four groups as defined in the ADCHS register. Table 21-1 shows the sequence configurations as controlled by the ACSCH and ACMOD<1:0> bits.

#### 21.1.1 CONVERSION TYPE

Two types of conversions exist in the high-speed 10-bit A/D Converter module that are selected using the ACONV bit. Single-Shot mode allows a single conversion or sequence to be enabled when ACONV = 0. At the end of the sequence, the  $GO/\overline{DONE}$  bit will be automatically cleared and the interrupt flag, ADIF, will be set. When using Single-Shot mode and configured for Simultaneous mode, STNM2, acquisition time must be used to ensure proper conversion of the analog input signals.

Continuous Loop mode allows the defined sequence to be executed in a continuous loop when ACONV = 1. In this mode, either the user <u>can</u> trigger the start of conversion by setting the GO/DONE bit, or one of the A/D triggers can start the conversion. The interrupt flag, ADIF, is set based on the configuration of the bits, ADRS<1:0> (ADCON3<7:6>). In Simultaneous modes, STNM1 and STNM2 acquisition time must be configured to ensure proper conversion of the analog input signals.

### 21.1.2 CONVERSION MODE

The ACSCH bit (ADCON0<4>) controls how many channels are used in the configured sequence. When clear, the A/D is configured for single channel conversion and will convert the group selected by the ACMOD<1:0> bits and the channel selected by the GxSEL<1:0> bits (ADCHS register). When ACSCH = 1, the A/D is configured for multiple channel conversion and the sequence is defined by ACMOD<1:0>.

| TABLE 21-1: | AUTO-CONVERSION SEQUENCE CONFIGURATIONS |

|-------------|-----------------------------------------|

|-------------|-----------------------------------------|

| Mode                                         | ACSCH | ACMOD<1:0> | Description                                                                                                                                                   |

|----------------------------------------------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|