Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

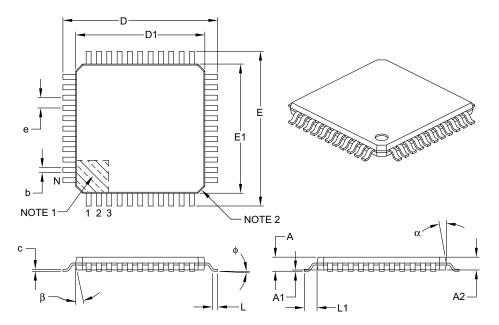

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN-S (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2431-i-mm |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

|                                                        | Pin Nu         | Pin Number |                      | Buffer                                                           |                                                                                                                  |  |  |

|--------------------------------------------------------|----------------|------------|----------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                               | SPDIP,<br>SOIC | QFN        | Pin<br>Type          |                                                                  | Description                                                                                                      |  |  |

|                                                        |                |            |                      |                                                                  | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |  |  |

| RB0/PWM0<br>RB0<br>PWM0                                | 21             | 18         | 1/O<br>O             | TTL<br>TTL                                                       | Digital I/O.<br>PWM Output 0.                                                                                    |  |  |

| RB1/PWM1<br>RB1<br>PWM1                                | 22             | 19         | 1/O<br>O             | TTL<br>TTL                                                       | Digital I/O.<br>PWM Output 1.                                                                                    |  |  |

| RB2/PWM2<br>RB2<br>PWM2                                | 23             | 20         | 1/O<br>O             | TTL<br>TTL                                                       | Digital I/O.<br>PWM Output 2.                                                                                    |  |  |

| RB3/PWM3<br>RB3<br>PWM3                                | 24             | 21         | 1/O<br>O             | TTL                                                              | Digital I/O.<br>PWM Output 3.                                                                                    |  |  |

| RB4/KBI0/PWM5<br>RB4<br>KBI0<br>PWM5                   | 25             | 22         | I/O<br>I<br>O        | TTL<br>TTL<br>TTL                                                | Digital I/O.<br>Interrupt-on-change pin.<br>PWM Output 5.                                                        |  |  |

| RB5/KBI1/PWM4/PGM<br>RB5<br>KBI1<br>PWM4<br>PGM        | 26             | 23         | I/O<br>I<br>O<br>I/O | TTL<br>TTL<br>TTL<br>ST                                          | Digital I/O.<br>Interrupt-on-change pin.<br>PWM Output 4.<br>Single-Supply ICSP™ Programming entry pin.          |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                     | 27             | 24         | 1/O<br>1<br>1/O      | TTL<br>TTL<br>ST                                                 | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                     | 28             | 25         | I/O<br>I<br>I/O      | TTL<br>TTL<br>ST                                                 | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |  |  |

| Legend: TTL = TTL comp<br>ST = Schmitt T<br>O = Output |                |            | CMO                  | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power |                                                                                                                  |  |  |

#### **TABLE 1-2:** PIC18F2331/2431 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name            | Pin Number |           |     | Pin  | Buffer | Description                                                      |

|---------------------|------------|-----------|-----|------|--------|------------------------------------------------------------------|

| Fill Name           | PDIP       | TQFP      | QFN | Туре | Туре   | Description                                                      |

|                     |            |           |     |      |        | PORTD is a bidirectional I/O port.                               |

| RD0/T0CKI/T5CKI     | 19         | 38        | 38  |      |        |                                                                  |

| RD0                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| TOCKI               |            |           |     | I    | ST     | Timer0 external clock input.                                     |

| T5CKI               |            |           |     | Ι    | ST     | Timer5 input clock.                                              |

| RD1/SDO             | 20         | 39        | 39  |      |        |                                                                  |

| RD1                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| SDO <sup>(1)</sup>  |            |           |     | 0    | —      | SPI data out.                                                    |

| RD2/SDI/SDA         | 21         | 40        | 40  |      |        |                                                                  |

| RD2                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| SDI <sup>(1)</sup>  |            |           |     | Ι    | ST     | SPI data in.                                                     |

| SDA <sup>(1)</sup>  |            |           |     | I/O  | ST     | I <sup>2</sup> C™ data I/O.                                      |

| RD3/SCK/SCL         | 22         | 41        | 41  |      |        |                                                                  |

| RD3                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| SCK <sup>(1)</sup>  |            |           |     | I/O  | ST     | Synchronous serial clock input/output for SPI mode.              |

| SCL <sup>(1)</sup>  |            |           |     | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RD4/FLTA            | 27         | 2         | 2   |      |        |                                                                  |

| RD4                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| FLTA <sup>(2)</sup> |            |           |     | Ι    | ST     | Fault interrupt input pin.                                       |

| RD5/PWM4            | 28         | 3         | 3   |      |        |                                                                  |

| RD5                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| PWM4 <sup>(3)</sup> |            |           |     | 0    | TTL    | PWM Output 4.                                                    |

| RD6/PWM6            | 29         | 4         | 4   |      |        |                                                                  |

| RD6                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| PWM6                |            |           |     | 0    | TTL    | PWM Output 6.                                                    |

| RD7/PWM7            | 30         | 5         | 5   |      |        |                                                                  |

| RD7                 |            |           |     | I/O  | ST     | Digital I/O.                                                     |

| PWM7                |            |           |     | 0    | TTL    | PWM Output 7.                                                    |

| Legend: TTL = TTL   | compa      | tible inp |     |      |        | CMOS = CMOS compatible input or output                           |

| TABLE 1-3: | PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (C | CONTINUED) |  |

|------------|--------------------------------------------|------------|--|

|            |                                            | ·•···••=•/ |  |

0

ST = Schmitt Trigger input with CMOS levels = Output

= Input L Ρ = Power

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL; RC7 is the alternate pin for SDO.

2: RD4 is the alternate pin for FLTA.

3: RD5 is the alternate pin for PWM4.

### 6.5.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 6-1 and Table 6-2.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's.

### TABLE 6-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2331/2431/4331/4431 DEVICES

| Address | Name                    | Address | Name                    | Address | Name    | Address | Name                 | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|---------|---------|----------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H  | F9Fh    | IPR1                 | F7Fh    | PTCON0               |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L  | F9Eh    | PIR1                 | F7Eh    | PTCON1               |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)             | FBDh    | CCP1CON | F9Dh    | PIE1                 | F7Dh    | PTMRL                |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H  | F9Ch    | (2)                  | F7Ch    | PTMRH                |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L  | F9Bh    | OSCTUNE              | F7Bh    | PTPERL               |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON | F9Ah    | ADCON3               | F7Ah    | PTPERH               |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | ANSEL1  | F99h    | ADCHS                | F79h    | PDC0L                |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ANSEL0  | F98h    | (2)                  | F78h    | PDC0H                |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | T5CON   | F97h    | (2)                  | F77h    | PDC1L                |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | QEICON  | F96h    | TRISE <sup>(3)</sup> | F76h    | PDC1H                |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | (2)     | F95h    | TRISD <sup>(3)</sup> | F75h    | PDC2L                |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | (2)     | F94h    | TRISC                | F74h    | PDC2H                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)     | F93h    | TRISB                | F73h    | PDC3L <sup>(3)</sup> |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | (2)     | F92h    | TRISA                | F72h    | PDC3H <sup>(3)</sup> |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | _(2)    | F91h    | PR5H                 | F71h    | SEVTCMPL             |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH  | F90h    | PR5L                 | F70h    | SEVTCMPH             |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG   | F8Fh    | (2)                  | F6Fh    | PWMCON0              |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG   | F8Eh    | (2)                  | F6Eh    | PWMCON1              |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG   | F8Dh    | LATE <sup>(3)</sup>  | F6Dh    | DTCON                |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA   | F8Ch    | LATD <sup>(3)</sup>  | F6Ch    | FLTCONFIG            |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA   | F8Bh    | LATC                 | F6Bh    | OVDCOND              |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | BAUDCON | F8Ah    | LATB                 | F6Ah    | OVDCONS              |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR   | F89h    | LATA                 | F69h    | CAP1BUFH             |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA  | F88h    | TMR5H                | F68h    | CAP1BUFL             |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2  | F87h    | TMR5L                | F67h    | CAP2BUFH             |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSPCON                  | FA6h    | EECON1  | F86h    | (2)                  | F66h    | CAP2BUFL             |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | (2)                     | FA5h    | IPR3    | F85h    | (2)                  | F65h    | CAP3BUFH             |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3    | F84h    | PORTE                | F64h    | CAP3BUFL             |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3    | F83h    | PORTD <sup>(3)</sup> | F63h    | CAP1CON              |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2    | F82h    | PORTC                | F62h    | CAP2CON              |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2    | F81h    | PORTB                | F61h    | CAP3CON              |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2    | F80h    | PORTA                | F60h    | DFLTCON              |

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available on 28-pin devices.

### 7.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available for the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation). The basic process is shown in Example 7-1.

### 7.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. The sequence in Example 7-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware. After a write sequence has been initiated, EECON1, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt or poll this bit. EEIF must be cleared by software.

### 7.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.6 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

### EXAMPLE 7-1: DATA EEPROM READ

MOVLW DATA\_EE\_ADDR MOVWF EEADR BCF EECON1, EEPGD BSF EECON1, RD MOVF EEDATA, W

; Data Memory Address to read ; Point to DATA memory ; EEPROM Read ; W = EEDATA

:

### EXAMPLE 7-2: DATA EEPROM WRITE

|          | MOVLW                                                 | DATA_EE_ADDR                                                                                             | ;                                                                                                                                       |

|----------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|          | MOVWF                                                 | EEADR                                                                                                    | ; Data Memory Address to write                                                                                                          |

|          | MOVLW                                                 | DATA_EE_DATA                                                                                             | ;                                                                                                                                       |

|          | MOVWF                                                 | EEDATA                                                                                                   | ; Data Memory Value to write                                                                                                            |

|          | BCF                                                   | EECON1, EEPGD                                                                                            | ; Point to DATA memory                                                                                                                  |

|          | BCF                                                   | EECON1, CFGS                                                                                             | ; Access EEPROM                                                                                                                         |

|          | BSF                                                   | EECON1, WREN                                                                                             | ; Enable writes                                                                                                                         |

|          | BCF                                                   | INTCON, GIE                                                                                              | ; Disable Interrupts                                                                                                                    |

|          | MOVLW                                                 | 55h                                                                                                      | ;                                                                                                                                       |

| Required | MOVWF                                                 | EECON2                                                                                                   | ; Write 55h                                                                                                                             |

| Sequence | MOVLW                                                 | 0AAh                                                                                                     | ;                                                                                                                                       |

|          | MOVWF                                                 | EECON2                                                                                                   | ; Write OAAh                                                                                                                            |

|          | BSF                                                   | EECON1, WR                                                                                               | ; Set WR bit to begin write                                                                                                             |

|          | BTFSC                                                 | EECON1, WR                                                                                               | ; Wait for write to complete                                                                                                            |

|          |                                                       |                                                                                                          |                                                                                                                                         |

|          | GOTO                                                  | \$-2                                                                                                     | ;                                                                                                                                       |

|          | BSF                                                   | INTCON, GIE                                                                                              | ; Enable interrupts                                                                                                                     |

| -        | BSF<br>BCF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>BTFSC | EECON1, WREN<br>INTCON, GIE<br>55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR<br>EECON1, WR<br>EECON1, WR | <pre>; Enable writes ; Disable Interrupts ; ; Write 55h ; ; Write 0AAh ; Set WR bit to begin write ; Wait for write to complete ;</pre> |

### REGISTER 8-1: EECON1: DATA EEPROM CONTROL REGISTER 1

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit (canne | ot be cleared in software) |                    |

|-------------------|-------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit      | , read as '0'      |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Access Flash program memory                                                                                                                                                                                |

|         | 0 = Access data EEPROM memory                                                                                                                                                                                  |

| bit 6   | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                    |

|         | 1 = Access Configuration registers                                                                                                                                                                             |

|         | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                 |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                               |

|         | 1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by                                                                                                                        |

|         | completion of erase operation)<br>0 = Perform write only                                                                                                                                                       |

| bit 3   |                                                                                                                                                                                                                |

| DILS    | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                 |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal<br/>operation, or an improper write attempt)</li> </ul>                                            |

|         | 0 = The write operation completed                                                                                                                                                                              |

| bit 2   | WREN: Flash Program/Data EEPROM Write Enable bit                                                                                                                                                               |

|         | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                           |

|         | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                         |

| bit 1   | WR: Write Control bit                                                                                                                                                                                          |

|         | 1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle                                                                                                                   |

|         | (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit                                                                                                             |

|         | can only be set (not cleared) in software.)<br>0 = Write cycle to the EEPROM is complete                                                                                                                       |

| bit 0   | RD: Read Control bit                                                                                                                                                                                           |

| DILU    |                                                                                                                                                                                                                |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)</li> </ul> |

|         | 0 = Does not initiate an EEPROM read                                                                                                                                                                           |

| Note 1. | When a WRERP assure the EERCD and CECS bits are not cleared. This allows tracing of the error                                                                                                                  |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

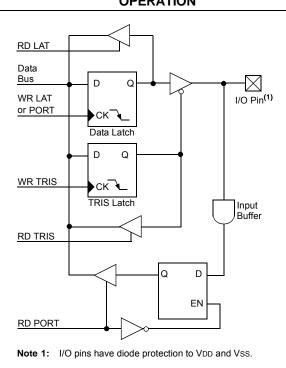

## 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port without the interfaces to other peripherals is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

### 11.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA<4:2> pins are multiplexed with three input capture pins and Quadrature Encoder Interface pins. Pins, RA6 and RA7, are multiplexed with the main oscillator pins. They are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see Section 23.1 "Configuration Bits" for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D Converter inputs is selected by clearing/setting the control bits in the ANSEL0 and ANSEL1 registers.

| Note 1: | On   | а   | Powe   | er-on | Rese    | et, R/  | ۹<5:( | 0> are           |

|---------|------|-----|--------|-------|---------|---------|-------|------------------|

|         | conf | īgu | red as | analo | og inpi | uts and | d rea | <b>d as</b> '0'. |

| 2:      |      |     |        |       |         | ,       | on    | 40-pin           |

|         | devi | ice | s (PIC | 18F4  | 331/4   | 431).   |       |                  |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| ł | EXAMPL | E 11-1: | INITIALIZING PORTA      |

|---|--------|---------|-------------------------|

|   | CLRF   | PORTA   | ; Initialize PORTA by   |

|   |        |         | ; clearing output       |

|   |        |         | ; data latches          |

|   | CLRF   | LATA    | ; Alternate method      |

|   |        |         | ; to clear output       |

|   |        |         | ; data latches          |

|   | MOVLW  | 0x3F    | ; Configure A/D         |

|   | MOVWF  | ANSEL0  | ; for digital inputs    |

|   | MOVLW  | 0xCF    | ; Value used to         |

|   |        |         | ; initialize data       |

|   |        |         | ; direction             |

|   | MOVWF  | TRISA   | ; Set RA<3:0> as inputs |

|   |        |         | ; RA<5:4> as outputs    |

| Pin           | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                            |

|---------------|---------------------|-----------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/PWM0      | RB0                 | 0               | 0   | DIG         | LATB<0> data output; not affected by analog input.                                                                     |

|               |                     | 1               | I   | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input is enabled.                  |

|               | PWM0                | 0               | 0   | DIG         | PWM Output 0.                                                                                                          |

| RB1/PWM1      | RB1                 | 0               | 0   | DIG         | LATB<1> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<1> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM1                | 0               | 0   | DIG         | PWM Output 1.                                                                                                          |

| RB2/PWM2      | RB2                 | 0               | 0   | DIG         | LATB<2> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<2> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM2                | 0               | 0   | DIG         | PWM Output 2.                                                                                                          |

| RB3/PWM3      | RB3                 | 0               | 0   | DIG         | LATB<3> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<3> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. |

|               | PWM3                | 0               | 0   | DIG         | PWM Output 3.                                                                                                          |

| RB4/KBI0/PWM5 | RB4                 | 0               | 0   | DIG         | LATB<4> data output; not affected by analog input.                                                                     |

|               |                     | 1               | Ι   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared. Disabled when analog input is enabled.                     |

|               | KBI0                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PWM5                | 0               | 0   | DIG         | PWM Output 5.                                                                                                          |

| RB5/KBI1/     | RB5                 | 0               | 0   | DIG         | LATB<5> data output.                                                                                                   |

| PWM4/PGM      |                     | 1               | Ι   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI1                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PWM4 <sup>(3)</sup> | 0               | 0   | DIG         | PWM Output 4; takes priority over port data.                                                                           |

|               | PGM <sup>(2)</sup>  | х               | I   | ST          | Single-Supply Programming mode entry (ICSP™). Enabled by LVP Configuration bit; all other pin functions are disabled.  |

| RB6/KBI2/PGC  | RB6                 | 0               | 0   | DIG         | LATB<6> data output.                                                                                                   |

|               |                     | 1               | Ι   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI2                | 1               | I   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PGC                 | x               | Ι   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operation. <sup>(1)</sup>                                        |

| RB7/KBI3/PGD  | RB7                 | 0               | 0   | DIG         | LATB<7> data output.                                                                                                   |

|               |                     | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                            |

|               | KBI3                | 1               | I   | TTL         | Interrupt-on-change pin.                                                                                               |

|               | PGD                 | x               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(1)</sup>                                                |

|               |                     | x               | Ι   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(1)</sup>                                                 |

### TABLE 11-3: PORTB I/O SUMMARY

Legend:DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;<br/>x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: All other pin functions are disabled when ICSP or ICD is enabled.

2: Single-Supply Programming must be enabled.

3: RD5 is the alternate pin for PWM4.

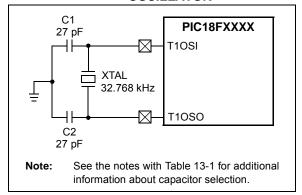

### 13.2 Timer1 Oscillator

A crystal oscillator circuit is built in-between pins, T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical LP oscillator is shown in Figure 13-3. Table 13-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

### FIGURE 13-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

## TABLE 13-1:CAPACITOR SELECTION FOR<br/>THE TIMER OSCILLATOR

| Osc Type | Freq   | C1                   | C2                   |

|----------|--------|----------------------|----------------------|

| LP       | 32 kHz | 27 pF <sup>(1)</sup> | 27 pF <sup>(1)</sup> |

- Note 1: Microchip suggests this value as a starting point in validating the oscillator circuit.

- 2: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- **3:** Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

### 13.3 Timer1 Oscillator Layout Considerations

The Timer1 oscillator for PIC18F2331/2431/4331/4431 devices incorporates an additional low-power feature. When this option is selected, it allows the oscillator to automatically reduce its power consumption when the microcontroller is in Sleep mode. During normal device operation, the oscillator draws full current. As high noise environments may cause excessive oscillator instability in Sleep mode, this option is best suited for low noise applications, where power conservation is an important design consideration.

<u>The low-power option is enabled by clearing the</u> T1OSCMX bit (CONFIG3L<5>). By default, the option is disabled, which results in a more or less constant current draw for the Timer1 oscillator.

Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 13-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD. Refer to **Section 2.0 "Guidelines for Getting Started with PIC18F Microcontrollers"** for additional information

| R/W-0         | R/W-0                                                                                                                                                                           | R-0                                                                                                                             | R-0                                                                          | R-0                       | R-0               | R-0               | R-0           |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------|-------------------|-------------------|---------------|--|--|--|--|

| SMP           | CKE                                                                                                                                                                             | D/A                                                                                                                             | Р                                                                            | S                         | R/W               | UA                | BF            |  |  |  |  |

| bit 7         | I                                                                                                                                                                               |                                                                                                                                 |                                                                              |                           |                   |                   | bi            |  |  |  |  |

| Legend:       |                                                                                                                                                                                 |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

| R = Readabl   | le bit                                                                                                                                                                          | W = Writable                                                                                                                    | bit                                                                          | U = Unimpler              | nented bit, read  | l as '0'          |               |  |  |  |  |

| -n = Value at | t POR                                                                                                                                                                           | '1' = Bit is set                                                                                                                |                                                                              | '0' = Bit is cle          | ared              | x = Bit is unkr   | nown          |  |  |  |  |

| L:1 7         | <b>011D</b> 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                               | 1- 1-14                                                                                                                         |                                                                              |                           |                   |                   |               |  |  |  |  |

| bit 7         | SMP: Sample bit<br>SPI Master mode:                                                                                                                                             |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | ta sampled at e                                                                                                                 | nd of data outr                                                              | out time                  |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | ta sampled at m                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | <u>SPI Slave m</u>                                                                                                                                                              | ode:                                                                                                                            |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | SMP must b                                                                                                                                                                      | e cleared when                                                                                                                  | SPI is used in                                                               | Slave mode.               |                   |                   |               |  |  |  |  |

| bit 6         | CKE: SPI CI                                                                                                                                                                     | lock Edge Selec                                                                                                                 | t bit (Figure 19                                                             | 9-2, Figure 19-3          | and Figure 19-    | 4)                |               |  |  |  |  |

|               | <u>SPI mode, C</u>                                                                                                                                                              |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | nsmitted on risir                                                                                                               |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | 0 = Data transmitted on falling edge of SCK<br>SPI mode, CKP = 1:                                                                                                               |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | <u>SPI mode, CKP = 1:</u><br>1 = Data transmitted on falling edge of SCK                                                                                                        |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | nsmitted on risir                                                                                                               |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | <u>I<sup>2</sup>C™ mode:</u>                                                                                                                                                    | <u>-</u>                                                                                                                        |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | _                                                                                                                                                                               | t be maintained                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

| bit 5         | <b>D/A</b> : Data/A                                                                                                                                                             | <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | s that the last by<br>s that the last by                                                                                        |                                                                              |                           |                   |                   |               |  |  |  |  |

| bit 4         | <b>P</b> : Stop bit (I <sup>2</sup> C mode only)                                                                                                                                |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | This bit is cleared when the SSP module is disabled or when the Start bit is detected last; SSPEN is<br>cleared.                                                                |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | cleared.<br>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)                                                                                     |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | was not detecte                                                                                                                 |                                                                              |                           |                   | .()               |               |  |  |  |  |

| bit 3         | <b>S</b> : Start bit ( $I^2C$ mode only)                                                                                                                                        |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | This bit is cleared when the SSP module is disabled or when the Stop bit is detected last; SSPEN is                                                                             |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | cleared.<br>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)                                                                                    |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               |                                                                                                                                                                                 | s that a Start bit<br>was not detecte                                                                                           |                                                                              | cted last (this b         | it is '0' on Rese | et)               |               |  |  |  |  |

| bit 2         |                                                                                                                                                                                 | Write Information                                                                                                               | •                                                                            | • ·                       |                   |                   |               |  |  |  |  |

|               | This bit hold                                                                                                                                                                   | s the R/W bit inf                                                                                                               | ormation follow                                                              | win <u>g the l</u> ast ad | dress match. T    | his bit is only v | alid from the |  |  |  |  |

|               | This bit holds the $R/\overline{W}$ bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or ACK bit. |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

|               | 1 = Read<br>0 = Write                                                                                                                                                           |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

| hit 1         |                                                                                                                                                                                 | Address bit (10                                                                                                                 | Bit I <sup>2</sup> C mode                                                    | only)                     |                   |                   |               |  |  |  |  |

|               | <b>UA</b> : Update Address bit (10-Bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSPADD register                            |                                                                                                                                 |                                                                              |                           |                   |                   |               |  |  |  |  |

| bit 1         | 1 = Indicates                                                                                                                                                                   | ,                                                                                                                               |                                                                              | e the address in          | the SSPADD r      | eaister           |               |  |  |  |  |

| DILI          |                                                                                                                                                                                 | ,                                                                                                                               | eeds to update                                                               | e the address ir          | the SSPADD r      | egister           |               |  |  |  |  |

| bit 0         |                                                                                                                                                                                 | s that the user n<br>does not need                                                                                              | eeds to update                                                               | e the address ir          | n the SSPADD r    | egister           |               |  |  |  |  |

|               | 0 = Address<br><b>BF</b> : Buffer F                                                                                                                                             | s that the user n<br>does not need                                                                                              | eeds to update<br>to be updated                                              | e the address ir          | the SSPADD r      | egister           |               |  |  |  |  |

|               | 0 = Address<br><b>BF</b> : Buffer F<br><u>Receive (SP</u><br>1 = Receive                                                                                                        | s that the user n<br>does not need<br>ull Status bit<br><u>Pl and I<sup>2</sup>C mode</u><br>complete, SSP                      | eeds to update<br>to be updated<br><u>s):</u><br>BUF is full                 |                           | the SSPADD r      | egister           |               |  |  |  |  |

|               | 0 = Address<br><b>BF</b> : Buffer F<br><u>Receive (SP</u><br>1 = Receive<br>0 = Receive                                                                                         | s that the user n<br>does not need<br>ull Status bit<br><u>et and I<sup>2</sup>C mode</u><br>complete, SSP<br>not complete, S   | eeds to update<br>to be updated<br><u>s):</u><br>BUF is full                 |                           | n the SSPADD r    | egister           |               |  |  |  |  |

|               | 0 = Address<br><b>BF</b> : Buffer F<br><u>Receive (SP</u><br>1 = Receive<br>0 = Receive<br><u>Transmit (I<sup>2</sup>(</u>                                                      | s that the user n<br>does not need<br>ull Status bit<br><u>Pl and I<sup>2</sup>C mode</u><br>complete, SSP                      | eeds to update<br>to be updated<br><u>s):</u><br>BUF is full<br>iSPBUF is em |                           | n the SSPADD r    | egister           |               |  |  |  |  |

| R/W-0                        | R/W-0                                       | R/W-0                                             | R/W-0                   | R/W-0             | R/W-0           | R-1             | R/W-0 |  |  |  |

|------------------------------|---------------------------------------------|---------------------------------------------------|-------------------------|-------------------|-----------------|-----------------|-------|--|--|--|

| CSRC                         | TX9                                         | TXEN <sup>(1)</sup>                               | SYNC                    | SENDB             | BRGH            | TRMT            | TX9D  |  |  |  |

| pit 7                        | ·                                           |                                                   |                         |                   |                 |                 | bit   |  |  |  |

|                              |                                             |                                                   |                         |                   |                 |                 |       |  |  |  |

| <b>₋egend:</b><br>R = Readab | le hit                                      | W = Writable                                      | hit                     | II = I Inimplen   | nented bit, rea | d as 'O'        |       |  |  |  |

| n = Value a                  |                                             | '1' = Bit is set                                  |                         | '0' = Bit is clea |                 | x = Bit is unkr | own   |  |  |  |

|                              |                                             | 2.1.0 000                                         |                         |                   |                 |                 |       |  |  |  |

| oit 7                        | CSRC: Clock                                 | Source Select                                     | bit                     |                   |                 |                 |       |  |  |  |

|                              | <u>Asynchronou</u><br>Don't care.           | <u>s mode:</u>                                    |                         |                   |                 |                 |       |  |  |  |

|                              |                                             | <u>mode:</u><br>ode (clock gen<br>ode (clock from |                         |                   |                 |                 |       |  |  |  |

| pit 6                        |                                             | ansmit Enable I                                   |                         |                   |                 |                 |       |  |  |  |

|                              |                                             | -bit transmissio<br>-bit transmissio              |                         |                   |                 |                 |       |  |  |  |

| oit 5                        | TXEN: Trans                                 | mit Enable bit <sup>(1</sup>                      | )                       |                   |                 |                 |       |  |  |  |

|                              | 1 = Transmit<br>0 = Transmit                |                                                   |                         |                   |                 |                 |       |  |  |  |

| oit 4                        | SYNC: EUSA                                  | SYNC: EUSART Mode Select bit                      |                         |                   |                 |                 |       |  |  |  |

|                              | 1 = Synchror                                |                                                   |                         |                   |                 |                 |       |  |  |  |

|                              | 0 = Asynchro                                |                                                   | - <b>t h</b> : <b>t</b> |                   |                 |                 |       |  |  |  |

| bit 3                        |                                             | d Break Chara                                     | cter bit                |                   |                 |                 |       |  |  |  |

|                              |                                             |                                                   |                         | n (cleared by ha  | rdware upon c   | ompletion)      |       |  |  |  |

|                              | <u>Synchronous</u><br>Don't care.           |                                                   | ·                       |                   |                 |                 |       |  |  |  |

| oit 2                        | BRGH: High                                  | Baud Rate Sel                                     | ect bit                 |                   |                 |                 |       |  |  |  |

|                              | Asynchronou<br>1 = High spe<br>0 = Low spee | ed                                                |                         |                   |                 |                 |       |  |  |  |

|                              | Synchronous<br>Unused in thi                | mode:                                             |                         |                   |                 |                 |       |  |  |  |

| pit 1                        | TRMT: Trans                                 | mit Shift Regist                                  | er Status bit           |                   |                 |                 |       |  |  |  |

|                              | 1 = TSR is er<br>0 = TSR is fu              |                                                   |                         |                   |                 |                 |       |  |  |  |

| oit O                        | <b>TX9D:</b> 9th Bi                         | t of Transmit Da                                  | ata                     |                   |                 |                 |       |  |  |  |

|                              | Can be addre                                |                                                   |                         |                   |                 |                 |       |  |  |  |

### 20.5 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the RC6/TX/CK/SS pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 20.5.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of Sleep mode.