Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 16KB (8K × 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2431-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC18F2331/2431 PINOUT I/O DESCRIPTIONS

|                                                                          | Pin Nu         | mber     | Dim                    | Duffer                              |                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------|----------------|----------|------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                 | SPDIP,<br>SOIC | QFN      | Pin<br>Type            | Buffer<br>Type                      | Description                                                                                                                                                                                                                                                                              |

| MCLR/Vpp<br>MCLR<br>Vpp                                                  | 1              | 26       | I<br>P                 | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.<br>High-voltage ICSP™ programming enable pin.                                                                                                      |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                                            | 9              | 6        |                        | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; CMOS otherwise<br>External clock source input. Always associated with pin<br>function OSC1. (See related OSC1/CLKI, OSC2/CLKO<br>pins.) |

| RA7                                                                      |                |          | I/O                    | TTL                                 | General purpose I/O pin.                                                                                                                                                                                                                                                                 |

| OSC2/CLKO/RA6<br>OSC2<br>CLKO                                            | 10             | 7        | 0                      | _                                   | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO, which has 1/4<br>the frequency of OSC1 and denotes the instruction<br>cycle rate.                                |

| RA6                                                                      |                |          | I/O                    | TTL                                 | General purpose I/O pin.                                                                                                                                                                                                                                                                 |

| RA0/AN0<br>RA0<br>AN0<br>RA1/AN1                                         | 2<br>3         | 27<br>28 | I/O<br>I               | TTL<br>Analog                       | PORTA is a bidirectional I/O port.<br>Digital I/O.<br>Analog Input 0.                                                                                                                                                                                                                    |

| RA1<br>AN1                                                               |                |          | I/O<br>I               | TTL<br>Analog                       | Digital I/O.<br>Analog Input 1.                                                                                                                                                                                                                                                          |

| RA2/AN2/VREF-/CAP1/INDX<br>RA2<br>AN2<br>VREF-<br>CAP1<br>INDX           | 4              | 1        | I/O<br> <br> <br> <br> | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.<br>Input Capture Pin 1.<br>Quadrature Encoder Interface index input pin.                                                                                                                                           |

| RA3/AN3/VREF+/CAP2/QEA<br>RA3<br>AN3<br>VREF+<br>CAP2<br>QEA             | 5              | 2        | I/O<br>I<br>I<br>I     | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.<br>Input Capture Pin 2.<br>Quadrature Encoder Interface Channel A input pin.                                                                                                                                      |

| RA4/AN4/CAP3/QEB<br>RA4<br>AN4<br>CAP3<br>QEB<br>Legend: TTL = TTL compa | 6              | 3        | I/O<br>I<br>I          | TTL<br>Analog<br>ST<br>ST           | Digital I/O.<br>Analog Input 4.<br>Input Capture Pin 3.<br>Quadrature Encoder Interface Channel B input pin.<br>CMOS = CMOS compatible input or output                                                                                                                                   |

0 = Output Р

= Power

# 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.2.3 CONSIDERATIONS WHEN USING BOR

When the Brown-out Reset (BOR) feature is enabled, a sudden change in VDD may result in a spontaneous BOR event. This can happen when the microcontroller is operating under normal operating conditions, regardless of what the BOR set point has been programmed to, and even if VDD does not approach the set point. The precipitating factor in these BOR events is a rise or fall in VDD with a slew rate faster than  $0.15V/\mu s$ .

An application that incorporates adequate decoupling between the power supplies will not experience such rapid voltage changes. Additionally, the use of an electrolytic tank capacitor across VDD and Vss, as described above, will be helpful in preventing high slew rate transitions.

If the application has components that turn on or off, and share the same VDD circuit as the microcontroller, the BOR can be disabled in software by using the SBOREN bit before switching the component. Afterwards, allow a small delay before re-enabling the BOR. By doing this, it is ensured that the BOR is disabled during the interval that might cause high slew rate changes of VDD.

Note: Not all devices incorporate software BOR control. See Section 5.0 "Reset" for device-specific information.

# 4.0 POWER-MANAGED MODES

PIC18F2331/2431/4331/4431 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked, and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<3:0> Configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes)

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

|          | 10116                |               |         |             |                                                                                                                                        |  |  |

|----------|----------------------|---------------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mada     | OSCCON               | l Bits<7,1:0> | Module  | Clocking    | Ausilable Clask and Ossillator Source                                                                                                  |  |  |

| Mode     | IDLEN <sup>(1)</sup> | SCS<1:0>      | CPU     | Peripherals | Available Clock and Oscillator Source                                                                                                  |  |  |

| Sleep    | 0                    | N/A           | Off     | Off         | None – All clocks are disabled                                                                                                         |  |  |

| PRI_RUN  | N/A                  | 00            | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC and<br>Internal Oscillator Block. <sup>(2)</sup><br>This is the normal, full-power execution mode. |  |  |

| SEC_RUN  | N/A                  | 01            | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                                          |  |  |

| RC_RUN   | N/A                  | 1x            | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                               |  |  |

| PRI_IDLE | 1                    | 00            | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                                                    |  |  |

| SEC_IDLE | 1                    | 01            | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                                          |  |  |

| RC_IDLE  | 1                    | 1x            | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                               |  |  |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the **SLEEP** instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

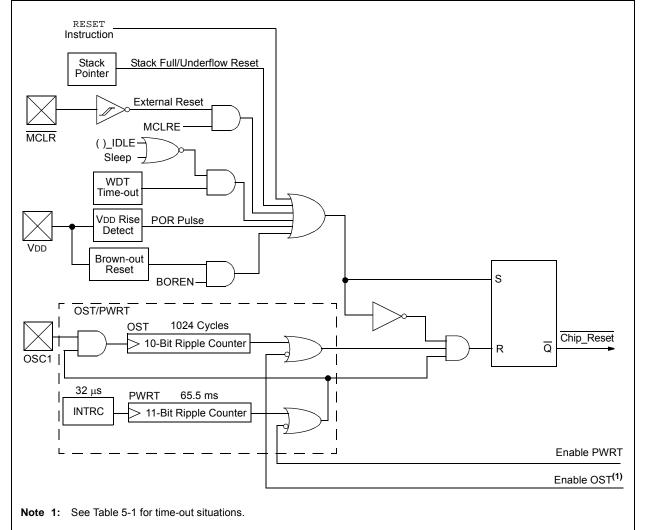

# 5.0 RESET

The PIC18F2331/2431/4331/4431 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR, and the operation of the various startup timers. Stack Reset events are covered in Section 6.1.2.4 "Stack Full/Underflow Resets". WDT Resets are covered in Section 23.2 "Watchdog Timer (WDT)".

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three peripheral interrupt priority registers (IPR1, IPR2 and IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 10-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| U-0   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| _     | ADIP  | RCIP  | TXIP  | SSPIP | CCPIP | TMR2IP | TMR1IP |

| bit 7 |       |       |       |       |       |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                   |

|-------|--------------------------------------------------------------|

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                   |

|       | 1 = High priority<br>0 = Low priority                        |

| bit 5 | RC1IP: EUSART Receive Interrupt Priority bit                 |

|       | 1 = High priority<br>0 = Low priority                        |

| bit 4 | TX1IP: EUSART Transmit Interrupt Priority bit                |

|       | 1 = High priority<br>0 = Low priority                        |

| bit 3 | SSP1IP: Synchronous Serial Port Interrupt Priority bit       |

|       | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |

| bit 2 | CCP1IP: CCP1 Interrupt Priority bit                          |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 1 | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit             |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 0 | TMR1IP: TMR1 Overflow Interrupt Priority bit                 |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module Special Event Trigger

- Status of system clock operation

Figure 13-1 is a simplified block diagram of the Timer1 module.

Register 13-1 details the Timer1 Control register. This register controls the operating mode of the Timer1 module and contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Timer1 oscillator can be used as a secondary clock source in power-managed modes. When the T1RUN bit is set, the Timer1 oscillator provides the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

## REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:<br>R = Readat | ole bit   | W = Writable bit                                             | U = Unimplemented bit                                      | read as '0'        |

|-----------------------|-----------|--------------------------------------------------------------|------------------------------------------------------------|--------------------|

| -n = Value a          |           | '1' = Bit is set                                             | '0' = Bit is cleared                                       | x = Bit is unknowr |

| -                     |           |                                                              |                                                            |                    |

| bit 7                 |           | -Bit Read/Write Mode Enabl                                   |                                                            |                    |

|                       |           | les register read/write of TIn                               | •                                                          |                    |

| bit 6                 |           | les register read/write of Tim<br>Fimer1 System Clock Status | •                                                          |                    |

| DILO                  |           | ce clock is derived from Time                                |                                                            |                    |

|                       |           | ce clock is derived from anot                                |                                                            |                    |

| bit 5-4               | T1CKPS    | <1:0>: Timer1 Input Clock Pi                                 | rescale Select bits                                        |                    |

|                       |           | Prescale value                                               |                                                            |                    |

|                       |           | Prescale value<br>Prescale value                             |                                                            |                    |

|                       |           | Prescale value                                               |                                                            |                    |

| bit 3                 | T1OSCE    | N: Timer1 Oscillator Enable I                                | bit                                                        |                    |

|                       |           | r1 oscillator is enabled                                     |                                                            |                    |

|                       |           | r1 oscillator is shut off                                    | aciator are turned off to alimin                           | ata nawar drain    |

| bit 2                 |           | Timer1 External Clock Input                                  | esistor are turned off to eliminate supervision solart bit | ale power drain.   |

|                       |           | R1CS = 1 (External Clock):                                   | Controllization Select bit                                 |                    |

|                       |           | t synchronize external clock                                 | input                                                      |                    |

|                       |           | nronize external clock input                                 |                                                            |                    |

|                       |           | R1CS = 0 (Internal Clock):                                   | ternal clock when TMR1CS =                                 | 0                  |

| bit 1                 |           | : Timer1 Clock Source Selec                                  |                                                            | 0.                 |

|                       |           |                                                              | SO/T1CKI (on the rising edge                               | )                  |

|                       |           | nal clock (Fosc/4)                                           |                                                            | /                  |

| bit 0                 | TMR1ON    | : Timer1 On bit                                              |                                                            |                    |

|                       |           | les Timer1                                                   |                                                            |                    |

|                       | 0 = Stops | s Timer1                                                     |                                                            |                    |

In Synchronous Counter mode configuration, the timer is clocked by the external clock (T5CKI) with the optional prescaler. The external T5CKI is selected by setting the TMR5CS bit (TMR5CS = 1); the internal clock is selected by clearing TMR5CS. The external clock is synchronized to the internal clock by clearing the T5SYNC bit. The input on T5CKI is sampled on every Q2 and Q4 of the internal clock. The low to rise transition is decoded on three adjacent samples and the Timer5 is incremented on the next Q1. The T5CKI minimum pulse-width high and low time must be greater than TcY/2.

In Asynchronous Counter mode configuration, Timer5 is clocked by the external clock (T5CKI) with the optional prescaler. In this mode, T5CKI is not synchronized to the internal clock. By setting TMR5CS, the external input clock (T5CKI) can be used as the counter sampling clock. When T5SYNC is set, the external clock is not synchronized to the internal device clock.

The timer count is not reset automatically when the module is disabled. The user may write the Counter register to initialize the counter.

Note: The Timer5 module does NOT prevent writes to the PR5 registers (PR5H:PR5L) while the timer is enabled. Writing to PR5 while the timer is enabled may result in unexpected period match events.

#### 15.1.1 CONTINUOUS COUNT AND SINGLE-SHOT OPERATION

Timer5 has two operating modes: Continuous Count and Single-Shot.

Continuous Count mode is selected by clearing the T5MOD control bit (= 0). In this mode, the Timer5 time base will start incrementing according to the prescaler settings until a TMR5/PR5 match occurs, or until TMR5 rolls over (FFFFh to 0000h). The TMR5IF interrupt flag is set, the TMR5 register is reset on the following input clock edge and the timer continues to count for as long as the TMR5ON bit remains set.

Single-Shot mode is selected by setting T5MOD (= 1). In this mode, the Timer5 time base begins to increment according to the prescaler settings until a TMR5/PR5 match occurs. This causes the TMR5IF interrupt flag to be set, the TMR5 register pair to be cleared on the following input clock edge and the TMR5ON bit to be cleared by the hardware to halt the timer.

The Timer5 time base can only start incrementing in Single-Shot mode under two conditions:

- 1. Timer5 is enabled (TMR5ON is set), or

- Timer5 is disabled and a Special Event Trigger Reset is present on the Timer5 Reset input. (See Section 15.7 "Timer5 Special Event Trigger Reset Input" for additional information.)

# 15.2 16-Bit Read/Write and Write Modes

As noted, the actual high byte of the Timer5 register pair is mapped to TMR5H, which serves as a buffer. Reading TMR5L will load the contents of the high byte of the register pair into the TMR5H register. This allows the user to accurately read all 16 bits of the register pair without having to determine whether a read of the high byte, followed by the low byte, is valid due to a rollover between reads.

Since the actual high byte of the Timer5 register pair is not directly readable or writable, it must be read and written to through the Timer5 High Byte Buffer register (TMR5H). The T5 high byte is updated with the contents of TMR5H when a write occurs to TMR5L. This allows a user to write all 16 bits to both the high and low bytes of Timer5 at once. Writes to TMR5H do not clear the Timer5 prescaler. The prescaler is only cleared on writes to TMR5L.

#### 15.2.1 16-BIT READ-MODIFY-WRITE

Read-modify-write instructions, like BSF and BCF, will read the contents of a register, make the appropriate changes and place the result back into the register. The write portion of a read-modify-write instruction of TMR5H will not update the contents of the high byte of TMR5 until a write of TMR5L takes place. Only then will the contents of TMR5H be placed into the high byte of TMR5.

# 15.3 Timer5 Prescaler

The Timer5 clock input (either TCY or the external clock) may be divided by using the Timer5 programmable prescaler. The prescaler control bits, T5PS<1:0> (T5CON<4:3>), select a prescale factor of 2, 4, 8 or no prescale.

The Timer5 prescaler is cleared by any of the following:

- A write to the Timer5 register

- Disabling Timer5 (TMR5ON = 0)

- A device Reset such as Master Clear, POR or BOR

Note: Writing to the T5CON register does not clear the Timer5.

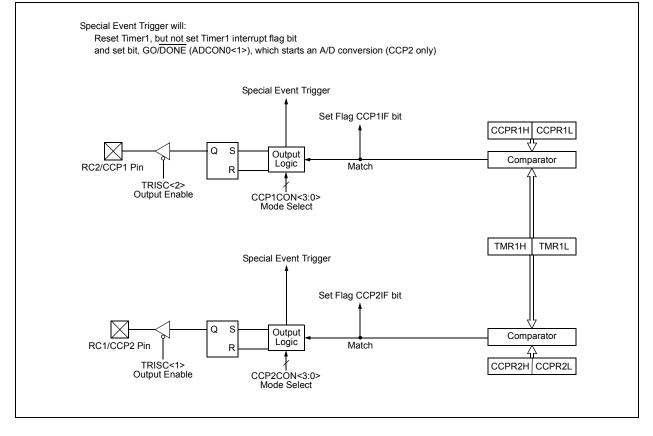

# 16.4 Compare Mode

In Compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 (RC1/CCP2) pin:

- is driven high

- is driven low

- toggles output (high-to-low or low-to-high)

- remains unchanged (interrupt only)

The action on the pin is based on the value of control bits, CCP1M<3:0> (CCP2M<3:0>). At the same time, interrupt flag bit CCP1IF (CCP2IF) is set.

#### 16.4.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISC bit.

Note: Clearing the CCPxCON register will force the RC1 or RC2 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 16.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.4.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 16.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP2 resets the TMR1 register pair. Additionally, the CCP2 Special Event Trigger will start an A/D conversion if the A/D module is enabled.

Note: The Special Event Trigger from the CCP2 module will not set the Timer1 interrupt flag bit.

#### FIGURE 16-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 17.2.1 QEI CONFIGURATION

The QEI module shares its input pins with the Input Capture (IC) module. The inputs are mutually exclusive; only the IC module or the QEI module (but not both) can be enabled at one time. Also, because the IC and QEI are multiplexed to the same input pins, the programmable noise filters can be dedicated to one module only. The operation of the QEI is controlled by the QEICON Configuration register (see Register 17-2).

Note: In the event that both QEI and IC are enabled, QEI will take precedence and IC will remain disabled.

### REGISTER 17-2: QEICON: QUADRATURE ENCODER INTERFACE CONTROL REGISTER

| R/W-0               | R/W-0                           | R-0                                 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0            | R/W-0        |

|---------------------|---------------------------------|-------------------------------------|------------------------|------------------------|------------------------|------------------|--------------|

| VELM                | QERR <sup>(1)</sup>             | UP/DOWN                             | QEIM2 <sup>(2,3)</sup> | QEIM1 <sup>(2,3)</sup> | QEIM0 <sup>(2,3)</sup> | PDEC1            | PDEC0        |

| bit 7               |                                 |                                     |                        |                        |                        | •                | bit (        |

| Legend:             |                                 |                                     |                        |                        |                        |                  |              |

| R = Read            | able bit                        | W = Writable I                      | oit                    | U = Unimplem           | nented bit, read       | d as '0'         |              |

| -n = Value          | e at POR                        | '1' = Bit is set                    |                        | '0' = Bit is clea      | ared                   | x = Bit is unkr  | iown         |

| bit 7               | VELM: Veloc                     | ity Mode bit                        |                        |                        |                        |                  |              |

|                     |                                 | mode disabled<br>mode enabled       |                        |                        |                        |                  |              |

| bit 6               | QERR: QEI E                     | Error bit <sup>(1)</sup>            |                        |                        |                        |                  |              |

|                     |                                 | counter overflow                    |                        | 4)                     |                        |                  |              |

|                     |                                 | low or underflow                    |                        |                        |                        |                  |              |

| bit 5               |                                 | Direction of Rota                   | tion Status bit        |                        |                        |                  |              |

|                     | 1 = Forward<br>0 = Reverse      |                                     |                        |                        |                        |                  |              |

| bit 4-2             |                                 | QEI Mode bits <sup>(2</sup>         | ,3)                    |                        |                        |                  |              |

| Dit <del>4</del> -2 | 111 = Unuse                     |                                     |                        |                        |                        |                  |              |

|                     |                                 | nabled in 4x Upo                    | late mode; pos         | ition counter is r     | reset on period        | match (POSCN     | IT = MAXCNT  |

|                     |                                 | nabled in 4x Up                     |                        |                        | •                      | •                |              |

|                     | 100 = Unuse                     |                                     |                        |                        |                        |                  | -            |

|                     |                                 | nabled in 2x Upo<br>nabled in 2x Up |                        |                        | •                      | •                | II = MAXCNI  |

|                     | 001 = QEI e<br>000 = QEI o      |                                     |                        |                        |                        |                  |              |

| bit 1-0             | PDEC<1:0>:                      | Velocity Pulse F                    | Reduction Ratio        | o bits                 |                        |                  |              |

|                     | 11 <b>= 1:64</b>                | 5                                   |                        |                        |                        |                  |              |

|                     | 10 <b>= 1:16</b>                |                                     |                        |                        |                        |                  |              |

|                     | 01 = 1:4                        |                                     |                        |                        |                        |                  |              |

|                     | 00 = 1:1                        |                                     |                        |                        |                        |                  |              |

| Note 1:             | QEI must be en                  | abled and in Ind                    | lex mode.              |                        |                        |                  |              |

| 2:                  | QEI mode select are both enable |                                     |                        | nable CAP1, C          | AP2 or CAP3 i          | nputs. If QEI ar | d IC modules |

| 3:                  | Enabling one of                 | the QEI operation                   | ing modes rem          |                        |                        | AP1BUFH, CAF     | 1BUFL,       |

- CAP2BUFH, CAP2BUFL, CAP3BUFH and CAP3BUFL, as the VELRH, VELRL, POSCNTH, POSCNTL, MAXCNTH and MAXCNTL registers (respectively) for the QEI.

- 4: The QERR bit must be cleared in software.

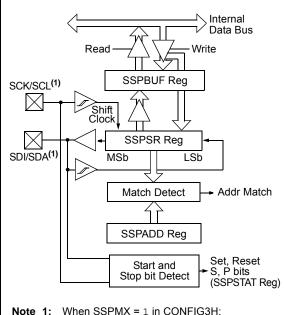

# 19.3 SSP I<sup>2</sup>C Operation

The SSP module, in I<sup>2</sup>C mode, fully implements all slave functions except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the SCK/ SCL pin, which is the clock (SCL), and the SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<5:4> or TRISD<3:2> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 19-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

Note 1: When SSPMX = 1 in CONFIG3H: SCK/SCL is multiplexed to the RC5 pin, SDA/ SDI is multiplexed to the RC4 pin and SDO is multiplexed to pin, RC7.

> When SSPMX = 0 in CONFIG3H: SCK/SCL is multiplexed to the RD3 pin, SDA/ SDI is multiplexed to the RD2 pin and SDO is multiplexed to pin, RD1.

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Controlled Master mode; Slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISC or TRISD bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

Additional information on SSP I<sup>2</sup>C operation can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

### 19.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<5:4> or TRISD<3:2> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- b) The SSP Overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit, SSPIF (PIR1<3>), is set. Table 19-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit, BF, is cleared by reading the SSPBUF register, while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing Parameter 100 and Parameter 101.

| Name    | Bit 7      | Bit 6                                         | Bit 5      | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset Values<br>on Page: |

|---------|------------|-----------------------------------------------|------------|-----------|-------|--------|--------|--------|--------------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL                                     | TMR0IE     | INT0IE    | RBIE  | TMR0IF | INT0IF | RBIF   | 54                       |

| PIR1    | _          | ADIF                                          | RCIF       | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 57                       |

| PIE1    | —          | ADIE                                          | RCIE       | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 57                       |

| IPR1    | —          | ADIP                                          | RCIP       | TXIP      | SSPIP | CCP1IP | TMR2IP | TMR1IP | 57                       |

| RCSTA   | SPEN       | RX9                                           | SREN       | CREN      | ADDEN | FERR   | OERR   | RX9D   | 56                       |

| TXREG   | EUSART Tra | insmit Regist                                 | er         |           |       |        |        |        | 56                       |

| TXSTA   | CSRC       | TX9                                           | TXEN       | SYNC      | SENDB | BRGH   | TRMT   | TX9D   | 56                       |

| BAUDCON | _          | RCIDL                                         | _          | SCKP      | BRG16 |        | WUE    | ABDEN  | 56                       |

| SPBRGH  | EUSART Ba  | EUSART Baud Rate Generator Register High Byte |            |           |       |        |        |        |                          |

| SPBRG   | EUSART Ba  | ud Rate Gen                                   | erator Reg | ister Low | Byte  |        |        |        | 56                       |

|         | ·          |                                               |            |           |       |        |        |        | •                        |

#### TABLE 20-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for asynchronous transmission.

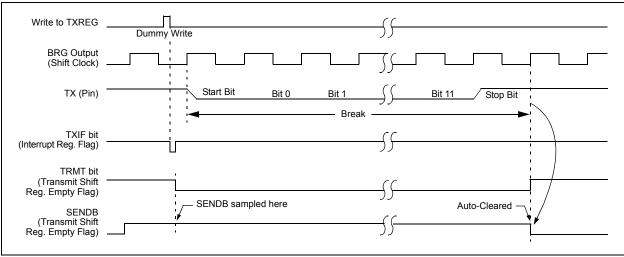

### 20.3.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-9 for the timing of the Break character sequence.

#### 20.3.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to setup the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 20.3.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 of the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 20.3.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit before placing the EUSART in its Sleep mode.

#### FIGURE 20-9: SEND BREAK CHARACTER SEQUENCE

| Bit 7                                         | Bit 6                                                             | Bit 5              | Bit 4                                                                                                                     | Bit 3                                                                                                                                                                    | Bit 2                                                                                                                                   | Bit 1                                                                                                                                                                                                                                                        | Bit 0                                                                                                                                                                                                                                                                            | Reset Values<br>on Page:                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------|-------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE/GIEH                                      | PEIE/GIEL                                                         | TMR0IE             | INT0IE                                                                                                                    | RBIE                                                                                                                                                                     | TMR0IF                                                                                                                                  | <b>INT0IF</b>                                                                                                                                                                                                                                                | RBIF                                                                                                                                                                                                                                                                             | 54                                                                                                                                                                                                                                                                                                                                                           |

| —                                             | ADIF                                                              | RCIF               | TXIF                                                                                                                      | SSPIF                                                                                                                                                                    | CCP1IF                                                                                                                                  | TMR2IF                                                                                                                                                                                                                                                       | TMR1IF                                                                                                                                                                                                                                                                           | 57                                                                                                                                                                                                                                                                                                                                                           |

| —                                             | ADIE                                                              | RCIE               | TXIE                                                                                                                      | SSPIE                                                                                                                                                                    | CCP1IE                                                                                                                                  | TMR2IE                                                                                                                                                                                                                                                       | TMR1IE                                                                                                                                                                                                                                                                           | 57                                                                                                                                                                                                                                                                                                                                                           |

| —                                             | ADIP                                                              | RCIP               | TXIP                                                                                                                      | SSPIP                                                                                                                                                                    | CCP1IP                                                                                                                                  | TMR2IP                                                                                                                                                                                                                                                       | TMR1IP                                                                                                                                                                                                                                                                           | 57                                                                                                                                                                                                                                                                                                                                                           |

| SPEN                                          | RX9                                                               | SREN               | CREN                                                                                                                      | ADDEN                                                                                                                                                                    | FERR                                                                                                                                    | OERR                                                                                                                                                                                                                                                         | RX9D                                                                                                                                                                                                                                                                             | 56                                                                                                                                                                                                                                                                                                                                                           |

| EUSART Re                                     | eceive Registe                                                    | er                 |                                                                                                                           |                                                                                                                                                                          |                                                                                                                                         |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                           |

| CSRC                                          | TX9                                                               | TXEN               | SYNC                                                                                                                      | SENDB                                                                                                                                                                    | BRGH                                                                                                                                    | TRMT                                                                                                                                                                                                                                                         | TX9D                                                                                                                                                                                                                                                                             | 56                                                                                                                                                                                                                                                                                                                                                           |

| —                                             | RCIDL                                                             |                    | SCKP                                                                                                                      | BRG16                                                                                                                                                                    | _                                                                                                                                       | WUE                                                                                                                                                                                                                                                          | ABDEN                                                                                                                                                                                                                                                                            | 56                                                                                                                                                                                                                                                                                                                                                           |

| EUSART Baud Rate Generator Register High Byte |                                                                   |                    |                                                                                                                           |                                                                                                                                                                          |                                                                                                                                         |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                           |

| EUSART Ba                                     | aud Rate Gen                                                      | erator Regi        | ster Low                                                                                                                  | Byte                                                                                                                                                                     |                                                                                                                                         |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                           |

|                                               | GIE/GIEH<br>—<br>—<br>SPEN<br>EUSART Re<br>CSRC<br>—<br>EUSART Ba | GIE/GIEH PEIE/GIEL | GIE/GIEHPEIE/GIELTMR0IEADIFRCIFADIERCIEADIPRCIPSPENRX9SRENEUSART Receive RegisterTXENRCIDLEUSART Baud Rate Generator Regi | GIE/GIEHPEIE/GIELTMR0IEINT0IE—ADIFRCIFTXIF—ADIERCIETXIE—ADIPRCIPTXIPSPENRX9SRENCRENEUSART Receive RegisterCSRCTX9TXEN—RCIDL—SCKPEUSART Baud Rate Generator Register High | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIE—ADIFRCIFTXIFSSPIF—ADIERCIETXIESSPIE—ADIPRCIPTXIPSSPIPSPENRX9SRENCRENADDENEUSART RegisterTXENSYNCSENDB | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IF—ADIFRCIFTXIFSSPIFCCP1IF—ADIERCIETXIESSPIECCP1IE—ADIPRCIPTXIPSSPIPCCP1IPSPENRX9SRENCRENADDENFERREUSART Receive RegisterTXENSYNCSENDBBRGH—RCIDL—SCKPBRG16—EUSART Baud Rate Generator Register High ByteStateStateState | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IFINT0IF—ADIFRCIFTXIFSSPIFCCP1IFTMR2IF—ADIERCIETXIESSPIECCP1IETMR2IE—ADIPRCIPTXIPSSPIPCCP1IPTMR2IPSPENRX9SRENCRENADDENFERROERREUSART Receive RegisterTXENSYNCSENDBBRGHTRMT—RCIDL—SCKPBRG16—WUEEUSART Baud Rate Generator Register High Byte | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFRBIFADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFADIERCIETXIESSPIECCP1IETMR2IETMR1IEADIPRCIPTXIPSSPIPCCP1IETMR2IETMR1IEADIPRCIPTXIPSSPIPCCP1IETMR2IETMR1IPSPENRX9SRENCRENADDENFERROERRRX9DEUSART ceive RegisterTXENSYNCSENDBBRGHTRMTTX9DRCIDLSCKPBRG16WUEABDENEUSART But Rate Generator Register HighByteByteByteByteByte |

### TABLE 20-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

#### REGISTER 23-13: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2331/2431/4331/4431 DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Readable bit             | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed           | U = Unchanged from programmed state |

| bit 7-5 | DEV<2:0>: Device ID bits                                                                             |

|---------|------------------------------------------------------------------------------------------------------|

|         | These bits are used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number. |

|         | 000 = PIC18F4331                                                                                     |

|         | 001 = PIC18F4431                                                                                     |

|         | 100 = PIC18F2331                                                                                     |

|         | 101 = PIC18F2431                                                                                     |

| bit 4-0 | REV<4:0>: Revision ID bits                                                                           |

|         | These bits are used to indicate the device revision.                                                 |

#### REGISTER 23-14: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2331/2431/4331/4431 DEVICES

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                | •                   |                     | •                   |                     |                     |                     | bit 0               |

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Readable bit             | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed           | U = Unchanged from programmed state |

bit 7-0 **DEV<10:3>:** Device ID bits<sup>(1)</sup> These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number 0000 0101 = PIC18F2331/2431/4331/4431 devices

**Note 1:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

# PIC18F2331/2431/4331/4431

| ANDWF              |                |                | AND W with f                    |                                                           |                                           |                                   |                                                  |  |

|--------------------|----------------|----------------|---------------------------------|-----------------------------------------------------------|-------------------------------------------|-----------------------------------|--------------------------------------------------|--|

| Synt               | ax:            | [/             | label] Al                       | NDWF                                                      | f [,d [                                   | ,a]]                              |                                                  |  |

| Operands:          |                |                | ≤ f ≤ 255<br>∈ [0,1]<br>∈ [0,1] |                                                           |                                           |                                   |                                                  |  |

| Oper               | ration:        | (V             | V) .AND.                        | $(f) \rightarrow des$                                     | st                                        |                                   |                                                  |  |

| Statu              | is Affected:   | Ν              | , Z                             |                                                           |                                           |                                   |                                                  |  |

| Enco               | oding:         |                | 0001                            | 01da                                                      | fff                                       | f                                 | ffff                                             |  |

| Description:       |                | re<br>st<br>st |                                 | If 'd' is '(<br>/. If 'd' is<br>k in regist<br>nk will be | )', the<br>'1', the<br>ter, 'f'.<br>selec | resu<br>e res<br>If 'a'<br>ted. I | llt is<br>ult is<br>is '0', the<br>f 'a' is '1', |  |

| Word               | ds:            | 1              | 1                               |                                                           |                                           |                                   |                                                  |  |

| Cycle              | es:            | 1              |                                 |                                                           |                                           |                                   |                                                  |  |

| QC                 | ycle Activity: |                |                                 |                                                           |                                           |                                   |                                                  |  |

|                    | Q1             |                | Q2                              | Q                                                         | 3                                         |                                   | Q4                                               |  |

|                    | Decode         |                | Read<br>gister 'f'              | Proce<br>Data                                             |                                           |                                   | /rite to<br>tination                             |  |

| Exar               | nple:          | A              | NDWF                            | REG,                                                      | W                                         |                                   |                                                  |  |

| Before Instruction |                | tion           |                                 |                                                           |                                           |                                   |                                                  |  |

|                    | W              | =              | 0x17                            |                                                           |                                           |                                   |                                                  |  |

|                    | REG            | =              | 0xC2                            |                                                           |                                           |                                   |                                                  |  |

|                    |                |                | 0xC2                            |                                                           |                                           |                                   |                                                  |  |

|                    | REG            |                | 0xC2<br>0x02                    |                                                           |                                           |                                   |                                                  |  |

| вс                                                                |                       | Branch if                                                                                                                                                                                                                                                                                 | Branch if Carry            |                 |  |  |  |  |