Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

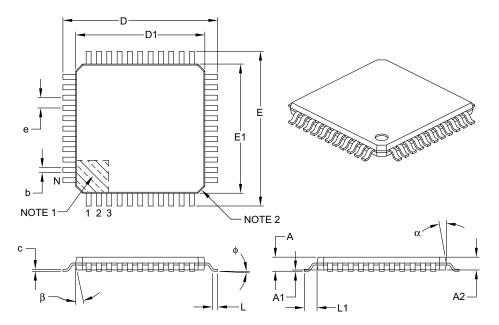

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2431t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| in Bu  | Buffer                                                                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ре Ту  | Type Description                                                                                                                                             |

|        | PORTB is a bidirectional I/O port. PORTB can be softw<br>programmed for internal weak pull-ups on all inputs.                                                |

|        | TTL Digital I/O.<br>TTL PWM Output 0.                                                                                                                        |

|        | TTL Digital I/O.<br>TTL PWM Output 1.                                                                                                                        |

|        | TTL Digital I/O.<br>TTL PWM Output 2.                                                                                                                        |

| -      | TTL Digital I/O.<br>TTL PWM Output 3.                                                                                                                        |

| T      | TTL Digital I/O.<br>TTL Interrupt-on-change pin.<br>TTL PWM Output 5.                                                                                        |

| T<br>T | <ul> <li>TTL Digital I/O.</li> <li>TTL Interrupt-on-change pin.</li> <li>TTL PWM Output 4.</li> <li>ST Single-Supply ICSP™ Programming entry pin.</li> </ul> |

| Τ-     | TTL       Digital I/O.         TTL       Interrupt-on-change pin.         ST       In-Circuit Debugger and ICSP programming clock p                          |

| T      | TTLDigital I/O.TTLInterrupt-on-change pin.STIn-Circuit Debugger and ICSP programming data pi                                                                 |

|        | 0                                                                                                                                                            |

| TABLE 1-3: | PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------------|

|            |                                                     |

ST = Schmitt Trigger input with CMOS levels 0 = Output

Ρ = Power

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL; RC7 is the alternate pin for SDO.

2: RD4 is the alternate pin for FLTA.

3: RD5 is the alternate pin for PWM4.

| Pin Name                                                                    |          |                        |     | Pin                    | Buffer                             | Description                                                                                                                                                      |

|-----------------------------------------------------------------------------|----------|------------------------|-----|------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                    | PDIP     | TQFP                   | QFN | Туре                   | Туре                               | Description                                                                                                                                                      |

|                                                                             |          |                        |     |                        |                                    | PORTC is a bidirectional I/O port.                                                                                                                               |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI                                    | 15       | 32                     | 34  | I/O<br>O<br>I          | ST<br>—<br>ST                      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.                                                                                        |

| RC1/T1OSI/CCP2/<br>FLTA                                                     | 16       | 35                     | 35  |                        | -                                  |                                                                                                                                                                  |

| RC1<br>T1OSI<br><u>CCP2</u><br>FLTA                                         |          |                        |     | I/O<br>I<br>I/O<br>I   | ST<br>CMOS<br>ST<br>ST             | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input, Compare 2 output, PWM2 output.<br>Fault interrupt input pin.                                        |

| RC2/CCP1/FLTB<br>RC2<br>CCP1<br>FLTB                                        | 17       | 36                     | 36  | I/O<br>I/O<br>I        | ST<br>ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Fault interrupt input pin.                                                                      |

| RC3/T0CKI/T5CKI/<br>INT0                                                    | 18       | 37                     | 37  |                        |                                    |                                                                                                                                                                  |

| RC3<br>T0CKI <sup>(1)</sup><br>T5CKI <sup>(1)</sup><br>INT0                 |          |                        |     | I/O<br>I<br>I          | ST<br>ST<br>ST<br>ST               | Digital I/O.<br>Timer0 alternate clock input.<br>Timer5 alternate clock input.<br>External Interrupt 0.                                                          |

| RC4/INT1/SDI/SDA<br>RC4<br>INT1<br>SDI <sup>(1)</sup><br>SDA <sup>(1)</sup> | 23       | 42                     | 42  | I/O<br>I<br>I<br>I/O   | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 1.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |

| RC5/INT2/SCK/SCL<br>RC5<br>INT2<br>SCK <sup>(1)</sup><br>SCL <sup>(1)</sup> | 24       | 43                     | 43  | I/O<br>I<br>I/O<br>I/O | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 2.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC6/TX/CK/ <del>SS</del><br>RC6<br>TX<br><u>CK</u><br>SS                    | 25       | 44                     | 44  | I/O<br>O<br>I/O<br>I   | ST<br>—<br>ST<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>SPI slave select input.                                        |

| RC7/RX/DT/SDO<br>RC7<br>RX<br>DT<br>SDO <sup>(1)</sup>                      | 26       | 1                      | 1   | I/O<br>I<br>I/O<br>O   | ST<br>ST<br>ST                     | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>SPI data out.                                                    |

| Legend: TTL = TTL<br>ST = Schi<br>O = Outp                                  | mitt Tri | atible inp<br>gger inp |     | CMOS                   | levels                             | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |

#### **TABLE 1-3:** PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED)

for SCK/SCL; RC7 is the alternate pin for SDO.

**2:** RD4 is the alternate pin for  $\overline{FLTA}$ .

3: RD5 is the alternate pin for PWM4.

## 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (Parameter 39, Table 26-8). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed, and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD, following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes, is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in more detail in each of the sections that relate to the power-managed modes (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

## 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 10.0 "Interrupts"**).

A fixed delay of interval, TCSD, following the wake event, is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 23.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

## 4.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up, and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 4-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 23.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 23.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

### 6.5.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 6-1 and Table 6-2.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's.

#### TABLE 6-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2331/2431/4331/4431 DEVICES

| Address | Name                    | Address | Name                    | Address | Name    | Address | Name                 | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|---------|---------|----------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H  | F9Fh    | IPR1                 | F7Fh    | PTCON0               |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L  | F9Eh    | PIR1                 | F7Eh    | PTCON1               |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)             | FBDh    | CCP1CON | F9Dh    | PIE1                 | F7Dh    | PTMRL                |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H  | F9Ch    | (2)                  | F7Ch    | PTMRH                |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L  | F9Bh    | OSCTUNE              | F7Bh    | PTPERL               |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON | F9Ah    | ADCON3               | F7Ah    | PTPERH               |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | ANSEL1  | F99h    | ADCHS                | F79h    | PDC0L                |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ANSEL0  | F98h    | (2)                  | F78h    | PDC0H                |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | T5CON   | F97h    | (2)                  | F77h    | PDC1L                |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | QEICON  | F96h    | TRISE <sup>(3)</sup> | F76h    | PDC1H                |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | (2)     | F95h    | TRISD <sup>(3)</sup> | F75h    | PDC2L                |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | (2)     | F94h    | TRISC                | F74h    | PDC2H                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)     | F93h    | TRISB                | F73h    | PDC3L <sup>(3)</sup> |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | (2)     | F92h    | TRISA                | F72h    | PDC3H <sup>(3)</sup> |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | _(2)    | F91h    | PR5H                 | F71h    | SEVTCMPL             |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH  | F90h    | PR5L                 | F70h    | SEVTCMPH             |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG   | F8Fh    | (2)                  | F6Fh    | PWMCON0              |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG   | F8Eh    | (2)                  | F6Eh    | PWMCON1              |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG   | F8Dh    | LATE <sup>(3)</sup>  | F6Dh    | DTCON                |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA   | F8Ch    | LATD <sup>(3)</sup>  | F6Ch    | FLTCONFIG            |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA   | F8Bh    | LATC                 | F6Bh    | OVDCOND              |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | BAUDCON | F8Ah    | LATB                 | F6Ah    | OVDCONS              |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR   | F89h    | LATA                 | F69h    | CAP1BUFH             |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA  | F88h    | TMR5H                | F68h    | CAP1BUFL             |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2  | F87h    | TMR5L                | F67h    | CAP2BUFH             |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSPCON                  | FA6h    | EECON1  | F86h    | (2)                  | F66h    | CAP2BUFL             |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | (2)                     | FA5h    | IPR3    | F85h    | (2)                  | F65h    | CAP3BUFH             |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3    | F84h    | PORTE                | F64h    | CAP3BUFL             |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3    | F83h    | PORTD <sup>(3)</sup> | F63h    | CAP1CON              |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2    | F82h    | PORTC                | F62h    | CAP2CON              |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2    | F81h    | PORTB                | F61h    | CAP3CON              |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2    | F80h    | PORTA                | F60h    | DFLTCON              |

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available on 28-pin devices.

## REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0         | U-0                                          | U-0                                                              | R/W-0           | U-0               | R/W-0           | U-0              | R/W-0     |  |  |

|---------------|----------------------------------------------|------------------------------------------------------------------|-----------------|-------------------|-----------------|------------------|-----------|--|--|

| OSCFIF        | _                                            |                                                                  | EEIF            | _                 | LVDIF           |                  | CCP2IF    |  |  |

| bit 7         |                                              |                                                                  |                 |                   |                 |                  | bit 0     |  |  |

|               |                                              |                                                                  |                 |                   |                 |                  |           |  |  |

| Legend:       |                                              |                                                                  |                 |                   |                 |                  |           |  |  |

| R = Readable  | e bit                                        | W = Writable I                                                   | bit             | U = Unimpler      | nented bit, rea | ad as '0'        |           |  |  |

| -n = Value at | POR                                          | '1' = Bit is set                                                 |                 | '0' = Bit is cle  | ared            | x = Bit is unk   | known     |  |  |

|               |                                              |                                                                  |                 |                   |                 |                  |           |  |  |

| bit 7         |                                              | scillator Fail Inter                                             | 1 0             |                   |                 |                  | <i></i>   |  |  |

|               |                                              | oscillator failed, o<br>clock operating                          | clock input has | s changed to IN   | HOSC (must      | be cleared in so | oftware)  |  |  |

| bit 6-5       |                                              | ented: Read as '0                                                | ,               |                   |                 |                  |           |  |  |

| bit 4         | •                                            | EEIF: EEPROM or Flash Write Operation Interrupt Flag bit         |                 |                   |                 |                  |           |  |  |

|               |                                              | ite operation is co                                              | •               |                   |                 |                  |           |  |  |

|               | 0 = The wr                                   | ite operation is no                                              | ot complete or  | has not been s    | tarted          |                  |           |  |  |

| bit 3         | Unimpleme                                    | ented: Read as '0                                                | ,               |                   |                 |                  |           |  |  |

| bit 2         | LVDIF: Low-Voltage Detect Interrupt Flag bit |                                                                  |                 |                   |                 |                  |           |  |  |

|               |                                              | pply voltage has f                                               |                 |                   | • •             | st be cleared in | software) |  |  |

|               |                                              | 0 = The supply voltage is greater than the specified LVD voltage |                 |                   |                 |                  |           |  |  |

| bit 1         | •                                            | ented: Read as '0                                                |                 |                   |                 |                  |           |  |  |

| bit 0         |                                              | CP2 Interrupt Flag                                               | g bit           |                   |                 |                  |           |  |  |

|               | Capture mo                                   | <u>lae:</u><br>1 register capture                                | occurred (mi    | ist be cleared ii | n software)     |                  |           |  |  |

|               |                                              | R1 register captul                                               |                 |                   | i continarc)    |                  |           |  |  |

|               | Compare m                                    | iode:                                                            |                 |                   |                 |                  |           |  |  |

|               |                                              | 1 register compar<br>R1 register comp                            |                 |                   | leared in soft  | ware)            |           |  |  |

|               | PWM mode                                     |                                                                  |                 |                   |                 |                  |           |  |  |

|               | Not used in                                  | this mode.                                                       |                 |                   |                 |                  |           |  |  |

## REGISTER 10-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0          | U-0        | U-0                               | R/W-0          | R/W-0             | R/W-0            | R/W-0          | R/W-0  |

|--------------|------------|-----------------------------------|----------------|-------------------|------------------|----------------|--------|

| _            | _          | —                                 | PTIE           | IC3DRIE           | IC2QEIE          | IC1IE          | TMR5IE |

| pit 7        |            |                                   |                | -                 |                  |                | bit 0  |

|              |            |                                   |                |                   |                  |                |        |

| _egend:      |            |                                   |                |                   |                  |                |        |

| R = Readable | e bit      | W = Writable                      | bit            | U = Unimplen      | nented bit, read | as '0'         |        |

| n = Value at | POR        | '1' = Bit is set                  |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |

|              |            |                                   |                |                   |                  |                |        |

| oit 7-5      | Unimpleme  | ented: Read as '                  | )'             |                   |                  |                |        |

| oit 4        | PTIE: PWM  | 1 Time Base Inter                 | rupt Enable bi | t                 |                  |                |        |

|              | 1 = PTIF e |                                   |                |                   |                  |                |        |

|              | 0 = PTIF d |                                   |                |                   |                  |                |        |

| bit 3        |            | C3 Interrupt Enab                 |                | hange Interrupt   | Enable bit       |                |        |

|              |            | d (CAP3CON<3:                     | <u>)&gt;):</u> |                   |                  |                |        |

|              |            | errupt enabled<br>errupt disabled |                |                   |                  |                |        |

|              |            | ed (QEIM<2:0>):                   |                |                   |                  |                |        |

|              |            | e of direction inte               | rrupt enabled  |                   |                  |                |        |

|              | 0          | e of direction inte               | •              |                   |                  |                |        |

| oit 2        | IC2QEIE: I | C2 Interrupt Flag/                | QEI Interrupt  | Flag Enable bit   |                  |                |        |

|              | IC2 Enable | d (CAP2CON<3:(                    | <u>)&gt;):</u> |                   |                  |                |        |

|              |            | errupt enabled)                   |                |                   |                  |                |        |

|              |            | errupt disabled                   |                |                   |                  |                |        |

|              |            | <u>ed (QEIM&lt;2:0&gt;):</u>      |                |                   |                  |                |        |

|              |            | errupt enabled<br>errupt disabled |                |                   |                  |                |        |

| .:+ 1        |            | •                                 | <b>_:</b> +    |                   |                  |                |        |

| oit 1        |            | Interrupt Enable t                | DIL            |                   |                  |                |        |

|              |            | errupt enabled<br>errupt disabled |                |                   |                  |                |        |

| oit O        |            | imer5 Interrupt Er                | nable bit      |                   |                  |                |        |

|              | 1 = Timer5 | •                                 |                |                   |                  |                |        |

|              |            | Interrunt enabled                 | 1              |                   |                  |                |        |

## 14.0 TIMER2 MODULE

The Timer2 module has the following features:

- 8-bit Timer register (TMR2)

- 8-bit Period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register, shown in Register 14-1. TMR2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption. Figure 14-1 is a simplified block diagram of the Timer2 module. Register 14-1 shows the Timer2 Control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

## 14.1 Timer2 Operation

Timer2 can be used as the PWM time base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T2CKPS<1:0> (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt, latched in flag bit, TMR2IF (PIR1<1>).

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh.

The prescaler and postscaler counters are cleared when any of the following occurs:

- · A write to the TMR2 register

- A write to the T2CON register

- Any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|-------|---------|---------|---------|---------|--------|---------|---------|

| —     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |         |         |         |         |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| DIL 7   | Unimplemented: Read as 0                         |

|---------|--------------------------------------------------|

| bit 6-3 | TOUTPS<3:0>: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                             |

|         | 0001 = 1:2 Postscale                             |

|         | •                                                |

|         | •                                                |

|         | •                                                |

|         | 1111 = 1:16 Postscale                            |

| bit 2   | TMR2ON: Timer2 On bit                            |

|         | 1 = Timer2 is on                                 |

|         | 0 = Timer2 is off                                |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits   |

|         | 00 = Prescaler is 1                              |

|         | 01 = Prescaler is 4                              |

|         | 1x = Prescaler is 16                             |

|         |                                                  |

#### 17.1.8 SPECIAL EVENT TRIGGER (CAP1 ONLY)

The Special Event Trigger mode of IC1 (CAP1M<3:0> = 1110 or 1111) enables the Special Event Trigger signal. The trigger signal can be used as the Special Event Trigger Reset input to TMR5, resetting the timer when the specific event happens on IC1. The events are summarized in Table 17-2.

| CAP1M<3:0> | Description                                                        |

|------------|--------------------------------------------------------------------|

| 1110       | The trigger occurs on every <b>falling</b> edge on the CAP1 input. |

| 1111       | The trigger occurs on every <b>rising</b> edge on the CAP1 input.  |

## 17.1.9 OPERATING MODES SUMMARY

Table 17-3 shows a summary of the input capture configuration when used in conjunction with the TMR5 timer resource.

#### 17.1.10 OTHER OPERATING MODES

Although the IC and QEI submodules are mutually exclusive, the IC can be reconfigured to work with the QEI module to perform specific functions. In effect, the QEI "borrows" hardware from the IC to perform these operations.

For velocity measurement, the QEI uses dedicated hardware in channel IC1. The CAP1BUF registers are remapped, becoming the VELR registers. Its operation and use are described in **Section 17.2.6** "**Velocity Measurement**".

While in QEI mode, the CAP2BUF and CAP3BUF registers of channel IC2 and IC3 are used for position determination. They are remapped as the POSCNT and MAXCNT Buffer registers, respectively.

| Pin  | CAPxM     | Mode                                              | Timer | Reset Timer<br>on Capture | Description                                                                             |

|------|-----------|---------------------------------------------------|-------|---------------------------|-----------------------------------------------------------------------------------------|

| CAP1 | 0001-0100 | Edge Capture                                      | TMR5  | optional <sup>(1)</sup>   | Simple Edge Capture mode (includes a selectable prescaler).                             |

|      | 0101      | Period Measurement                                | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on period boundaries.                                                   |

|      | 0110-0111 | Pulse-Width<br>Measurement                        | TMR5  | always                    | Captures Timer5 on pulse boundaries.                                                    |

|      | 1000      | Input Capture on State<br>Change                  | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on state change.                                                        |

|      | 1110-1111 | Special Event Trigger<br>(rising or falling edge) | TMR5  | optional <sup>(2)</sup>   | Used as a Special Event Trigger to be used with the Timer5 or other peripheral modules. |

| CAP2 | 0001-0100 | Edge Capture                                      | TMR5  | optional <sup>(1)</sup>   | Simple Edge Capture mode (includes a selectable prescaler).                             |

|      | 0101      | Period Measurement                                | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on period boundaries.                                                   |

|      | 0110-0111 | Pulse-Width<br>Measurement                        | TMR5  | always                    | Captures Timer5 on pulse boundaries.                                                    |

|      | 1000      | Input Capture on State<br>Change                  | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on state change.                                                        |

| CAP3 | 0001-0100 | Edge Capture                                      | TMR5  | optional <sup>(1)</sup>   | Simple Edge Capture mode (includes a selectable prescaler).                             |

|      | 0101      | Period Measurement                                | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on period boundaries.                                                   |

|      | 0110-0111 | Pulse-Width<br>Measurement                        | TMR5  | always                    | Captures Timer5 on pulse boundaries.                                                    |

|      | 1000      | Input Capture on State<br>Change                  | TMR5  | optional <sup>(1)</sup>   | Captures Timer5 on state change.                                                        |

TABLE 17-3: INPUT CAPTURE TIME BASE RESET SUMMARY

Note 1: Timer5 may be reset on capture events only when CAPxREN = 1.

**2:** Trigger mode will not reset Timer5 unless  $\overline{\text{RESEN}} = 0$  in the T5CON register.

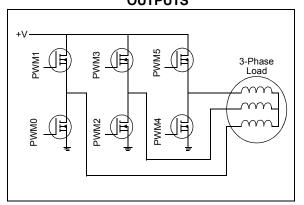

#### 18.6.5 COMPLEMENTARY PWM OPERATION

The Complementary mode of PWM operation is useful to drive one or more power switches in half-bridge configuration as shown in Figure 18-16. This inverter topology is typical for a 3-phase induction motor, brushless DC motor or a 3-phase Uninterruptible Power Supply (UPS) control applications.

Each upper/lower power switch pair is fed by a complementary PWM signal. Dead time may be optionally inserted during device switching, where both outputs are inactive for a short period (see **Section 18.7 "Dead-Time Generators"**).

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC0 register controls PWM1/PWM0 outputs

- PDC1 register controls PWM3/PWM2 outputs

- · PDC2 register controls PWM5/PWM4 outputs

- PDC3 register controls PWM7/PWM6 outputs

PWM1/3/5/7 are the main PWMs that are controlled by the PDCx registers and PWM0/2/4/6 are the complemented outputs. When using the PWMs to control the half bridge, the odd numbered PWMs can be used to control the upper power switch and the even numbered PWMs used for the lower switches.

#### FIGURE 18-16: TYPICAL LOAD FOR COMPLEMENTARY PWM OUTPUTS

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON0 register. The PWM I/O pins are set to Complementary mode by default upon all kinds of device Resets.

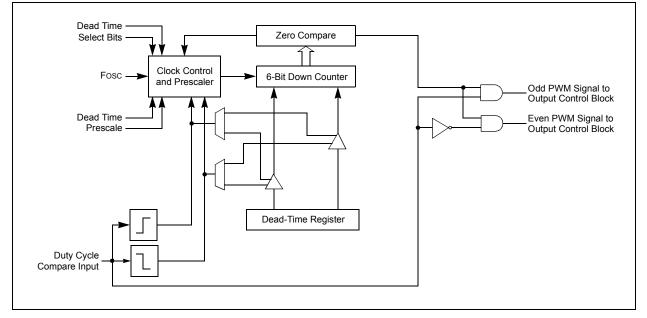

## **18.7 Dead-Time Generators**

In power inverter applications, where the PWMs are used in Complementary mode to control the upper and lower switches of a half-bridge, a dead-time insertion is highly recommended. The dead-time insertion keeps both outputs in inactive state for a brief time. This avoids any overlap in the switching during the state change of the power devices due to TON and TOFF characteristics.

Because the power output devices cannot switch instantaneously, some amount of time must be provided between the turn-off event of one PWM output in a complementary pair and the turn-on event of the other transistor. The PWM module allows dead time to be programmed. The following sections explain the dead-time block in detail.

## 18.7.1 DEAD-TIME INSERTION

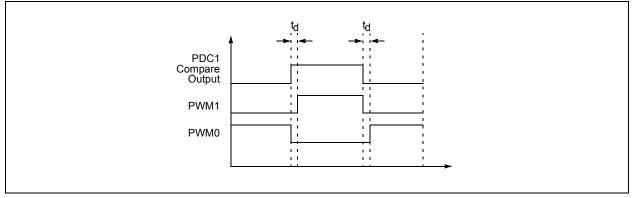

Each complementary output pair for the PWM module has a 6-bit down counter used to produce the dead-time insertion. As shown in Figure 18-17, each dead-time unit has a rising and falling edge detector connected to the duty cycle comparison output. The dead time is loaded into the timer on the detected PWM edge event. Depending on whether the edge is rising or falling, one of the transitions on the complementary outputs is delayed until the timer counts down to zero. A timing diagram, indicating the dead-time insertion for one pair of PWM outputs, is shown in Figure 18-18.

FIGURE 18-17: DEAD-TIME CONTROL UNIT BLOCK DIAGRAM FOR ONE PWM OUTPUT PAIR

## FIGURE 18-18: DEAD-TIME INSERTION FOR COMPLEMENTARY PWM

## 18.10.3 OUTPUT OVERRIDE EXAMPLES

Figure 18-21 shows an example of a waveform that might be generated using the PWM output override feature. The figure shows a six-step commutation sequence for a BLDC motor. The motor is driven through a 3-phase inverter as shown in Figure 18-16. When the appropriate rotor position is detected, the PWM outputs are switched to the next commutation state in the sequence. In this example, the PWM outputs are driven to specific logic states. The OVDCOND and OVDCONS register values used to generate the signals in Figure 18-21 are given in Table 18-4. The PWM Duty Cycle registers may be used in conjunction with the OVDCOND and OVDCONS registers. The Duty Cycle registers control the average voltage across the load and the OVDCOND and OVDCONS registers control the commutation sequence. Figure 18-22 shows the waveforms, while Table 18-4 and Table 18-5 show the OVDCOND and OVDCONS register values used to generate the signals.

## REGISTER 18-6: OVDCOND: OUTPUT OVERRIDE CONTROL REGISTER

| R/W-1                | R/W-1                | R/W-1            | R/W-1 | R/W-1             | R/W-1           | R/W-1           | R/W-1 |  |

|----------------------|----------------------|------------------|-------|-------------------|-----------------|-----------------|-------|--|

| POVD7 <sup>(1)</sup> | POVD6 <sup>(1)</sup> | POVD5            | POVD4 | POVD3             | POVD2           | POVD1           | POVD0 |  |

| bit 7 bit            |                      |                  |       |                   |                 |                 |       |  |

|                      |                      |                  |       |                   |                 |                 |       |  |

| Legend:              |                      |                  |       |                   |                 |                 |       |  |

| R = Readable bit     |                      | W = Writable bit |       | U = Unimplem      | ented bit, read | as '0'          |       |  |

| -n = Value at POR    |                      | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkn | own   |  |

#### bit 7-0 **POVD<7:0>:** PWM Output Override bits

1 = Output on PWM I/O pin is controlled by the value in the Duty Cycle register and the PWM time base

0 = Output on PWM I/O pin is controlled by the value in the corresponding POUT bit

**Note 1:** Unimplemented in PIC18F2331/2431 devices; maintain these bits clear.

## **REGISTER 18-7:** OVDCONS: OUTPUT STATE REGISTER<sup>(1,2)</sup>

| R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|-------|-------|-------|-------|-------|-------|

| POUT7 <sup>(1)</sup> | POUT6 <sup>(1)</sup> | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| bit 7                |                      |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 POUT<7:0>: PWM Manual Output bits

1 = Output on PWM I/O pin is active when the corresponding PWM output override bit is cleared

0 = Output on PWM I/O pin is inactive when the corresponding PWM output override bit is cleared

Note 1: Unimplemented in PIC18F2331/2431 devices; maintain these bits clear.

2: With PWMs configured in Complementary mode, the output of even numbered PWM (PM0,2,4) will be complementary of the output of odd PWM (PWM1,3,5), irrespective of the POUT bit setting.

## 18.11.3 PWM OUTPUT PIN RESET STATES

The PWMPIN Configuration bit determines the PWM output pins to be PWM output pins or digital I/O pins, after the device comes out of Reset. If the PWMPIN Configuration bit is unprogrammed (default), the PWMEN<2:0> control bits will be cleared on a device Reset. Consequently, all PWM outputs will be tri-stated and controlled by the corresponding PORT and TRIS registers. If the PWMPIN Configuration bit is programmed low, the PWMEN<2:0> control bits will be set, as follows, on a device Reset:

- PWMEN<2:0> = 101 if device has 8 PWM pins (PIC18F4331/4431 devices)

- PWMEN<2:0> = 100 if device has 6 PWM pins (PIC18F2331/2431 devices)

All PWM pins will be enabled for PWM output and will have the output polarity defined by the HPOL and LPOL Configuration bits.

## 18.12 PWM Fault Inputs

There are two Fault inputs associated with the PWM module. The main purpose of the input Fault pins is to disable the PWM output signals and drive them into an inactive state. The action of the Fault inputs is performed directly in hardware so that when a Fault occurs, it can be managed quickly and the PWM outputs are put into an inactive state to save the power devices connected to the PWMs.

The PWM Fault inputs are FLTA and FLTB, which can come from I/O pins, the CPU or another module. The FLTA and FLTB pins are active-low inputs so it is easy to "OR" many sources to the same input. FLTB and its associated logic are not implemented on PIC18F2331/2431 devices.

The FLTCONFIG register (Register 18-8) defines the settings of FLTA and FLTB inputs.

| Note: | The inactive state of the PWM pins are     |

|-------|--------------------------------------------|

|       | dependent on the HPOL and LPOL Con-        |

|       | figuration bit settings, which define the  |

|       | active and inactive state for PWM outputs. |

#### 18.12.1 FAULT PIN ENABLE BITS

By setting the bits, FLTAEN and FLTBEN in the FLTCONFIG register, the corresponding Fault inputs are enabled. If both bits are cleared, then the Fault inputs have no effect on the PWM module.

#### 18.12.2 MFAULT INPUT MODES

The FLTAMOD and FLTBMOD bits in the FLTCONFIG register determine the modes of PWM I/O pins that are deactivated when they are overridden by Fault input.

The FLTAS and FLTBS bits in the FLTCONFIG register give the status of Fault A and Fault B inputs.

Each of the Fault inputs have two modes of operation:

#### • Inactive Mode (FLTxMOD = 0)

This is a Catastrophic Fault Management mode. When the Fault occurs in this mode, the PWM outputs are deactivated. The PWM pins will remain in Inactivate mode until the Fault is cleared (Fault input is driven high) and the corresponding Fault Status bit has been cleared in software. The PWM outputs are enabled immediately at the beginning of the following PWM period, after the Fault Status bit (FLTxS) is cleared.

#### • Cycle-by-Cycle Mode (FLTxMOD = 1)

When the Fault occurs in this mode, the PWM outputs are deactivated. The PWM outputs will remain in the defined Fault states (all PWM outputs inactive) for as long as the Fault pin is held low. After the Fault pin is driven high, the PWM outputs will return to normal operation at the beginning of the following PWM period and the FLTxS bit is automatically cleared.

| U-0        | R-1                                                                                                                     | U-0                                                                                                                                                                                                                                                    | R/W-1           | R/W-0                       | U-0            | R/W-0           | R/W-0           |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|----------------|-----------------|-----------------|--|--|--|--|--|

| —          | RCIDL                                                                                                                   |                                                                                                                                                                                                                                                        | SCKP            | BRG16                       | —              | WUE             | ABDEN           |  |  |  |  |  |

| bit 7      |                                                                                                                         |                                                                                                                                                                                                                                                        |                 |                             |                |                 | bit             |  |  |  |  |  |

|            |                                                                                                                         |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

| Legend:    |                                                                                                                         |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

| R = Reada  | able bit                                                                                                                | W = Writable                                                                                                                                                                                                                                           | bit             | U = Unimplem                | ented bit, rea | d as '0'        |                 |  |  |  |  |  |

| -n = Value | e at POR                                                                                                                | '1' = Bit is se                                                                                                                                                                                                                                        | t               | '0' = Bit is clea           | ared           | x = Bit is unki | nown            |  |  |  |  |  |

| bit 7      | Unimplemen                                                                                                              | ted: Read as                                                                                                                                                                                                                                           | 0'              |                             |                |                 |                 |  |  |  |  |  |

| bit 6      | RCIDL: Rece                                                                                                             | eive Operation                                                                                                                                                                                                                                         | Idle Status bit |                             |                |                 |                 |  |  |  |  |  |

|            |                                                                                                                         | 1 = Receiver is Idle<br>0 = Receive in progress                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

| bit 5      |                                                                                                                         | ited: Read as '                                                                                                                                                                                                                                        | 0'              |                             |                |                 |                 |  |  |  |  |  |

| bit 4      | SCKP: Synchronous Clock Polarity Select bit                                                                             |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

|            | Asynchronous mode:<br>Unused in this mode.                                                                              |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

|            | Synchronous mode:                                                                                                       |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

|            | <ul> <li>1 = Idle state for clock (CK) is a high level</li> <li>0 = Idle state for clock (CK) is a low level</li> </ul> |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

| bit 3      | BRG16: 16-Bit Baud Rate Register Enable bit                                                                             |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

|            |                                                                                                                         |                                                                                                                                                                                                                                                        |                 | H and SPBRG                 | mode), SPBF    | RGH value igno  | ored            |  |  |  |  |  |

| bit 2      | Unimplemen                                                                                                              | ted: Read as                                                                                                                                                                                                                                           | 0'              |                             |                |                 |                 |  |  |  |  |  |

| bit 1      | WUE: Wake-                                                                                                              | up Enable bit                                                                                                                                                                                                                                          |                 |                             |                |                 |                 |  |  |  |  |  |

|            | hardware                                                                                                                |                                                                                                                                                                                                                                                        | ising edge      | RX pin – interru<br>etected | pt generated   | on falling edge | ; bit cleared i |  |  |  |  |  |

|            | Synchronous mode:<br>Unused in this mode.                                                                               |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

| bit 0      | ABDEN: Auto-Baud Detect Enable bit                                                                                      |                                                                                                                                                                                                                                                        |                 |                             |                |                 |                 |  |  |  |  |  |

|            | 1 = Enable b<br>cleared in                                                                                              | <ul> <li><u>Asynchronous mode:</u></li> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) cleared in hardware upon completion.</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |                 |                             |                |                 |                 |  |  |  |  |  |

|            | Synchronous<br>Unused in thi                                                                                            | mode:                                                                                                                                                                                                                                                  |                 | ·                           |                |                 |                 |  |  |  |  |  |

## REGISTER 23-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0                              | U-0   | U-0 | U-0 | R/C-1                | R/C-1                | R/C-1              | R/C-1              |  |  |

|----------------------------------|-------|-----|-----|----------------------|----------------------|--------------------|--------------------|--|--|

| —                                | _     | _   | _   | CP3 <sup>(1,2)</sup> | CP2 <sup>(1,2)</sup> | CP1 <sup>(2)</sup> | CP0 <sup>(2)</sup> |  |  |

| bit 7                            | bit 7 |     |     |                      |                      |                    |                    |  |  |

|                                  |       |     |     |                      |                      |                    |                    |  |  |

| Legend:                          |       |     |     |                      |                      |                    |                    |  |  |

| R = Readable bit C = Clearable b |       |     | bit | U = Unimplem         | nented bit, read     | as '0'             |                    |  |  |

| -n = Value when device is unprogrammed |                                                                                                                      | U = Unchanged from programmed state |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| bit 7-4                                | Unimplemented: Read as '0'                                                                                           |                                     |

| bit 3                                  | <b>CP3:</b> Code Protection bit <sup>(1,2)</sup>                                                                     |                                     |

|                                        | <ul><li>1 = Block 3 is not code-protected</li><li>0 = Block 3 is code-protected</li></ul>                            |                                     |

| bit 2                                  | <b>CP2:</b> Code Protection bit <sup>(1,2)</sup>                                                                     |                                     |

|                                        | <ol> <li>1 = Block 2 is not code-protected</li> <li>0 = Block 2 is code-protected</li> </ol>                         |                                     |

| bit 1                                  | CP1: Code Protection bit <sup>(2)</sup>                                                                              |                                     |

|                                        | <ol> <li>1 = Block 1 is not code-protected</li> <li>0 = Block 1 is code-protected</li> </ol>                         |                                     |

| bit 0                                  | <b>CP0:</b> Code Protection bit <sup>(2)</sup><br>1 = Block 0 is not code-protected<br>0 = Block 0 is code-protected |                                     |

|                                        |                                                                                                                      |                                     |

Note 1: Unimplemented in PIC18F2331/4331 devices; maintain this bit set.

2: Refer to Figure 23-5 for block boundary addresses.

## REGISTER 23-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1              | R/C-1              | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|--------------------|-----|-----|-----|-----|-----|-------|

| CPD <sup>(1)</sup> | CPB <sup>(1)</sup> | —   | —   | —   | —   | —   | _     |

| bit 7              |                    |     |     |     |     |     | bit 0 |

| Legend:                |                   |                                     |  |

|------------------------|-------------------|-------------------------------------|--|

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |  |

| -n = Value when device | is unprogrammed   | U = Unchanged from programmed state |  |

| bit 7   | <b>CPD:</b> Data EEPROM Code Protection bit <sup>(1)</sup>                                      |

|---------|-------------------------------------------------------------------------------------------------|

|         | 1 = Data EEPROM is not code-protected<br>0 = Data EEPROM is code-protected                      |

| bit 6   | <b>CPB:</b> Boot Block Code Protection bit <sup>(1)</sup>                                       |

|         | <ul><li>1 = Boot Block is not code-protected</li><li>0 = Boot Block is code-protected</li></ul> |

| bit 5-0 | Unimplemented: Read as '0'                                                                      |

#### Note 1: Refer to Figure 23-5 for block boundary addresses.

| SLE                                | ΞP                  | Enter Sleep Mode                                               |                                       |            | SUBFWB |                                                                       | Subtract f from W with Borrow |                                          |                      |  |  |  |

|------------------------------------|---------------------|----------------------------------------------------------------|---------------------------------------|------------|--------|-----------------------------------------------------------------------|-------------------------------|------------------------------------------|----------------------|--|--|--|

| Synta                              | X:                  | [label]                                                        | SLEEP                                 |            | Synta  | ax:                                                                   | [ label ]                     | [ <i>label</i> ] SUBFWB f[,d[,a]]        |                      |  |  |  |

| Opera                              |                     | None                                                           |                                       |            | Oper   | ands:                                                                 | 0 ≤ f ≤ 255                   |                                          |                      |  |  |  |

| Operation: $00h \rightarrow WDT$ , |                     |                                                                |                                       |            |        | d ∈ [0,1]                                                             |                               |                                          |                      |  |  |  |

|                                    |                     |                                                                | postscaler,                           |            |        |                                                                       | a ∈ [0,1]                     | <del></del>                              |                      |  |  |  |

|                                    |                     | $1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD}$ |                                       |            | •      | ation:                                                                |                               | $(\overline{C}) \rightarrow \text{dest}$ |                      |  |  |  |

| Statu                              | s Affected:         | TO, PD                                                         |                                       |            |        | is Affected:                                                          | N, OV, C,                     |                                          |                      |  |  |  |

|                                    |                     | 0000                                                           | 0000 000                              | 0 0011     | Enco   | oding:                                                                | 0101                          |                                          | ff ffff              |  |  |  |

| Enco                               | 0                   |                                                                |                                       |            | Desc   | ription:                                                              |                               | egister, 'f', and                        |                      |  |  |  |

| Desci                              | ription:            |                                                                | r-Down status<br>he Time-out sta      |            |        |                                                                       |                               | om W (2's con<br>f 'd' is '0', the r     |                      |  |  |  |

|                                    |                     | is set. Wat                                                    | tchdog Timer a                        |            |        |                                                                       | in W. If 'd'                  | is '1', the resu                         | t is stored in       |  |  |  |

|                                    |                     | scaler are                                                     |                                       | Sloop modo |        |                                                                       |                               |                                          | Access Bank          |  |  |  |

|                                    |                     |                                                                | ssor is put into<br>scillator stoppe  |            |        |                                                                       |                               | ected, overridir<br>' is '1', then the   |                      |  |  |  |

| Word                               | s:                  | 1                                                              | · · · · · · · · · · · · · · · · · · · |            |        |                                                                       |                               | s per the BSR                            |                      |  |  |  |

| Cycle                              |                     | 1                                                              |                                       |            | Word   | ls:                                                                   | 1                             |                                          |                      |  |  |  |

| -                                  | cle Activity:       |                                                                |                                       |            | Cycle  | es:                                                                   | 1                             |                                          |                      |  |  |  |

| QO                                 | Q1                  | Q2                                                             | Q3                                    | Q4         | QC     | ycle Activity:                                                        |                               |                                          |                      |  |  |  |

| Ī                                  | Decode              | No                                                             | Process                               | Go to      |        | Q1                                                                    | Q2                            | Q3                                       | Q4                   |  |  |  |

|                                    |                     | operation                                                      | Data                                  | Sleep      |        | Decode                                                                | Read                          | Process                                  | Write to destination |  |  |  |

| Exam                               | nle.                | SLEEP                                                          |                                       |            | Exan   | register 'f'     Data     destination       Example 1:     SUBFWB REG |                               |                                          |                      |  |  |  |

| -                                  | Before Instruc      |                                                                |                                       |            |        | Before Instru                                                         |                               |                                          |                      |  |  |  |