Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 9x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4331-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

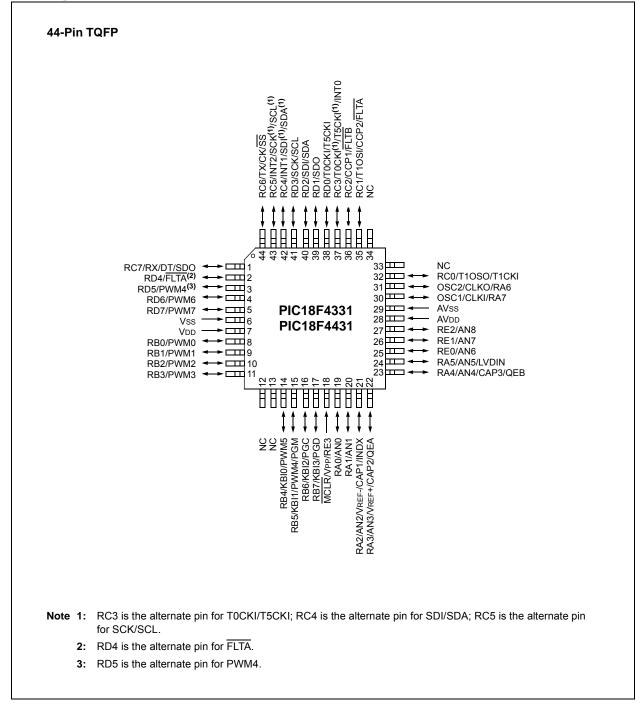

#### **Pin Diagrams (Continued)**

#### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.2.3 CONSIDERATIONS WHEN USING BOR

When the Brown-out Reset (BOR) feature is enabled, a sudden change in VDD may result in a spontaneous BOR event. This can happen when the microcontroller is operating under normal operating conditions, regardless of what the BOR set point has been programmed to, and even if VDD does not approach the set point. The precipitating factor in these BOR events is a rise or fall in VDD with a slew rate faster than  $0.15V/\mu s$ .

An application that incorporates adequate decoupling between the power supplies will not experience such rapid voltage changes. Additionally, the use of an electrolytic tank capacitor across VDD and Vss, as described above, will be helpful in preventing high slew rate transitions.

If the application has components that turn on or off, and share the same VDD circuit as the microcontroller, the BOR can be disabled in software by using the SBOREN bit before switching the component. Afterwards, allow a small delay before re-enabling the BOR. By doing this, it is ensured that the BOR is disabled during the interval that might cause high slew rate changes of VDD.

Note: Not all devices incorporate software BOR control. See Section 5.0 "Reset" for device-specific information.

#### 3.6 Internal Oscillator Block

The PIC18F2331/2431/4331/4431 devices include an internal oscillator block, which generates two different clock signals; either can be used as the system's clock source. This can eliminate the need for external oscillator circuits on the OSC1 and/or OSC2 pins.

The main output (INTOSC) is an 8 MHz clock source, which can be used to directly drive the system clock. It also drives a postscaler, which can provide a range of clock frequencies from 125 kHz to 4 MHz. The INTOSC output is enabled when a system clock frequency from 125 kHz to 8 MHz is selected.

The other clock source is the internal RC oscillator (INTRC), which provides a 31 kHz output. The INTRC oscillator is enabled by selecting the internal oscillator block as the system clock source, or when any of the following are enabled:

- Power-up Timer

- Fail-Safe Clock Monitor

- · Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 23.0 "Special Features of the CPU".

The clock source frequency (INTOSC direct, INTRC direct or INTOSC postscaler) is selected by configuring the IRCF bits of the OSCCON register (Register 3-2).

#### 3.6.1 INTIO MODES

Using the internal oscillator as the clock source can eliminate the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

#### 3.6.2 INTRC OUTPUT FREQUENCY

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz. This changes the frequency of the INTRC source from its nominal 31.25 kHz. Peripherals and features that depend on the INTRC source will be affected by this shift in frequency.

#### 3.6.3 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory, but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 3-1). Each increment may adjust the FRC frequency by varying amounts and may not be monotonic. The next closest frequency may be multiple steps apart.

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

#### 3.6.4 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. This frequency, however, may drift as the VDD or temperature changes, which can affect the controller operation in a variety of ways.

The INTOSC frequency can be adjusted by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make an adjustment, in which direction it should be made, and in some cases, how large a change is needed. Three compensation techniques are discussed in Section 3.6.4.1 "Compensating with the EUSART", Section 3.6.4.2 "Compensating with the Timers" and Section 3.6.4.3 "Compensating with the CCP Module in Capture Mode", but other techniques may be used.

#### 6.5.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes.

Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a four-bit Bank Pointer. Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the four Most Significant bits of a location's address; the instruction itself includes the eight Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 6-6.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to the eight-bit address of F9h, while the BSR is 0Fh, will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-5 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

#### 6.5.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected; otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

#### 6.5.3 GENERAL PURPOSE REGISTER (GPR) FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

| R/W-1      | R/W-1                                                                                                                                             | U-0                                      | R/W-0            | R/W-0            | U-0             | R/W-0              | R/W-0            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------------|--------------------|------------------|

| INT2IF     | P INT1IP                                                                                                                                          | —                                        | INT2IE           | INT1IE           | —               | INT2IF             | INT1IF           |

| bit 7      |                                                                                                                                                   |                                          |                  |                  |                 |                    | bit 0            |

| Lonondi    |                                                                                                                                                   |                                          |                  |                  |                 |                    |                  |

| Legend:    |                                                                                                                                                   |                                          | - :4             |                  |                 | (O)                |                  |

| R = Read   |                                                                                                                                                   | W = Writable                             | DIL              | •                | nented bit, rea |                    |                  |

| -n = Value | alPOR                                                                                                                                             | '1' = Bit is set                         |                  | '0' = Bit is cle | areo            | x = Bit is unkr    | lown             |

| bit 7      | INT2IP: INT2                                                                                                                                      | External Interre                         | upt Priority bit |                  |                 |                    |                  |

|            | 1 = High prio<br>0 = Low prior                                                                                                                    | •                                        |                  |                  |                 |                    |                  |

| bit 6      | INT1IP: INT1                                                                                                                                      | External Interre                         | upt Priority bit |                  |                 |                    |                  |

|            | 1 = High prio<br>0 = Low prior                                                                                                                    |                                          |                  |                  |                 |                    |                  |

| bit 5      | Unimplemen                                                                                                                                        | ted: Read as 'd                          | )'               |                  |                 |                    |                  |

| bit 4      | INT2IE: INT2                                                                                                                                      | External Interre                         | upt Enable bit   |                  |                 |                    |                  |

|            |                                                                                                                                                   | the INT2 extern the INT2 extern          |                  |                  |                 |                    |                  |

| bit 3      | INT1IE: INT1                                                                                                                                      | External Interre                         | upt Enable bit   |                  |                 |                    |                  |

|            | <ul> <li>1 = Enables the INT1 external interrupt</li> <li>0 = Disables the INT1 external interrupt</li> </ul>                                     |                                          |                  |                  |                 |                    |                  |

| bit 2      | Unimplemen                                                                                                                                        | ted: Read as 'o                          | )'               |                  |                 |                    |                  |

| bit 1      | INT2IF: INT2                                                                                                                                      | INT2IF: INT2 External Interrupt Flag bit |                  |                  |                 |                    |                  |

|            | 1 = The INT2 external interrupt occurred (must be cleared in software)                                                                            |                                          |                  |                  |                 |                    |                  |

|            | 0 = The INT2 external interrupt did not occur                                                                                                     |                                          |                  |                  |                 |                    |                  |

| bit 0      | INT1IF: INT1 External Interrupt Flag bit                                                                                                          |                                          |                  |                  |                 |                    |                  |

|            | <ul> <li>1 = The INT1 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT1 external interrupt did not occur</li> </ul> |                                          |                  |                  |                 |                    |                  |

|            |                                                                                                                                                   |                                          | apt dia not 00   | oui              |                 |                    |                  |

| Note:      | Interrupt flag bits                                                                                                                               |                                          |                  |                  |                 |                    |                  |

|            | enable bit or the g                                                                                                                               |                                          |                  |                  |                 | ate interrupt flag | y bits are clear |

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

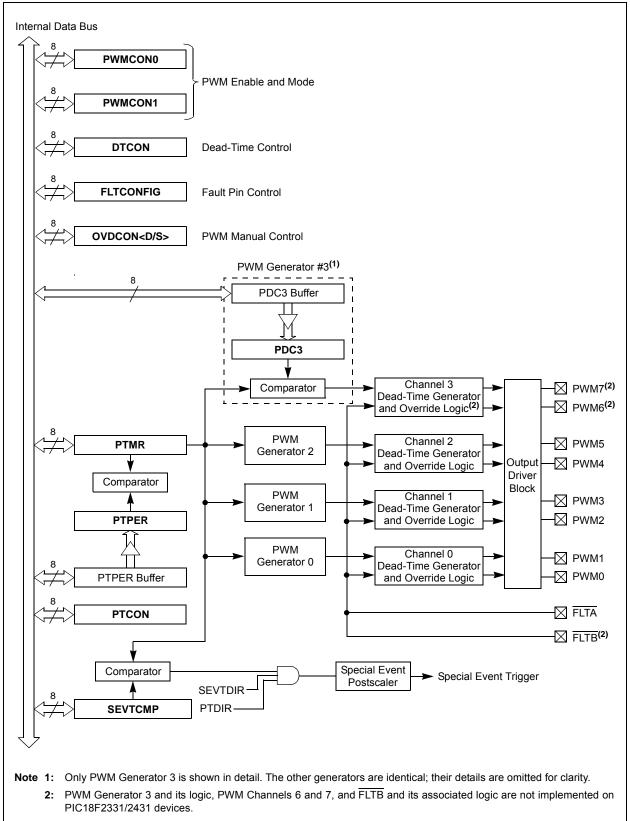

#### FIGURE 18-1: POWER CONTROL PWM MODULE BLOCK DIAGRAM

#### 18.4.2 INTERRUPTS IN SINGLE-SHOT MODE

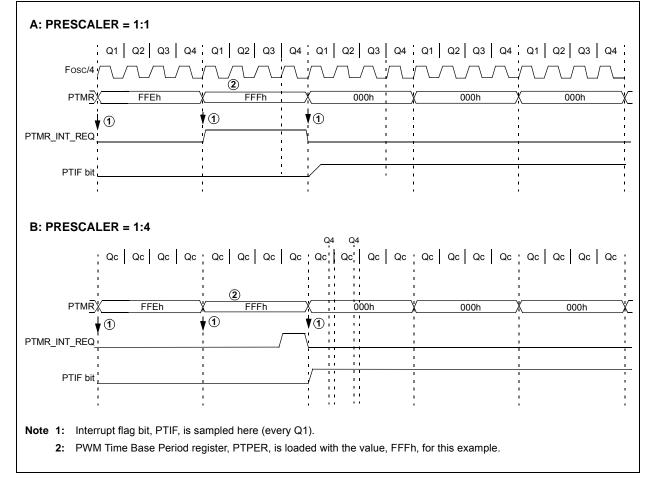

When the PWM time base is in the Single-Shot mode (PTMOD<1:0> = 01), an interrupt event is generated when a match with the PTPER register occurs. The PWM Time Base register (PTMR) is reset to zero on the following input clock edge and the PTEN bit is cleared. The postscaler selection bits have no effect in this Timer mode.

#### 18.4.3 INTERRUPTS IN CONTINUOUS UP/DOWN COUNT MODE

In the Continuous Up/Down Count mode (PTMOD<1:0> = 10), an interrupt event is generated each time the value of the PTMR register becomes zero and the PWM time base begins to count upwards. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events. Figure 18-7 shows the interrupts in Continuous Up/Down Count mode.

#### FIGURE 18-6: PWM TIME BASE INTERRUPT TIMING, SINGLE-SHOT MODE

#### 18.11.3 PWM OUTPUT PIN RESET STATES

The PWMPIN Configuration bit determines the PWM output pins to be PWM output pins or digital I/O pins, after the device comes out of Reset. If the PWMPIN Configuration bit is unprogrammed (default), the PWMEN<2:0> control bits will be cleared on a device Reset. Consequently, all PWM outputs will be tri-stated and controlled by the corresponding PORT and TRIS registers. If the PWMPIN Configuration bit is programmed low, the PWMEN<2:0> control bits will be set, as follows, on a device Reset:

- PWMEN<2:0> = 101 if device has 8 PWM pins (PIC18F4331/4431 devices)

- PWMEN<2:0> = 100 if device has 6 PWM pins (PIC18F2331/2431 devices)

All PWM pins will be enabled for PWM output and will have the output polarity defined by the HPOL and LPOL Configuration bits.

#### 18.12 PWM Fault Inputs

There are two Fault inputs associated with the PWM module. The main purpose of the input Fault pins is to disable the PWM output signals and drive them into an inactive state. The action of the Fault inputs is performed directly in hardware so that when a Fault occurs, it can be managed quickly and the PWM outputs are put into an inactive state to save the power devices connected to the PWMs.

The PWM Fault inputs are FLTA and FLTB, which can come from I/O pins, the CPU or another module. The FLTA and FLTB pins are active-low inputs so it is easy to "OR" many sources to the same input. FLTB and its associated logic are not implemented on PIC18F2331/2431 devices.

The FLTCONFIG register (Register 18-8) defines the settings of FLTA and FLTB inputs.

| Note: | The inactive state of the PWM pins are     |

|-------|--------------------------------------------|

|       | dependent on the HPOL and LPOL Con-        |

|       | figuration bit settings, which define the  |

|       | active and inactive state for PWM outputs. |

#### 18.12.1 FAULT PIN ENABLE BITS

By setting the bits, FLTAEN and FLTBEN in the FLTCONFIG register, the corresponding Fault inputs are enabled. If both bits are cleared, then the Fault inputs have no effect on the PWM module.

#### 18.12.2 MFAULT INPUT MODES

The FLTAMOD and FLTBMOD bits in the FLTCONFIG register determine the modes of PWM I/O pins that are deactivated when they are overridden by Fault input.

The FLTAS and FLTBS bits in the FLTCONFIG register give the status of Fault A and Fault B inputs.

Each of the Fault inputs have two modes of operation:

#### • Inactive Mode (FLTxMOD = 0)

This is a Catastrophic Fault Management mode. When the Fault occurs in this mode, the PWM outputs are deactivated. The PWM pins will remain in Inactivate mode until the Fault is cleared (Fault input is driven high) and the corresponding Fault Status bit has been cleared in software. The PWM outputs are enabled immediately at the beginning of the following PWM period, after the Fault Status bit (FLTxS) is cleared.

#### • Cycle-by-Cycle Mode (FLTxMOD = 1)

When the Fault occurs in this mode, the PWM outputs are deactivated. The PWM outputs will remain in the defined Fault states (all PWM outputs inactive) for as long as the Fault pin is held low. After the Fault pin is driven high, the PWM outputs will return to normal operation at the beginning of the following PWM period and the FLTxS bit is automatically cleared.

NOTES:

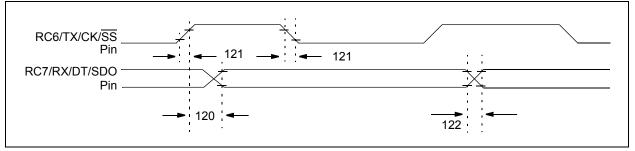

#### 20.3.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line, while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 20-7), and asynchronously if the device is in Sleep mode (Figure 20-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

### 20.3.4.1 Special Considerations Using Auto-Wake-up

Since Auto-Wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character

and cause data or framing errors. To work properly, therefore, the initial characters in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices, or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

### 20.3.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/ DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set), and the RCIF flag is set, should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

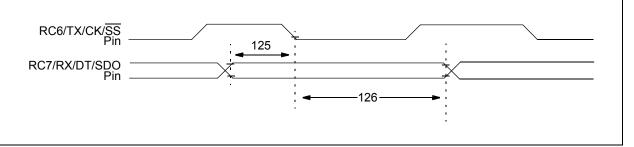

#### FIGURE 20-7: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

#### FIGURE 20-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

### 22.0 LOW-VOLTAGE DETECT (LVD)

PIC18F2331/2431/4331/4431 devices have a Low-Voltage Detect module (LVD), a programmable circuit that enables the user to specify a device voltage trip point. If the device experiences an excursion below the trip point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The Low-Voltage Detect Control register (Register 22-1) completely controls the operation of the LVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the LVD module is shown in Figure 22-1.

The module is enabled by setting the LVDEN bit, but the circuitry requires some time to stabilize each time that it is enabled. The IRVST bit is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and the IRVST bit is set. The module monitors for drops in VDD below a predetermined set point.

#### REGISTER 22-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0                                                                   | U-0                         | R-0              | R/W-0            | R/W-0                                | R/W-1                | R/W-0                | R/W-1                |

|-----------------------------------------------------------------------|-----------------------------|------------------|------------------|--------------------------------------|----------------------|----------------------|----------------------|

| _                                                                     |                             | IRVST            | LVDEN            | LVDL3 <sup>(1)</sup>                 | LVDL2 <sup>(1)</sup> | LVDL1 <sup>(1)</sup> | LVDL0 <sup>(1)</sup> |

| bit 7                                                                 |                             | •                |                  |                                      |                      |                      | bit 0                |

|                                                                       |                             |                  |                  |                                      |                      |                      |                      |

| Legend:                                                               |                             |                  |                  |                                      |                      |                      |                      |

| R = Readabl                                                           | le bit                      | W = Writable     | bit              | U = Unimplem                         | nented bit, read     | l as '0'             |                      |

| -n = Value at                                                         | t POR                       | '1' = Bit is set |                  | '0' = Bit is clea                    | ared                 | x = Bit is unkr      | nown                 |

|                                                                       |                             |                  |                  |                                      |                      |                      |                      |

| bit 7-6                                                               | Unimplemen                  | ted: Read as '   | )'               |                                      |                      |                      |                      |

| bit 5                                                                 | IRVST: Intern               | al Reference V   | oltage Stable    | Flag bit                             |                      |                      |                      |

|                                                                       | 1 = Indicates               | that the Low-V   | oltage Detect    | logic will generated                 | ate the interrup     | ot flag at the sp    | ecified voltage      |

|                                                                       | range                       |                  |                  |                                      |                      |                      |                      |

|                                                                       |                             |                  |                  | t logic will not<br>nould not be ena |                      | nterrupt flag at     | t the specified      |

| bit 4                                                                 | LVDEN: Low-                 | Voltage Detect   | Power Enable     | e bit                                |                      |                      |                      |

|                                                                       | 1 = Enables L               | VD, powers up    | LVD circuit      |                                      |                      |                      |                      |

|                                                                       | 0 = Disables                | LVD, powers do   | own LVD circu    | it                                   |                      |                      |                      |

| bit 3-0                                                               | LVDL<3:0>:                  | _ow-Voltage De   | etection Limit b | oits <sup>(1)</sup>                  |                      |                      |                      |

| 1111 = External analog input is used (input comes from the LVDIN pin) |                             |                  |                  |                                      |                      |                      |                      |

| 1110 = Maximum setting                                                |                             |                  |                  |                                      |                      |                      |                      |

|                                                                       | •                           |                  |                  |                                      |                      |                      |                      |

|                                                                       |                             |                  |                  |                                      |                      |                      |                      |

|                                                                       | •                           |                  |                  |                                      |                      |                      |                      |

|                                                                       | 0.010 = Minim               | um settina       |                  |                                      |                      |                      |                      |

|                                                                       | 0010 = Minim<br>0001 = Rese | 0                |                  |                                      |                      |                      |                      |

**Note 1:** LVDL<3:0> bit modes, which result in a trip point below the valid operating voltage of the device, are not tested.

#### 24.2 Instruction Set

| ADD   | DLW            | ADD Literal to W                                                                          |               |      |               |  |

|-------|----------------|-------------------------------------------------------------------------------------------|---------------|------|---------------|--|

| Synta | ax:            | [ <i>label</i> ] A                                                                        | DDLW          | k    |               |  |

| Oper  | ands:          | $0 \le k \le 25$                                                                          | 5             |      |               |  |

| Oper  | ation:         | (W) + k $\rightarrow$                                                                     | W             |      |               |  |

| Statu | s Affected:    | N, OV, C, DC, Z                                                                           |               |      |               |  |

| Enco  | ding:          | 0000                                                                                      | 1111          | kkkk | kkkk          |  |

| Desc  | ription:       | The contents of W are added to the<br>8-bit literal 'k' and the result is placed in<br>W. |               |      |               |  |

| Word  | ls:            | 1                                                                                         |               |      |               |  |

| Cycle | es:            | 1                                                                                         |               |      |               |  |

| QC    | ycle Activity: |                                                                                           |               |      |               |  |

|       | Q1             | Q2                                                                                        | Q3            | 5    | Q4            |  |

|       | Decode         | Read<br>literal 'k'                                                                       | Proce<br>Data |      | /rite to<br>W |  |

| Even  |                | ADDIN                                                                                     | 0.15          | ·    |               |  |

| ADDWF                      | ADD W to                                            | o f                                                                                            |                                                       |

|----------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Syntax:                    | [ label ] AD                                        | DWF f[,d[                                                                                      | ,a]]                                                  |

| Operands:                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                                                                                |                                                       |

| Operation:                 | (W) + (f) $\rightarrow$                             | dest                                                                                           |                                                       |

| Status Affected:           | N, OV, C, E                                         | DC, Z                                                                                          |                                                       |

| Encoding:                  | 0010                                                | 01da ff:                                                                                       | ff ffff                                               |

| Description:               | result is sto<br>result is sto<br>is '0', the A     | egister, 'f'. If 'd<br>ored in W. If 'd'<br>ored back in re<br>ccess Bank wi<br>che BSR is use | is '1', the<br>gister, 'f'. If 'a'<br>Il be selected. |

| Words:                     | 1                                                   |                                                                                                |                                                       |

| Cycles:                    | 1                                                   |                                                                                                |                                                       |

| Q Cycle Activity:          |                                                     |                                                                                                |                                                       |

| Q1                         | Q2                                                  | Q3                                                                                             | Q4                                                    |

| Decode                     | Read<br>register 'f'                                | Process<br>Data                                                                                | Write to destination                                  |

| Example:                   | ADDWF                                               | REG, W                                                                                         |                                                       |

| Before Instruc<br>W<br>REG | tion<br>= 0x17<br>= 0xC2                            |                                                                                                |                                                       |

After Instruction W

REG

=

=

0xD9

0xC2

Example: ADDLW 0x15

> Before Instruction W = 0x10 After Instruction

W = 0x25

| BTG          |                         | Bit Toggle                                                                                                                                                                                                                 | e f                   |                                                                                                                                                                                                                              | BOV                           | Branch if                   | Overflow                                                                                                                                                                                                              |                 |                                                                    |

|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------|

| Synta        | ix:                     | [ <i>label</i> ] BT                                                                                                                                                                                                        | G f,b[,a]             |                                                                                                                                                                                                                              | Syntax:                       | [label] BC                  | V n                                                                                                                                                                                                                   |                 |                                                                    |

| Oper         | ands:                   | $0 \leq f \leq 255$                                                                                                                                                                                                        |                       |                                                                                                                                                                                                                              | Operands:                     | -128 ≤ n ≤ ′                | 127                                                                                                                                                                                                                   |                 |                                                                    |

|              |                         | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                     |                       |                                                                                                                                                                                                                              | Operation:                    | if Overflow<br>(PC) + 2 + 2 | ,                                                                                                                                                                                                                     |                 |                                                                    |

| Oper         | ation:                  | $(\overline{f} < b >) \to f <$                                                                                                                                                                                             | b>                    |                                                                                                                                                                                                                              | Status Affected:              | None                        |                                                                                                                                                                                                                       |                 |                                                                    |

| Statu        | s Affected:             | None                                                                                                                                                                                                                       |                       |                                                                                                                                                                                                                              | Encoding:                     | 1110                        | 0100 nn                                                                                                                                                                                                               | nn nnnn         |                                                                    |

| Enco<br>Desc | ding:<br>ription:       | 0111bbbaffffffffBit 'b' in data memory location, 'f', is<br>inverted. If 'a' is '0', the Access Bank will<br>be selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected as<br>per the BSR value. |                       | 0111bbbaffffffffDescription:Bit 'b' in data memory location, 'f', is<br>inverted. If 'a' is '0', the Access Bank will<br>be selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected asDescription: |                               | 0                           | If the Overflow bit is '1', then the<br>program will branch.<br>The 2's complement number, '2n', is<br>added to the PC. Since the PC will ha<br>incremented to fetch the next<br>instruction, the new address will be |                 | hen the<br>ber, '2n', is<br>le PC will have<br>next<br>ess will be |

| Word         | s:                      | 1                                                                                                                                                                                                                          |                       |                                                                                                                                                                                                                              |                               | PC + 2 + 2r<br>two-cycle ir | n. This instruction                                                                                                                                                                                                   | tion is then a  |                                                                    |

| Cycle        | es:                     | 1                                                                                                                                                                                                                          |                       |                                                                                                                                                                                                                              | Words:                        | 1                           |                                                                                                                                                                                                                       |                 |                                                                    |

| QC           | cle Activity:           |                                                                                                                                                                                                                            |                       |                                                                                                                                                                                                                              | Cycles:                       | 1(2)                        |                                                                                                                                                                                                                       |                 |                                                                    |

|              | Q1<br>Decode            | Q2<br>Read<br>register 'f'                                                                                                                                                                                                 | Q3<br>Process<br>Data | Q4<br>Write<br>register 'f'                                                                                                                                                                                                  | Q Cycle Activity:<br>If Jump: | 1(2)                        |                                                                                                                                                                                                                       |                 |                                                                    |

|              |                         | register i                                                                                                                                                                                                                 | Data                  |                                                                                                                                                                                                                              | Q1                            | Q2                          | Q3                                                                                                                                                                                                                    | Q4              |                                                                    |

| Exam         |                         |                                                                                                                                                                                                                            | PORTC, 4              |                                                                                                                                                                                                                              | Decode                        | Read literal<br>'n'         | Process<br>Data                                                                                                                                                                                                       | Write to<br>PC  |                                                                    |

|              | Before Instruc<br>PORTC |                                                                                                                                                                                                                            | 0101 <b>[0x75]</b>    |                                                                                                                                                                                                                              | No<br>operation               | No<br>operation             | No<br>operation                                                                                                                                                                                                       | No<br>operation |                                                                    |

|              | After Instructio        |                                                                                                                                                                                                                            |                       |                                                                                                                                                                                                                              | If No Jump:                   |                             |                                                                                                                                                                                                                       |                 |                                                                    |

|              | PORTC                   | = 0110 0                                                                                                                                                                                                                   | 101 <b>[0x65]</b>     |                                                                                                                                                                                                                              | Q1                            | Q2                          | Q3                                                                                                                                                                                                                    | Q4              |                                                                    |

|              |                         |                                                                                                                                                                                                                            |                       |                                                                                                                                                                                                                              | Decode                        | Read literal<br>'n'         | Process<br>Data                                                                                                                                                                                                       | No<br>operation |                                                                    |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If Overflow = 1;<br>PC = address (JUMP)<br>If Overflow = 0;<br>PC = address (HERE + 2) | Example:                         | HERE    | BOV           | JUMP   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|---------------|--------|

| If Overflow = 1;<br>PC = address (JUMP)<br>If Overflow = 0;                                                                                              |                                  | on<br>= | address       | (HERE) |

|                                                                                                                                                          | If Overflow<br>PC<br>If Overflow | =       | address<br>0; | ( ,    |

| RCA   | LL             | Relative (                          | Call                             |     |           | RESET          |

|-------|----------------|-------------------------------------|----------------------------------|-----|-----------|----------------|

| Synta | ax:            | [label] RC                          | ALL n                            |     |           | Syntax:        |

| Oper  | ands:          | -1024 ≤ n ≤                         | 1023                             |     |           | Operands:      |

| Oper  | ation:         | $(PC) + 2 \rightarrow (PC) + 2 + 2$ | ,                                |     |           | Operation:     |

| Statu | is Affected:   | None                                |                                  |     |           | Status Affecte |

| Enco  | oding:         | 1101                                | lnnn n                           | nnn | nnnn      | Encoding:      |

| Desc  | cription:      | Subroutine from the cu              | call with a ju                   | • • |           | Description:   |

|       |                | address (Po                         | <i>,</i> .                       |     |           | Words:         |

|       |                |                                     | i, add the 2's<br>' to the PC. S |     |           | Cycles:        |

|       |                |                                     | nented to fe                     |     |           | Q Cycle Acti   |

|       |                | ,                                   | the new add                      |     |           | Q1             |

|       |                | two-cycle in                        |                                  |     | 5 a       | Deco           |

| Word  | ls:            | 1                                   |                                  |     |           |                |

| Cycle | es:            | 2                                   |                                  |     |           | Example:       |

| QC    | ycle Activity: |                                     |                                  |     |           | After Ins      |

|       | Q1             | Q2                                  | Q3                               |     | Q4        | Re             |

|       | Decode         | Read literal                        | Process                          | Wri | ite to PC | Fla            |

|       |                | 'n'                                 | Data                             |     |           |                |

|       |                | PUSH PC to<br>stack                 |                                  |     |           |                |

|       | No             | No                                  | No                               | _   | No        |                |

|       | 110            | 110                                 | INU                              |     | NU        |                |

operation operation

Example: HERE RCALL Jump

Before Instruction

operation operation

PC = Address (HERE)

After Instruction

PC = Address (Jump) TOS = Address (HERE + 2)

| RES   | ET             | Reset                                                                |                                                                  |        |                |  |

|-------|----------------|----------------------------------------------------------------------|------------------------------------------------------------------|--------|----------------|--|

| Synta | ax:            | [ <i>label</i> ] F                                                   | RESET                                                            |        |                |  |

| Oper  | ands:          | None                                                                 |                                                                  |        |                |  |

| Oper  | ation:         |                                                                      | Reset all registers and flags that are affected by a MCLR Reset. |        |                |  |

| Statu | s Affected:    | ffected: All                                                         |                                                                  |        |                |  |

| Enco  | ding:          | 0000 0000 1111 111                                                   |                                                                  |        | 1111           |  |

| Desc  | ription:       | This instruction provides a way to execute a MCLR Reset in software. |                                                                  |        |                |  |

| Word  | ls:            | 1                                                                    |                                                                  |        |                |  |

| Cycle | es:            | 1                                                                    |                                                                  |        |                |  |

| QC    | ycle Activity: |                                                                      |                                                                  |        |                |  |

|       | Q1             | Q2                                                                   | Q3                                                               |        | Q4             |  |

|       | Decode         | Start<br>Reset                                                       | No<br>operati                                                    | ion op | No<br>peration |  |

nstruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

| тѕт         | FSZ                                               | Test f, Sk                                                                   | Test f, Skip if 0                                                                                                                                                                                                                                                                                              |                 |  |  |  |  |

|-------------|---------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta       | ax:                                               | [label] T                                                                    | STFSZ f[,a]                                                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Oper        | ands:                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$              |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| Oper        | ation:                                            | skip if f = 0                                                                |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| Statu       | s Affected:                                       | None                                                                         |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| Enco        | ding:                                             | 0110                                                                         | 011a ff                                                                                                                                                                                                                                                                                                        | ff ffff         |  |  |  |  |

| Desc        | ription:                                          | during the c<br>is discarded<br>making this<br>is '0', the A<br>overriding t | If 'f' = 0, the next instruction, fetched<br>during the current instruction execution,<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction. If 'a'<br>is '0', the Access Bank will be selected,<br>overriding the BSR value. If 'a' is '1',<br>then the bank will be selected as per |                 |  |  |  |  |

| Word        | Is:                                               | 1                                                                            |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| Cycle       | es:                                               |                                                                              |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| QC          | ycle Activity:                                    |                                                                              |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

|             | Q1                                                | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                                             | Q4              |  |  |  |  |

|             | Decode                                            | Read<br>register 'f'                                                         | Process<br>Data                                                                                                                                                                                                                                                                                                | No<br>operation |  |  |  |  |

| lf sk       | ip:                                               | •                                                                            |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

|             | Q1                                                | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                                             | Q4              |  |  |  |  |

|             | No                                                | No                                                                           | No                                                                                                                                                                                                                                                                                                             | No              |  |  |  |  |

|             | operation                                         | operation                                                                    | operation                                                                                                                                                                                                                                                                                                      | operation       |  |  |  |  |

| lf sk       | ip and followe                                    |                                                                              |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

|             | Q1                                                | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                                             | Q4              |  |  |  |  |

|             | No                                                | No                                                                           | No                                                                                                                                                                                                                                                                                                             | No              |  |  |  |  |

|             | operation<br>No                                   | operation<br>No                                                              | operation<br>No                                                                                                                                                                                                                                                                                                | operation<br>No |  |  |  |  |

|             | operation                                         | operation                                                                    | operation                                                                                                                                                                                                                                                                                                      | operation       |  |  |  |  |

| <u>Exan</u> | nple:                                             | HERE T<br>NZERO<br>ZERO :                                                    | NZERO :                                                                                                                                                                                                                                                                                                        |                 |  |  |  |  |

|             | Before Instruc<br>PC = Ado                        | tion<br>dress (HERE)                                                         |                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |