Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT       |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 9x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4431-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

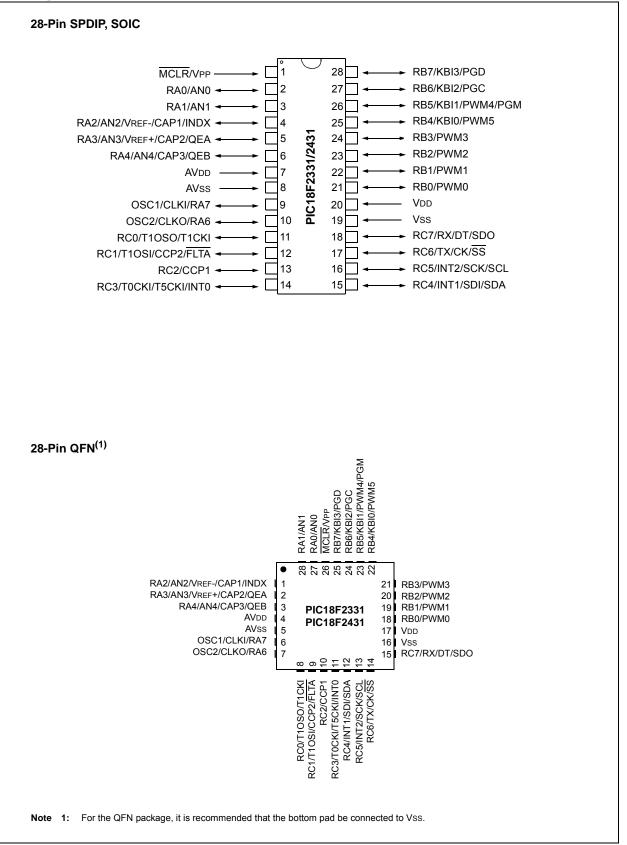

## **Pin Diagrams**

| Din Nomo                                                         | Pin Number |      |     | Pin                | Buffer                              | Description                                                                                                                                         |  |  |

|------------------------------------------------------------------|------------|------|-----|--------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                         | PDIP       | TQFP | QFN | Туре               | Туре                                | Description                                                                                                                                         |  |  |

|                                                                  |            |      |     |                    |                                     | PORTA is a bidirectional I/O port.                                                                                                                  |  |  |

| RA0/AN0<br>RA0<br>AN0                                            | 2          | 19   | 19  | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog Input 0.                                                                                                                     |  |  |

| RA1/AN1<br>RA1<br>AN1                                            | 3          | 20   | 20  | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog Input 1.                                                                                                                     |  |  |

| RA2/AN2/Vref-/CAP1/<br>INDX                                      | 4          | 21   | 21  |                    |                                     |                                                                                                                                                     |  |  |

| RA2<br>AN2<br>VREF-<br>CAP1<br>INDX                              |            |      |     | I/O<br>I<br>I<br>I | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.<br>Input Capture Pin 1.<br>Quadrature Encoder Interface index input pin.      |  |  |

| RA3/AN3/VREF+/<br>CAP2/QEA<br>RA3<br>AN3<br>VREF+<br>CAP2<br>QEA | 5          | 22   | 22  | I/O<br>I<br>I<br>I | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.<br>Input Capture Pin 2.<br>Quadrature Encoder Interface Channel A input pin. |  |  |

| RA4/AN4/CAP3/QEB<br>RA4<br>AN4<br>CAP3<br>QEB                    | 6          | 23   | 23  | I/O<br>I<br>I      | TTL<br>Analog<br>ST<br>ST           | Digital I/O.<br>Analog Input 4.<br>Input Capture Pin 3.<br>Quadrature Encoder Interface Channel B input pin.                                        |  |  |

| RA5/AN5/LVDIN<br>RA5<br>AN5<br>LVDIN                             | 7          | 24   | 24  | I/O<br>I<br>I      | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog Input 5.<br>Low-Voltage Detect input.                                                                                        |  |  |

#### **TABLE 1-3:** PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED)

'yy 0

= Output

= Power

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL; RC7 is the alternate pin for SDO.

Ρ

2: RD4 is the alternate pin for FLTA.

3: RD5 is the alternate pin for PWM4.

| Pin Name                                                                    | Pin Number Pin |                        |     | Pin                    | Buffer                             | Description                                                                                                                                                      |

|-----------------------------------------------------------------------------|----------------|------------------------|-----|------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                    | PDIP           | TQFP                   | QFN | Туре                   | Туре                               | Description                                                                                                                                                      |

|                                                                             |                |                        |     |                        |                                    | PORTC is a bidirectional I/O port.                                                                                                                               |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI                                    | 15             | 32                     | 34  | I/O<br>O<br>I          | ST<br>—<br>ST                      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.                                                                                        |

| RC1/T1OSI/CCP2/<br>FLTA                                                     | 16             | 35                     | 35  |                        | -                                  |                                                                                                                                                                  |

| RC1<br>T1OSI<br><u>CCP2</u><br>FLTA                                         |                |                        |     | I/O<br>I<br>I/O<br>I   | ST<br>CMOS<br>ST<br>ST             | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input, Compare 2 output, PWM2 output.<br>Fault interrupt input pin.                                        |

| RC2/CCP1/FLTB<br>RC2<br>CCP1<br>FLTB                                        | 17             | 36                     | 36  | I/O<br>I/O<br>I        | ST<br>ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Fault interrupt input pin.                                                                      |

| RC3/T0CKI/T5CKI/<br>INT0                                                    | 18             | 37                     | 37  |                        |                                    |                                                                                                                                                                  |

| RC3<br>T0CKI <sup>(1)</sup><br>T5CKI <sup>(1)</sup><br>INT0                 |                |                        |     | I/O<br>I<br>I          | ST<br>ST<br>ST<br>ST               | Digital I/O.<br>Timer0 alternate clock input.<br>Timer5 alternate clock input.<br>External Interrupt 0.                                                          |

| RC4/INT1/SDI/SDA<br>RC4<br>INT1<br>SDI <sup>(1)</sup><br>SDA <sup>(1)</sup> | 23             | 42                     | 42  | I/O<br>I<br>I<br>I/O   | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 1.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |

| RC5/INT2/SCK/SCL<br>RC5<br>INT2<br>SCK <sup>(1)</sup><br>SCL <sup>(1)</sup> | 24             | 43                     | 43  | I/O<br>I<br>I/O<br>I/O | ST<br>ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>External Interrupt 2.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC6/TX/CK/ <del>SS</del><br>RC6<br>TX<br><u>CK</u><br>SS                    | 25             | 44                     | 44  | I/O<br>O<br>I/O<br>I   | ST<br>—<br>ST<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>SPI slave select input.                                        |

| RC7/RX/DT/SDO<br>RC7<br>RX<br>DT<br>SDO <sup>(1)</sup>                      | 26             | 1                      | 1   | I/O<br>I<br>I/O<br>O   | ST<br>ST<br>ST                     | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>SPI data out.                                                    |

| Legend: TTL = TTL<br>ST = Schi<br>O = Outp                                  | mitt Tri       | atible inp<br>gger inp |     | CMOS                   | levels                             | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |

#### **TABLE 1-3:** PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED)

for SCK/SCL; RC7 is the alternate pin for SDO.

**2:** RD4 is the alternate pin for  $\overline{FLTA}$ .

3: RD5 is the alternate pin for PWM4.

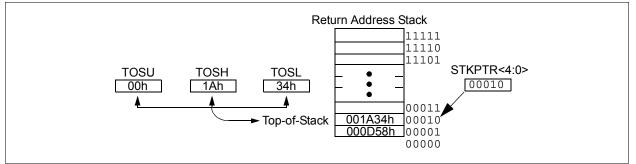

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset as the contents of the SFRs are not affected.

# FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| R/C-0                 | R/C-0                 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------------------|-----------------------|-----|-------|-------|-------|-------|-------|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —   | SP4   | SP3   | SP2   | SP1   | SP0   |

| bit 7                 |                       |     |       |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | <ol> <li>1 = Stack became full or overflowed</li> <li>0 = Stack has not become full or overflowed</li> </ol> |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                                              |

|         | 1 = Stack underflow occurred                                                                                 |

|         | 0 = Stack underflow did not occur                                                                            |

| bit 5   | Unimplemented: Read as '0'                                                                                   |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                                                         |

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

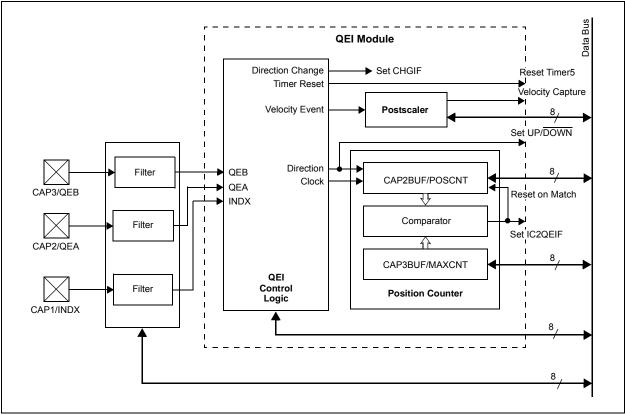

# 17.2 Quadrature Encoder Interface

The Quadrature Encoder Interface (QEI) decodes speed and motion sensor information. It can be used in any application that uses a quadrature encoder for feedback. The interface implements these features:

- Three QEI inputs: two phase signals (QEA and QEB) and one index signal (INDX)

- Direction of movement detection with a direction change interrupt (IC3DRIF)

- 16-bit up/down position counter

- Standard and High-Precision Position Tracking modes

- Two Position Update modes (x2 and x4)

- Velocity measurement with a programmable postscaler for high-speed velocity measurement

- Position counter interrupt (IC2QEIF in the PIR3 register)

- Velocity control interrupt (IC1IF in the PIR3 register)

The QEI submodule has three main components: the QEI control logic block, the position counter and velocity postscaler.

The QEI control logic detects the leading edge on the QEA or QEB phase input pins and generates the count pulse, which is sent to the position counter logic. It also samples the index input signal (INDX) and generates the direction of the rotation signal (up/down) and the velocity event signals.

The position counter acts as an integrator for tracking distance traveled. The QEA and QEB input edges serve as the stimulus to create the input clock which advances the Position Counter register (POSCNT). The register is incremented on either the QEA input edge, or the QEA and QEB input edges, depending on the operating mode. It is reset either by a rollover on match to the Period register, MAXCNT, or on the external index pulse input signal (INDX). An interrupt is generated on a Reset of POSCNT if the position counter interrupt is enabled.

The velocity postscaler down samples the velocity pulses used to increment the velocity counter by a specified ratio. It essentially divides down the number of velocity pulses to one output per so many inputs, preserving the pulse width in the process.

A simplified block-diagram of the QEI module is shown in Figure 17-8.

### FIGURE 17-8: QEI BLOCK DIAGRAM

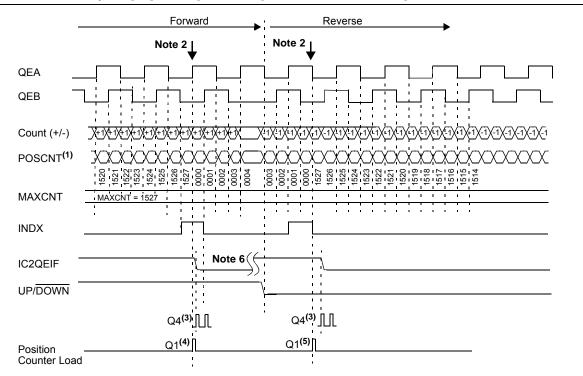

#### FIGURE 17-11: QEI MODULE RESET TIMING WITH THE INDEX INPUT

- Note 1: POSCNT register is shown in QEI x4 Update mode (POSCNT increments on every rising and every falling edge of QEA and QEB input signals).

- 2: When an INDX Reset pulse is detected, POSCNT is reset to '0' on the next QEA or QEB edge. POSCNT is set to MAXCNT when POSCNT = 0 (when decrementing), which occurs on the next QEA or QEB edge. a similar Reset sequence occurs for the reverse direction, except that the INDX signal is recognized on its falling edge. The Reset is generated on the next QEA or QEB edge.

- 3: IC2QEIF is enabled for one TCY clock cycle.

- 4: The position counter is loaded with 0000h (i.e., Reset) on the next QEA or QEB edge when the INDX is high.

- 5: The position counter is loaded with a MAXCNT value (e.g., 1527h) on the next QEA or QEB edge following the INDX falling edge input signal detect).

- 6: IC2QEIF must be cleared in software.

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-4       PTOPS<3:0>: PWM Time Base Output Postscale Select bits       0000 = 1:1 Postscale         0000 = 1:1 Postscale       0001 = 1:2 Postscale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                                                                                                                                                                                                                               |                                   |               |                   |                  |                 |        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|-------------------|------------------|-----------------|--------|--|

| bit 7 bit<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 7-4 PTOPS<3:0>: PWM Time Base Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>0001 = 1:2 Postscale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0      | R/W-0                                                                                                                                                                                                                                                         | R/W-0                             | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 7-4 PTOPS<3:0>: PWM Time Base Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>0001 = 1:2 Postscale<br>iiiii = 1:16 Postscale<br>bit 3-2 PTCKPS<1:0>: PWM Time Base Input Clock Prescale Select bits<br>00 = PWM time base input clock is Fosc/4 (1:1 prescale)<br>01 = PWM time base input clock is Fosc/46 (1:4 prescale)<br>10 = PWM time base input clock is Fosc/256 (1:64 prescale)<br>11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWI<br>updates<br>10 = PWM time base operates in a Continuous Up/Down Count mode<br>01 = PWM time base configured for Single-Shot mode                                                        | PTOPS3     | PTOPS2                                                                                                                                                                                                                                                        | PTOPS1                            | PTOPS0        | PTCKPS1           | PTCKPS0          | PTMOD1          | PTMOD0 |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-4       PTOPS<3:0>: PWM Time Base Output Postscale Select bits       0000 = 1:1 Postscale         0000 = 1:1 Postscale       0001 = 1:2 Postscale       0001 = 1:2 Postscale         1111 = 1:16 Postscale                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 7      |                                                                                                                                                                                                                                                               |                                   |               |                   |                  |                 | bit 0  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-4       PTOPS<3:0>: PWM Time Base Output Postscale Select bits       0000 = 1:1 Postscale         0001 = 1:2 Postscale       001 = 1:2 Postscale       1111 = 1:16 Postscale         bit 3-2       PTCKPS<1:0>: PWM Time Base Input Clock Prescale Select bits       00 = PWM time base input clock is Fosc/4 (1:1 prescale)         01 = PWM time base input clock is Fosc/16 (1:4 prescale)       10 = PWM time base input clock is Fosc/256 (1:64 prescale)         11 = PWM time base input clock is Fosc/256 (1:64 prescale)       11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWI updates         10 = PWM time base operates in a Continuous Up/Down Count mode       01 = PWM time base configured for Single-Shot mode | Legend:    |                                                                                                                                                                                                                                                               |                                   |               |                   |                  |                 |        |  |

| bit 7-4 PTOPS<3:0>: PWM Time Base Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R = Reada  | able bit                                                                                                                                                                                                                                                      | W = Writable b                    | bit           | U = Unimplem      | nented bit, read | as '0'          |        |  |

| <ul> <li>0000 = 1:1 Postscale</li> <li>1111 = 1:16 Postscale</li> <li>bit 3-2 PTCKPS&lt;1:0&gt;: PWM Time Base Input Clock Prescale Select bits</li> <li>00 = PWM time base input clock is Fosc/4 (1:1 prescale)</li> <li>01 = PWM time base input clock is Fosc/16 (1:4 prescale)</li> <li>10 = PWM time base input clock is Fosc/256 (1:64 prescale)</li> <li>11 = PWM time base input clock is Fosc/256 (1:64 prescale)</li> <li>bit 1-0 PTMOD&lt;1:0&gt;: PWM Time Base Mode Select bits</li> <li>11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWI updates</li> <li>10 = PWM time base operates in a Continuous Up/Down Count mode</li> <li>01 = PWM time base configured for Single-Shot mode</li> </ul>                                                                                                                               | -n = Value | at POR                                                                                                                                                                                                                                                        | '1' = Bit is set                  |               | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |

| <ul> <li>00 = PWM time base input clock is Fosc/4 (1:1 prescale)</li> <li>01 = PWM time base input clock is Fosc/16 (1:4 prescale)</li> <li>10 = PWM time base input clock is Fosc/64 (1:16 prescale)</li> <li>11 = PWM time base input clock is Fosc/256 (1:64 prescale)</li> <li>bit 1-0</li> <li>PTMOD&lt;1:0&gt;: PWM Time Base Mode Select bits</li> <li>11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWI updates</li> <li>10 = PWM time base operates in a Continuous Up/Down Count mode</li> <li>01 = PWM time base configured for Single-Shot mode</li> </ul>                                                                                                                                                                                                                                                                       |            | 0000 = 1:1 P<br>0001 = 1:2 P                                                                                                                                                                                                                                  | ostscale<br>ostscale<br>Postscale |               |                   |                  |                 |        |  |

| <ul> <li>11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWI updates</li> <li>10 = PWM time base operates in a Continuous Up/Down Count mode</li> <li>01 = PWM time base configured for Single-Shot mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 3-2    | <ul> <li>00 = PWM time base input clock is Fosc/4 (1:1 prescale)</li> <li>01 = PWM time base input clock is Fosc/16 (1:4 prescale)</li> <li>10 = PWM time base input clock is Fosc/64 (1:16 prescale)</li> </ul>                                              |                                   |               |                   |                  |                 |        |  |

| updates<br>10 = PWM time base operates in a Continuous Up/Down Count mode<br>01 = PWM time base configured for Single-Shot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 1-0    | PTMOD<1:0>                                                                                                                                                                                                                                                    | -: PWM Time Ba                    | ase Mode Sele | ect bits          |                  |                 |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | <ul> <li>11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWM updates</li> <li>10 = PWM time base operates in a Continuous Up/Down Count mode</li> <li>01 = PWM time base configured for Single-Shot mode</li> </ul> |                                   |               |                   |                  |                 |        |  |

# REGISTER 18-1: PTCON0: PWM TIMER CONTROL REGISTER 0

#### REGISTER 18-2: PTCON1: PWM TIMER CONTROL REGISTER 1

| R/W-0       | R-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|-------|-----|-----|-----|-----|-----|-----|

| PTEN        | PTDIR | —   | —   | _   | —   | —   | —   |

| bit 7 bit 0 |       |     |     |     |     |     |     |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7 PTEN: PWM Time Base Timer Enable bit

1 = PWM time base is on

0 = PWM time base is off

bit 6 PTDIR: PWM Time Base Count Direction Status bit

- 1 = PWM time base counts down

- 0 = PWM time base counts up

# bit 5-0 Unimplemented: Read as '0'

|  | REGISTER 18-3: | PWMCON0: PWM CONTROL REGISTER 0 |

|--|----------------|---------------------------------|

|--|----------------|---------------------------------|

| U-0   | R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|----------------------|----------------------|----------------------|-------|-------|-------|

| _     | PWMEN2               | PWMEN1               | PWMEN0               | PMOD3 <sup>(3)</sup> | PMOD2 | PMOD1 | PMOD0 |

| bit 7 |                      |                      |                      |                      |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 6-4 | PWMEN<2:0>: PWM Module Enable bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|         | <ul> <li>111 = All odd PWM I/O pins are enabled for PWM output<sup>(2)</sup></li> <li>110 = PWM1, PWM3 pins are enabled for PWM output</li> <li>101 = All PWM I/O pins are enabled for PWM output<sup>(2)</sup></li> <li>100 = PWM0, PWM1, PWM2, PWM3, PWM4 and PWM5 pins are enabled for PWM output</li> <li>011 = PWM0, PWM1, PWM2 and PWM3 I/O pins are enabled for PWM output</li> <li>010 = PWM0 and PWM1 pins are enabled for PWM output</li> <li>010 = PWM1 pin is enabled for PWM output</li> <li>000 = PWM module is disabled; all PWM I/O pins are general purpose I/O</li> </ul> |  |  |  |  |  |  |

| bit 3-0 | PMOD<3:0>: PWM Output Pair Mode bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|         | For PMOD0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|         | 1 = PWM I/O pin pair (PWM0, PWM1) is in the Independent mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         | 0 = PWM I/O pin pair (PWM0, PWM1) is in the Complementary mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         | For PMOD1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|         | 1 = PWM I/O pin pair (PWM2, PWM3) is in the Independent mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         | 0 = PWM I/O pin pair (PWM2, PWM3) is in the Complementary mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         | For PMOD2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|         | <ul> <li>1 = PWM I/O pin pair (PWM4, PWM5) is in the Independent mode</li> <li>0 = PWM I/O pin pair (PWM4, PWM5) is in the Complementary mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|         | For PMOD3: <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|         | 1 = PWM I/O pin pair (PWM6, PWM7) is in the Independent mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         | 0 = PWM I/O pin pair (PWM6, PWM7) is in the Complementary mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Note 1: | Reset condition of the PWMEN bits depends on the PWMPIN Configuration bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 2:      | When PWMEN<2:0> = 101, PWM<5:0> outputs are enabled for PIC18F2331/2431 devices; PWM<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|         | subsuts are enabled for DIC10E1221/1121 devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

outputs are enabled for PIC18F4331/4431 devices. When PWMEN<2:0> = 111, PWM Outputs 1, 3 and 5 are enabled in PIC18F2331/2431 devices; PWM Outputs 1, 3, 5 and 7 are enabled in PIC18F4331/4431 devices.

3: Unimplemented in PIC18F2331/2431 devices; maintain these bits clear.

# 19.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 19.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

Refer to application note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

# 19.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- · Serial Data Out (SDO)

- · Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON (SSPCON<5:0>) and SSPSTAT<7:6> registers. These control bits allow the following to be specified:

- · Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock rate (Master mode only)

- Slave Select mode (Slave mode only)

## 19.3.1.2 Reception

When the R/ $\overline{W}$  bit of the address byte is clear and an address match occurs, the R/ $\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 19-6: I<sup>2</sup>C<sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address $R\overline{W} = 0$ Receiving Data $A\overline{CK}$ Receiving Data<br>SDA $\overline{1} \sqrt{A7} \times A6 \times A5 \times A4 \times A3 \times A2 \times A1 \times PT \times D7 \times D6 \times D5 \times D4 \times D3 \times D2 \times D1 \times D0 \times PT \times D6 \times D5 \times D4 \times D3 \times D2 \times D1 \times D1 \times D1 \times D1 \times D1 \times D1 \times D1$ |                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                                                                                                                                                                                                                                                  | Bus master<br>terminates<br>transfer |

| SSPOV (SSPCON<6>)<br>SSPOV bit is set because the SSPBUF register is still ful<br>ACK is not ser                                                                                                                                                                                                                                                                                                             |                                      |

## 19.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<5:4> or TRISD<3:2> bits. The output level is always low, regardless of the value(s) in PORTC<5:4> or PORTD<3:2>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<4> or TRISD<2> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt will occur if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode Idle (SSPM<3:0> = 1011) or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

# 19.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<5:4> or TRISD<3:2>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| Name                 | Bit 7                                        | Bit 6                      | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Reset Values<br>on Page: |

|----------------------|----------------------------------------------|----------------------------|---------|--------|-------|--------|---------------|--------|--------------------------|

| INTCON               | GIE/GIEH                                     | PEIE/GIEL                  | TMR0IE  | INT0IE | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 54                       |

| PIR1                 | _                                            | ADIF                       | RCIF    | TXIF   | SSPIF | CCP1IF | TMR2IF        | TMR1IF | 57                       |

| PIE1                 | _                                            | ADIE                       | RCIE    | TXIE   | SSPIE | CCP1IE | TMR2IE        | TMR1IE | 57                       |

| SSPBUF               | SSP Receiv                                   |                            | 55      |        |       |        |               |        |                          |

| SSPADD               | SSP Addres                                   | s Register (I <sup>2</sup> | C mode) |        |       |        |               |        | 55                       |

| SSPCON               | WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0 |                            |         |        |       | 55     |               |        |                          |

| SSPSTAT              | SMP <sup>(1)</sup>                           | CKE <sup>(1)</sup>         | D/Ā     | Р      | S     | R/W    | UA            | BF     | 55                       |

| TRISC <sup>(2)</sup> | PORTC Data Direction Register                |                            |         |        |       |        |               |        | 57                       |

| TRISD <sup>(2)</sup> | PORTD Dat                                    | a Direction Re             | egister |        |       |        |               | 0      | 57                       |

TABLE 19-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the SSP module in  $I^2C$  mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

2: Depending upon the setting of SSPMX in CONFIG3H, these pins are multiplexed to PORTC or PORTD.

# 22.0 LOW-VOLTAGE DETECT (LVD)

PIC18F2331/2431/4331/4431 devices have a Low-Voltage Detect module (LVD), a programmable circuit that enables the user to specify a device voltage trip point. If the device experiences an excursion below the trip point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The Low-Voltage Detect Control register (Register 22-1) completely controls the operation of the LVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the LVD module is shown in Figure 22-1.

The module is enabled by setting the LVDEN bit, but the circuitry requires some time to stabilize each time that it is enabled. The IRVST bit is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and the IRVST bit is set. The module monitors for drops in VDD below a predetermined set point.

# REGISTER 22-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0           | U-0                                                                   | R-0                                                                                                       | R/W-0            | R/W-0                                | R/W-1                | R/W-0                | R/W-1                |  |  |  |  |

|---------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|----------------------|----------------------|----------------------|--|--|--|--|

| _             | —                                                                     | IRVST                                                                                                     | LVDEN            | LVDL3 <sup>(1)</sup>                 | LVDL2 <sup>(1)</sup> | LVDL1 <sup>(1)</sup> | LVDL0 <sup>(1)</sup> |  |  |  |  |

| bit 7         | ÷                                                                     | ÷                                                                                                         |                  | ÷                                    | ÷                    | ÷                    | bit 0                |  |  |  |  |

|               |                                                                       |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

| Legend:       |                                                                       |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

| R = Readable  | e bit                                                                 | W = Writable                                                                                              | bit              | U = Unimplem                         | nented bit, read     | l as '0'             |                      |  |  |  |  |

| -n = Value at | POR                                                                   | '1' = Bit is set                                                                                          |                  | '0' = Bit is clea                    | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

|               |                                                                       |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

| bit 7-6       | •                                                                     | ted: Read as '                                                                                            |                  |                                      |                      |                      |                      |  |  |  |  |

| bit 5         |                                                                       | al Reference V                                                                                            | 0                | 0                                    |                      |                      |                      |  |  |  |  |

|               | 1 = Indicates                                                         | 1 = Indicates that the Low-Voltage Detect logic will generate the interrupt flag at the specified voltage |                  |                                      |                      |                      |                      |  |  |  |  |

|               | range                                                                 |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               |                                                                       |                                                                                                           | •                | t logic will not<br>nould not be ena | •                    | nterrupt flag at     | the specified        |  |  |  |  |

| bit 4         | LVDEN: Low-                                                           | Voltage Detect                                                                                            | Power Enable     | e bit                                |                      |                      |                      |  |  |  |  |

|               | 1 = Enables LVD, powers up LVD circuit                                |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | 0 = Disables LVD, powers down LVD circuit                             |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

| bit 3-0       | LVDL<3:0>: L                                                          | _ow-Voltage De                                                                                            | etection Limit b | oits <sup>(1)</sup>                  |                      |                      |                      |  |  |  |  |

|               | 1111 = External analog input is used (input comes from the LVDIN pin) |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | 1110 = Maximum setting                                                |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | •                                                                     |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | •                                                                     |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | •                                                                     |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | 0010 = Minim                                                          | 0                                                                                                         |                  |                                      |                      |                      |                      |  |  |  |  |

|               | 0001 = Reserved                                                       |                                                                                                           |                  |                                      |                      |                      |                      |  |  |  |  |

|               | 0000 <b>= Rese</b> r                                                  | ved                                                                                                       |                  |                                      |                      |                      |                      |  |  |  |  |

**Note 1:** LVDL<3:0> bit modes, which result in a trip point below the valid operating voltage of the device, are not tested.

# 22.4 LVD Start-up Time

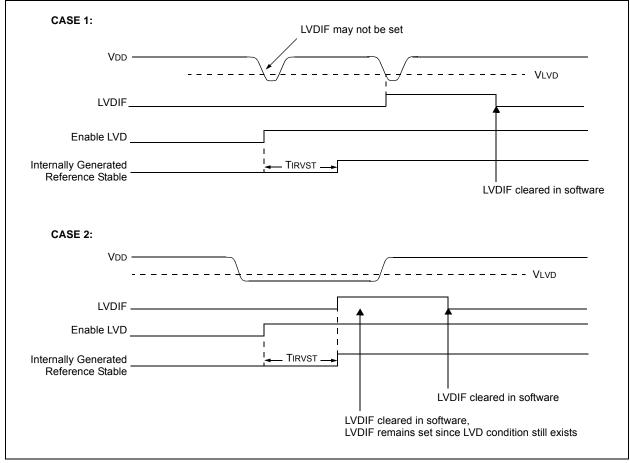

The internal reference voltage of the LVD module, specified in electrical specification Parameter D420, may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the LVD, or other circuits using the voltage reference, are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification Parameter 36.

The LVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (refer to Figure 22-2).

# REGISTER 23-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0          | U-0                                                                                     | U-0                                 | U-0             | R/P-1        | R/P-1            | R/P-1                | R/P-1                 |  |  |

|--------------|-----------------------------------------------------------------------------------------|-------------------------------------|-----------------|--------------|------------------|----------------------|-----------------------|--|--|

| _            | _                                                                                       | —                                   | _               | BORV1        | BORV0            | BOREN <sup>(1)</sup> | PWRTEN <sup>(1)</sup> |  |  |

| bit 7        |                                                                                         |                                     |                 |              |                  |                      | bit (                 |  |  |

|              |                                                                                         |                                     |                 |              |                  |                      |                       |  |  |

| Legend:      |                                                                                         |                                     |                 |              |                  |                      |                       |  |  |

| R = Readab   | ole bit                                                                                 | P = Programm                        | able bit        | U = Unimplem | nented bit, read | l as '0'             |                       |  |  |

| -n = Value v | vhen device is un                                                                       | programmed                          |                 | U = Unchange | ed from prograi  | mmed state           |                       |  |  |

|              |                                                                                         |                                     |                 |              |                  |                      |                       |  |  |

| bit 7-4      | Unimplement                                                                             | ted: Read as '0                     | ,               |              |                  |                      |                       |  |  |

| bit 3-2      | BORV<1:0>:                                                                              | Brown-out Res                       | et Voltage bits |              |                  |                      |                       |  |  |

|              | 11 = Reserved                                                                           |                                     |                 |              |                  |                      |                       |  |  |

|              | 10 = VBOR se                                                                            |                                     |                 |              |                  |                      |                       |  |  |

|              | 01 = VBOR se<br>00 = VBOR se                                                            |                                     |                 |              |                  |                      |                       |  |  |

| L:1 4        |                                                                                         | vn-out Reset Ei                     |                 |              |                  |                      |                       |  |  |

| bit 1        |                                                                                         |                                     |                 |              |                  |                      |                       |  |  |

|              |                                                                                         | t Reset is enab<br>t Reset is disab |                 |              |                  |                      |                       |  |  |

| hit O        | 0 = Brown-out Reset is disabled <b>PWRTEN:</b> Power-up Timer Enable bit <sup>(1)</sup> |                                     |                 |              |                  |                      |                       |  |  |

| bit 0        | 1 = PWRT is (                                                                           | -                                   |                 |              |                  |                      |                       |  |  |

|              | $\perp = PVRIIS($                                                                       | uisabieu                            |                 |              |                  |                      |                       |  |  |

**Note 1:** Having BOREN = 1 does not automatically override the PWRTEN to '0', nor automatically enables the Power-up Timer.

## REGISTER 23-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| U-0   | U | R/P-1   | R/P-1               | R/P-1               | R/P-1                 | U | U     |

|-------|---|---------|---------------------|---------------------|-----------------------|---|-------|

| _     | — | T1OSCMX | HPOL <sup>(1)</sup> | LPOL <sup>(1)</sup> | PWMPIN <sup>(3)</sup> | _ | —     |

| bit 7 |   |         |                     |                     |                       |   | bit 0 |

| Legend:                                                                                                          |                                     |                                                                      |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| R = Reada                                                                                                        | ble bit P = Programmable b          | it U = Unimplemented bit, read as '0'                                |  |  |  |  |  |  |

| -n = Value                                                                                                       | when device is unprogrammed         | U = Unchanged from programmed state                                  |  |  |  |  |  |  |

|                                                                                                                  |                                     |                                                                      |  |  |  |  |  |  |

| bit 7-6                                                                                                          | Unimplemented: Read as '0'          |                                                                      |  |  |  |  |  |  |

| bit 5                                                                                                            | T1OSCMX: Timer1 Oscillator Mode     |                                                                      |  |  |  |  |  |  |

|                                                                                                                  | 1 = Low-power Timer1 operation w    | 1 = Low-power Timer1 operation when microcontroller is in Sleep mode |  |  |  |  |  |  |

|                                                                                                                  | 0 = Standard (legacy) Timer1 oscill | ator operation                                                       |  |  |  |  |  |  |

| bit 4 <b>HPOL:</b> High Side Transistors Polarity bit (i.e., Odd PWM Output Polarity Control bit) <sup>(1)</sup> |                                     |                                                                      |  |  |  |  |  |  |

|                                                                                                                  | 1 = PWM1, 3, 5 and 7 are active-hi  | gh (default) <sup>(2)</sup>                                          |  |  |  |  |  |  |

|                                                                                                                  | 0 = PWM1, 3, 5 and 7 are active-lo  | <sub>w</sub> (2)                                                     |  |  |  |  |  |  |

| bit 3                                                                                                            | LPOL: Low Side Transistors Polarit  | y bit (i.e., Even PWM Output Polarity Control bit) <sup>(1)</sup>    |  |  |  |  |  |  |

|                                                                                                                  | 1 = PWM0, 2, 4 and 6 are active-hi  |                                                                      |  |  |  |  |  |  |

|                                                                                                                  | 0 = PWM0, 2, 4 and 6 are active-lo  | <sub>w</sub> (2)                                                     |  |  |  |  |  |  |

| bit 2                                                                                                            | PWMPIN: PWM Output Pins Reset       | State Control bit <sup>(3)</sup>                                     |  |  |  |  |  |  |

|                                                                                                                  | 1 = PWM outputs are disabled upo    | n Reset (default)                                                    |  |  |  |  |  |  |

|                                                                                                                  | 0 = PWM outputs drive active state  |                                                                      |  |  |  |  |  |  |

| bit 1-0                                                                                                          | Unimplemented: Read as '0'          |                                                                      |  |  |  |  |  |  |

| Note 1:                                                                                                          | -                                   | lefine PWM signal output active and inactive states; PWM states      |  |  |  |  |  |  |

- ote 1: Polarity control bits, HPOL and LPOL, define PWM signal output active and inactive states; PV generated by the Fault inputs or PWM manual override.