Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (8K × 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 9x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4431-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-490-2

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

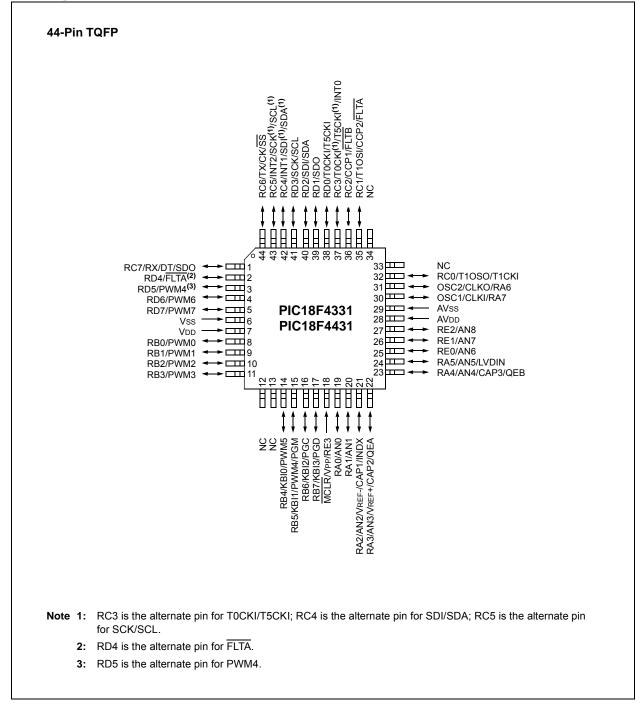

### **Pin Diagrams (Continued)**

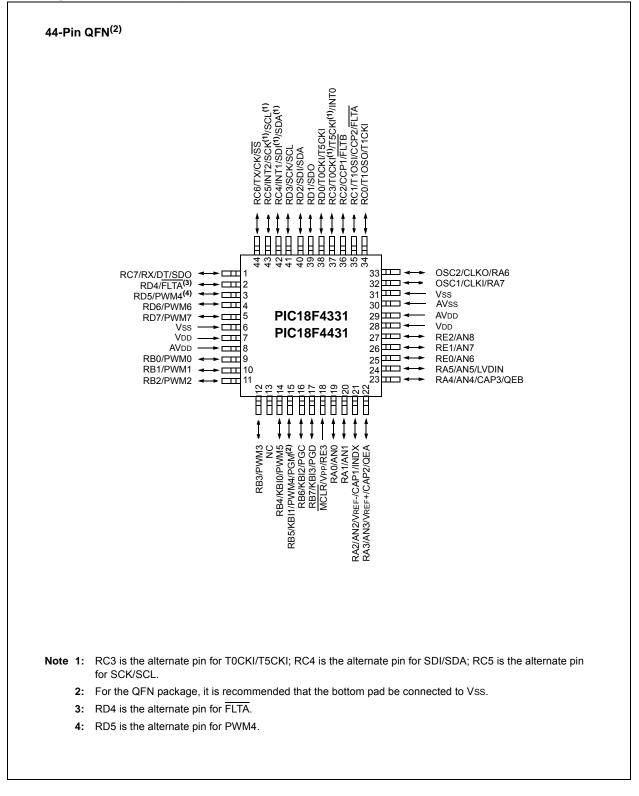

### **Pin Diagrams (Continued)**

# 4.0 POWER-MANAGED MODES

PIC18F2331/2431/4331/4431 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- · Sleep mode

These categories define which portions of the device are clocked, and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<3:0> Configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in Section 4.1.3 "Clock Transitions and Status Indicators" and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mada     | OSCCON               | l Bits<7,1:0> | Module  | Clocking    | Available Cleak and Casillaton Source                                                                                                  |

|----------|----------------------|---------------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Mode     | IDLEN <sup>(1)</sup> | SCS<1:0>      | CPU     | Peripherals | Available Clock and Oscillator Source                                                                                                  |

| Sleep    | 0                    | N/A           | Off     | Off         | None – All clocks are disabled                                                                                                         |

| PRI_RUN  | N/A                  | 00            | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC and<br>Internal Oscillator Block. <sup>(2)</sup><br>This is the normal, full-power execution mode. |

| SEC_RUN  | N/A                  | 01            | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                                          |

| RC_RUN   | N/A                  | 1x            | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                               |

| PRI_IDLE | 1                    | 00            | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                                                    |

| SEC_IDLE | 1                    | 01            | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                                          |

| RC_IDLE  | 1                    | 1x            | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                               |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the **SLEEP** instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

# 5.0 RESET

The PIC18F2331/2431/4331/4431 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR, and the operation of the various startup timers. Stack Reset events are covered in Section 6.1.2.4 "Stack Full/Underflow Resets". WDT Resets are covered in Section 23.2 "Watchdog Timer (WDT)".

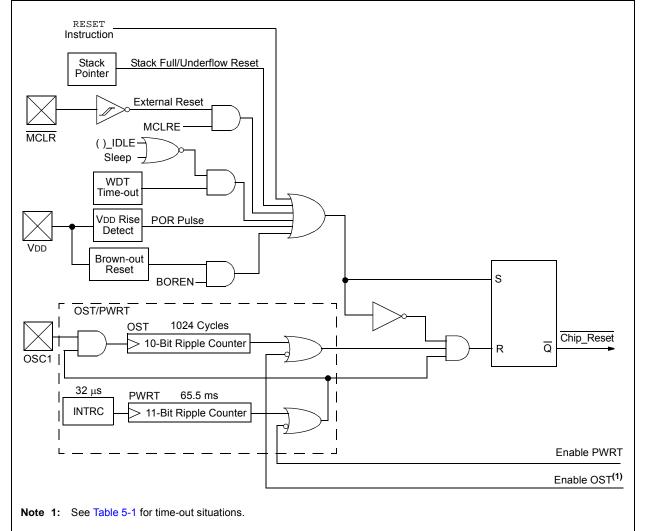

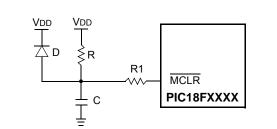

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 5.2 Master Clear (MCLR)

The MCLR pin can trigger an external Reset of the device by holding the pin low. These devices have a noise filter in the MCLR Reset path that detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the Watchdog Timer.

In PIC18F2331/2431/4331/4431 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. For more information, see Section 11.5 "PORTE, TRISE and LATE Registers".

### 5.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. The minimum rise rate for VDD is specified (Parameter D004). For a slow rise time, see Figure 5-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (such as voltage, frequency and temperature) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

Power-on Reset events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs and does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

| Note: |            | following<br>mmended: | decoupling                  | method    | is |

|-------|------------|-----------------------|-----------------------------|-----------|----|

|       |            | • •                   | citor should b<br>and AVss. | e connect | ed |

|       | <b>~</b> ^ | oimilor               | aanaaitar                   | abould    | ha |

A similar capacitor should be connected across VDD and Vss. FIGURE 5-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode, D, helps discharge the capacitor quickly when VDD powers down.

- **2:**  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 \ge 1 \ k\Omega$  will limit any current flowing into MCLR from external capacitor, C, in the event of MCLR/VPP pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 5.4 Brown-out Reset (BOR)

A Configuration bit, BOREN, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (Parameter D005A through D005F) for greater than TBOR (Parameter 35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay TPWRT (Parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling the Brown-out Reset does not automatically enable the PWRT.

| TABLE 5-3: | INI                        | TIALIZ | ZATIO                              | N CO                                                          | ONDITIONS FOR ALL REGISTERS (CONTINUED) |           |           |  |  |  |  |  |

|------------|----------------------------|--------|------------------------------------|---------------------------------------------------------------|-----------------------------------------|-----------|-----------|--|--|--|--|--|

| Register   | egister Applicable Devices |        | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt         |           |           |  |  |  |  |  |

| ADRESH     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| ADRESL     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| ADCON0     | 2331                       | 2431   | 4331                               | 4431                                                          | 00 0000                                 | 00 0000   | uu uuuu   |  |  |  |  |  |

| ADCON1     | 2331                       | 2431   | 4331                               | 4431                                                          | 00-0 0000                               | 00-0 0000 | uu-u uuuu |  |  |  |  |  |

| ADCON2     | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| ADCON3     | 2331                       | 2431   | 4331                               | 4431                                                          | 00-0 0000                               | 00-0 0000 | uu-u uuuu |  |  |  |  |  |

| ADCHS      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| CCPR1H     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| CCPR1L     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| CCP1CON    | 2331                       | 2431   | 4331                               | 4431                                                          | 00 0000                                 | 00 0000   | uu uuuu   |  |  |  |  |  |

| CCPR2H     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| CCPR2L     | 2331                       | 2431   | 4331                               | 4431                                                          | xxxx xxxx                               | uuuu uuuu | uuuu uuuu |  |  |  |  |  |

| CCP2CON    | 2331                       | 2431   | 4331                               | 4431                                                          | 00 0000                                 | 00 0000   | uu uuuu   |  |  |  |  |  |

| ANSEL1     | 2331                       | 2431   | 4331                               | 4431                                                          | 1                                       | 1         | u         |  |  |  |  |  |

| ANSEL0     | 2331                       | 2431   | 4331                               | 4431                                                          | 1111 1111                               | 1111 1111 | uuuu uuuu |  |  |  |  |  |

| T5CON      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| QEICON     | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| SPBRGH     | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| SPBRG      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| RCREG      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| TXREG      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| TXSTA      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 -010                               | 0000 -010 | uuuu -uuu |  |  |  |  |  |

| RCSTA      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 000x                               | 0000 000x | uuuu uuuu |  |  |  |  |  |

| BAUDCON    | 2331                       | 2431   | 4331                               | 4431                                                          | -1-1 0-00                               | -1-1 0-00 | -u-u u-uu |  |  |  |  |  |

| EEADR      | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| EEDATA     | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | uuuu uuuu |  |  |  |  |  |

| EECON2     | 2331                       | 2431   | 4331                               | 4431                                                          | 0000 0000                               | 0000 0000 | 0000 0000 |  |  |  |  |  |

| EECON1     | 2331                       | 2431   | 4331                               | 4431                                                          | xx-0 x000                               | uu-0 u000 | uu-0 u000 |  |  |  |  |  |

| IPR3       | 2331                       | 2431   | 4331                               | 4431                                                          | 1 1111                                  | 1 1111    | u uuuu    |  |  |  |  |  |

| PIE3       | 2331                       | 2431   | 4331                               | 4431                                                          | 0 0000                                  | 0 0000    | u uuuu    |  |  |  |  |  |

| PIR3       | 2331                       | 2431   | 4331                               | 4431                                                          | 0 0000                                  | 0 0000    | u uuuu    |  |  |  |  |  |

### TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-2 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** Bit 3 of PORTE and LATE are enabled if MCLR functionality is disabled. When not enabled as the PORTE pin, they are disabled and read as '0'. The 28-pin devices do not have only RE3 implemented.

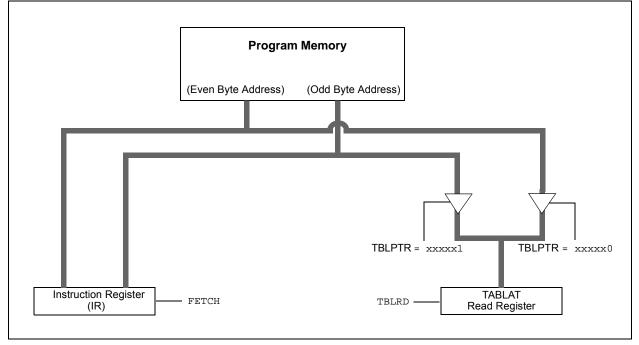

### 8.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 8-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 8-4: READS FROM FLASH PROGRAM MEMORY

### EXAMPLE 8-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |   |                                                  |

| READ_WORD |                                           |                                                                          |   |                                                  |

|           | TBLRD*-                                   | +                                                                        | ; | read into TABLAT and increment TBLPTR            |

|           | MOVF                                      | TABLAT,W                                                                 | ; | get data                                         |

|           | MOVWF                                     | WORD_EVEN                                                                |   |                                                  |

|           | TBLRD*-                                   | +                                                                        | ; | read into TABLAT and increment TBLPTR            |

|           | MOVF                                      | TABLAT,W                                                                 | ; | get data                                         |

|           | MOVWF                                     | WORD_ODD                                                                 |   |                                                  |

### REGISTER 10-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0          | U-0                                                     | U-0                                                                                | R/W-0          | R/W-0             | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------|------------------------------------------------------------------------------------|----------------|-------------------|------------------|----------------|--------|--|--|--|--|--|--|

| _            | _                                                       | —                                                                                  | PTIE           | IC3DRIE           | IC2QEIE          | IC1IE          | TMR5IE |  |  |  |  |  |  |

| pit 7        |                                                         |                                                                                    |                | -                 |                  |                | bit 0  |  |  |  |  |  |  |

|              |                                                         |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

| _egend:      |                                                         |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

| R = Readable | e bit                                                   | W = Writable                                                                       | bit            | U = Unimplen      | nented bit, read | as '0'         |        |  |  |  |  |  |  |

| n = Value at | POR                                                     | '1' = Bit is set                                                                   |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |  |  |  |  |  |  |

|              |                                                         |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

| oit 7-5      | Unimpleme                                               | ented: Read as '                                                                   | )'             |                   |                  |                |        |  |  |  |  |  |  |

| oit 4        | PTIE: PWM                                               | 1 Time Base Inter                                                                  | rupt Enable bi | t                 |                  |                |        |  |  |  |  |  |  |

|              | 1 = PTIF e                                              |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              | 0 = PTIF d                                              |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

| bit 3        |                                                         | C3 Interrupt Enab                                                                  |                | hange Interrupt   | Enable bit       |                |        |  |  |  |  |  |  |

|              | IC3 Enabled (CAP3CON<3:0>):                             |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              | 1 = IC3 interrupt enabled<br>0 = IC3 interrupt disabled |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | <u>QEI Enabled (QEIM&lt;2:0&gt;):</u><br>1 = Change of direction interrupt enabled |                |                   |                  |                |        |  |  |  |  |  |  |

|              | 0                                                       | e of direction inte                                                                | •              |                   |                  |                |        |  |  |  |  |  |  |

| oit 2        | IC2QEIE: I                                              | C2 Interrupt Flag/                                                                 | QEI Interrupt  | Flag Enable bit   |                  |                |        |  |  |  |  |  |  |

|              | IC2 Enable                                              | IC2 Enabled (CAP2CON<3:0>):                                                        |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | errupt enabled)                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | 0 = IC2 interrupt disabled                                                         |                |                   |                  |                |        |  |  |  |  |  |  |

|              | QEI Enabled (QEIM<2:0>):                                |                                                                                    |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | 1 = QEI interrupt enabled<br>0 = QEI interrupt disabled                            |                |                   |                  |                |        |  |  |  |  |  |  |

| .:+ 1        |                                                         | •                                                                                  | <b>_:</b> +    |                   |                  |                |        |  |  |  |  |  |  |

| oit 1        |                                                         | Interrupt Enable t                                                                 | DIL            |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | errupt enabled<br>errupt disabled                                                  |                |                   |                  |                |        |  |  |  |  |  |  |

| oit O        |                                                         | imer5 Interrupt Er                                                                 | nable bit      |                   |                  |                |        |  |  |  |  |  |  |

|              | 1 = Timer5                                              | •                                                                                  |                |                   |                  |                |        |  |  |  |  |  |  |

|              |                                                         | Interrunt enabled                                                                  | 1              |                   |                  |                |        |  |  |  |  |  |  |

### 17.1.5 ENTERING INPUT CAPTURE MODE AND CAPTURE TIMING

The following is a summary of functional operation upon entering any of the Input Capture modes:

- After the module is configured for one of the Capture modes by setting the Capture Mode Select bits (CAPxM<3:0>), the first detected edge captures the Timer5 value and stores it in the CAPxBUF register. The timer is then reset (depending on the setting of CAPxREN bit) and starts to increment according to its settings (see Figure 17-4, Figure 17-5 and Figure 17-6).

- 2. On all edges, the capture logic performs the following:

- a) Input Capture mode is decoded and the active edge is identified.

- b) The CAPxREN bit is checked to determine whether Timer5 is reset or not.

- c) On every active edge, the Timer5 value is recorded in the Input Capture Buffer (CAPxBUF).

- Reset Timer5 after capturing the value of the timer when the CAPxREN bit is enabled. Timer5 is reset on every active capture edge in this case.

- e) On all continuing capture edge events, repeat steps (a) through (d) until the operational mode is terminated, either by user firmware, POR or BOR.

- f) The timer value is not affected when switching into and out of various Input Capture modes.

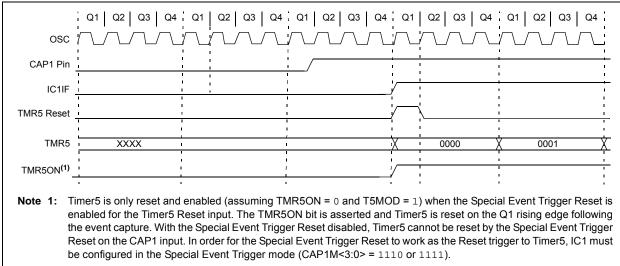

### 17.1.6 TIMER5 RESET

Every input capture trigger can optionally reset (TMR5). The Capture Reset Enable bit, CAPxREN, gates the automatic Reset of the time base of the capture event with this enable Reset signal. All capture events reset the selected timer when CAPxREN is set. Resets are disabled when CAPxREN is cleared (see Figure 17-4, Figure 17-5 and Figure 17-6).

| Note: | The   | CAPxREN     | bit  | has  | no  | effect | in |

|-------|-------|-------------|------|------|-----|--------|----|

|       | Pulse | e-Width Mea | sure | ment | mod | le.    |    |

### 17.1.7 IC INTERRUPTS

There are four operating modes for which the IC module can generate an interrupt and set one of the Interrupt Capture Flag bits (IC1IF, IC2QEIF or IC3DRIF). The interrupt flag that is set depends on the channel in which the event occurs. The modes are:

- Edge Capture (CAPxM<3:0> = 0001, 0010, 0011 or 0100)

- Period Measurement Event (CAPxM<3:0> = 0101)

- Pulse-Width Measurement Event (CAPxM<3:0> = 0110 or 0111)

- State Change Event (CAPxM<3:0> = 1000)

Note: The Special Event Trigger is generated only in the Special Event Trigger mode on the CAP1 input (CAP1M<3:0> = 1110 and 1111). IC1IF interrupt is not set in this mode.

The timing of interrupt and Special Event Trigger events is shown in Figure 17-7. Any active edge is detected on the rising edge of Q2 and propagated on the rising edge of Q4 rising edge. If an active edge happens to occur any later than this (on the falling edge of Q2, for example), then it will be recognized on the next Q2 rising edge.

### FIGURE 17-7: CAPx INTERRUPTS AND IC1 SPECIAL EVENT TRIGGER

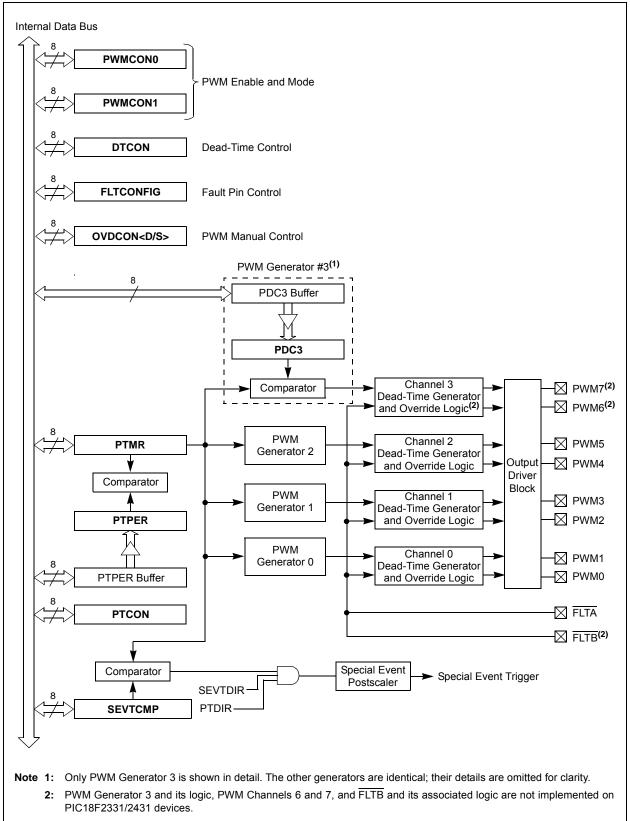

### FIGURE 18-1: POWER CONTROL PWM MODULE BLOCK DIAGRAM

### 19.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF, is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave (Figure 19-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-Bit Addressing mode is as follows, with Steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (SSPIF, BF and UA bits are set).

- Update the SSPADD register with second (low) byte of address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (SSPIF, BF and UA bits are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (SSPIF and BF bits are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

### TABLE 19-2: DATA TRANSFER RECEIVED BYTE ACTIONS

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set SSPIF Bit<br>(SSP interrupt occurs |  |  |

|---------------------------------------------|-------|--------------------|-----------------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                    | Fuise                 | if enabled)                            |  |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                    |  |  |

| 1                                           | 0     | No                 | No                    | Yes                                    |  |  |

| 1                                           | 1     | No                 | No                    | Yes                                    |  |  |

| 0                                           | 1     | No                 | No                    | Yes                                    |  |  |

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

|              |                       |            |                             | SYNC = 0          | , BRGH = | = 1, BRG16                  | = 1 or SY             | NC = 1,    | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-------------------|----------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz |          |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | value Rate % val  |          | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 33332                       | 0.300             | 0.00     | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00       | 8332                        | 1.200             | 0.02     | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02       | 4165                        | 2.400             | 0.02     | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06       | 1040                        | 9.596             | -0.03    | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03      | 520                         | 19.231            | 0.16     | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35       | 172                         | 57.471            | -0.22    | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22      | 86                          | 116.279           | 0.94     | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|             |                       | SYN        | NC = 0, BRO                 | GH = 1, BI            | <b>RG16 =</b> 1 | or SYNC =                   | : 1, BRG1             | 6 = 1      |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000       | MHz                         | Fosc = 1.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04           | 1665                        | 0.300                 | -0.04      | 832                         |

| 1.2         | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16           | 415                         | 1.201                 | -0.16      | 207                         |

| 2.4         | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16           | 207                         | 2.403                 | -0.16      | 103                         |

| 9.6         | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16           | 51                          | 9.615                 | -0.16      | 25                          |

| 19.2        | 19.231                | 0.16       | 51                          | 19.230                | -0.16           | 25                          | 19.230                | -0.16      | 12                          |

| 57.6        | 58.824                | 2.12       | 16                          | 55.555                | 3.55            | 8                           | —                     | _          | _                           |

| 115.2       | 111.111               | -3.55      | 8                           | _                     | _               | _                           | _                     | _          |                             |

| U-0          | U-0                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                 | R/W-0                                                                 | R/W-0                                                                                  | R/W-0                                                                                    | R/W-0                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| _            | _                                                                                                                                       | ACONV                                                                                                                                                                                                                                                                                                          | ACSCH                                                                                                                                                 | ACMOD1                                                                | ACMOD0                                                                                 | GO/DONE                                                                                  | ADON                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 7        |                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                       | •                                                                                      |                                                                                          | bit                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| Legend:      |                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| R = Readat   | ole bit                                                                                                                                 | W = Writable                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                   | U = Unimplen                                                          | nented bit, rea                                                                        | d as '0'                                                                                 |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| -n = Value a | n = Value at POR                                                                                                                        |                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                      |                                                                       | ared                                                                                   | x = Bit is unkno                                                                         | own                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| bit 7-6      | Unimpleme                                                                                                                               | ented: Read as '                                                                                                                                                                                                                                                                                               | 0'                                                                                                                                                    |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 5        | ACONV: Au                                                                                                                               | to-Conversion C                                                                                                                                                                                                                                                                                                | Continuous Loc                                                                                                                                        | p or Single-Sho                                                       | ot Mode Select                                                                         | bit                                                                                      |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                         | ious Loop mode<br>Shot mode enab                                                                                                                                                                                                                                                                               |                                                                                                                                                       |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 4        | ACSCH: Au                                                                                                                               | to-Conversion S                                                                                                                                                                                                                                                                                                | ingle or Multi-                                                                                                                                       | Channel Mode b                                                        | oit                                                                                    |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                         | hannel mode en<br>Channel mode e                                                                                                                                                                                                                                                                               |                                                                                                                                                       |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 3-2      | ACMOD<1:                                                                                                                                | 0>: Auto-Conve                                                                                                                                                                                                                                                                                                 | rsion Mode Se                                                                                                                                         | quence Select I                                                       | oits                                                                                   |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|              | 1st sai<br>2nd sa<br>01 = Seque<br>1st sai<br>2nd sa<br>3rd sa<br>4th sai<br>10 = Simult<br>1st sai<br>11 = Simult<br>1st sai<br>2nd sa | ntial Mode 1 (SE<br>mple: Group A <sup>(1)</sup><br>imple: Group B <sup>(1)</sup><br>imple: Group A <sup>(1)</sup><br>imple: Group A <sup>(1)</sup><br>imple: Group C <sup>(1)</sup><br>aneous Mode 1<br>mple: Group A a<br>aneous Mode 2<br>mple: Group A a<br>imple: Group C a<br><u>0</u> , Auto-Conversion | )<br>EQM2); four sa<br>)<br>)<br>(STNM1); two<br>nd Group B <sup>(1)</sup><br>(STNM2); two<br>nd Group B <sup>(1)</sup><br>and Group D <sup>(1)</sup> | amples are taken<br>samples are tal<br>samples are tal                | n in sequence:<br>ken simultanec<br>ken simultanec                                     | ously:<br>ously:                                                                         |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|              | 00 = Single<br>01 = Single<br>10 = Single                                                                                               | Channel Mode<br>Channel Mode<br>Channel Mode<br>Channel Mode                                                                                                                                                                                                                                                   | 1 (SCM1); Gro<br>2 (SCM2); Gro<br>3 (SCM3); Gro                                                                                                       | up A is taken a<br>up B is taken a<br>up C is taken a                 | nd converted <sup>(1</sup><br>nd converted <sup>(1</sup><br>nd converted <sup>(1</sup> | )<br>)<br>)                                                                              |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 1        | GO/DONE:                                                                                                                                | A/D Conversion                                                                                                                                                                                                                                                                                                 | Status bit                                                                                                                                            |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|              | Conver<br>hardwa<br>comple<br>set afte<br>to stop                                                                                       | sion Single-Sho<br>re when the A/D<br>ted. If Auto-Con<br>r the user/trigger<br>the conversions                                                                                                                                                                                                                | t mode is en<br>conversion (s<br>version Contin<br>has set it (con                                                                                    | abled (ACONV<br>single or multi-c<br>uous Loop moo<br>tinuous convers | = 0), this bit<br>hannel depend<br>le is enabled (<br>ions). It may be                 | D conversion cy<br>is automaticall<br>ling on ACMOD<br>ACONV = 1), th<br>e cleared manua | y cleared<br>settings) h<br>is bit remai                                                                           |  |  |  |  |  |  |  |  |  |  |

| bit 0        | ADON: A/D                                                                                                                               | On bit                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |                                                                       |                                                                                        |                                                                                          | <ul> <li>0 = A/D conversion or multiple conversions completed/not in progress</li> <li>ADON: A/D On bit</li> </ul> |  |  |  |  |  |  |  |  |  |  |

|              | 1 = A/D Co                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                       |                                                                                        |                                                                                          |                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

### REGISTER 21-1: ADCON0: A/D CONTROL REGISTER 0

Note 1: Groups A, B, C, and D refer to the ADCHS register.

### REGISTER 21-2: ADCON1: A/D CONTROL REGISTER 1

| R/W-0 | R/W-0 | U-0 | R/W-0  | R-0   | R-0   | R-0    | R-0    |

|-------|-------|-----|--------|-------|-------|--------|--------|

| VCFG1 | VCFG0 | _   | FIFOEN | BFEMT | BFOVL | ADPNT1 | ADPNT0 |

| bit 7 |       |     |        |       |       |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | VCFG<1:0>: A/D VREF+ and A/D VREF- Source Selection bits<br>00 = VREF+ = AVDD, VREF- = AVSS (AN2 and AN3 are analog inputs or digital I/O)<br>01 = VREF+ = External VREF+, VREF- = AVSS (AN2 is an analog input or digital I/O)<br>10 = VREF+ = AVDD, VREF- = External VREF- (AN3 is an analog input or digital I/O)<br>11 = VREF+ = External VREF-, VREF- = External VREF- |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                  |

| bit 4   | FIFOEN: FIFO Buffer Enable bit                                                                                                                                                                                                                                                                                                                                              |

|         | <ul><li>1 = FIFO is enabled</li><li>0 = FIFO is disabled</li></ul>                                                                                                                                                                                                                                                                                                          |

| bit 3   | BFEMT: Buffer Empty bit                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = FIFO is empty</li> <li>0 = FIFO is not empty (at least one of four locations has unread A/D result data)</li> </ul>                                                                                                                                                                                                                                            |

| bit 2   | BFOVFL: Buffer Overflow bit                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = A/D result has overwritten a buffer location that has unread data</li> <li>0 = A/D result has not overflowed</li> </ul>                                                                                                                                                                                                                                        |

| bit 1-0 | ADPNT<1:0>: Buffer Read Pointer Location bits                                                                                                                                                                                                                                                                                                                               |

|         | Designates the location to be read next.<br>00 = Buffer Address 0<br>01 = Buffer Address 1<br>10 = Buffer Address 2<br>11 = Buffer Address 3                                                                                                                                                                                                                                |

### 21.1.3 CONVERSION SEQUENCING

The ACMOD<1:0> bits control the sequencing of the A/D conversions. When ACSCH = 0, the A/D is configured to sample and convert a single channel. The ACMOD bits select which group to perform the conversions and the GxSEL<1:0> bits select which channel in the group is to be converted. If Single-Shot mode is enabled, the A/D interrupt flag will be set after the channel is converted. If Continuous Loop mode is enabled, the A/D interrupt flag will be set according to the ADRS<1:0> bits.

When ACSCH = 1, multiple channel sequencing is enabled and two submodes can be selected. The first mode is Sequential mode with two settings. The first setting is called SEQM1, and first samples and converts the selected Group A channel, and then samples and converts the selected Group B channel. The second mode is called SEQM2, and it samples and converts a Group A channel, Group B channel, Group C channel and finally, a Group D channel.

The second multiple channel sequencing submode is Simultaneous Sampling mode. In this mode, there are also two settings. The first setting is called STNM1, and uses the two sample and hold circuits on the A/D module. The selected Group A and B channels are simultaneously sampled and then the Group A channel is converted followed by the conversion of the Group B channel. The second setting is called STNM2, and starts the same as STNM1, but follows it with a simultaneous sample of Group C and D channels. The A/D module will then convert the Group C channel followed by the Group D channel.

### 21.1.4 TRIGGERING A/D CONVERSIONS

The PIC18F2331/2431/4331/4431 devices are capable of triggering conversions from many different sources. The same method used by all other microcontrollers of setting the GO/DONE bit still works. The other trigger sources are:

- RC3/INT0 Pin

- Timer5 Overflow

- Input Capture 1 (IC1)

- CCP2 Compare Match

- · Power Control PWM Rising Edge

These triggers are enabled using the SSRC<4:0> bits (ADCON3<4:0>). Any combination of the five sources can trigger a conversion by simply setting the corresponding bit in ADCON3. When the trigger occurs, the GO/DONE bit is automatically set by the hardware and then cleared once the conversion completes.

### 21.1.5 A/D MODULE INITIALIZATION STEPS

The following steps should be followed to initialize the A/D module:

- 1. Configure the A/D module:

- a) Configure the analog pins, voltage reference and digital I/O.

- b) Select the A/D input channels.

- c) Select the A/D Auto-Conversion mode (Single-Shot or Continuous Loop).

- d) Select the A/D conversion clock.

- e) Select the A/D conversion trigger.

- 2. Configure the A/D interrupt (if required):

- a) Set the GIE bit.

- b) Set the PEIE bit.

- c) Set the ADIE bit.

- d) Clear the ADIF bit.

- e) Select the A/D trigger setting.

- f) Select the A/D interrupt priority.

- 3. Turn on ADC:

- a) Set the ADON bit in the ADCON0 register.

- b) Wait the required power-up setup time, about 5-10  $\ensuremath{\mu s}.$

- 4. Start the sample/conversion sequence:

- a) Sample for a minimum of 2 TAD and start the conversion by setting the GO/DONE bit. The GO/DONE bit is set by the user in software or by the module if initiated by a trigger.

- b) If TACQ is assigned a value (multiple of TAD), then setting the GO/DONE bit starts a sample period of the TACQ value, then starts a conversion.

- 5. Wait for A/D conversion/conversions to complete using one of the following options:

- a) Poll for the GO/DONE bit to be cleared if in Single-Shot mode.

- b) Wait for the A/D Interrupt Flag (ADIF) to be set.

- c) Poll for the BFEMT bit to be cleared to signify that at least the first conversion has completed.

- 6. Read the A/D results, clear the ADIF flag, reconfigure the trigger.

| ADD   | OWFC                                      | AD                                                                                                                                                                                                                                                            | ADD W and Carry bit to f  |                      |      |                                    |                   |

|-------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|------|------------------------------------|-------------------|

| Synta | ax:                                       | [ lat                                                                                                                                                                                                                                                         | bel] ADI                  | DWFC                 | f[,d | [,a]]                              |                   |

| Oper  | ands:                                     | d ∈                                                                                                                                                                                                                                                           | f ≤ 255<br>[0,1]<br>[0,1] |                      |      |                                    |                   |