Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

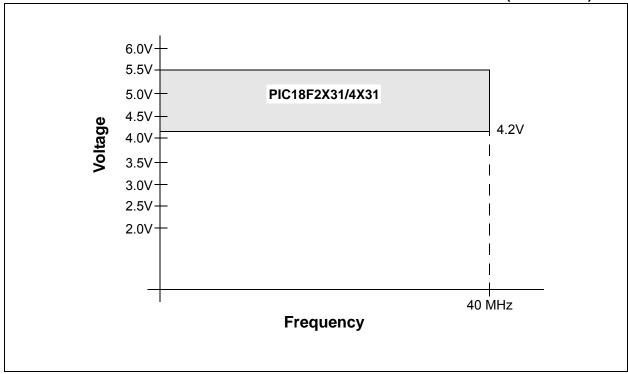

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

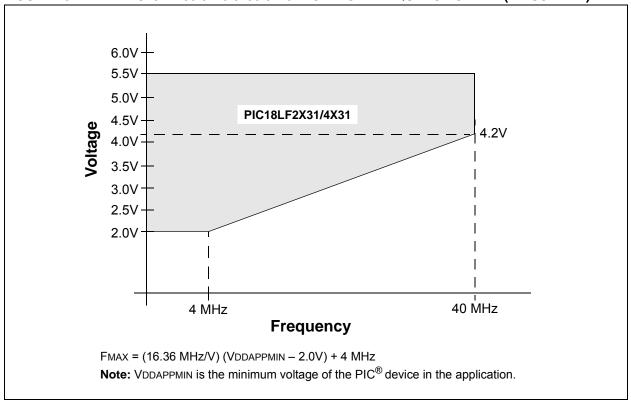

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 9x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4431t-i-pt |

#### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is no greater

than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1 μF in parallel with 0.001 μF).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.2.3 CONSIDERATIONS WHEN USING BOR

When the Brown-out Reset (BOR) feature is enabled, a sudden change in VDD may result in a spontaneous BOR event. This can happen when the microcontroller is operating under normal operating conditions, regardless of what the BOR set point has been programmed to, and even if VDD does not approach the set point. The precipitating factor in these BOR events is a rise or fall in VDD with a slew rate faster than  $0.15V/\mu s$ .

An application that incorporates adequate decoupling between the power supplies will not experience such rapid voltage changes. Additionally, the use of an electrolytic tank capacitor across VDD and Vss, as described above, will be helpful in preventing high slew rate transitions.

If the application has components that turn on or off, and share the same VDD circuit as the microcontroller, the BOR can be disabled in software by using the SBOREN bit before switching the component. Afterwards, allow a small delay before re-enabling the BOR. By doing this, it is ensured that the BOR is disabled during the interval that might cause high slew rate changes of VDD.

Note:

Not all devices incorporate software BOR control. See **Section 5.0** "**Reset**" for device-specific information.

#### 5.2 Master Clear (MCLR)

The MCLR pin can trigger an external Reset of the device by holding the pin low. These devices have a noise filter in the MCLR Reset path that detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the Watchdog Timer.

In PIC18F2331/2431/4331/4431 devices, the  $\overline{\text{MCLR}}$  input can be disabled with the MCLRE Configuration bit. When  $\overline{\text{MCLR}}$  is disabled, the pin becomes a digital input. For more information, see **Section 11.5** "PORTE, TRISE and LATE Registers".

#### 5.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{MCLR}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. The minimum rise rate for VDD is specified (Parameter D004). For a slow rise time, see Figure 5-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (such as voltage, frequency and temperature) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

Power-on Reset events are captured by the  $\overline{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs and does not change for any other Reset event.  $\overline{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

**Note:** The following decoupling method is recommended:

- 1. A 1  $\mu F$  capacitor should be connected across AVDD and AVss.

- 2. A similar capacitor should be connected across VDD and VSS.

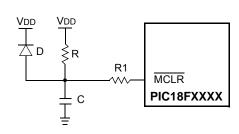

#### FIGURE 5-2:

EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode, D, helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3: R1  $\geq$  1 k $\Omega$  will limit any current flowing into MCLR from external capacitor, C, in the event of MCLR/VPP pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 5.4 Brown-out Reset (BOR)

A Configuration bit, BOREN, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (Parameter D005A through D005F) for greater than TBOR (Parameter 35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay TPWRT (Parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling the Brown-out Reset does not automatically enable the PWRT.

TABLE 6-2: REGISTER FILE SUMMARY (PIC18F2331/2431/4331/4431) (CONTINUED)

| File Name | Bit 7               | Bit 6                        | Bit 5               | Bit 4       | Bit 3          | Bit 2                        | Bit 1     | Bit 0               | Value on POR, BOR |

|-----------|---------------------|------------------------------|---------------------|-------------|----------------|------------------------------|-----------|---------------------|-------------------|

| OSCCON    | IDLEN               | IRCF2                        | IRCF1               | IRCF0       | OSTS           | IOFS                         | SCS1      | SCS0                | 0000 q000         |

| LVDCON    | _                   | _                            | IRVST               | LVDEN       | LVDL3          | LVDL2                        | LVDL1     | LVDL0               | 00 0101           |

| WDTCON    | WDTW                | _                            | _                   | _           | _              | _                            | _         | SWDTEN              | 00                |

| RCON      | IPEN                | _                            | _                   | RI          | TO             | PD                           | POR       | BOR                 | 01 11q0           |

| TMR1H     | Timer1 Regist       | er High Byte                 |                     |             | •              | •                            | •         |                     | xxxx xxxx         |

| TMR1L     | Timer1 Regist       | er Low Byte                  |                     |             |                |                              |           |                     | xxxx xxxx         |

| T1CON     | RD16                | T1RUN                        | T1CKPS1             | T1CKPS0     | T10SCEN        | T1SYNC                       | TMR1CS    | TMR10N              | 0000 0000         |

| TMR2      | Timer2 Regist       | er                           |                     |             | •              | •                            | •         | •                   | 0000 0000         |

| PR2       | Timer2 Period       | Register                     |                     |             |                |                              |           |                     | 1111 1111         |

| T2CON     | _                   | TOUTPS3                      | TOUTPS2             | TOUTPS1     | TOUTPS0        | TMR2ON                       | T2CKPS1   | T2CKPS0             | -000 0000         |

| SSPBUF    | SSP Receive         | Buffer/Transmit              | Register            |             |                |                              |           |                     | xxxx xxxx         |

| SSPADD    | SSP Address         | Register in I <sup>2</sup> C | ™ Slave mode.       | SSP Baud Ra | te Reload Regi | ster in I <sup>2</sup> C Mas | ter mode. |                     | 0000 0000         |

| SSPSTAT   | SMP                 | CKE                          | D/A                 | Р           | S              | R/W                          | UA        | BF                  | 0000 0000         |

| SSPCON    | WCOL                | SSPOV                        | SSPEN               | CKP         | SSPM3          | SSPM2                        | SSPM1     | SSPM0               | 0000 0000         |

| ADRESH    | A/D Result Re       | gister High Byt              | e                   |             | •              | •                            | •         |                     | xxxx xxxx         |

| ADRESL    | A/D Result Re       | gister Low Byte              | 9                   |             |                |                              |           |                     | xxxx xxxx         |

| ADCON0    | _                   | _                            | ACONV               | ACSCH       | ACMOD1         | ACMOD0                       | GO/DONE   | ADON                | 00 0000           |

| ADCON1    | VCFG1               | VCFG0                        | _                   | FIFOEN      | BFEMT          | BFOVFL                       | ADPNT1    | ADPNT0              | 00-0 0000         |

| ADCON2    | ADFM                | ACQT3                        | ACQT2               | ACQT1       | ACQT0          | ADCS2                        | ADCS1     | ADCS0               | 0000 0000         |

| ADCON3    | ADRS1               | ADRS0                        | _                   | SSRC4       | SSRC3          | SSRC2                        | SSRC1     | SSRC0               | 00-0 0000         |

| ADCHS     | GDSEL1              | GDSEL0                       | GBSEL1              | GBSEL0      | GCSEL1         | GCSEL0                       | GASEL1    | GASEL0              | 0000 0000         |

| CCPR1H    | Capture/Comp        | are/PWM Reg                  | ister 1 High Byt    | е           |                |                              |           |                     | xxxx xxxx         |

| CCPR1L    | Capture/Comp        | oare/PWM Reg                 | ister 1 Low Byte    | Э           |                |                              |           |                     | xxxx xxxx         |

| CCP1CON   | _                   | _                            | DC1B1               | DC1B0       | CCP1M3         | CCP1M2                       | CCP1M1    | CCP1M0              | 00 0000           |

| CCPR2H    | Capture/Comp        | oare/PWM Reg                 | ister 2 High Byt    | е           |                |                              |           |                     | xxxx xxxx         |

| CCPR2L    | Capture/Comp        | oare/PWM Reg                 | ister 2 Low Byte    | Э           |                |                              |           |                     | xxxx xxxx         |

| CCP2CON   | _                   | _                            | DC2B1               | DC2B0       | CCP2M3         | CCP2M2                       | CCP2M1    | CCP2M0              | 00 0000           |

| ANSEL1    | _                   | _                            | ı                   | ı           | _              | _                            | _         | ANS8 <sup>(4)</sup> | 1                 |

| ANSEL0    | ANS7 <sup>(4)</sup> | ANS6 <sup>(4)</sup>          | ANS5 <sup>(4)</sup> | ANS4        | ANS3           | ANS2                         | ANS1      | ANS0                | 1111 1111         |

| T5CON     | T5SEN               | RESEN <sup>(4)</sup>         | T5MOD               | T5PS1       | T5PS0          | T5SYNC                       | TMR5CS    | TMR5ON              | 0000 0000         |

| QEICON    | VELM                | QERR                         | UP/DOWN             | QEIM2       | QEIM1          | QEIM0                        | PDEC1     | PDEC0               | 0000 0000         |

| SPBRGH    | EUSART Bau          | d Rate General               | or Register Hig     | h Byte      | •              | •                            | •         | •                   | 0000 0000         |

| SPBRG     | EUSART Bau          | d Rate General               | or Register Lov     | v Byte      |                |                              |           |                     | 0000 0000         |

| RCREG     | EUSART Rec          | eive Register                |                     |             |                |                              |           |                     | 0000 0000         |

| TXREG     | EUSART Tran         | smit Register                |                     |             |                |                              |           |                     | 0000 0000         |

| TXSTA     | CSRC                | TX9                          | TXEN                | SYNC        | SENDB          | BRGH                         | TRMT      | TX9D                | 0000 0010         |

| RCSTA     | SPEN                | RX9                          | SREN                | CREN        | ADDEN          | FERR                         | OERR      | RX9D                | 0000 000x         |

| BAUDCON   |                     | RCIDL                        |                     | SCKP        | BRG16          |                              | WUE       | ABDEN               | -1-1 0-00         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented.

- 2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read '0' in all other modes.

- 3: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

- 4: These registers and/or bits are not implemented on the PIC18F2331/2431 devices and read as '0'.

- 5: The RE3 port bit is only available for PIC18F4331/4431 devices when the MCLRE fuse (CONFIG3H<7>) is programmed to '0'; otherwise, RE3 reads '0'. This bit is read-only.

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator modes only and read '0' in all other oscillator modes.

#### 6.7 Data Addressing Modes

The data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- · Direct

- Indirect

# 6.7.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all. They either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.7.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.5.4 "Special Function Registers") or a location in the Access Bank (Section 6.5.2 "Access Bank") as the data source for the instruction.

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.5.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their op codes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.7.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 6-5.

# EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | E     |            | ; | YES, continue  |

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 6.7.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contain FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

#### REGISTER 10-8: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0  | U-0 | U-0 | R/W-0 | U-0 | R/W-0 | U-0 | R/W-0  |

|--------|-----|-----|-------|-----|-------|-----|--------|

| OSCFIE | _   | _   | EEIE  | _   | LVDIE | _   | CCP2IE |

| bit 7  |     |     |       |     |       |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIE: Oscillator Fail Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6-5 **Unimplemented:** Read as '0'

bit 4 **EEIE:** Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 3 Unimplemented: Read as '0'

bit 2 LVDIE: Low-Voltage Detect Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 1 **Unimplemented:** Read as '0'

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enabled

0 = Disabled

# 11.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

#### **EXAMPLE 11-2: INITIALIZING PORTB**

| CLRF  | PORTB | ; Initialize PORTB by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATB  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISB | ; Set RB<3:0> as inputs |

|       |       | ; RB<5:4> as outputs    |

|       |       | ; RB<7:6> as inputs     |

|       |       |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB port change interrupt with flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the  ${\tt MOVFF}$  (ANY), PORTB instruction).

- b) NOP (or any 1 Tcy delay).

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB and waiting 1 Tcy will end the mismatch condition and allow flag bit, RBIF, to be cleared. Also, if the port pin returns to its original state, the mismatch condition will be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB<3:0> and RB4 pins are multiplexed with the 14-bit PWM module for PWM<3:0> and PWM5 output. The RB5 pin can be configured by the Configuration bit, PWM4MX, as the alternate pin for PWM4 output.

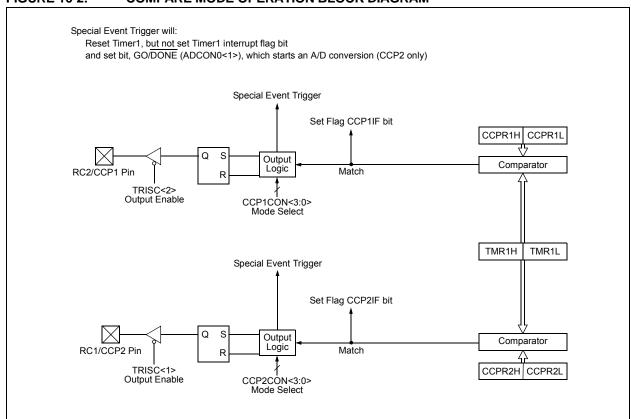

#### 16.4 Compare Mode

In Compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 (RC1/CCP2) pin:

- · is driven high

- · is driven low

- toggles output (high-to-low or low-to-high)

- remains unchanged (interrupt only)

The action on the pin is based on the value of control bits, CCP1M<3:0> (CCP2M<3:0>). At the same time, interrupt flag bit CCP1IF (CCP2IF) is set.

#### 16.4.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISC bit.

Note:

Clearing the CCPxCON register will force the RC1 or RC2 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 16.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.4.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 16.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP2 resets the TMR1 register pair. Additionally, the CCP2 Special Event Trigger will start an A/D conversion if the A/D module is enabled.

Note:

The Special Event Trigger from the CCP2 module will not set the Timer1 interrupt flag bit.

#### FIGURE 16-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# 17.1.5 ENTERING INPUT CAPTURE MODE AND CAPTURE TIMING

The following is a summary of functional operation upon entering any of the Input Capture modes:

- 1. After the module is configured for one of the Capture modes by setting the Capture Mode Select bits (CAPxM<3:0>), the first detected edge captures the Timer5 value and stores it in the CAPxBUF register. The timer is then reset (depending on the setting of CAPxREN bit) and starts to increment according to its settings (see Figure 17-4, Figure 17-5 and Figure 17-6).

- 2. On all edges, the capture logic performs the following:

- Input Capture mode is decoded and the active edge is identified.

- The CAPxREN bit is checked to determine whether Timer5 is reset or not.

- On every active edge, the Timer5 value is recorded in the Input Capture Buffer (CAPxBUF).

- d) Reset Timer5 after capturing the value of the timer when the CAPxREN bit is enabled. Timer5 is reset on every active capture edge in this case.

- e) On all continuing capture edge events, repeat steps (a) through (d) until the operational mode is terminated, either by user firmware, POR or BOR.

- The timer value is not affected when switching into and out of various Input Capture modes.

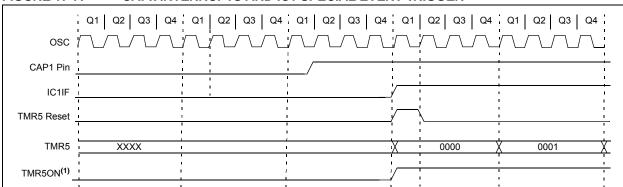

#### 17.1.6 TIMER5 RESET

Every input capture trigger can optionally reset (TMR5). The Capture Reset Enable bit, CAPxREN, gates the automatic Reset of the time base of the capture event with this enable Reset signal. All capture events reset the selected timer when CAPxREN is set. Resets are disabled when CAPxREN is cleared (see Figure 17-4, Figure 17-5 and Figure 17-6).

**Note:** The CAPxREN bit has no effect in Pulse-Width Measurement mode.

#### 17.1.7 IC INTERRUPTS

There are four operating modes for which the IC module can generate an interrupt and set one of the Interrupt Capture Flag bits (IC1IF, IC2QEIF or IC3DRIF). The interrupt flag that is set depends on the channel in which the event occurs. The modes are:

- Edge Capture (CAPxM<3:0> = 0001, 0010, 0011 or 0100)

- Period Measurement Event (CAPxM<3:0> = 0101)

- Pulse-Width Measurement Event (CAPxM<3:0> = 0110 or 0111)

- State Change Event (CAPxM<3:0> = 1000)

Note: The Special Event Trigger is generated only in the Special Event Trigger mode on the CAP1 input (CAP1M<3:0> = 1110 and 1111). IC1IF interrupt is not set in this mode.

The timing of interrupt and Special Event Trigger events is shown in Figure 17-7. Any active edge is detected on the rising edge of Q2 and propagated on the rising edge of Q4 rising edge. If an active edge happens to occur any later than this (on the falling edge of Q2, for example), then it will be recognized on the next Q2 rising edge.

#### FIGURE 17-7: CAPX INTERRUPTS AND IC1 SPECIAL EVENT TRIGGER

Note 1: Timer5 is only reset and enabled (assuming TMR5ON = 0 and T5MOD = 1) when the Special Event Trigger Reset is enabled for the Timer5 Reset input. The TMR5ON bit is asserted and Timer5 is reset on the Q1 rising edge following the event capture. With the Special Event Trigger Reset disabled, Timer5 cannot be reset by the Special Event Trigger Reset on the CAP1 input. In order for the Special Event Trigger Reset to work as the Reset trigger to Timer5, IC1 must be configured in the Special Event Trigger mode (CAP1M<3:0> = 1110 or 1111).

#### 17.2.2 QEI MODES

Position measurement resolution depends on how often the Position Counter register, POSCNT, is incremented. There are two QEI Update modes to measure the rotor's position: QEI x2 and QEI x4.

TABLE 17-4: QEI MODES

| QEIM<2:0> | Mode/<br>Reset                | Description                                                                           |

|-----------|-------------------------------|---------------------------------------------------------------------------------------|

| 000       |                               | QEI disabled. <sup>(1)</sup>                                                          |

| 001       | x2 update/<br>index pulse     | Two clocks per QEA pulse. INDX resets POSCNT.                                         |

| 010       | x2 update/<br>period<br>match | Two clocks per QEA pulse. POSCNT is reset by the period match (MAXCNT).               |

| 011       | _                             | Unused.                                                                               |

| 100       | _                             | Unused.                                                                               |

| 101       | x4 update/<br>index pulse     | Four clocks per QEA and QEB pulse pair. INDX resets POSCNT.                           |

| 110       | x4 update/<br>period<br>match | Four clocks per QEA and QEB pulse pair. POSCNT is reset by the period match (MAXCNT). |

| 111       | _                             | Unused.                                                                               |

**Note 1:** QEI module is disabled. The position counter and the velocity measurement functions are fully disabled in this mode.

#### 17.2.2.1 QEI x2 Update Mode

QEI x2 Update mode is selected by setting the QEI Mode Select bits (QEIM<2:0>) to '001' or '010'. In this mode, the QEI logic detects every edge on the QEA input only. Every rising and falling edge on the QEA signal clocks the position counter.

The position counter can be reset by either an input on the INDX pin (QEIM<2:0> = 001), or by a period match, even when the POSCNT register pair equals MAXCNT (QEIM<2:0> = 010).

#### 17.2.2.2 QEI x4 Update Mode

QEI x4 Update mode provides for a finer resolution of the rotor position, since the counter increments or decrements more frequently for each QEA/QEB input pulse pair than in QEI x2 mode. This mode is selected by setting the QEI mode select bits to '101' or '110'. In QEI x4, the phase measurement is made on the rising and the falling edges of both QEA and QEB inputs. The position counter is clocked on every QEA and QEB edge.

Like QEI x2 mode, the position counter can be reset by an input on the pin (QEIM<2:0> = 101), or by the period match event (QEIM<2:0> = 010).

#### 17.2.3 QEI OPERATION

The Position Counter register pair (POSCNTH: POSCNTL) acts as an integrator, whose value is proportional to the position of the sensor rotor that corresponds to the number of active edges detected. POSCNT can either increment or decrement, depending on a number of selectable factors which are decoded by the QEI logic block. These include the Count mode selected, the phase relationship of QEA to QEB ("lead/lag"), the direction of rotation and if a Reset event occurs. The logic is detailed in the sections that follow.

#### 17.2.3.1 Edge and Phase Detect

In the first step, the active edges of QEA and QEB are detected, and the phase relationship between them is determined. The position counter is changed based on the selected QEI mode.

In QEI x2 Update mode, the position counter increments or decrements on every QEA edge based on the phase relationship of the QEA and QEB signals.

In QEI x4 Update mode, the position counter increments or decrements on every QEA and QEB edge based on the phase relationship of the QEA and QEB signals. For example, if QEA leads QEB, the position counter is incremented by '1'. If QEB lags QEA, the position counter is decremented by '1'.

#### 17.2.3.2 Direction of Count

The QEI control logic generates a signal that sets the UP/DOWN bit (QEICON<5>); this, in turn, determines the direction of the count. When QEA leads QEB, UP/DOWN is set (= 1) and the position counter increments on every active edge. When QEA lags QEB, UP/DOWN is cleared and the position counter decrements on every active edge.

TABLE 17-5: DIRECTION OF ROTATION

| Current         | P   | Previous Signal<br>Detected |     |      |                               |  |  |

|-----------------|-----|-----------------------------|-----|------|-------------------------------|--|--|

| Signal Detected | Ris | sing                        | Fal | ling | Pos.<br>Cntrl. <sup>(1)</sup> |  |  |

|                 | QEA | QEB                         | QEA | QEB  |                               |  |  |

| QEA Rising      |     |                             |     | Х    | INC                           |  |  |

|                 |     | Х                           |     |      | DEC                           |  |  |

| QEA Falling     |     |                             |     | Х    | DEC                           |  |  |

|                 |     | Х                           |     |      | INC                           |  |  |

| QEB Rising      | Х   |                             |     |      | INC                           |  |  |

|                 |     |                             | Х   |      | DEC                           |  |  |

| QEB Falling     |     |                             | Х   |      | INC                           |  |  |

|                 | Х   |                             |     |      | DEC                           |  |  |

Note 1: When UP/DOWN = 1, the position counter is incremented. When UP/DOWN = 0, the position counter is decremented.

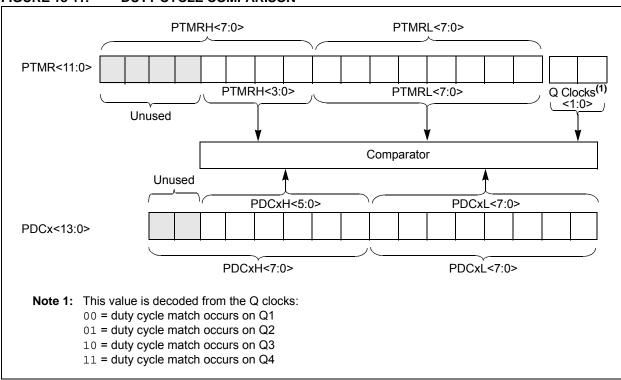

#### 18.6 PWM Duty Cycle

PWM duty cycle is defined by the PDCx (PDCxL and PDCxH) registers. There are a total of four PWM Duty Cycle registers for four pairs of PWM channels. The Duty Cycle registers have 14-bit resolution by combining six LSbs of PDCxH with the 8 bits of PDCxL. PDCx is a double-buffered register used to set the counting period for the PWM time base.

#### 18.6.1 PWM DUTY CYCLE REGISTERS

There are four 14-bit Special Function Registers used to specify duty cycle values for the PWM module:

- PDC0 (PDC0L and PDC0H)

- PDC1 (PDC1L and PDC1H)

- PDC2 (PDC2L and PDC2H)

- PDC3 (PDC3L and PDC3H)

The value in each Duty Cycle register determines the amount of time that the PWM output is in the active state. The upper 12 bits of PDCx holds the actual duty cycle value from PTMRH/L<11:0>, while the lower 2 bits control which internal Q clock the duty cycle match will occur. This 2-bit value is decoded from the Q clocks as shown in Figure 18-11 (when the prescaler is 1:1 or PTCKPS<1:0> = 00).

In Edge-Aligned mode, the PWM period starts at Q1 and ends when the Duty Cycle register matches the PTMR register as follows. The duty cycle match is considered when the upper 12 bits of the PDCx are equal to the PTMR and the lower 2 bits are equal to Q1, Q2, Q3 or Q4, depending on the lower two bits of the PDCx (when the prescaler is 1:1 or PTCKPS<1:0> = 00).

Note: When the prescaler is not 1:1 (PTCKPS<1:0> ≠ ~00), the duty cycle match occurs at the Q1 clock of the instruction cycle when the PTMR and PDCx match occurs.

Each compare unit has logic that allows override of the PWM signals. This logic also ensures that the PWM signals will complement each other (with dead-time insertion) in Complementary mode (see **Section 18.7** "**Dead-Time Generators**").

FIGURE 18-11: DUTY CYCLE COMPARISON

#### REGISTER 18-5: DTCON: DEAD-TIME CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DTPS1 | DTPS0 | DT5   | DT4   | DT3   | DT2   | DT1   | DT0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 **DTPS<1:0>:** Dead-Time Unit A Prescale Select bits

11 = Clock source for dead-time unit is Fosc/16

10 = Clock source for dead-time unit is Fosc/8

01 = Clock source for dead-time unit is Fosc/4

00 = Clock source for dead-time unit is Fosc/2

bit 5-0 **DT<5:0>:** Unsigned 6-Bit Dead-Time Value for Dead-Time Unit bits

#### 18.7.2 DEAD-TIME RANGES

The amount of dead time provided by the dead-time unit is selected by specifying the input clock prescaler value and a 6-bit unsigned value defined in the DTCON register. Four input clock prescaler selections have been provided to allow a suitable range of dead times based on the device operating frequency. Fosc/2, Fosc/4, Fosc/8 and Fosc/16 are the clock prescaler options available using the DTPS<1:0> control bits in the DTCON register.

After selecting an appropriate prescaler value, the dead time is adjusted by loading a 6-bit unsigned value into DTCON<5:0>. The dead-time unit prescaler is cleared on any of the following events:

- On a load of the down timer due to a duty cycle comparison edge event;

- · On a write to the DTCON register; or

- · On any device Reset.

# 18.7.3 DECREMENTING THE DEAD-TIME COUNTER

The dead-time counter is clocked from any of the Q clocks based on the following conditions.

- 1. The dead-time counter is clocked on Q1 when:

- The DTPS bits are set to any of the following dead-time prescaler settings: Fosc/4, Fosc/8, Fosc/16

- The PWM Time Base Prescale bits (PTCKPS) are set to any of the following prescale ratios: Fosc/16, Fosc/64, Fosc/256

- The dead-time counter is clocked by a pair of Q clocks when the PWM Time Base Prescale bits are set to 1:1 (PTCKPS<1:0> = 00, Fosc/4) and the dead-time counter is clocked by the Fosc/2 (DTPS<1:0> = 00).

- The dead-time counter is clocked using every other Q clock, depending on the two LSbs in the Duty Cycle registers:

- If the PWM duty cycle match occurs on Q1 or Q3, then the dead-time counter is clocked using every Q1 and Q3.

- If the PWM duty cycle match occurs on Q2 or Q4, then the dead-time counter is clocked using every Q2 and Q4.

- 4. When the DTPS<1:0> bits are set to any of the other dead-time prescaler settings (i.e., Fosc/4, Fosc/8 or Fosc/16) and the PWM time base prescaler is set to 1:1, the dead-time counter is clocked by the Q clock corresponding to the Q clocks on which the PWM duty cycle match occurs.

#### 18.13 PWM Update Lockout

For a complex PWM application, the user may need to write up to four Duty Cycle registers and the PWM Time Base Period register, PTPER, at a given time. In some applications, it is important that all buffer registers be written before the new duty cycle and period values are loaded for use by the module.

A PWM update lockout feature may optionally be enabled so the user may specify when new duty cycle buffer values are valid. The PWM update lockout feature is enabled by setting the control bit, UDIS, in the PWMCON1 register. This bit affects all Duty Cycle Buffer registers and the PWM Time Base Period register, PTPER.

To perform a PWM update lockout:

- 1. Set the UDIS bit.

- 2. Write all Duty Cycle registers and PTPER, if applicable.

- 3. Clear the UDIS bit to re-enable updates.

- With this, when UDIS bit is cleared, the buffer values will be loaded to the actual registers. This makes a synchronous loading of the registers.

#### 18.14 PWM Special Event Trigger

The PWM module has a Special Event Trigger capability that allows A/D conversions to be synchronized to the PWM time base. The A/D sampling and conversion time may be programmed to occur at any point within the PWM period. The Special Event Trigger allows the user to minimize the delay between the time when A/D conversion results are acquired and the time when the duty cycle value is updated.

The PWM 16-bit Special Event Trigger register, SEVTCMP (high and low), and five control bits in the PWMCON1 register are used to control its operation.

The PTMR value for which a Special Event Trigger should occur is loaded into the SEVTCMP register pair. The SEVTDIR bit in the PWMCON1 register specifies the counting phase when the PWM time base is in a Continuous Up/Down Count mode.

If the SEVTDIR bit is cleared, the Special Event Trigger will occur on the upward counting cycle of the PWM time base. If SEVTDIR is set, the Special Event Trigger will occur on the downward count cycle of the PWM time base. The SEVTDIR bit has effect only when the PWM timer is in the Continuous Up/Down Count mode.

#### 18.14.1 SPECIAL EVENT TRIGGER ENABLE

The PWM module will always produce Special Event Trigger pulses. This signal may optionally be used by the A/D module. Refer to Section 21.0 "10-Bit High-Speed Analog-to-Digital Converter (A/D) Module" for details.

# 18.14.2 SPECIAL EVENT TRIGGER POSTSCALER

The PWM Special Event Trigger has a postscaler that allows a 1:1 to 1:16 postscale ratio. The postscaler is configured by writing the SEVOPS<3:0> control bits in the PWMCON1 register.

The Special Event Trigger output postscaler is cleared on any write to the SEVTCMP register pair, or on any device Reset.

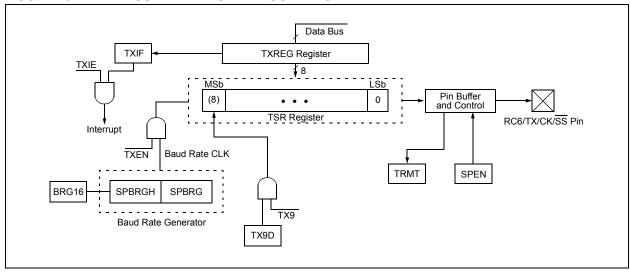

#### FIGURE 20-2: EUSART TRANSMIT BLOCK DIAGRAM

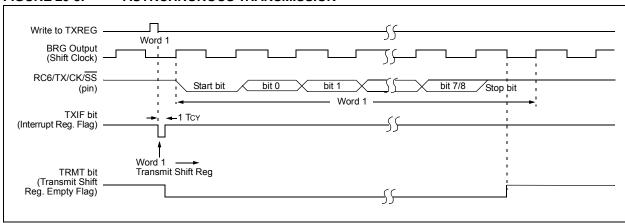

#### FIGURE 20-3: ASYNCHRONOUS TRANSMISSION

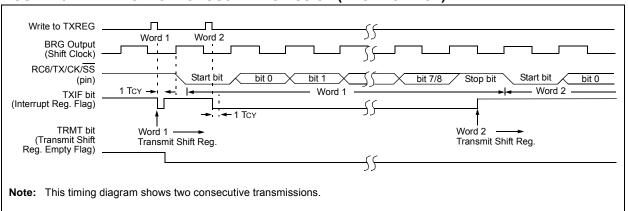

#### FIGURE 20-4: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### 24.0 INSTRUCTION SET SUMMARY

The PIC18 instruction set adds many enhancements to the previous PIC® instruction sets, while maintaining an easy migration from these PIC instruction sets.

Most instructions are a single program memory word (16 bits), but there are three instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most **byte-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction.

The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the WREG register. If 'd' is '1', the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator, 'b', selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the call or return instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for three double-word instructions. These three instructions were made double word instructions so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have.

All examples use the format 'nnh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 24-2, lists the instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup> Assembler). **Section 24.2** "Instruction Set" provides a description of each instruction.

#### 24.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator, 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "BCF PORTB, 1" instruction will read PORTB, clear bit 1 of the data, then write the result back to PORTB. The read operation would have the unintended result that any condition that sets the RBIF flag would be cleared. The R-M-W operation may also copy the level of an input pin to its corresponding output latch.

| BTFSC       | FSC Bit Test File, Skip if Clear                                             |                                                                                                                                     | BTFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S                                                                  | Bit Test File, Skip if Set |                                          |                                                     |                 |                                                         |               |  |

|-------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|------------------------------------------|-----------------------------------------------------|-----------------|---------------------------------------------------------|---------------|--|

| Syntax:     |                                                                              | [label] BTF                                                                                                                         | SC f,b[,a]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    | Syntax                     | :                                        | [ label ] BT                                        | FSS f,b[,a]     |                                                         |               |  |

| Operands:   | :                                                                            | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | Operands:                  |                                          | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$ |                 |                                                         |               |  |

| Operation:  | :                                                                            | skip if (f <b>)</b>                                                                                                                 | = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    | Operat                     | ion:                                     | skip if (f <b>) = 1</b>                             |                 |                                                         |               |  |

| Status Affe | ected:                                                                       | None                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | Status                     | Affected:                                | None                                                |                 |                                                         |               |  |

| Encoding:   |                                                                              | 1011                                                                                                                                | bbba ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ff ffff                                                            | Encodi                     | ng:                                      | 1010                                                | bbba            | ffff                                                    | ffff          |  |

| Description | n:                                                                           | instruction is<br>If bit 'b' is '0'<br>fetched during<br>execution is<br>executed instruction. I'<br>will be selectivalue. If 'a' = | Description:  If bit 'b' in register, 'f', is '1', then the next instruction is skipped.  Description:  If bit 'b' in register, 'f', is '1', then the next instruction is skipped.  If bit 'b' is '1', then the next instruction is discarded, and a NOP is execution, is discarded and a NOP ted instead, making this a two-cycle executed instead, making this a two-cycle executed instead, making this a two-cycle executed, overriding the BSR will be selected, overriding the BSR will be selected, overriding the BSR will be selected as per the BSR value. |                                                                    |                            |                                          |                                                     |                 | uction<br>ction<br>OP is<br>two-cycle<br>ss Bank<br>BSR |               |  |

| Words:      |                                                                              | 1                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | Words                      | :                                        | 1                                                   |                 |                                                         |               |  |

| Cycles:     | : 1(2) Cycles:  Note: 3 cycles if skip and followed by a 2-word instruction. |                                                                                                                                     | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1(2)  Note: 3 cycles if skip and followed by a 2-word instruction. |                            |                                          |                                                     |                 |                                                         |               |  |

| Q Cycle A   | Activity:                                                                    |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | Q Cyc                      | cle Activity:                            |                                                     |                 |                                                         |               |  |

|             | Q1                                                                           | Q2                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                 | _                          | Q1                                       | Q2                                                  | Q3              | -                                                       | Q4            |  |

| De          | ecode                                                                        | Read register 'f'                                                                                                                   | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No operation                                                       |                            | Decode                                   | Read register 'f'                                   | Process<br>Data | l l                                                     | No<br>eration |  |

| If skip:    |                                                                              |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | If skip                    | :                                        |                                                     |                 |                                                         |               |  |

|             | Q1                                                                           | Q2                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                 | _                          | Q1                                       | Q2                                                  | Q3              | 1                                                       | Q4            |  |

|             | No<br>eration                                                                | No operation                                                                                                                        | No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No operation                                                       |                            | No operation                             | No operation                                        | No operation    | n on                                                    | No<br>eration |  |

| <u> </u>    |                                                                              | by 2-word ins                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | operation                                                          | ∟<br>If skip               | •                                        | d by 2-word in                                      | <u> </u>        | .   ор                                                  | oracion .     |  |

| ·           | Q1                                                                           | Q2                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                 | •                          | Q1                                       | Q2                                                  | Q3              |                                                         | Q4            |  |

|             | No                                                                           | No                                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No                                                                 |                            | No                                       | No                                                  | No              |                                                         | No            |  |

|             | eration                                                                      | operation                                                                                                                           | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation                                                          | _                          | operation                                | operation                                           | operation       | n op                                                    | eration       |  |

|             | No<br>eration                                                                | No<br>operation                                                                                                                     | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No<br>operation                                                    |                            | No<br>operation                          | No<br>operation                                     | No<br>operation | п ор                                                    | No<br>eration |  |

| Example:    |                                                                              | HERE BY                                                                                                                             | TFSC FLAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3, 1                                                               | Examp                      | lle:                                     | HERE FALSE :                                        |                 | LAG, 1                                                  |               |  |

|             | re Instruct<br>PC                                                            |                                                                                                                                     | ress (HERE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    | В                          | efore Instruc                            |                                                     | dress (HEI      | RE)                                                     |               |  |

| After<br>I  | Instructio If FLAG< PC If FLAG< PC                                           | n<br>1> = 0;<br>= add<br>1> = 1;                                                                                                    | ress (TRUE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    | A                          | fter Instruction If FLAG< PC If FLAG< PC | on<br>1> = 0;<br>= ad<br>1> = 1;                    | dress (FA       | LSE)                                                    |               |  |

| CON         | ИF             | Complen                                                                                                                                                                                                                                                                                         | Complement f               |      |                    |  |  |  |  |  |