Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN-S (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2331-i-mm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

PIC18LF2431

- PIC18F2331 PIC18LF2331

- PIC18F2431

- PIC18F4331 PIC18LF4331

- PIC18F4431 PIC18LF4431

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price, with the addition of high-endurance enhanced Flash program memory and a high-speed 10-bit A/D Converter. On top of these features, the PIC18F2331/2431/4331/4431 family introduces design enhancements that make these micro-controllers a logical choice for many high-performance, power control and motor control applications. These special peripherals include:

- 14-Bit Resolution Power Control PWM module (PCPWM) with Programmable Dead-Time Insertion

- Motion Feedback Module (MFM), including a 3-Channel Input Capture (IC) module and Quadrature Encoder Interface (QEI)

- High-Speed 10-Bit A/D Converter (HSADC)

The PCPWM can generate up to eight complementary PWM outputs with dead-band time insertion. Overdrive current is detected by off-chip analog comparators or the digital Fault inputs (FLTA, FLTB).

The MFM Quadrature Encoder Interface provides precise rotor position feedback and/or velocity measurement. The MFM 3x input capture or external interrupts can be used to detect the rotor state for electrically commutated motor applications using Hall sensor feedback, such as BLDC motor drives.

PIC18F2331/2431/4331/4431 devices also feature Flash program memory and an internal RC oscillator with built-in LP modes.

## 1.1 New Core Features

### 1.1.1 nanoWatt Technology

All of the devices in the PIC18F2331/2431/4331/4431 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled, but the peripherals are still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Lower Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer have been reduced by up to 80%, with typical values of 1.1 and 2.1  $\mu$ A, respectively.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2331/2431/4331/4431 family offer nine different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes, with the same pin options as the External Clock modes.

- An internal oscillator block, which provides an 8 MHz clock and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of 6 user-selectable clock frequencies (from 125 kHz to 4 MHz) for a total of 8 clock frequencies.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

## 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

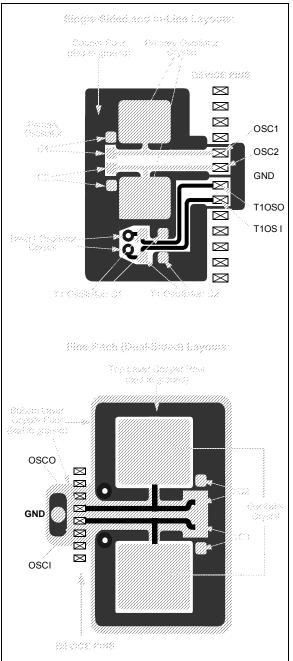

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

## 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| R/W-0         | R/W-0                                                                                                    | R/W-0                                                  | R/W-0            | R <sup>(1)</sup>                                                  | R-0              | R/W-0           | R/W-0 |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|-------------------------------------------------------------------|------------------|-----------------|-------|

| IDLEN         | IRCF2                                                                                                    | IRCF1                                                  | IRCF0            | OSTS                                                              | IOFS             | SCS1            | SCS0  |

| bit 7         |                                                                                                          |                                                        |                  |                                                                   |                  | •               | bit 0 |

| Legend:       |                                                                                                          |                                                        |                  |                                                                   |                  |                 |       |

| R = Readabl   | e bit                                                                                                    | W = Writable                                           | bit              | U = Unimpler                                                      | nented bit, read | d as '0'        |       |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                                       |                  | '0' = Bit is clea                                                 | ared             | x = Bit is unkr | iown  |

| bit 7         |                                                                                                          | le enabled; CPl                                        |                  | ocked in power-<br>ked in power-ma                                | •                | les             |       |

| bit 6-4       | 111 = 8 MHz<br>110 = 4 MHz<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kH<br>010 = 250 kH<br>001 = 125 kH | z<br>z<br>Hz<br>Hz                                     | e drives clock o | directly)                                                         |                  |                 |       |

| bit 3         | 1 = Oscillato                                                                                            |                                                        | r time-out has   | Status bit <sup>(1)</sup><br>expired; primar<br>inning; primary o |                  | U U             |       |

| bit 2         | 1 = INTOSC                                                                                               | SC Frequency S<br>frequency is st<br>frequency is no   | able             |                                                                   |                  |                 |       |

| bit 1-0       | 1x = Internal                                                                                            | System Clock So<br>oscillator block<br>ary (Timer1) os |                  |                                                                   |                  |                 |       |

#### REGISTER 3-2: OSCCON: OSCILLATOR CONTROL REGISTER

2: Default output frequency of INTOSC on Reset.

| TABLE 5-3:           | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |      |      |      |                                    |                                                               | NUED)                           |  |

|----------------------|---------------------------------------------------------|------|------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|--|

| Register             | Applicable Devices                                      |      |      | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| PTCON0               | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | uuuu uuuu                                                     | uuuu uuuu                       |  |

| PTCON1               | 2331                                                    | 2431 | 4331 | 4431 | 00                                 | 00                                                            | uu                              |  |

| PTMRL                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| PTMRH                | 2331                                                    | 2431 | 4331 | 4431 | 0000                               | 0000                                                          | uuuu                            |  |

| PTPERL               | 2331                                                    | 2431 | 4331 | 4431 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |

| PTPERH               | 2331                                                    | 2431 | 4331 | 4431 | 1111                               | 1111                                                          | uuuu                            |  |

| PDC0L                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| PDC0H                | 2331                                                    | 2431 | 4331 | 4431 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |

| PDC1L                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| PDC1H                | 2331                                                    | 2431 | 4331 | 4431 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |

| PDC2L                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| PDC2H                | 2331                                                    | 2431 | 4331 | 4431 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |

| PDC3L                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| PDC3H                | 2331                                                    | 2431 | 4331 | 4431 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |

| SEVTCMPL             | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| SEVTCMPH             | 2331                                                    | 2431 | 4331 | 4431 | 0000                               | 0000                                                          | uuuu                            |  |

| PWMCON0              | 2331                                                    | 2431 | 4331 | 4431 | -111 0000                          | -111 0000                                                     | -uuu uuuu                       |  |

| PWMCON1              | 2331                                                    | 2431 | 4331 | 4431 | 0000 0-00                          | 0000 0-00                                                     | uuuu u-uu                       |  |

| DTCON                | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| FLTCONFIG            | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| OVDCOND              | 2331                                                    | 2431 | 4331 | 4431 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |

| OVDCONS              | 2331                                                    | 2431 | 4331 | 4431 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| CAP1BUFH/<br>VELRH   | 2331                                                    | 2431 | 4331 | 4431 | XXXX XXXX                          | սսսս սսսս                                                     | <u>uuuu</u> uuuu                |  |

| CAP1BUFL/<br>VELRL   | 2331                                                    | 2431 | 4331 | 4431 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| CAP2BUFH/<br>POSCNTH | 2331                                                    | 2431 | 4331 | 4431 | XXXX XXXX                          | սսսս սսսս                                                     | <u>uuuu</u> uuuu                |  |

| CAP2BUFL/<br>POSCNTL | 2331                                                    | 2431 | 4331 | 4431 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |

| CAP3BUFH/<br>MAXCNTH | 2331                                                    | 2431 | 4331 | 4431 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |

## TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-2 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** Bit 3 of PORTE and LATE are enabled if MCLR functionality is disabled. When not enabled as the PORTE pin, they are disabled and read as '0'. The 28-pin devices do not have only RE3 implemented.

#### 6.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location. Look-up table data may be stored, two bytes per program word, by using table reads and writes.

The Table Pointer register (TBLPTR) specifies the byte address and the Table Latch register (TABLAT) contains the data that is read from or written to program memory. Data is transferred to or from program memory, one byte at a time.

Table read and table write operations are discussed further in Section 8.1 "Table Reads and Table Writes".

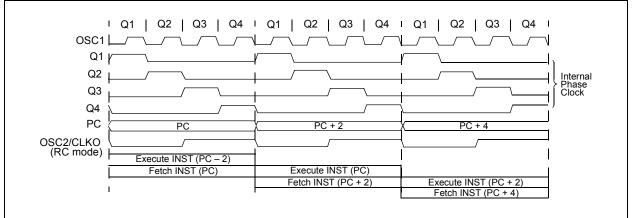

## 6.2 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the Instruction Register (IR) in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 6-4.

## FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

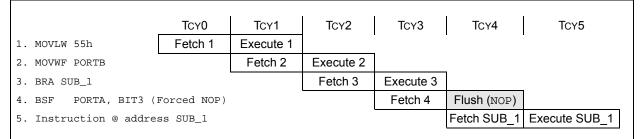

## 6.3 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 6-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle, Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

## 6.4 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). Figure 6-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0'.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction 2 in Figure 6-5 shows how the instruction, 'GOTO 00006h', is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 24.0 "Instruction Set Summary"** provides further details of the instruction set.

## 6.4.1 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the four MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence, immediately after the first word, the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 shows how this works.

Note: For information on two-word instructions in the extended instruction set, see Section 24.2 "Instruction Set".

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program N  |                    |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 000006h            | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h     | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

## FIGURE 6-5: INSTRUCTIONS IN PROGRAM MEMORY

#### EXAMPLE 6-4: TWO-WORD INSTRUCTIONS

| CASE 1:             |             |                               |

|---------------------|-------------|-------------------------------|

| Object Code         | Source Code |                               |

| 0110 0110 0000 0000 | TSTFSZ REG1 | ; is RAM location 0?          |

| 1100 0001 0010 0011 | MOVFF REG1, | REG2 ; No, skip this word     |

| 1111 0100 0101 0110 |             | ; Execute this word as a NOP  |

| 0010 0100 0000 0000 | ADDWF REG3  | ; continue code               |

| CASE 2:             |             |                               |

| Object Code         | Source Code |                               |

| 0110 0110 0000 0000 | TSTFSZ REG1 | ; is RAM location 0?          |

| 1100 0001 0010 0011 | MOVFF REG1, | REG2 ; Yes, execute this word |

| 1111 0100 0101 0110 |             | ; 2nd word of instruction     |

| 0010 0100 0000 0000 | ADDWF REG3  | ; continue code               |

## 8.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 8.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. Setting the 22nd bit allows access to the Device ID, the User ID and the Configuration bits.

The TBLPTR is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 8-1. These operations on the TBLPTR only affect the low-order 21 bits.

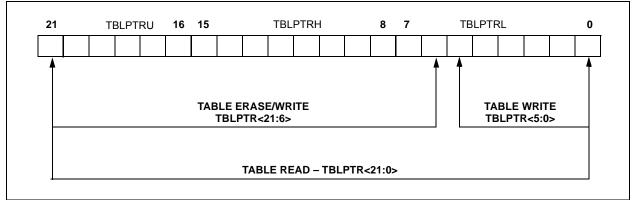

## 8.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program or configuration memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer, TBLPTR (TBLPTR<21:3>), will determine which program memory block of 8 bytes is written to (TBLPTR<2:0> are ignored). For more detail, see **Section 8.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 8-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

#### TABLE 8-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 8-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

## 8.3 Reading the Flash Program Memory

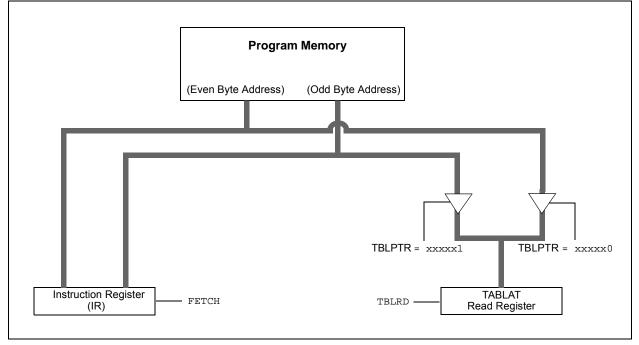

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 8-4 shows the interface between the internal program memory and the TABLAT.

## FIGURE 8-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 8-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |   |                                                  |

| READ_WORD |                                           |                                                                          |   |                                                  |

|           | TBLRD*-                                   | +                                                                        | ; | read into TABLAT and increment TBLPTR            |

|           | MOVF                                      | TABLAT,W                                                                 | ; | get data                                         |

|           | MOVWF                                     | WORD_EVEN                                                                |   |                                                  |

|           | TBLRD*-                                   | +                                                                        | ; | read into TABLAT and increment TBLPTR            |

|           | MOVF                                      | TABLAT,W                                                                 | ; | get data                                         |

|           | MOVWF                                     | WORD_ODD                                                                 |   |                                                  |

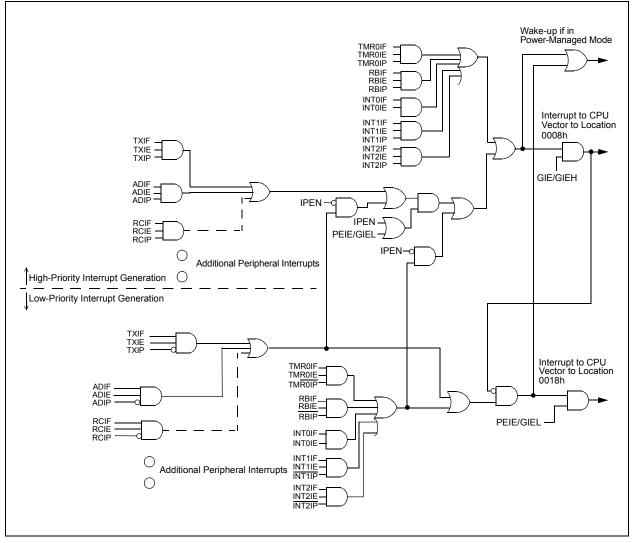

### 10.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7    |           |        |        |       |        |        | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit                                            |

|-------|----------------------------------------------------------------------------------|

|       | $\frac{\text{When IPEN} = 0}{1000}$                                              |

|       | 1 = Enables all unmasked interrupts                                              |

|       | 0 = Disables all interrupts                                                      |

|       | <u>When IPEN = 1:</u><br>1 = Enables all high-priority interrupts                |

|       | 0 = Disables all high-priority interrupts                                        |

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit                                       |

| bit o | When IPEN = $0$ :                                                                |

|       | 1 = Enables all unmasked peripheral interrupts                                   |

|       | 0 = Disables all peripheral interrupts                                           |

|       | When IPEN = 1:                                                                   |

|       | 1 = Enables all low-priority peripheral interrupts                               |

|       | 0 = Disables all low-priority peripheral interrupts                              |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit                                       |

|       | 1 = Enables the TMR0 overflow interrupt                                          |

|       | 0 = Disables the TMR0 overflow interrupt                                         |

| bit 4 | INTOIE: INTO External Interrupt Enable bit                                       |

|       | 1 = Enables the INT0 external interrupt                                          |

|       | 0 = Disables the INT0 external interrupt                                         |

| bit 3 | RBIE: RB Port Change Interrupt Enable bit                                        |

|       | 1 = Enables the RB port change interrupt for RB<7:4> pins                        |

|       | 0 = Disables the RB port change interrupt for RB<7:4> pins                       |

| bit 2 | TMR0IF: TMR0 Overflow Interrupt Flag bit                                         |

|       | 1 = TMR0 register has overflowed (must be cleared in software)                   |

|       | 0 = TMR0 register did not overflow                                               |

| bit 1 | INTOIF: INTO External Interrupt Flag bit                                         |

|       | 1 = The INT0 external interrupt occurred (must be cleared in software)           |

|       | 0 = The INT0 external interrupt did not occur                                    |

| bit 0 | RBIF: RB Port Change Interrupt Flag bit                                          |

|       | 1 = At least one of the RB<7:4> pins changed state (must be cleared in software) |

|       | 0 = None of the RB<7:4> pins have changed state                                  |

|       |                                                                                  |

NOTES:

## 18.12.3 PWM OUTPUTS WHILE IN FAULT CONDITION

While in the Fault state (i.e., one or both FLTA and FLTB inputs are active), the PWM output signals are driven into their inactive states. The selection of which PWM outputs are deactivated (while in the Fault state) is determined by the FLTCON bit in the FLTCONFIG register as follows:

- FLTCON = 1: When FLTA or FLTB is asserted, the PWM outputs (i.e., PWM<7:0>) are driven into their inactive state.

- FLTCON = 0: When FLTA or FLTB is asserted, only PWM<5:0> outputs are driven inactive, leaving PWM<7:6> activated.

- Note: Disabling only three PWM channels and leaving one PWM channel enabled when in the Fault state, allows the flexibility to have at least one PWM channel enabled. None of the PWM outputs can be enabled (driven with the PWM Duty Cycle registers) while FLTCON = 1 and the Fault condition is present.

## 18.12.4 PWM OUTPUTS IN DEBUG MODE

The BRFEN bit in the FLTCONFIG register controls the simulation of a Fault condition, when a breakpoint is hit, while debugging the application using an In-Circuit Emulator (ICE) or an In-Circuit Debugger (ICD). Setting the BRFEN to high, enables the Fault condition on breakpoint, thus driving the PWM outputs to the inactive state. This is done to avoid any continuous keeping of status on the PWM pin, which may result in damage of the power devices connected to the PWM outputs.

If BRFEN = 0, the Fault condition on breakpoint is disabled.

Note: It is highly recommended to enable the Fault condition on breakpoint if a debugging tool is used while developing the firmware and high-power circuitry. When the device is ready to program after debugging the firmware, the BRFEN bit can be disabled.

| Mnemonic, |      |                                | 16-1   | Bit Instr | uction V | Vord | Status |                        |   |

|-----------|------|--------------------------------|--------|-----------|----------|------|--------|------------------------|---|

| Opera     | ,    | Description                    | Cycles | MSb       |          |      | LSb    | Affected Notes         |   |

| CONTROL   | OPER | ATIONS                         |        | •         |          |      |        | ·                      |   |

| BC        | n    | Branch if Carry                | 1 (2)  | 1110      | 0010     | nnnn | nnnn   | None                   |   |

| BN        | n    | Branch if Negative             | 1 (2)  | 1110      | 0110     | nnnn | nnnn   | None                   |   |

| BNC       | n    | Branch if Not Carry            | 1 (2)  | 1110      | 0011     | nnnn | nnnn   | None                   |   |

| BNN       | n    | Branch if Not Negative         | 1 (2)  | 1110      | 0111     | nnnn | nnnn   | None                   |   |

| BNOV      | n    | Branch if Not Overflow         | 1 (2)  | 1110      | 0101     | nnnn | nnnn   | None                   |   |

| BNZ       | n    | Branch if Not Zero             | 2      | 1110      | 0001     | nnnn | nnnn   | None                   |   |

| BOV       | n    | Branch if Overflow             | 1 (2)  | 1110      | 0100     | nnnn | nnnn   | None                   |   |

| BRA       | n    | Branch Unconditionally         | 1 (2)  | 1101      | 0nnn     | nnnn | nnnn   | None                   |   |

| BZ        | n    | Branch if Zero                 | 1 (2)  | 1110      | 0000     | nnnn | nnnn   | None                   |   |

| CALL      | n, s | Call Subroutine 1st word       | 2      | 1110      | 110s     | kkkk | kkkk   | None                   |   |

|           |      | 2nd word                       |        | 1111      | kkkk     | kkkk | kkkk   |                        |   |

| CLRWDT    | _    | Clear Watchdog Timer           | 1      | 0000      | 0000     | 0000 | 0100   | TO, PD                 |   |

| DAW       | —    | Decimal Adjust WREG            | 1      | 0000      | 0000     | 0000 | 0111   | C, DC                  |   |

| GOTO      | n    | Go to Address 1st word         | 2      | 1110      | 1111     | kkkk | kkkk   | None                   |   |

|           |      | 2nd word                       |        | 1111      | kkkk     | kkkk | kkkk   |                        |   |

| NOP       | _    | No Operation                   | 1      | 0000      | 0000     | 0000 | 0000   | None                   |   |

| NOP       | —    | No Operation                   | 1      | 1111      | xxxx     | xxxx | xxxx   | None                   | 4 |

| POP       | _    | Pop Top of Return Stack (TOS)  | 1      | 0000      | 0000     | 0000 | 0110   | None                   |   |

| PUSH      | —    | Push Top of Return Stack (TOS) | 1      | 0000      | 0000     | 0000 | 0101   | None                   |   |

| RCALL     | n    | Relative Call                  | 2      | 1101      | 1nnn     | nnnn | nnnn   | None                   |   |

| RESET     |      | Software Device Reset          | 1      | 0000      | 0000     | 1111 | 1111   | All                    |   |

| RETFIE    | S    | Return from Interrupt Enable   | 2      | 0000      | 0000     | 0001 | 000s   | GIE/GIEH,<br>PEIE/GIEL |   |

| RETLW     | k    | Return with Literal in WREG    | 2      | 0000      | 1100     | kkkk | kkkk   | None                   |   |

| RETURN    | S    | Return from Subroutine         | 2      | 0000      | 0000     | 0001 | 001s   | None                   |   |

| SLEEP     | _    | Go into Standby mode           | 1      | 0000      | 0000     | 0000 | 0011   | TO, PD                 |   |

## TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**4:** Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| ADD      | OWFC                                      | AD                          | ADD W and Carry bit to f                                                                                                                                                                                                                                                        |                      |    |    |                   |  |  |  |

|----------|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|----|-------------------|--|--|--|

| Synta    | ax:                                       | [ lat                       | [ <i>label</i> ] ADDWFC f [,d [,a]]                                                                                                                                                                                                                                             |                      |    |    |                   |  |  |  |

| Oper     | ands:                                     | d ∈                         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                             |                      |    |    |                   |  |  |  |

| Oper     | ation:                                    | (W)                         | + (f) + (                                                                                                                                                                                                                                                                       | $C) \rightarrow des$ | st |    |                   |  |  |  |

| Statu    | s Affected:                               | Ν, Ο                        | DV, C, D                                                                                                                                                                                                                                                                        | C, Z                 |    |    |                   |  |  |  |

| Enco     | oding:                                    | (                           | 010                                                                                                                                                                                                                                                                             | 00da                 | ff | ff | ffff              |  |  |  |

| Desc     | ription:                                  | loca<br>in V<br>data<br>Acc | Add W, the Carry flag and data memory<br>location, 'f'. If 'd' is '0', the result is placed<br>in W. If 'd' is '1', the result is placed in<br>data memory location, 'f'. If 'a' is '0', the<br>Access Bank will be selected. If 'a' is '1',<br>the BSR will not be overridden. |                      |    |    |                   |  |  |  |

| Word     | ls:                                       | 1                           | 1                                                                                                                                                                                                                                                                               |                      |    |    |                   |  |  |  |

| Cycle    | es:                                       | 1                           | 1                                                                                                                                                                                                                                                                               |                      |    |    |                   |  |  |  |

| QC       | ycle Activity:                            |                             |                                                                                                                                                                                                                                                                                 |                      |    |    |                   |  |  |  |

|          | Q1                                        | (                           | Q2                                                                                                                                                                                                                                                                              | Q3                   |    |    | Q4                |  |  |  |

|          | Decode                                    |                             | ead<br>ster 'f'                                                                                                                                                                                                                                                                 | Proces<br>Data       | S  |    | ite to<br>ination |  |  |  |

| Example: |                                           | ADI                         | DWFC                                                                                                                                                                                                                                                                            | REG,                 | W  |    |                   |  |  |  |

|          | Before Instruc<br>Carry bit<br>REG<br>W   | =                           | 1<br>0x02<br>0x4D                                                                                                                                                                                                                                                               |                      |    |    |                   |  |  |  |

|          | After Instructic<br>Carry bit<br>REG<br>W | =                           | 0<br>0x02<br>0x50                                                                                                                                                                                                                                                               |                      |    |    |                   |  |  |  |

| ANDLW                 |  | Α         | AND Literal with W                                                                 |      |                   |    |               |  |  |

|-----------------------|--|-----------|------------------------------------------------------------------------------------|------|-------------------|----|---------------|--|--|

| Syntax:               |  | [/        | [ <i>label</i> ] ANDLW k                                                           |      |                   |    |               |  |  |

| Operands:             |  | 0         | $0 \le k \le 255$                                                                  |      |                   |    |               |  |  |

| Operation:            |  | (V        | (W) .AND. $k \rightarrow W$                                                        |      |                   |    |               |  |  |

| Status Affected:      |  | N,        | N, Z                                                                               |      |                   |    |               |  |  |

| Encoding:             |  | Γ         | 0000                                                                               | 1011 | kkkk              |    | kkkk          |  |  |

| Description:          |  |           | The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in W. |      |                   |    |               |  |  |

| Words:                |  | 1         |                                                                                    |      |                   |    |               |  |  |

| Cycles:               |  | 1         |                                                                                    |      |                   |    |               |  |  |

| Q Cycle Activity:     |  |           |                                                                                    |      |                   |    |               |  |  |

| Q1                    |  |           | Q2                                                                                 | Q3   |                   | Q4 |               |  |  |

| Decode                |  | Rea       |                                                                                    |      | Process V<br>Data |    | /rite to<br>W |  |  |

|                       |  |           |                                                                                    |      |                   |    |               |  |  |

| Example:              |  | Al        | JDLW                                                                               | 0x5F |                   |    |               |  |  |

| Before Instructi<br>W |  | tion<br>= | 0xA3                                                                               |      |                   |    |               |  |  |

0x03

=

After Instruction

W

| RLNCF                   | Rotate L                                                             | eft f (No                                                                                                                                                                                                                                                                                                                                  | Carry)      |                     |  |  |  |  |

|-------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|--|--|--|--|

| Syntax:                 | [ label ]                                                            | RLNCF                                                                                                                                                                                                                                                                                                                                      | f [,d [,a]] |                     |  |  |  |  |

| Operands:               | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                |                                                                                                                                                                                                                                                                                                                                            |             |                     |  |  |  |  |

| Operation:              | · · ·                                                                | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                                                                                                                              |             |                     |  |  |  |  |

| Status Affected:        | N, Z                                                                 | N, Z                                                                                                                                                                                                                                                                                                                                       |             |                     |  |  |  |  |

| Encoding:               | 0100                                                                 | 01da                                                                                                                                                                                                                                                                                                                                       | ffff        | ffff                |  |  |  |  |

| Description:            | one bit to t<br>placed in \<br>stored bac<br>Access Ba<br>ing the BS | The contents of register, 'f', are rotated<br>one bit to the left. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>stored back in register, 'f'. If 'a' is '0', the<br>Access Bank will be selected, overrid-<br>ing the BSR value. If 'a' is '1', then the<br>bank will be selected as per the BSR<br>value. |             |                     |  |  |  |  |

| Words:                  | 1                                                                    |                                                                                                                                                                                                                                                                                                                                            |             |                     |  |  |  |  |

| Cycles:                 | 1                                                                    |                                                                                                                                                                                                                                                                                                                                            |             |                     |  |  |  |  |

| Q Cycle Activity:       |                                                                      |                                                                                                                                                                                                                                                                                                                                            |             |                     |  |  |  |  |

| Q1                      | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                                                         |             | Q4                  |  |  |  |  |

| Decode                  | Read<br>register 'f'                                                 | Proces<br>Data                                                                                                                                                                                                                                                                                                                             |             | rite to<br>tination |  |  |  |  |

| Example: RLNCF REG      |                                                                      |                                                                                                                                                                                                                                                                                                                                            |             |                     |  |  |  |  |

| Before Instruc<br>REG   | tion<br>= 1010 1                                                     | .011                                                                                                                                                                                                                                                                                                                                       |             |                     |  |  |  |  |

| After Instructio<br>REG | on<br>= 0101 0                                                       | 111                                                                                                                                                                                                                                                                                                                                        |             |                     |  |  |  |  |

| RRCF                                         | Rotate Right f through Carry                                                                                                                                                                                                                                             |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RRCF f[,d[,a]]                                                                                                                                                                                                                                          |  |  |  |  |

| Operands:                                    | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                    |  |  |  |  |

| Operation:                                   | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow C,$<br>$(C) \rightarrow dest < 7 >$                                                                                                                                                                    |  |  |  |  |

| Status Affected:                             | C, N, Z                                                                                                                                                                                                                                                                  |  |  |  |  |

| Encoding:                                    | 0011 00da ffff fff:                                                                                                                                                                                                                                                      |  |  |  |  |

|                                              | Flag. If 'd' is '0', the result is placed in<br>W. If 'd' is '1', the result is placed back<br>in register, 'f'. If 'a' is '0', the Access<br>Bank will be selected, overriding the<br>BSR value. If 'a' is '1', then the bank will<br>be selected as per the BSR value. |  |  |  |  |

|                                              | C register f                                                                                                                                                                                                                                                             |  |  |  |  |

| Words:                                       |                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                              | 1                                                                                                                                                                                                                                                                        |  |  |  |  |

| Words:<br>Cycles:                            |                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                              | 1                                                                                                                                                                                                                                                                        |  |  |  |  |

| Cycles:<br>Q Cycle Activity:                 | 1                                                                                                                                                                                                                                                                        |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1           | 1<br>1<br>Q2 Q3 Q4<br>Read Process Write to                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode | 1<br>1<br>2<br>Q2 Q3 Q4<br>Read Process Write to<br>register 'f' Data destinatio<br>RRCF REG, W                                                                                                                                                                          |  |  |  |  |

| XORWF                                           | Exclusive                                                                                   | Exclusive OR W with f                                                                                                                                                                                                                                                                                                           |                      |  |  |  |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|

| Syntax:                                         | [label] >                                                                                   | label] XORWF f [,d [,a]]                                                                                                                                                                                                                                                                                                        |                      |  |  |  |  |  |  |

| Operands:                                       | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                         | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                       |                      |  |  |  |  |  |  |

| Operation:                                      | (W) .XOR.                                                                                   | (W) .XOR. (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                |                      |  |  |  |  |  |  |

| Status Affected:                                | N, Z                                                                                        | N, Z                                                                                                                                                                                                                                                                                                                            |                      |  |  |  |  |  |  |

| Encoding:                                       | 0001                                                                                        | 10da ff:                                                                                                                                                                                                                                                                                                                        | ff ffff              |  |  |  |  |  |  |

| Description:                                    | register, 'f'.<br>stored in W<br>stored back<br>'0', the Acc<br>overriding t<br>then the ba | Exclusive OR the contents of W with<br>register, 'f'. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in the register, 'f'. If 'a' is<br>'0', the Access Bank will be selected,<br>overriding the BSR value. If 'a' is '1',<br>then the bank will be selected as per<br>the BSR value. |                      |  |  |  |  |  |  |

| Words:                                          | 1                                                                                           |                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |  |  |

| Cycles:                                         | 1                                                                                           |                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |  |  |

| Q Cycle Activity:                               |                                                                                             |                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |  |  |

| Q1                                              | Q2                                                                                          | Q3                                                                                                                                                                                                                                                                                                                              | Q4                   |  |  |  |  |  |  |

| Decode                                          | Read<br>register 'f'                                                                        | Process<br>Data                                                                                                                                                                                                                                                                                                                 | Write to destination |  |  |  |  |  |  |

| Example:                                        | XORWF 1                                                                                     | REG                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |  |  |

| Before Instruct<br>REG<br>W<br>After Instructio | = 0xAF<br>= 0xB5                                                                            |                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |  |  |

| REG<br>W                                        | = 0x1A<br>= 0xB5                                                                            |                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |  |  |

## 25.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 25.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 25.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.