Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data II.                   |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2331-i-sp |

TABLE 1-3: PIC18F4331/4431 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                                           | Pin Number    |    | Pin  | Buffer                      | Description                         |                                                                                                                                         |

|--------------------------------------------------------------------|---------------|----|------|-----------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                           | PDIP TQFP QFN |    | Туре | Туре                        | Description                         |                                                                                                                                         |

|                                                                    |               |    |      |                             |                                     | PORTA is a bidirectional I/O port.                                                                                                      |

| RA0/AN0<br>RA0<br>AN0                                              | 2             | 19 | 19   | I/O<br>I                    | TTL<br>Analog                       | Digital I/O.<br>Analog Input 0.                                                                                                         |

| RA1/AN1<br>RA1<br>AN1                                              | 3             | 20 | 20   | I/O<br>I                    | TTL<br>Analog                       | Digital I/O.<br>Analog Input 1.                                                                                                         |

| RA2/AN2/VREF-/CAP1/<br>INDX<br>RA2<br>AN2<br>VREF-<br>CAP1<br>INDX | 4             | 21 | 21   | I/O<br> <br> <br> <br> <br> | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O. Analog Input 2. A/D reference voltage (low) input. Input Capture Pin 1. Quadrature Encoder Interface index input pin.      |

| RA3/AN3/VREF+/<br>CAP2/QEA<br>RA3<br>AN3<br>VREF+<br>CAP2<br>QEA   | 5             | 22 | 22   | I/O<br> <br> <br> <br> <br> | TTL<br>Analog<br>Analog<br>ST<br>ST | Digital I/O. Analog Input 3. A/D reference voltage (high) input. Input Capture Pin 2. Quadrature Encoder Interface Channel A input pin. |

| RA4/AN4/CAP3/QEB<br>RA4<br>AN4<br>CAP3<br>QEB                      | 6             | 23 | 23   | I/O<br> <br> <br> <br>      | TTL<br>Analog<br>ST<br>ST           | Digital I/O. Analog Input 4. Input Capture Pin 3. Quadrature Encoder Interface Channel B input pin.                                     |

| RA5/AN5/LVDIN<br>RA5<br>AN5<br>LVDIN                               | 7             | 24 | 24   | I/O<br>I<br>I               | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog Input 5.<br>Low-Voltage Detect input.                                                                            |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output I = Input

ST = Schmitt Trigger input with CMOS levels

= Output P = Power

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL; RC7 is the alternate pin for SDO.

2: RD4 is the alternate pin for FLTA.

3: RD5 is the alternate pin for PWM4.

#### 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte (PCH register) contains the PC<15:8> bits and is not directly readable or writable.

Updates to the PCH register are performed through the PCLATH register. The upper byte is the PCU register and contains the bits, PC<20:16>. This register is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes to the PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of the PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

#### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, with the Stack Pointer initialized to 00000b after all Resets. There is no RAM associated with Stack Pointer, 00000b. This is only a Reset value. During a CALL type instruction, causing a push onto the stack, the Stack Pointer is first incremented and the RAM location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). During a RETURN type instruction, causing a pop from the stack, the contents of the RAM location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The stack space is not part of either program or data space. The Stack Pointer is readable and writable, and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from, the stack using the Top-of-Stack SFRs. Status bits indicate if the stack is full. has overflowed or underflowed.

#### 6.1.2.1 Top-of-Stack Access

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

#### 6.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. At Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to Section 23.1 "Configuration Bits" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

#### 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from 00h to FFh.

The EEPROM data memory is rated for high erase/ write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip-to-chip. Please refer to Parameter D122 (Table 26-1 in **Section 26.0** "Electrical Characteristics") for exact limits.

#### 7.1 EEADR

The Address register can address 256 bytes of data EEPROM.

#### 7.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 7-1) is the control register for data and program memory access. Control bit, EEPGD, determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either Flash program or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

Note: During normal operation, the WRERR bit is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset or a write operation was attempted improperly.

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 7.3 "Reading the Data EEPROM Memory"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1  | R/W-1  | U-0 | R/W-0  | R/W-0  | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|--------|--------|-----|--------|--------|

| INT2IP | INT1IP | _   | INT2IE | INT1IE | _   | INT2IF | INT1IF |

| bit 7  |        |     |        |        |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 INT2IP: INT2 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 INT1IP: INT1 External Interrupt Priority bit

1 = High priority0 = Low priority

bit 5 **Unimplemented:** Read as '0'

bit 4 INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt0 = Disables the INT2 external interrupt

bit 3 INT1IE: INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt

0 = Disables the INT1 external interrupt

bit 2 Unimplemented: Read as '0'

bit 1 INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared in software)

0 = The INT2 external interrupt did not occur

bit 0 INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared in software)

0 = The INT1 external interrupt did not occur

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

**Note:** On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

External interrupts, IN0, INT1 and INT2, are placed on RC3, RC4 and RC5 pins, respectively.

SSP alternate interface pins, SDI/SDA, SCK/SCL and SDO are placed on RC4, RC5 and RC7 pins, respectively.

These pins are multiplexed on PORTC and PORTD by using the SSPMX bit in the CONFIG3L register.

EUSART pins RX/DT and TX/CK are placed on RC7 and RC6 pins, respectively.

The alternate Timer5 external clock input, T5CKI, and the alternate TMR0 external clock input, T0CKI, are placed on RC3 and are multiplexed with the PORTD (RD0) pin using the EXCLKMX Configuration bit in CONFIG3H. Fault inputs to the 14-bit PWM module, FLTA and FLTB, are located on RC1 and RC2. FLTA input on RC1 is multiplexed with RD4 using the FLTAMX bit.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### **EXAMPLE 11-3: INITIALIZING PORTC**

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

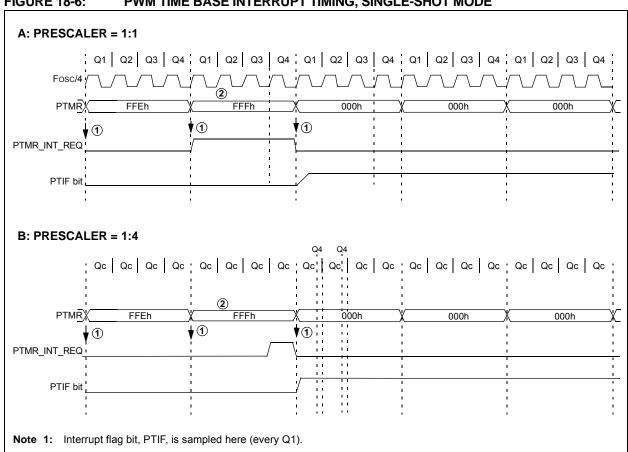

#### 18.4.2 INTERRUPTS IN SINGLE-SHOT MODE

When the PWM time base is in the Single-Shot mode (PTMOD<1:0> = 01), an interrupt event is generated when a match with the PTPER register occurs. The PWM Time Base register (PTMR) is reset to zero on the following input clock edge and the PTEN bit is cleared. The postscaler selection bits have no effect in this Timer mode.

#### INTERRUPTS IN CONTINUOUS 18.4.3 **UP/DOWN COUNT MODE**

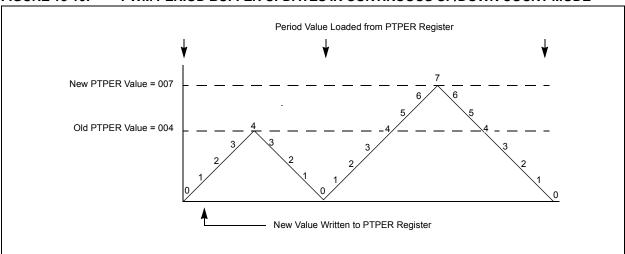

Continuous Up/Down Count mode (PTMOD<1:0> = 10), an interrupt event is generated each time the value of the PTMR register becomes zero and the PWM time base begins to count upwards. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events. Figure 18-7 shows the interrupts in Continuous Up/Down Count mode.

#### **FIGURE 18-6:** PWM TIME BASE INTERRUPT TIMING, SINGLE-SHOT MODE

2: PWM Time Base Period register, PTPER, is loaded with the value, FFFh, for this example.

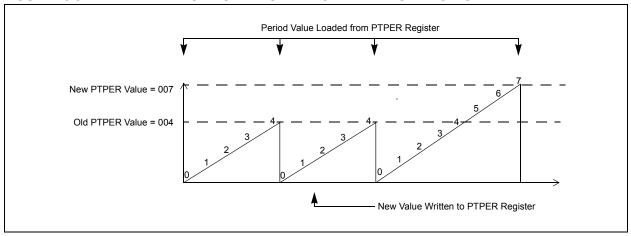

FIGURE 18-9: PWM PERIOD BUFFER UPDATES IN FREE-RUNNING MODE

#### FIGURE 18-10: PWM PERIOD BUFFER UPDATES IN CONTINUOUS UP/DOWN COUNT MODE

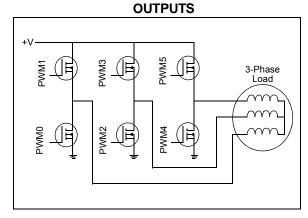

# 18.6.5 COMPLEMENTARY PWM OPERATION

The Complementary mode of PWM operation is useful to drive one or more power switches in half-bridge configuration as shown in Figure 18-16. This inverter topology is typical for a 3-phase induction motor, brushless DC motor or a 3-phase Uninterruptible Power Supply (UPS) control applications.

Each upper/lower power switch pair is fed by a complementary PWM signal. Dead time may be optionally inserted during device switching, where both outputs are inactive for a short period (see Section 18.7 "Dead-Time Generators").

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC0 register controls PWM1/PWM0 outputs

- PDC1 register controls PWM3/PWM2 outputs

- PDC2 register controls PWM5/PWM4 outputs

- PDC3 register controls PWM7/PWM6 outputs

PWM1/3/5/7 are the main PWMs that are controlled by the PDCx registers and PWM0/2/4/6 are the complemented outputs. When using the PWMs to control the half bridge, the odd numbered PWMs can be used to control the upper power switch and the even numbered PWMs used for the lower switches.

# FIGURE 18-16: TYPICAL LOAD FOR COMPLEMENTARY PWM

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON0 register. The PWM I/O pins are set to Complementary mode by default upon all kinds of device Resets.

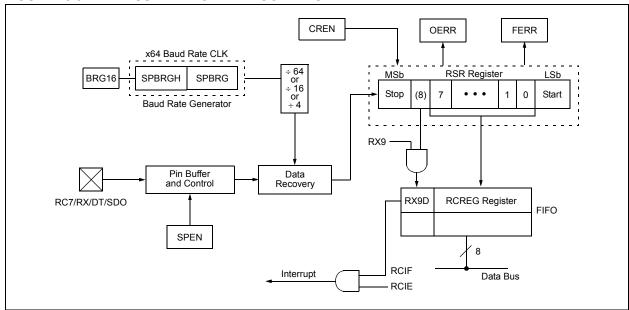

# 20.3.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 20-5. The data is received on the RC7/RX/DT/SDO pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 20.3.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### FIGURE 20-5: EUSART RECEIVE BLOCK DIAGRAM

To set up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit, BRGH (see Section 20.2 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

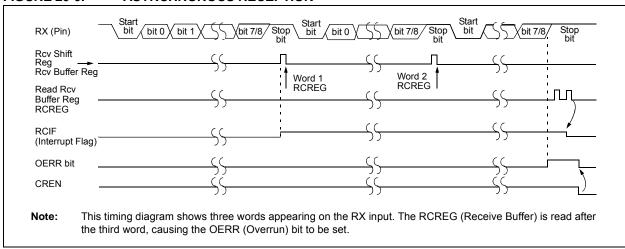

#### FIGURE 20-6: ASYNCHRONOUS RECEPTION

#### TABLE 20-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7                                         | Bit 6          | Bit 5       | Bit 4     | Bit 3 | Bit 2  | Bit 1                                        | Bit 0  | Reset Values on Page: |  |  |  |  |  |  |

|---------|-----------------------------------------------|----------------|-------------|-----------|-------|--------|----------------------------------------------|--------|-----------------------|--|--|--|--|--|--|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL      | TMR0IE      | INT0IE    | RBIE  | TMR0IF | INT0IF                                       | RBIF   | 54                    |  |  |  |  |  |  |

| PIR1    | _                                             | ADIF           | RCIF        | TXIF      | SSPIF | CCP1IF | TMR2IF                                       | TMR1IF | 57                    |  |  |  |  |  |  |

| PIE1    | _                                             | ADIE           | RCIE        | TXIE      | SSPIE | CCP1IE | TMR2IE                                       | TMR1IE | 57                    |  |  |  |  |  |  |

| IPR1    | _                                             | ADIP           | RCIP        | TXIP      | SSPIP | CCP1IP | TMR2IP                                       | TMR1IP | 57                    |  |  |  |  |  |  |

| RCSTA   | SPEN                                          | RX9            | SREN        | CREN      | ADDEN | FERR   | OERR                                         | RX9D   | 56                    |  |  |  |  |  |  |

| RCREG   | EUSART Re                                     | ceive Register | -           |           |       |        |                                              |        | 56                    |  |  |  |  |  |  |

| TXSTA   | CSRC                                          | TX9            | TXEN        | SYNC      | SENDB | BRGH   | TRMT                                         | TX9D   | 56                    |  |  |  |  |  |  |

| BAUDCON | _                                             | RCIDL          | _           | SCKP      | BRG16 | _      | WUE                                          | ABDEN  | 56                    |  |  |  |  |  |  |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |                |             |           |       |        |                                              |        | 56                    |  |  |  |  |  |  |

| SPBRG   | EUSART Ba                                     | ud Rate Gene   | rator Regis | ter Low B | yte   | •      | EUSART Baud Rate Generator Register Low Byte |        |                       |  |  |  |  |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

#### 21.1 Configuring the A/D Converter

The A/D Converter has two types of conversions, two modes of operation and eight different Sequencing modes. These features are controlled by the ACONV bit (ADCON0<5>), ACSCH bit (ADCON0<4>) and ACMOD<1:0> bits (ADCON0<3:2>). In addition, the A/D channels are divided into four groups as defined in the ADCHS register. Table 21-1 shows the sequence configurations as controlled by the ACSCH and ACMOD<1:0> bits.

#### 21.1.1 CONVERSION TYPE

Two types of conversions exist in the high-speed 10-bit A/D Converter module that are selected using the ACONV bit. Single-Shot mode allows a single conversion or sequence to be enabled when ACONV = 0. At the end of the sequence, the GO/DONE bit will be automatically cleared and the interrupt flag, ADIF, will be set. When using Single-Shot mode and configured for Simultaneous mode, STNM2, acquisition time must be used to ensure proper conversion of the analog input signals.

Continuous Loop mode allows the defined sequence to be executed in a continuous loop when ACONV = 1. In this mode, either the user can trigger the start of conversion by setting the  $GO/\overline{DONE}$  bit, or one of the A/D triggers can start the conversion. The interrupt flag, ADIF, is set based on the configuration of the bits, ADRS<1:0> (ADCON3<7:6>). In Simultaneous modes, STNM1 and STNM2 acquisition time must be configured to ensure proper conversion of the analog input signals.

#### 21.1.2 CONVERSION MODE

The ACSCH bit (ADCON0<4>) controls how many channels are used in the configured sequence. When clear, the A/D is configured for single channel conversion and will convert the group selected by the ACMOD<1:0> bits and the channel selected by the GxSEL<1:0> bits (ADCHS register). When ACSCH = 1, the A/D is configured for multiple channel conversion and the sequence is defined by ACMOD<1:0>.

TABLE 21-1: AUTO-CONVERSION SEQUENCE CONFIGURATIONS

| Mode                                      | ACSCH | ACMOD<1:0> | Description                                                                                                                                          |

|-------------------------------------------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-Channel Sequential Mode 1 (SEQM1)   | 1     | 00         | Groups A and B are sampled and converted sequentially.                                                                                               |

| Multi-Channel Sequential Mode 2 (SEQM2)   | 1     | 01         | Groups A, B, C and D are sampled and converted sequentially.                                                                                         |

| Multi-Channel Simultaneous Mode 1 (STNM1) | 1     | 10         | Groups A and B are sampled simultaneously and converted sequentially.                                                                                |

| Multi-Channel Simultaneous Mode 2 (STNM2) | 1     | 11         | Groups A and B are sampled simultaneously, then converted sequentially. Then, Group C and D are sampled simultaneously, then converted sequentially. |

| Single Channel Mode 1 (SCM1)              | 0     | 00         | Group A is sampled and converted.                                                                                                                    |

| Single Channel Mode 2 (SCM2)              | 0     | 01         | Group B is sampled and converted.                                                                                                                    |

| Single Channel Mode 3 (SCM3)              | 0     | 10         | Group C is sampled and converted.                                                                                                                    |

| Single Channel Mode 4 (SCM4)              | 0     | 11         | Group D is sampled and converted.                                                                                                                    |

Externally Generated Trip Point Vdd Vdd LVDL<3:0> LVDCON Register LVDIN VDIRMAG LVDEN LVDIN Set LVDIF 16-to-1 MUX LVDEN Internal Voltage Reference **BOREN**

**FIGURE 22-1:** LVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

#### REGISTER 23-13: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2331/2431/4331/4431 DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed U = Unchanged from programmed state

bit 7-5 **DEV<2:0>:** Device ID bits

These bits are used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.

000 = PIC18F4331 001 = PIC18F4431 100 = PIC18F2331 101 = PIC18F2431

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to indicate the device revision.

#### REGISTER 23-14: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2331/2431/4331/4431 DEVICES

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed U = Unchanged from programmed state

bit 7-0 **DEV<10:3>:** Device ID bits<sup>(1)</sup>

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number

0000 0101 = PIC18F2331/2431/4331/4431 devices

**Note 1:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

| LFSR             | Load FSR                                                                          |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] LFSR f,k                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 4095 \end{array}$              |  |  |  |  |  |

| Operation:       | $k \to FSRf$                                                                      |  |  |  |  |  |

| Status Affected: | None                                                                              |  |  |  |  |  |

| Encoding:        | 1110 1110 00ff k <sub>11</sub> kkk<br>1111 0000 k <sub>7</sub> kkk kkkk           |  |  |  |  |  |

| Description:     | The 12-bit literal 'k' is loaded into the file select register pointed to by 'f'. |  |  |  |  |  |

| Words:           | 2                                                                                 |  |  |  |  |  |

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4            |

|--------|--------------|---------|---------------|

| Decode | Read literal | Process | Write         |

|        | 'k' MSB      | Data    | literal 'k'   |

|        |              |         | MSB to        |

|        |              |         | FSRfH         |

| Decode | Read literal | Process | Write literal |

|        | 'k' LSB      | Data    | 'k' to FSRfL  |

Example: LFSR 2, 0x3AB

After Instruction

FSR2H = 0x03 FSR2L = 0xAB

| MΟ\          | /F             | Move f                                                                                                                                        |                                                                                    |                                                                    |                                                                        |  |  |

|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|--|--|

| Synta        | ax:            | [label] N                                                                                                                                     | 10VF f                                                                             | [,d [,a]]                                                          |                                                                        |  |  |

| Oper         | ands:          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                |                                                                                    |                                                                    |                                                                        |  |  |

| Oper         | ration:        | $f \to dest \\$                                                                                                                               |                                                                                    |                                                                    |                                                                        |  |  |

| Statu        | s Affected:    | N, Z                                                                                                                                          |                                                                                    |                                                                    |                                                                        |  |  |

| Enco         | oding:         | 0101                                                                                                                                          | 00da                                                                               | ffff                                                               | ffff                                                                   |  |  |

| Description: |                | to a destina<br>status of 'd'<br>placed in W<br>placed back<br>can be any<br>If 'a' is '0', t<br>selected, o'<br>'a' = 1, then<br>per the BSI | '. If 'd' is ' '. If 'd' is ' k in regis  where in  the Access verriding  the bank | 0', the res '1', the res ter, 'f'. Loc the 256-b ss Bank w the BSR | sult is<br>sult is<br>cation, 'f',<br>yte bank.<br>ill be<br>value. If |  |  |

| Word         | ds:            | 1                                                                                                                                             | 1                                                                                  |                                                                    |                                                                        |  |  |

| Cycle        | es:            | 1                                                                                                                                             | 1                                                                                  |                                                                    |                                                                        |  |  |

| QC           | ycle Activity: |                                                                                                                                               |                                                                                    |                                                                    |                                                                        |  |  |

|              | Q1             | Q2                                                                                                                                            | Q3                                                                                 |                                                                    | Q4                                                                     |  |  |

|              | Decode         | Read<br>register 'f'                                                                                                                          | Proce<br>Data                                                                      |                                                                    | Write<br>W                                                             |  |  |

Example:

MOVF

REG, W

Before Instruction

REG = 0x22

W = 0xFF

After Instruction

REG = 0x22W = 0x22

#### XORWF Exclusive OR W with f

Syntax: [ label ] XORWF f [,d [,a]]

$\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$

Operation: (W) .XOR. (f)  $\rightarrow$  dest

Status Affected: N, Z

Operands:

Encoding: 0001 10da ffff ffff

Description: Exclusive OR the contents of W with

register, 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in the register, 'f'. If 'a' is '0', the Access Bank will be selected, overriding the BSR value. If 'a' is '1', then the bank will be selected as per

the BSR value.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: XORWF REG

Before Instruction

REG = 0xAFW = 0xB5

After Instruction

REG = 0x1A W = 0xB5

# 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2331/2431/4331/4431 (Industrial, Extended) PIC18LF2331/2431/4331/4431 (Industrial) (Continued)

| PIC18LF2331/2431/4331/4431<br>(Industrial)          |                           |      |                                                                                                                                                                                                                                       | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for industrial |        |                        |                                                               |  |  |

|-----------------------------------------------------|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|------------------------|---------------------------------------------------------------|--|--|

| PIC18F2331/2431/4331/4431<br>(Industrial, Extended) |                           |      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                                                                                                                 |        |                        |                                                               |  |  |

| Param<br>No. Device                                 |                           |      | Max Units Conditions                                                                                                                                                                                                                  |                                                                                                                 |        |                        |                                                               |  |  |

|                                                     | Supply Current (IDD)(2,3) |      |                                                                                                                                                                                                                                       |                                                                                                                 |        |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 8    | 40                                                                                                                                                                                                                                    | μА                                                                                                              | -40°C  |                        |                                                               |  |  |

|                                                     |                           | 9    | 40                                                                                                                                                                                                                                    | μА                                                                                                              | +25°C  | V <sub>DD</sub> = 2.0V |                                                               |  |  |

|                                                     |                           | 11   | 40                                                                                                                                                                                                                                    | μА                                                                                                              | +85°C  |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 25   | 68                                                                                                                                                                                                                                    | μА                                                                                                              | -40°C  |                        |                                                               |  |  |

|                                                     |                           | 25   | 68                                                                                                                                                                                                                                    | μА                                                                                                              | +25°C  | VDD = 3.0V             | Fosc = 31 kHz<br>(RC_RUN mode,<br>Internal oscillator source) |  |  |

|                                                     |                           | 20   | 68                                                                                                                                                                                                                                    | μА                                                                                                              | +85°C  | VDD = 5.0V             |                                                               |  |  |

|                                                     | All devices               | 55   | 180                                                                                                                                                                                                                                   | μА                                                                                                              | -40°C  |                        |                                                               |  |  |

|                                                     |                           | 55   | 180                                                                                                                                                                                                                                   | μА                                                                                                              | +25°C  |                        |                                                               |  |  |

|                                                     |                           | 50   | 180                                                                                                                                                                                                                                   | μА                                                                                                              | +85°C  |                        |                                                               |  |  |

|                                                     |                           | 0.25 | 1                                                                                                                                                                                                                                     | mA                                                                                                              | +125°C |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 140  | 220                                                                                                                                                                                                                                   | μА                                                                                                              | -40°C  | V <sub>DD</sub> = 2.0V |                                                               |  |  |

|                                                     |                           | 145  | 220                                                                                                                                                                                                                                   | μА                                                                                                              | +25°C  |                        |                                                               |  |  |

|                                                     |                           | 155  | 220                                                                                                                                                                                                                                   | μА                                                                                                              | +85°C  |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 215  | 330                                                                                                                                                                                                                                   | μΑ                                                                                                              | -40°C  |                        | 1                                                             |  |  |

|                                                     |                           | 225  | 330                                                                                                                                                                                                                                   | μΑ                                                                                                              | +25°C  | VDD = 3.0V             | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,                         |  |  |

|                                                     |                           | 235  | 330                                                                                                                                                                                                                                   | μΑ                                                                                                              | +85°C  |                        | Internal oscillator source)                                   |  |  |

|                                                     | All devices               | 385  | 550                                                                                                                                                                                                                                   | μΑ                                                                                                              | -40°C  |                        |                                                               |  |  |

|                                                     |                           | 390  | 550                                                                                                                                                                                                                                   | μΑ                                                                                                              | +25°C  | VDD = 5.0V             |                                                               |  |  |

|                                                     |                           | 405  | 550                                                                                                                                                                                                                                   | μА                                                                                                              | +85°C  | VDD = 5.0 V            |                                                               |  |  |

|                                                     |                           | 0.7  | 2.8                                                                                                                                                                                                                                   | mA                                                                                                              | +125°C |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 410  | 600                                                                                                                                                                                                                                   | μА                                                                                                              | -40°C  |                        |                                                               |  |  |

|                                                     |                           | 425  | 600                                                                                                                                                                                                                                   | μА                                                                                                              | +25°C  | VDD = 2.0V             |                                                               |  |  |

|                                                     |                           | 435  | 600                                                                                                                                                                                                                                   | μА                                                                                                              | +85°C  |                        |                                                               |  |  |

|                                                     | PIC18LF2X31/4X31          | 650  | 900                                                                                                                                                                                                                                   | μΑ                                                                                                              | -40°C  | _                      | Fosc = 4 MHz<br>(RC_RUN mode,<br>Internal oscillator source)  |  |  |

|                                                     |                           | 670  | 900                                                                                                                                                                                                                                   | μΑ                                                                                                              | +25°C  | VDD = 3.0V             |                                                               |  |  |

|                                                     |                           | 680  | 900                                                                                                                                                                                                                                   | μΑ                                                                                                              | +85°C  |                        |                                                               |  |  |

|                                                     | All devices               | 1.2  | 1.8                                                                                                                                                                                                                                   | mA                                                                                                              | -40°C  | _                      |                                                               |  |  |

|                                                     |                           | 1.2  | 1.8                                                                                                                                                                                                                                   | mA                                                                                                              | +25°C  | VDD = 5.0V             |                                                               |  |  |

|                                                     |                           | 1.2  | 1.8                                                                                                                                                                                                                                   | mA                                                                                                              | +85°C  | J VDD 0.0V             |                                                               |  |  |

|                                                     |                           | 2.2  | 6                                                                                                                                                                                                                                     | mA                                                                                                              | +125°C |                        |                                                               |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in  $k\Omega$ .

- 4: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

TABLE 26-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                           | Min       | Тур  | Max       | Units | Conditions                                    |

|---------------|--------|----------------------------------------------------------|-----------|------|-----------|-------|-----------------------------------------------|

| 30            | TMCL   | MCLR Pulse Width (low)                                   | 2         |      | _         | μS    |                                               |

| 31            | TWDT   | Watchdog Timer Time-out Period (no postscaler)           | _         | 4.00 | _         | ms    |                                               |

| 32            | Tost   | Oscillation Start-up Timer Period                        | 1024 Tosc | _    | 1024 Tosc | _     | Tosc = OSC1 period                            |

| 33            | TPWRT  | Power-up Timer Period                                    | _         | 65.5 | _         | ms    |                                               |

| 34            | Tıoz   | I/O High-impedance from MCLR Low or Watchdog Timer Reset | _         | 2    | _         | μS    |                                               |

| 35            | TBOR   | Brown-out Reset Pulse Width                              | 200       | _    | _         | μS    | V <sub>DD</sub> ≤ B <sub>VDD</sub> (see D005) |

| 36            | TIRVST | Time for Internal Reference<br>Voltage to become Stable  | _         | 20   | 50        | μS    |                                               |

| 37            | TLVD   | Low-Voltage Detect Pulse Width                           | 200       | _    | _         | μS    | $VDD \le VLVD$                                |

| 38            | TCSD   | CPU Start-up Time                                        | _         | 10   | _         | μS    |                                               |

| 39            | TIOBST | Time for INTOSC to Stabilize                             | _         | 1    | _         | ms    |                                               |

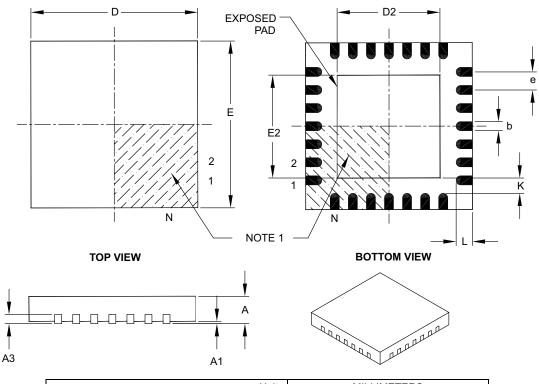

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS |      |      |  |

|------------------------|----------|-------------|------|------|--|

| Dimension              | n Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | N        | 28          |      |      |  |

| Pitch                  | е        | 0.65 BSC    |      |      |  |

| Overall Height         | Α        | 0.80        | 0.90 | 1.00 |  |

| Standoff               | A1       | 0.00        | 0.02 | 0.05 |  |

| Contact Thickness      | A3       | 0.20 REF    |      |      |  |

| Overall Width          | Е        | 6.00 BSC    |      |      |  |

| Exposed Pad Width      | E2       | 3.65        | 3.70 | 4.20 |  |

| Overall Length         | D        | 6.00 BSC    |      |      |  |

| Exposed Pad Length     | D2       | 3.65        | 3.70 | 4.20 |  |

| Contact Width          | b        | 0.23        | 0.30 | 0.35 |  |

| Contact Length         | L        | 0.50        | 0.55 | 0.70 |  |

| Contact-to-Exposed Pad | K        | 0.20        | _    | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

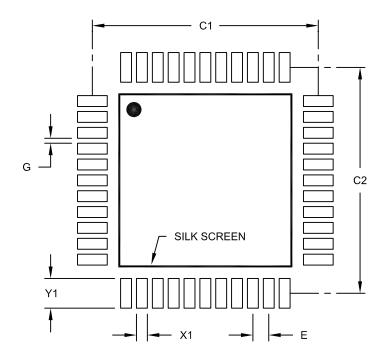

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension Limits         |             | MIN      | NOM   | MAX  |

| Contact Pitch            | Е           | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X44)  | X1          |          |       | 0.55 |

| Contact Pad Length (X44) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.25     |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A

# APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC16C74A to a PIC16C74B.

**Not Applicable**

# APPENDIX D: MIGRATION FROM BASELINE TO ENHANCED DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to an enhanced MCU device (i.e., PIC18FXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

**Not Currently Available**