Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 9x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4331-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

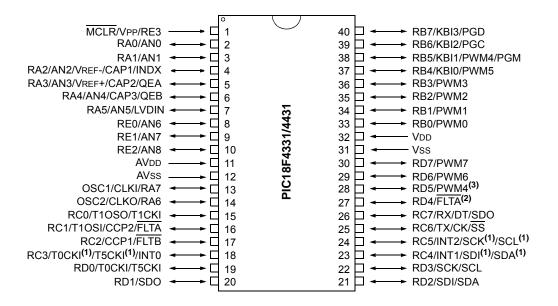

#### Pin Diagrams (Continued)

Note 1: RC3 is the alternate pin for T0CKI/T5CKI; RC4 is the alternate pin for SDI/SDA; RC5 is the alternate pin for SCK/SCL.

- 2: RD4 is the alternate pin for  $\overline{\text{FLTA}}$ .

- 3: RD5 is the alternate pin for PWM4.

TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets WDT Reset RESET Instruction Stack Resets | Wake-up via WDT<br>or Interrupt |           |                          |

|----------|--------------------|------|------------------------------------|------------------------------------------------------|---------------------------------|-----------|--------------------------|

| TOSU     | 2331               | 2431 | 4331                               | 4431                                                 | 0 0000                          | 0 0000    | 0 uuuu <b>(3)</b>        |

| TOSH     | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu <sup>(3)</sup> |

| TOSL     | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu <sup>(3)</sup> |

| STKPTR   | 2331               | 2431 | 4331                               | 4431                                                 | 00-0 0000                       | uu-0 0000 | uu-u uuuu <sup>(3)</sup> |

| PCLATU   | 2331               | 2431 | 4331                               | 4431                                                 | 0 0000                          | 0 0000    | u uuuu                   |

| PCLATH   | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu                |

| PCL      | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | PC + 2 <sup>(2)</sup>    |

| TBLPTRU  | 2331               | 2431 | 4331                               | 4431                                                 | 00 0000                         | 00 0000   | uu uuuu                  |

| TBLPTRH  | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu                |

| TBLPTRL  | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu                |

| TABLAT   | 2331               | 2431 | 4331                               | 4431                                                 | 0000 0000                       | 0000 0000 | uuuu uuuu                |

| PRODH    | 2331               | 2431 | 4331                               | 4431                                                 | xxxx xxxx                       | uuuu uuuu | uuuu uuuu                |

| PRODL    | 2331               | 2431 | 4331                               | 4431                                                 | xxxx xxxx                       | uuuu uuuu | uuuu uuuu                |

| INTCON   | 2331               | 2431 | 4331                               | 4431                                                 | 0000 000x                       | 0000 000u | uuuu uuuu <sup>(1)</sup> |

| INTCON2  | 2331               | 2431 | 4331                               | 4431                                                 | 1111 -1-1                       | 1111 -1-1 | uuuu -u-u <sup>(1)</sup> |

| INTCON3  | 2331               | 2431 | 4331                               | 4431                                                 | 11-0 0-00                       | 11-0 0-00 | uu-u u-uu <sup>(1)</sup> |

| INDF0    | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| POSTINC0 | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| POSTDEC0 | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| PREINC0  | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| PLUSW0   | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| FSR0H    | 2331               | 2431 | 4331                               | 4431                                                 | xxxx                            | uuuu      | uuuu                     |

| FSR0L    | 2331               | 2431 | 4331                               | 4431                                                 | xxxx xxxx                       | uuuu uuuu | uuuu uuuu                |

| WREG     | 2331               | 2431 | 4331                               | 4431                                                 | xxxx xxxx                       | uuuu uuuu | uuuu uuuu                |

| INDF1    | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| POSTINC1 | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| POSTDEC1 | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| PREINC1  | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

| PLUSW1   | 2331               | 2431 | 4331                               | 4431                                                 | N/A                             | N/A       | N/A                      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-2 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- **6:** Bit 3 of PORTE and LATE are enabled if MCLR functionality is disabled. When not enabled as the PORTE pin, they are disabled and read as '0'. The 28-pin devices do not have only RE3 implemented.

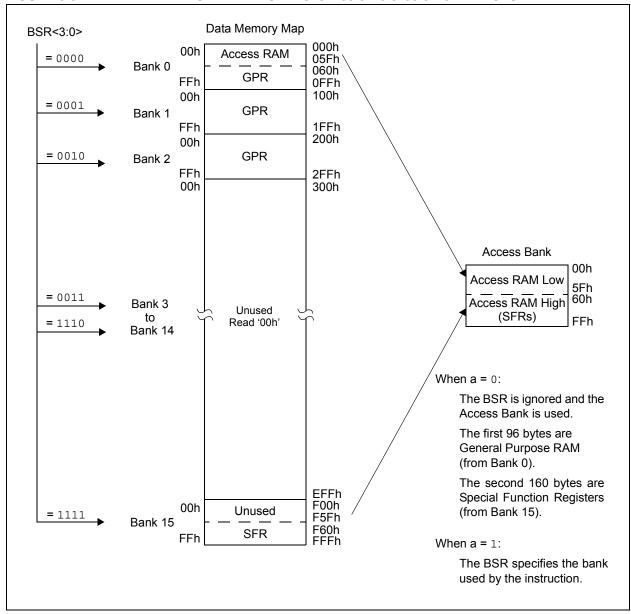

#### 6.5 Data Memory Organization

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4,096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. PIC18F2331/2431/4331/4431 devices implement all 16 banks.

Figure 6-6 shows the data memory organization for the PIC18F2331/2431/4331/4431 devices. The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 6.5.2 "Access Bank"** provides a detailed description of the Access RAM.

FIGURE 6-6: DATA MEMORY MAP FOR PIC18F2331/2431/4331/4431 DEVICES

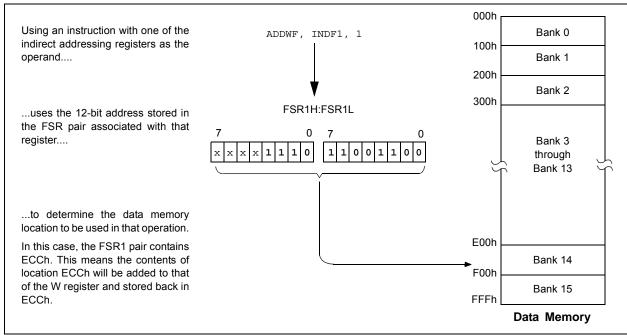

# 6.7.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands: INDF0 through INDF2. These can be thought of as "virtual" registers; they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

# 6.7.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

FIGURE 6-7: INDIRECT ADDRESSING

# 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

**Note:** On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

External interrupts, IN0, INT1 and INT2, are placed on RC3, RC4 and RC5 pins, respectively.

SSP alternate interface pins, SDI/SDA, SCK/SCL and SDO are placed on RC4, RC5 and RC7 pins, respectively.

These pins are multiplexed on PORTC and PORTD by using the SSPMX bit in the CONFIG3L register.

EUSART pins RX/DT and TX/CK are placed on RC7 and RC6 pins, respectively.

The alternate Timer5 external clock input, T5CKI, and the alternate TMR0 external clock input, T0CKI, are placed on RC3 and are multiplexed with the PORTD (RD0) pin using the EXCLKMX Configuration bit in CONFIG3H. Fault inputs to the 14-bit PWM module, FLTA and FLTB, are located on RC1 and RC2. FLTA input on RC1 is multiplexed with RD4 using the FLTAMX bit.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### **EXAMPLE 11-3: INITIALIZING PORTC**

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

#### 12.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing the T0CS bit. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In Counter mode, Timer0 will increment, either on every rising or falling edge of pin, RC3/T0CKI/T5CKI/INT0. The incrementing edge is determined by the Timer0 Source Edge Select bit (T0SE). Clearing the T0SE bit selects the rising edge.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 12.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not readable or writable.

The PSA and T0PS<2:0> bits determine the prescaler assignment and prescale ratio.

Clearing bit, PSA, will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF  $\,$  TMR0 ,  $\,$  MOVWF  $\,$  TMR0 ,  $\,$  BSF  $\,$  TMR0 ,  $\,$  x..., etc.) will clear the prescaler count.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

# 12.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution).

#### 12.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF bit. The interrupt can be masked by clearing the TMR0IE bit. The TMR0IF bit must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep mode, since the timer requires clock cycles, even when T0CS is set.

# 12.4 16-Bit Mode Timer Reads and Writes

TMR0H is not the high byte of the timer/counter in 16-bit mode, but is actually a buffered version of the high byte of Timer0 (refer to Figure 12-2). The high byte of the Timer0 counter/timer is not directly readable nor writable. TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid due to a rollover between successive reads of the high and low byte.

A write to the high byte of Timer0 must also take place through the TMR0H Buffer register. Timer0 high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

TABLE 12-1: REGISTERS ASSOCIATED WITH TIMERO

| Name   | Bit 7                     | Bit 6                 | Bit 5   | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0 | Reset Values on Page: |

|--------|---------------------------|-----------------------|---------|-------------|------------|--------|--------|-------|-----------------------|

| TMR0L  | Timer0 Regis              |                       | 55      |             |            |        |        |       |                       |

| TMR0H  | Timer0 Register High Byte |                       |         |             |            |        |        |       |                       |

| INTCON | GIE/GIEH                  | PEIE/GIEL             | TMR0IE  | INT0IE      | RBIE       | TMR0IF | INT0IF | RBIF  | 54                    |

| T0CON  | TMR00N                    | T016BIT               | T0CS    | 55          |            |        |        |       |                       |

| TRISA  | TRISA7 <sup>(1)</sup>     | TRISA6 <sup>(1)</sup> | PORTA D | ata Directi | on Registe | er     |        |       | 57                    |

Legend: Shaded cells are not used by Timer0.

Note 1: RA6 and RA7 are enabled as I/O pins depending on the oscillator mode selected in Configuration Word 1H.

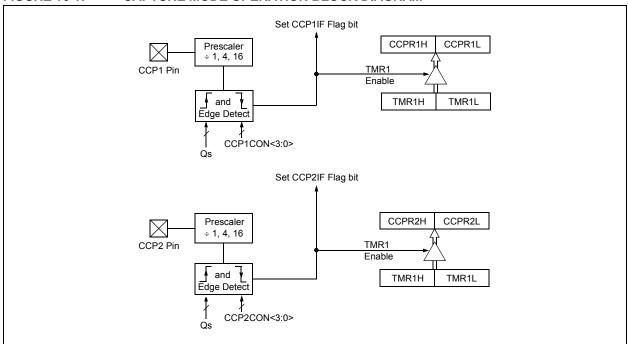

#### 16.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- · every falling edge

- every rising edge

- · every 4th rising edge

- · every 16th rising edge

The event is selected by control bits, CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 16.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### 16.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode to be used with the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 16.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 16.3.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M<3:0>. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; Turn CCP module off |

|-------|-------------|-----------------------|

| MOVLW | NEW_CAPT_PS | ; Load WREG with the  |

|       |             | ; new prescaler mode  |

|       |             | ; value and CCP ON    |

| MOVWF | CCP1CON     | ; Load CCP1CON with   |

|       |             | ; this value          |

|       |             |                       |

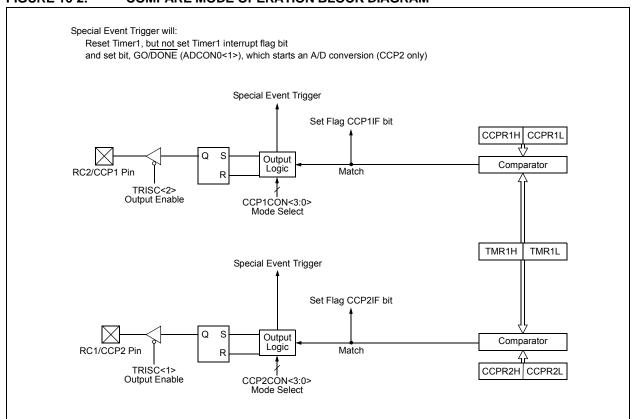

#### FIGURE 16-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 16.4 Compare Mode

In Compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 (RC1/CCP2) pin:

- · is driven high

- · is driven low

- toggles output (high-to-low or low-to-high)

- remains unchanged (interrupt only)

The action on the pin is based on the value of control bits, CCP1M<3:0> (CCP2M<3:0>). At the same time, interrupt flag bit CCP1IF (CCP2IF) is set.

#### 16.4.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISC bit.

Note:

Clearing the CCPxCON register will force the RC1 or RC2 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 16.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.4.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 16.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP2 resets the TMR1 register pair. Additionally, the CCP2 Special Event Trigger will start an A/D conversion if the A/D module is enabled.

Note:

The Special Event Trigger from the CCP2 module will not set the Timer1 interrupt flag bit.

#### FIGURE 16-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 17.2.2 QEI MODES

Position measurement resolution depends on how often the Position Counter register, POSCNT, is incremented. There are two QEI Update modes to measure the rotor's position: QEI x2 and QEI x4.

TABLE 17-4: QEI MODES

| QEIM<2:0> | Mode/<br>Reset                | Description                                                                           |

|-----------|-------------------------------|---------------------------------------------------------------------------------------|

| 000       |                               | QEI disabled. <sup>(1)</sup>                                                          |

| 001       | x2 update/<br>index pulse     | Two clocks per QEA pulse. INDX resets POSCNT.                                         |

| 010       | x2 update/<br>period<br>match | Two clocks per QEA pulse. POSCNT is reset by the period match (MAXCNT).               |

| 011       | _                             | Unused.                                                                               |

| 100       | _                             | Unused.                                                                               |

| 101       | x4 update/<br>index pulse     | Four clocks per QEA and QEB pulse pair. INDX resets POSCNT.                           |

| 110       | x4 update/<br>period<br>match | Four clocks per QEA and QEB pulse pair. POSCNT is reset by the period match (MAXCNT). |

| 111       | _                             | Unused.                                                                               |

**Note 1:** QEI module is disabled. The position counter and the velocity measurement functions are fully disabled in this mode.

#### 17.2.2.1 QEI x2 Update Mode

QEI x2 Update mode is selected by setting the QEI Mode Select bits (QEIM<2:0>) to '001' or '010'. In this mode, the QEI logic detects every edge on the QEA input only. Every rising and falling edge on the QEA signal clocks the position counter.

The position counter can be reset by either an input on the INDX pin (QEIM<2:0> = 001), or by a period match, even when the POSCNT register pair equals MAXCNT (QEIM<2:0> = 010).

#### 17.2.2.2 QEI x4 Update Mode

QEI x4 Update mode provides for a finer resolution of the rotor position, since the counter increments or decrements more frequently for each QEA/QEB input pulse pair than in QEI x2 mode. This mode is selected by setting the QEI mode select bits to '101' or '110'. In QEI x4, the phase measurement is made on the rising and the falling edges of both QEA and QEB inputs. The position counter is clocked on every QEA and QEB edge.

Like QEI x2 mode, the position counter can be reset by an input on the pin (QEIM<2:0> = 101), or by the period match event (QEIM<2:0> = 010).

#### 17.2.3 QEI OPERATION

The Position Counter register pair (POSCNTH: POSCNTL) acts as an integrator, whose value is proportional to the position of the sensor rotor that corresponds to the number of active edges detected. POSCNT can either increment or decrement, depending on a number of selectable factors which are decoded by the QEI logic block. These include the Count mode selected, the phase relationship of QEA to QEB ("lead/lag"), the direction of rotation and if a Reset event occurs. The logic is detailed in the sections that follow.

#### 17.2.3.1 Edge and Phase Detect

In the first step, the active edges of QEA and QEB are detected, and the phase relationship between them is determined. The position counter is changed based on the selected QEI mode.

In QEI x2 Update mode, the position counter increments or decrements on every QEA edge based on the phase relationship of the QEA and QEB signals.

In QEI x4 Update mode, the position counter increments or decrements on every QEA and QEB edge based on the phase relationship of the QEA and QEB signals. For example, if QEA leads QEB, the position counter is incremented by '1'. If QEB lags QEA, the position counter is decremented by '1'.

#### 17.2.3.2 Direction of Count

The QEI control logic generates a signal that sets the UP/DOWN bit (QEICON<5>); this, in turn, determines the direction of the count. When QEA leads QEB, UP/DOWN is set (= 1) and the position counter increments on every active edge. When QEA lags QEB, UP/DOWN is cleared and the position counter decrements on every active edge.

TABLE 17-5: DIRECTION OF ROTATION

| Current         | P   | Previous Signal<br>Detected |     |      |                               |  |  |  |

|-----------------|-----|-----------------------------|-----|------|-------------------------------|--|--|--|

| Signal Detected | Ris | sing                        | Fal | ling | Pos.<br>Cntrl. <sup>(1)</sup> |  |  |  |

|                 | QEA | QEB                         | QEA | QEB  |                               |  |  |  |

| QEA Rising      |     |                             |     | Х    | INC                           |  |  |  |

|                 |     | Х                           |     |      | DEC                           |  |  |  |

| QEA Falling     |     |                             |     | Х    | DEC                           |  |  |  |

|                 |     | Х                           |     |      | INC                           |  |  |  |

| QEB Rising      | Х   |                             |     |      | INC                           |  |  |  |

|                 |     |                             | Х   |      | DEC                           |  |  |  |

| QEB Falling     |     |                             | Х   |      | INC                           |  |  |  |

|                 | Х   |                             |     |      | DEC                           |  |  |  |

Note 1: When UP/DOWN = 1, the position counter is incremented. When UP/DOWN = 0, the position counter is decremented.

PTMR Register PTMR Clock Timer Reset Up/Down Zero Match Comparator Timer ➤ PTDIR Direction Period Match Comparator Control **Duty Cycle Load** PTMOD1 **PTPER** Period Load PTPER Buffer Update Disable (UDIS) -Zero Match -Period Match Clock PTMOD1 - PTMR Clock Control PTMOD0 Prescaler 1:1, 1:4, 1:16, 1:64 Fosc/4 **PTEN** Postscaler 1:1-1:16 Zero Match Interrupt PTIF Control Period Match PTMOD1 PTMOD0

FIGURE 18-4: PWM TIME BASE BLOCK DIAGRAM

The PWM time base can be configured for four different modes of operation:

- · Free-Running mode

- · Single-Shot mode

- · Continuous Up/Down Count mode

- Continuous Up/Down Count mode with interrupts for double updates

These four modes are selected by the PTMOD<1:0> bits in the PTCON0 register. The Free-Running mode produces edge-aligned PWM generation. The Continuous Up/Down Count modes produce center-aligned PWM generation. The Single-Shot mode allows the PWM module to support pulse control of certain Electronically Commutated Motors (ECMs) and produces edge-aligned operation.

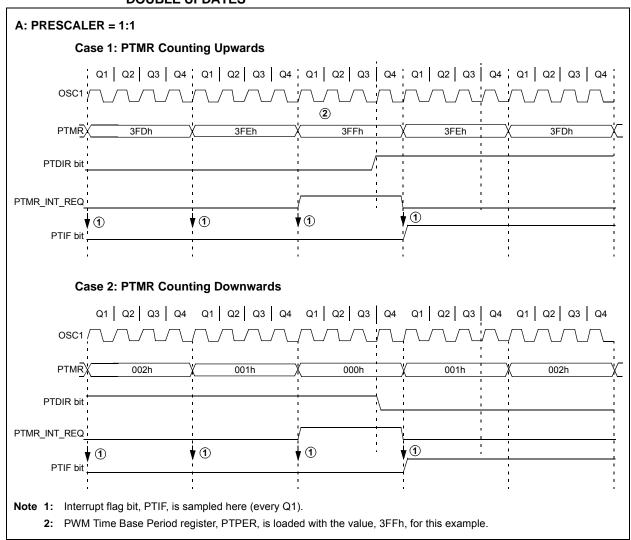

# 18.4.4 INTERRUPTS IN DOUBLE UPDATE MODE

This mode is available in Continuous Up/Down Count mode. In the Double Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero and each time the PTMR matches with PTPER register. Figure 18-8 shows the interrupts in Continuous Up/Down Count mode with double updates.

The Double Update mode provides two additional functions to the user in Center-Aligned mode.

- The control loop bandwidth is doubled because the PWM duty cycles can be updated twice per period.

- Asymmetrical center-aligned PWM waveforms can be generated, which are useful for minimizing output waveform distortion in certain motor control applications.

Note: Do not change the PTMOD bits while PTEN is active; it will yield unexpected results. To change the PWM Timer mode of operation, first clear the PTEN bit, load the PTMOD bits with the required data and then set PTEN.

# FIGURE 18-8: PWM TIME BASE INTERRUPT, CONTINUOUS UP/DOWN COUNT MODE WITH DOUBLE UPDATES

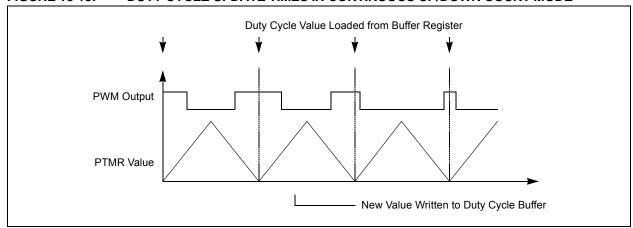

#### 18.6.2 DUTY CYCLE REGISTER BUFFERS

The four PWM Duty Cycle registers are double-buffered to allow glitchless updates of the PWM outputs. For each duty cycle block, there is a Duty Cycle Buffer register that is accessible by the user and a second Duty Cycle register that holds the actual compare value used in the present PWM period.

In Edge-Aligned PWM Output mode, a new duty cycle value will be updated whenever a PTMR match with the PTPER register occurs and PTMR is reset as shown in Figure 18-12. Also, the contents of the duty cycle buffers are automatically loaded into the Duty Cycle registers when the PWM time base is disabled (PTEN = 0).

When the PWM time base is in the Continuous Up/Down Count mode, new duty cycle values will be updated when the value of the PTMR register is zero and the PWM time base begins to count upwards. The contents of the duty cycle buffers are automatically loaded into the Duty Cycle registers when the PWM time base is disabled (PTEN = 0). Figure 18-13 shows the timings when the duty cycle update occurs for the Continuous Up/Down Count mode. In this mode, up to one entire PWM period is available for calculating and loading the new PWM duty cycle before changes take effect.

When the PWM time base is in the Continuous Up/Down Count mode with double updates, new duty cycle values will be updated when the value of the PTMR register is zero and when the value of the PTMR register matches the value in the PTPER register. The contents of the duty cycle buffers are automatically loaded into the Duty Cycle registers during both of the previously described conditions. Figure 18-14 shows the duty cycle updates for Continuous Up/Down Count mode with double updates. In this mode, only up to half of a PWM period is available for calculating and loading the new PWM duty cycle before changes take effect.

#### 18.6.3 EDGE-ALIGNED PWM

Edge-aligned PWM signals are produced by the module when the PWM time base is in the Free-Running mode or the Single-Shot mode. For edge-aligned PWM outputs, the output for a given PWM channel has a period specified by the value loaded in PTPER and a duty cycle specified by the appropriate Duty Cycle register (see Figure 18-12). The PWM output is driven active at the beginning of the period (PTMR = 0) and is driven inactive when the value in the Duty Cycle register matches PTMR. A new cycle is started when PTMR matches the PTPER as explained in the PWM period section.

If the value in a particular Duty Cycle register is zero, then the output on the corresponding PWM pin will be inactive for the entire PWM period. In addition, the output on the PWM pin will be active for the entire PWM period if the value in the Duty Cycle register is greater than the value held in the PTPER register.

PTPER - PTMR (old) Value PDCx (new) O - Duty Cycle Active at Beginning of Period

FIGURE 18-12: EDGE-ALIGNED PWM

FIGURE 18-13: DUTY CYCLE UPDATE TIMES IN CONTINUOUS UP/DOWN COUNT MODE

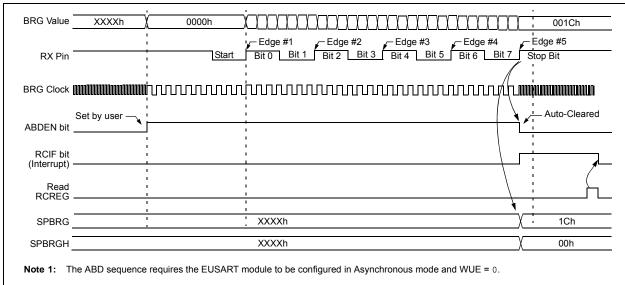

#### 20.2.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 20-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Detect must receive a byte with the value of 55h (ASCII "U", which is also the LIN/J2602 bus Sync character) in order to calculate the proper bit rate. The measurement takes over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG registers. Once the 5th edge is seen (should correspond to the Stop bit), the ABDEN bit is automatically cleared.

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. The BRG clock can be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG and SPBRGH as a 16-bit counter.

This allows the user to verify that no carry occurred for 8bit modes by checking for 00h in the SPBRGH register. Refer to Table 20-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character (see Section 20.3.4 "Auto-Wake-up on Sync Break Character").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

- **3:** To maximize baud rate range, setting the BRG16 bit is recommended if the auto-baud feature is used.

TABLE 20-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/256          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

# 20.4 EUSART Synchronous Master Mode

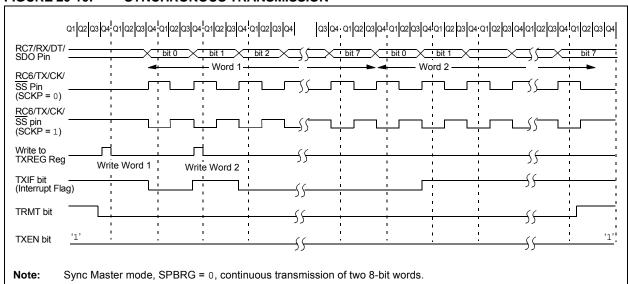

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK/SS and RC7/RX/DT/SDO I/O pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit, sets the Idle state low. This option is provided to support Microwire devices with this module.

# 20.4.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-2. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit, TXIF, will be set, regardless of the state of enable bit, TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### REGISTER 21-3: ADCON2: A/D CONTROL REGISTER 2

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADFM  | ACQT3 | ACQT2 | ACQT1 | ACQT0 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified

0 = Left justified

bit 6-3 ACQT<3:0>: A/D Acquisition Time Select bits

0000 = No delay (conversion starts immediately when GO/DONE is set)(1)

0001 **= 2** TAD

0010 **= 4 T**AD

0011 **= 6** TAD

0100 **= 8** TAD

0101 = 10 TAD

0110 = 12 TAD 0111 = 16 TAD

1000 **= 20 T**AD

1001 **= 24 T**AD

1010 = 28 TAD

1011 = 32 TAD

1100 = 36 TAD

1101 **= 40 T**AD

1110 = 48 TAD

1111 = 64 TAD

bit 2-0 ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2

001 = Fosc/8

010 = Fosc/32

011 = FRC/4

100 = Fosc/4

101 = Fosc/16

110 = Fosc/64

111 = FRC (Internal A/D RC Oscillator)

Note 1: If the A/D RC clock source is selected, a delay of one Tcy (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

#### FIGURE 24-1: GENERAL FORMAT FOR INSTRUCTIONS

#### Byte-oriented file register operations **Example Instruction** 15 OPCODE f (FILE #) d а ADDWF MYREG, W, B d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 12 11 **OPCODE** f (Source FILE #) MOVFF MYREG1, MYREG2 15 12 11 0 1111 f (Destination FILE #) f = 12-bit file register address Bit-oriented file register operations 12 11 15 987 OPCODE b (BIT#) a f (FILE #) BSF MYREG, bit, B b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Literal operations 15 8 7 **OPCODE** MOVLW 0x7F k (literal) k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 0 OPCODE n<7:0> (literal) GOTO Label 15 n<19:8> (literal) 1111 n = 20-bit immediate value 15 CALL MYFUNC OPCODE n<7:0> (literal) 0 15 12 11 n<19:8> (literal) S = Fast bit 15 11 10 n BRA MYFUNC **OPCODE** n<10:0> (literal) 8 7 15 **OPCODE** n<7:0> (literal) BC MYFUNC

# 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2331/2431/4331/4431 (Industrial, Extended) PIC18LF2331/2431/4331/4431 (Industrial)

| PIC18LF2331/2431/4331/4431<br>(Industrial)          |                                         |     |     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial                                                                        |        |                                                |  |  |  |

|-----------------------------------------------------|-----------------------------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------|--|--|--|

| PIC18F2331/2431/4331/4431<br>(Industrial, Extended) |                                         |     |     | andard Operating Conditions (unless otherwise stated) berating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |        |                                                |  |  |  |

| Param<br>No.                                        | Device   Typ   Max   Units   Conditions |     |     |                                                                                                                                                                                                                                 |        |                                                |  |  |  |

|                                                     | Power-Down Current (IPD)                | (1) |     |                                                                                                                                                                                                                                 |        |                                                |  |  |  |

|                                                     | PIC18LF2X31/4X31                        | 0.1 | 0.5 | μΑ                                                                                                                                                                                                                              | -40°C  | \/pp = 2.0\/                                   |  |  |  |

|                                                     |                                         | 0.1 | 0.5 | μΑ                                                                                                                                                                                                                              | +25°C  | V <sub>DD</sub> = 2.0V<br>( <b>Sleep</b> mode) |  |  |  |

|                                                     |                                         | 0.2 | 1.9 | μΑ                                                                                                                                                                                                                              | +85°C  | (Gleep Mode)                                   |  |  |  |

|                                                     | PIC18LF2X31/4X31                        | 0.1 | 0.5 | μΑ                                                                                                                                                                                                                              | -40°C  | \/ 0.0\/                                       |  |  |  |

|                                                     |                                         | 0.1 | 0.5 | μΑ                                                                                                                                                                                                                              | +25°C  | V <sub>DD</sub> = 3.0V<br>( <b>Sleep</b> mode) |  |  |  |

|                                                     |                                         | 0.3 | 1.9 | μΑ                                                                                                                                                                                                                              | +85°C  | (Sieep Mode)                                   |  |  |  |

|                                                     | All devices                             | 0.1 | 2.0 | μΑ                                                                                                                                                                                                                              | -40°C  | _                                              |  |  |  |

|                                                     |                                         |     | 2.0 | μΑ                                                                                                                                                                                                                              | +25°C  | VDD = 5.0V                                     |  |  |  |

|                                                     |                                         | 0.4 | 6.5 | μΑ                                                                                                                                                                                                                              | +85°C  | (Sleep mode)                                   |  |  |  |

|                                                     |                                         | 5   | 33  | μΑ                                                                                                                                                                                                                              | +125°C |                                                |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

- 4: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

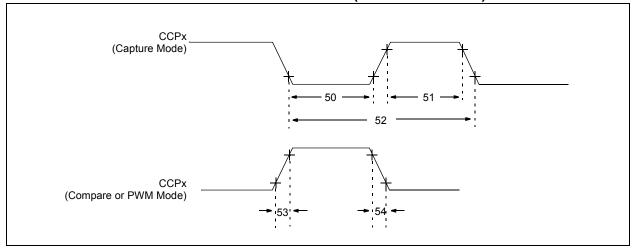

FIGURE 26-10: CAPTURE/COMPARE/PWM TIMINGS (ALL CCP MODULES)

TABLE 26-10: CAPTURE/COMPARE/PWM REQUIREMENTS (ALL CCP MODULES)

| Param<br>No. | Symbol               | С                     | haracteristi | С           | Min             | Max | Units | Conditions                         |

|--------------|----------------------|-----------------------|--------------|-------------|-----------------|-----|-------|------------------------------------|

| 50           | TccL                 | CCPx Input Low        | No prescale  | er          | 0.5 Tcy + 20    | _   | ns    |                                    |

|              |                      | Time                  | With         | PIC18FXX31  | 10              | _   | ns    |                                    |

|              |                      |                       | prescaler    | PIC18LFXX31 | 20              | _   | ns    |                                    |

| 51           | TccH CCPx Input High |                       | No prescaler |             | 0.5 Tcy + 20    | _   | ns    |                                    |

|              |                      | Time                  | With         | PIC18FXX31  | 10              | _   | ns    |                                    |

|              |                      |                       | prescaler    | PIC18LFXX31 | 20              | _   | ns    |                                    |

| 52           | TccP                 | CCPx Input Perio      | od           |             | 3 Tcy + 40<br>N | _   | ns    | N = prescale<br>value (1, 4 or 16) |

| 53           | TccR                 | CCPx Output Fal       | l Time       | PIC18FXX31  | _               | 25  | ns    |                                    |

|              |                      |                       |              | PIC18LFXX31 | _               | 45  | ns    |                                    |

| 54           | TccF                 | CCPx Output Fall Time |              | PIC18FXX31  | _               | 25  | ns    |                                    |

|              |                      |                       |              | PIC18LFXX31 | _               | 45  | ns    |                                    |

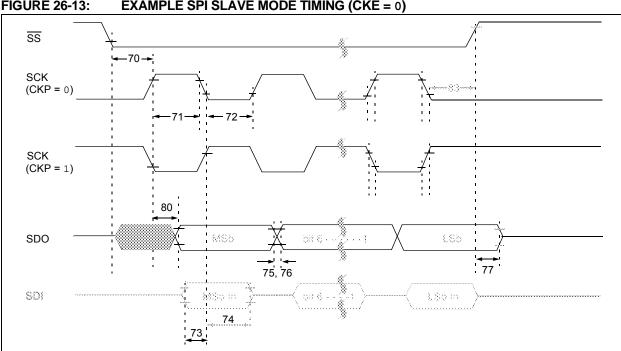

FIGURE 26-13: **EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)**

TABLE 26-13: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                  |                  | Min           | Max | Units | Conditions |

|--------------|-----------------------|-------------------------------------------------|------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS ↓ to SCK ↓ or SCK ↑ Input                    |                  | Tcy           | _   | ns    |            |

| 71           | TscH                  | SCK Input High Time                             | Continuous       | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       |                                                 | Single byte      | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                              | Continuous       | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       |                                                 | Single byte      | 40            | _   | ns    | (Note 1)   |

| 73           | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SCK Ed          | dge              | 20            | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First Cloc     | k Edge of Byte 2 | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edg          | је               | 40            | _   | ns    |            |

| 75           | TdoR                  | SDO Data Output Rise Time                       | PIC18FXX31       | _             | 25  | ns    |            |

|              |                       |                                                 | PIC18LFXX31      | _             | 45  | ns    | 1          |

| 76           | TdoF                  | SDO Data Output Fall Time                       |                  | _             | 25  | ns    |            |

| 77           | TssH2doZ              | SS ↑ to SDO Output High-Impedance               |                  | 10            | 50  | ns    |            |

| 80           | TscH2doV,             | SDO Data Output Valid after SCK Edge PIC18FXX31 |                  | _             | 50  | ns    |            |

|              | TscL2doV              |                                                 | PIC18LFXX31      | _             | 100 | ns    | ]          |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                             |                  | 1.5 Tcy + 40  | _   | ns    |            |

Requires the use of Parameter 73A. Note 1:

2: Only if Parameter 71A and 72A are used.

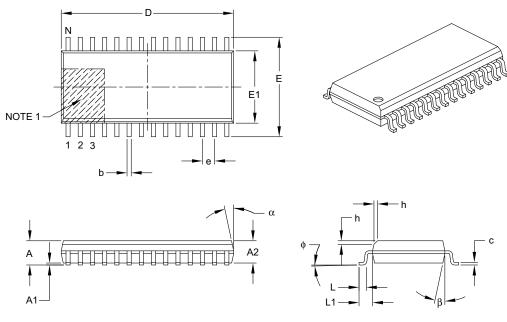

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units          |           | MILLIMETERS |      |  |

|--------------------------|----------------|-----------|-------------|------|--|

| Dir                      | mension Limits | MIN       | NOM         | MAX  |  |

| Number of Pins           | N              | 28        |             |      |  |

| Pitch                    | е              | 1.27 BSC  |             |      |  |

| Overall Height           | А              | -         | _           | 2.65 |  |

| Molded Package Thickness | A2             | 2.05      | _           | _    |  |

| Standoff §               | A1             | 0.10      | _           | 0.30 |  |

| Overall Width            | E              | 10.30 BSC |             |      |  |

| Molded Package Width     | E1             | 7.50 BSC  |             |      |  |

| Overall Length           | D              | 17.90 BSC |             |      |  |

| Chamfer (optional)       | h              | 0.25      | _           | 0.75 |  |

| Foot Length              | L              | 0.40      | _           | 1.27 |  |

| Footprint                | L1             | 1.40 REF  |             |      |  |

| Foot Angle Top           | ф              | 0°        | _           | 8°   |  |

| Lead Thickness           | С              | 0.18      | _           | 0.33 |  |

| Lead Width               | b              | 0.31      | _           | 0.51 |  |

| Mold Draft Angle Top     | α              | 5°        | _           | 15°  |  |

| Mold Draft Angle Bottom  | β              | 5°        | _           | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B