#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT        |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 9x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4431-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

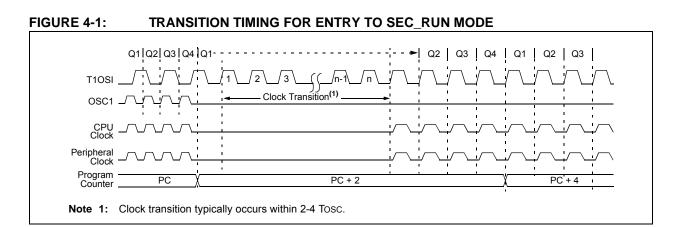

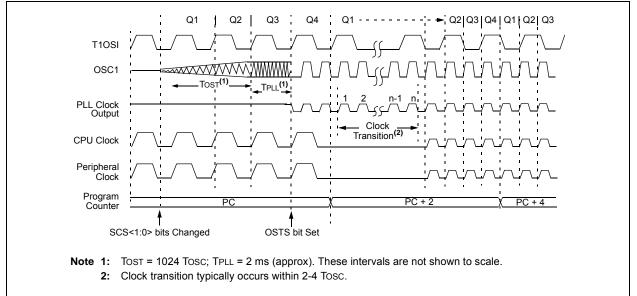

#### 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer. In this mode, the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

NOTES:

| Name   | Bit 7                       | Bit 6          | Bit 5         | Bit 4        | Bit 3   | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values on<br>page |

|--------|-----------------------------|----------------|---------------|--------------|---------|--------|---------------|--------|----------------------------|

| INTCON | GIE/GIEH                    | PEIE/GIEL      | TMR0IE        | INT0IE       | RBIE    | TMR0IF | <b>INT0IF</b> | RBIF   | 54                         |

| EEADR  | ADR EEPROM Address Register |                |               |              |         |        |               |        | 56                         |

| EEDATA | EEPROM Data Register        |                |               |              |         |        |               |        | 56                         |

| EECON2 | EEPROM C                    | ontrol Registe | er 2 (not a p | physical reg | gister) |        |               |        | 56                         |

| EECON1 | EEPGD                       | CFGS           | _             | FREE         | WRERR   | WREN   | WR            | RD     | 56                         |

| IPR2   | OSCFIP                      | —              | —             | EEIP         | —       | LVDIP  | _             | CCP2IP | 57                         |

| PIR2   | OSCFIF                      | _              |               | EEIF         |         | LVDIF  |               | CCP2IF | 57                         |

| PIE2   | OSCFIE                      | _              |               | EEIE         |         | LVDIE  |               | CCP2IE | 57                         |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### EXAMPLE 8-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

| PROGRAM_MEMORY |              |                             |

|----------------|--------------|-----------------------------|

| BCF            | INTCON, GIE  | ; disable interrupts        |

| MOVLW          | 55h          | ; required sequence         |

| MOVWF          | EECON2       | ; write 55h                 |

| MOVLW          | 0AAh         |                             |

| MOVWF          | EECON2       | ; write OAAh                |

| BSF            | EECON1, WR   | ; start program (CPU stall) |

| NOP            |              |                             |

| BSF            | INTCON, GIE  | ; re-enable interrupts      |

| DECFSZ         | COUNTER_HI   | ; loop until done           |

| GOTO           | PROGRAM_LOOP |                             |

| BCF            | EECON1, WREN | ; disable write to memory   |

|                |              |                             |

#### 8.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 8.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. The WRE<u>RR bit</u> is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, users can check the WRERR bit and rewrite the location.

#### 8.6 Flash Program Operation During Code Protection

See Section 23.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7           | Bit 6        | Bit 5                                                                         | Bit 4       | Bit 3       | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on Page: |

|---------|-----------------|--------------|-------------------------------------------------------------------------------|-------------|-------------|--------|---------------|--------|-----------------------------|

| TBLPTRU |                 | _            | bit 21 <sup>(1)</sup> Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |             |             |        |               |        | 54                          |

| TBPLTRH | Program N       | lemory Table | e Pointer I                                                                   | High Byte ( | TBLPTR<15   | :8>)   |               |        | 54                          |

| TBLPTRL | Program N       | lemory Table | e Pointer I                                                                   | _ow Byte (  | TBLPTR<7:0  | >)     |               |        | 54                          |

| TABLAT  | Program N       | lemory Table | e Latch                                                                       |             |             |        |               |        | 54                          |

| INTCON  | <b>GIE/GIEH</b> | PEIE/GIEL    | TMR0IE                                                                        | INT0IE      | RBIE        | TMR0IF | <b>INT0IF</b> | RBIF   | 54                          |

| EECON2  | EEPROM          | Control Reg  | ister 2 (no                                                                   | t a physica | l register) |        |               |        | 56                          |

| EECON1  | EEPGD           | CFGS         |                                                                               | FREE        | WRERR       | WREN   | WR            | RD     | 56                          |

| IPR2    | OSCFIP          | _            |                                                                               | EEIP        | _           | LVDIP  |               | CCP2IP | 57                          |

| PIR2    | OSCFIF          | —            |                                                                               | EEIF        | _           | LVDIF  | _             | CCP2IF | 57                          |

| PIE2    | OSCFIE          | _            | _                                                                             | EEIE        | _           | LVDIE  | _             | CCP2IE | 57                          |

#### TABLE 8-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

| R/W-1      | R/W-1                                                                                                              | U-0                                           | R/W-0            | R/W-0            | U-0             | R/W-0              | R/W-0            |  |

|------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------|-----------------|--------------------|------------------|--|

| INT2IF     | P INT1IP                                                                                                           | —                                             | INT2IE           | INT1IE           | —               | INT2IF             | INT1IF           |  |

| bit 7      |                                                                                                                    |                                               |                  |                  |                 |                    | bit 0            |  |

| Lonondi    |                                                                                                                    |                                               |                  |                  |                 |                    |                  |  |

| Legend:    |                                                                                                                    |                                               | - :4             |                  |                 | (O)                |                  |  |

| R = Read   |                                                                                                                    | W = Writable                                  | DIL              | •                | nented bit, rea |                    |                  |  |

| -n = Value | alPOR                                                                                                              | '1' = Bit is set                              |                  | '0' = Bit is cle | areo            | x = Bit is unkr    | lown             |  |

| bit 7      | INT2IP: INT2                                                                                                       | External Interre                              | upt Priority bit |                  |                 |                    |                  |  |

|            | 1 = High prio<br>0 = Low prior                                                                                     | •                                             |                  |                  |                 |                    |                  |  |

| bit 6      | INT1IP: INT1                                                                                                       | External Interre                              | upt Priority bit |                  |                 |                    |                  |  |

|            | 1 = High prio<br>0 = Low prior                                                                                     |                                               |                  |                  |                 |                    |                  |  |

| bit 5      | Unimplemen                                                                                                         | ted: Read as 'd                               | )'               |                  |                 |                    |                  |  |

| bit 4      | INT2IE: INT2                                                                                                       | External Interre                              | upt Enable bit   |                  |                 |                    |                  |  |

|            |                                                                                                                    | the INT2 extern the INT2 extern               |                  |                  |                 |                    |                  |  |

| bit 3      | INT1IE: INT1                                                                                                       | External Interre                              | upt Enable bit   |                  |                 |                    |                  |  |

|            |                                                                                                                    | the INT1 extern the INT1 extern               |                  |                  |                 |                    |                  |  |

| bit 2      | Unimplemen                                                                                                         | ted: Read as 'o                               | )'               |                  |                 |                    |                  |  |

| bit 1      | INT2IF: INT2                                                                                                       | External Interru                              | upt Flag bit     |                  |                 |                    |                  |  |

|            |                                                                                                                    |                                               |                  | must be cleare   | d in software)  |                    |                  |  |

|            |                                                                                                                    | 0 = The INT2 external interrupt did not occur |                  |                  |                 |                    |                  |  |

| bit 0      | INT1IF: INT1 External Interrupt Flag bit<br>1 = The INT1 external interrupt occurred (must be cleared in software) |                                               |                  |                  |                 |                    |                  |  |

|            |                                                                                                                    | external interr                               |                  |                  | d in software)  |                    |                  |  |

|            |                                                                                                                    |                                               | apt dia not 00   | oui              |                 |                    |                  |  |

| Note:      | Interrupt flag bits                                                                                                |                                               |                  |                  |                 |                    |                  |  |

|            | enable bit or the g                                                                                                |                                               |                  |                  |                 | ate interrupt flag | y bits are clear |  |

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| Name    | Bit 7                          | Bit 6          | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset Values<br>on Page: |

|---------|--------------------------------|----------------|---------|---------|--------|--------|---------------|--------|--------------------------|

| PORTB   | RB7                            | RB6            | RB5     | RB4     | RB3    | RB2    | RB1           | RB0    | 57                       |

| LATB    | LATB LATB Data Output Register |                |         |         |        |        |               |        | 57                       |

| TRISB   | PORTB Dat                      | a Direction Re | egister |         |        |        |               |        | 57                       |

| INTCON  | GIE/GIEH                       | PEIE/GIEL      | TMR0IE  | INT0IE  | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 54                       |

| INTCON2 | RBPU                           | INTEDG0        | INTEDG1 | INTEDG2 | _      | TMR0IP |               | RBIP   | 54                       |

| INTCON3 | INT2IP                         | INT1IP         | _       | INT2IE  | INT1IE | _      | INT2IF        | INT1IF | 54                       |

#### TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

#### 11.4 PORTD, TRISD and LATD Registers

| Note: | PORTD is only available on PIC18F4331/ |

|-------|----------------------------------------|

|       | 4431 devices.                          |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power-on Reset, these pins are |

|-------|-------------------------------------|

|       | configured as digital inputs.       |

PORTD includes PWM<7:6> complementary fourth channel PWM outputs. PWM4 is the complementary output of PWM5 (the third channel), which is multiplexed with the RB5 pin. This output can be used as the alternate output using the PWM4MX Configuration bit in CONFIG3H when the Single-Supply Programming pin (PGM) is used on RB5.

RD1, RD2 and RD3 can be used as the alternate output for SDO, SDI/SDA and SCK/SCL using the SSPMX Configuration bit in CONFIG3H.

RD4 an be used as the alternate output for FLTA using the FLTAMX Configuration bit in CONFIG3H.

| EXAMPLE 11-4: INIT | <b>FIALIZING PORTD</b> |

|--------------------|------------------------|

|--------------------|------------------------|

| CLRF  | PORTD | ; Initialize PORTD by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       |                         |

The three input capture channels are controlled through the Input Capture Control registers, CAP1CON, CAP2CON and CAP3CON. Each channel is configured independently with its dedicated register. The implementation of the registers is identical except for the Special Event Trigger (see Section 17.1.8 "Special Event Trigger (CAP1 Only)"). The typical Capture Control register is shown in Register 17-1.

Note: Throughout this section, references to registers and bit names that may be associated with a specific capture channel will be referred to generically by the use of the term 'x' in place of the channel number. For example, 'CAPxREN' may refer to the Capture Reset Enable bit in CAP1CON, CAP2CON or CAP3CON.

#### REGISTER 17-1: CAPxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0   | R/W-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|---------|-----|-----|--------|--------|--------|--------|

| —     | CAPxREN | —   | —   | CAPxM3 | CAPxM2 | CAPxM1 | CAPxM0 |

| bit 7 |         |     |     |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 7   | Unimplemented: Read as '0'                                                                               |  |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| bit 6   | CAPxREN: Time Base Reset Enable bit                                                                      |  |  |  |  |  |  |  |  |

| 5.00    | 1 = Enabled                                                                                              |  |  |  |  |  |  |  |  |

|         | 0 = Disable selected time base Reset on capture                                                          |  |  |  |  |  |  |  |  |

| bit 5-4 | Unimplemented: Read as '0'                                                                               |  |  |  |  |  |  |  |  |

| bit 3-0 | CAPxM<3:0>: Input Capture x (ICx) Mode Select bits                                                       |  |  |  |  |  |  |  |  |

|         | 1111 = Special Event Trigger mode; the trigger occurs on every rising edge on CAP1 input <sup>(1)</sup>  |  |  |  |  |  |  |  |  |

|         | 1110 = Special Event Trigger mode; the trigger occurs on every falling edge on CAP1 input <sup>(1)</sup> |  |  |  |  |  |  |  |  |

|         | 1101 = Unused                                                                                            |  |  |  |  |  |  |  |  |

|         | 1100 = Unused                                                                                            |  |  |  |  |  |  |  |  |

|         | 1011 = Unused                                                                                            |  |  |  |  |  |  |  |  |

|         | 1010 = Unused                                                                                            |  |  |  |  |  |  |  |  |

|         | 1001 = Unused                                                                                            |  |  |  |  |  |  |  |  |

|         | 1000 = Capture on every CAPx input state change                                                          |  |  |  |  |  |  |  |  |

|         | 0111 = Pulse-Width Measurement mode, every rising to falling edge                                        |  |  |  |  |  |  |  |  |

|         | 0110 = Pulse-Width Measurement mode, every falling to rising edge                                        |  |  |  |  |  |  |  |  |

|         | 0101 = Frequency Measurement mode, every rising edge                                                     |  |  |  |  |  |  |  |  |

|         | 0100 = Capture mode, every 16th rising edge                                                              |  |  |  |  |  |  |  |  |

|         | 0011 = Capture mode, every 4th rising edge                                                               |  |  |  |  |  |  |  |  |

|         | 0010 = Capture mode, every rising edge                                                                   |  |  |  |  |  |  |  |  |

|         | 0001 = Capture mode, every falling edge                                                                  |  |  |  |  |  |  |  |  |

|         | 0000 = Input Capture x (ICx) off                                                                         |  |  |  |  |  |  |  |  |

**Note 1:** Special Event Trigger is only available on CAP1. For CAP2 and CAP3, this configuration is unused.

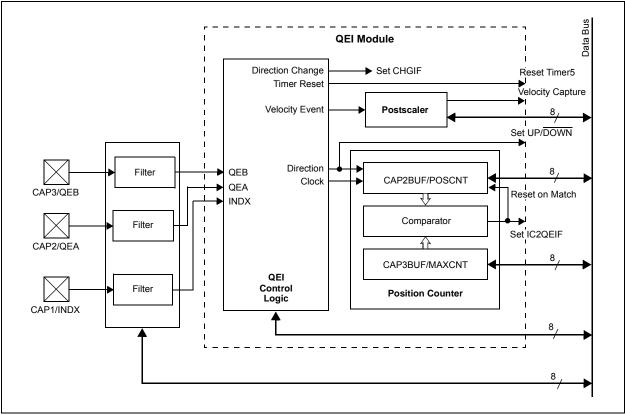

#### 17.2 Quadrature Encoder Interface

The Quadrature Encoder Interface (QEI) decodes speed and motion sensor information. It can be used in any application that uses a quadrature encoder for feedback. The interface implements these features:

- Three QEI inputs: two phase signals (QEA and QEB) and one index signal (INDX)

- Direction of movement detection with a direction change interrupt (IC3DRIF)

- 16-bit up/down position counter

- Standard and High-Precision Position Tracking modes

- Two Position Update modes (x2 and x4)

- Velocity measurement with a programmable postscaler for high-speed velocity measurement

- Position counter interrupt (IC2QEIF in the PIR3 register)

- Velocity control interrupt (IC1IF in the PIR3 register)

The QEI submodule has three main components: the QEI control logic block, the position counter and velocity postscaler.

The QEI control logic detects the leading edge on the QEA or QEB phase input pins and generates the count pulse, which is sent to the position counter logic. It also samples the index input signal (INDX) and generates the direction of the rotation signal (up/down) and the velocity event signals.

The position counter acts as an integrator for tracking distance traveled. The QEA and QEB input edges serve as the stimulus to create the input clock which advances the Position Counter register (POSCNT). The register is incremented on either the QEA input edge, or the QEA and QEB input edges, depending on the operating mode. It is reset either by a rollover on match to the Period register, MAXCNT, or on the external index pulse input signal (INDX). An interrupt is generated on a Reset of POSCNT if the position counter interrupt is enabled.

The velocity postscaler down samples the velocity pulses used to increment the velocity counter by a specified ratio. It essentially divides down the number of velocity pulses to one output per so many inputs, preserving the pulse width in the process.

A simplified block-diagram of the QEI module is shown in Figure 17-8.

#### FIGURE 17-8: QEI BLOCK DIAGRAM

#### 17.2.2 QEI MODES

Position measurement resolution depends on how often the Position Counter register, POSCNT, is incremented. There are two QEI Update modes to measure the rotor's position: QEI x2 and QEI x4.

| QEIM<2:0> | Mode/<br>Reset                | Description                                                                                    |

|-----------|-------------------------------|------------------------------------------------------------------------------------------------|

| 000       |                               | QEI disabled. <sup>(1)</sup>                                                                   |

| 001       | x2 update/<br>index pulse     | Two clocks per QEA<br>pulse. INDX resets<br>POSCNT.                                            |

| 010       | x2 update/<br>period<br>match | Two clocks per QEA pulse.<br>POSCNT is reset by the<br>period match (MAXCNT).                  |

| 011       | _                             | Unused.                                                                                        |

| 100       | _                             | Unused.                                                                                        |

| 101       | x4 update/<br>index pulse     | Four clocks per QEA and QEB pulse pair. INDX resets POSCNT.                                    |

| 110       | x4 update/<br>period<br>match | Four clocks per QEA and<br>QEB pulse pair.<br>POSCNT is reset by the<br>period match (MAXCNT). |

| 111       | _                             | Unused.                                                                                        |

**Note 1:** QEI module is disabled. The position counter and the velocity measurement functions are fully disabled in this mode.

#### 17.2.2.1 QEI x2 Update Mode

QEI x2 Update mode is selected by setting the QEI Mode Select bits (QEIM<2:0>) to '001' or '010'. In this mode, the QEI logic detects every edge on the QEA input only. Every rising and falling edge on the QEA signal clocks the position counter.

The position counter can be reset by either an input on the INDX pin (QEIM<2:0> = 001), or by a period match, even when the POSCNT register pair equals MAXCNT (QEIM<2:0> = 010).

#### 17.2.2.2 QEI x4 Update Mode

QEI x4 Update mode provides for a finer resolution of the rotor position, since the counter increments or decrements more frequently for each QEA/QEB input pulse pair than in QEI x2 mode. This mode is selected by setting the QEI mode select bits to '101' or '110'. In QEI x4, the phase measurement is made on the rising and the falling edges of both QEA and QEB inputs. The position counter is clocked on every QEA and QEB edge.

Like QEI x2 mode, the position counter can be reset by an input on the pin (QEIM<2:0> = 101), or by the period match event (QEIM<2:0> = 010).

#### 17.2.3 QEI OPERATION

The Position Counter register pair (POSCNTH: POSCNTL) acts as an integrator, whose value is proportional to the position of the sensor rotor that corresponds to the number of active edges detected. POSCNT can either increment or decrement, depending on a number of selectable factors which are decoded by the QEI logic block. These include the Count mode selected, the phase relationship of QEA to QEB ("lead/lag"), the direction of rotation and if a Reset event occurs. The logic is detailed in the sections that follow.

#### 17.2.3.1 Edge and Phase Detect

In the first step, the active edges of QEA and QEB are detected, and the phase relationship between them is determined. The position counter is changed based on the selected QEI mode.

In QEI x2 Update mode, the position counter increments or decrements on every QEA edge based on the phase relationship of the QEA and QEB signals.

In QEI x4 Update mode, the position counter increments or decrements on every QEA and QEB edge based on the phase relationship of the QEA and QEB signals. For example, if QEA leads QEB, the position counter is incremented by '1'. If QEB lags QEA, the position counter is decremented by '1'.

#### 17.2.3.2 Direction of Count

The QEI control logic generates a signal that sets the UP/DOWN bit (QEICON<5>); this, in turn, determines the direction of the count. When QEA leads QEB, UP/DOWN is set (= 1) and the position counter increments on every active edge. When QEA lags QEB, UP/DOWN is cleared and the position counter decrements on every active edge.

#### TABLE 17-5: DIRECTION OF ROTATION

| Current            | P   | Previous Signal<br>Detected |     |      |                               |  |  |  |

|--------------------|-----|-----------------------------|-----|------|-------------------------------|--|--|--|

| Signal<br>Detected | Ris | Rising                      |     | ling | Pos.<br>Cntrl. <sup>(1)</sup> |  |  |  |

|                    | QEA | QEB                         | QEA | QEB  |                               |  |  |  |

| QEA Rising         |     |                             |     | х    | INC                           |  |  |  |

|                    |     | х                           |     |      | DEC                           |  |  |  |

| QEA Falling        |     |                             |     | х    | DEC                           |  |  |  |

|                    |     | х                           |     |      | INC                           |  |  |  |

| QEB Rising         | х   |                             |     |      | INC                           |  |  |  |

|                    |     |                             | х   |      | DEC                           |  |  |  |

| QEB Falling        |     |                             | х   |      | INC                           |  |  |  |

|                    | х   |                             |     |      | DEC                           |  |  |  |

**Note 1:** When UP/DOWN = 1, the position counter is incremented. When UP/DOWN = 0, the position counter is decremented.

| R/W-0      | R/W-0                         | R/W-0                                | R/W-0                 | R/W-0                 | R/W-0            | R/W-0           | R/W-0                    |

|------------|-------------------------------|--------------------------------------|-----------------------|-----------------------|------------------|-----------------|--------------------------|

| BRFEN      | FLTBS <sup>(1)</sup>          | FLTBMOD <sup>(1)</sup>               | FLTBEN <sup>(1)</sup> | FLTCON <sup>(2)</sup> | FLTAS            | FLTAMOD         | FLTAEN                   |

| bit 7      |                               |                                      |                       |                       |                  |                 | bit C                    |

|            |                               |                                      |                       |                       |                  |                 |                          |

| Legend:    |                               |                                      |                       |                       |                  |                 |                          |

| R = Read   |                               | W = Writable bi                      | t                     | -                     | nented bit, rea  |                 |                          |

| -n = Value | e at POR                      | '1' = Bit is set                     |                       | '0' = Bit is cle      | ared             | x = Bit is unkn | own                      |

| bit 7      | BRFEN: Brea                   | akpoint Fault Ena                    | ble bit               |                       |                  |                 |                          |

|            |                               | Fault condition on                   | a breakpoint          | (i.e., only wher      | ו PWMPIN = 1     | .)              |                          |

| bit 6      | FLTBS: Faul                   | t B Status bit <sup>(1)</sup>        |                       |                       |                  |                 |                          |

|            | $1 = \overline{FLTB}$ is a    |                                      |                       |                       |                  |                 |                          |

|            |                               | 10D = 0, cleared                     |                       |                       | 6 4km            |                 |                          |

|            | 0 = No Fault                  | IOD = 1, cleared                     | automatically         | at beginning o        | r the new perio  | a when FLIB is  | deasserted               |

| bit 5      | FLTBMOD: F                    | -<br>Fault B Mode bit <sup>(1</sup>  | )                     |                       |                  |                 |                          |

|            | 1 = Cycle-by                  | -Cycle mode: Pir                     | ns are inactiv        | e for the remair      | nder of the cur  | rent PWM period | d or until FLTB          |

|            |                               | erted; FLTBS is c                    |                       |                       |                  |                 |                          |

|            |                               | mode: Pins are only the user only    | deactivated (         | catastrophic fai      | lure) until FLI  | B is deasserted | and FLIBS is             |

| bit 4      |                               | ult B Enable bit <sup>(1)</sup>      |                       |                       |                  |                 |                          |

|            | 1 = Enable F                  |                                      |                       |                       |                  |                 |                          |

|            | 0 = Disable I                 |                                      |                       |                       |                  |                 |                          |

| bit 3      |                               | ult Configuration                    |                       |                       |                  |                 |                          |

|            |                               | <u>TB</u> or both deact              |                       | M outputs             |                  |                 |                          |

| bit 2      | FLTAS: Fault                  |                                      | F VVIVI~5.0~          |                       |                  |                 |                          |

|            | $1 = \overline{FLTA}$ is a    |                                      |                       |                       |                  |                 |                          |

|            | if FLTAM                      | IOD = 0, cleared                     |                       |                       |                  |                 |                          |

|            |                               | IOD = 1, cleared                     | automatically         | at beginning o        | f the new peric  | od when FLTA is | deasserted               |

| bit 1      | 0 = No Fault                  | ault A Mode bit                      |                       |                       |                  |                 |                          |

|            | -                             | -Cycle mode: Pin                     | is are inactive       | for the remain        | der of the curre | ent PWM period  | or until <u>FI TA</u> is |

|            |                               | ed; FLTAS is clea                    |                       |                       |                  |                 |                          |

|            |                               | mode: Pins are only the user only    | deactivated (         | catastrophic fai      | lure) until FLT  | A is deasserted | and FLTAS is             |

| bit 0      | FLTAEN: Fau                   | ult A Enable bit                     |                       |                       |                  |                 |                          |

|            | 1 = Enable F<br>0 = Disable I |                                      |                       |                       |                  |                 |                          |

| Note 1:    | Unimplemented                 | 1 in PIC18F2331/2                    | 2431 devices          | ; maintain these      | e bits clear.    |                 |                          |

| 2:         | PWM<7:6> are                  | implemented only<br>N has no effect. |                       |                       |                  | F2331/2431 devi | ces, setting or          |

#### REGISTER 18-8: FLTCONFIG: FAULT CONFIGURATION REGISTER

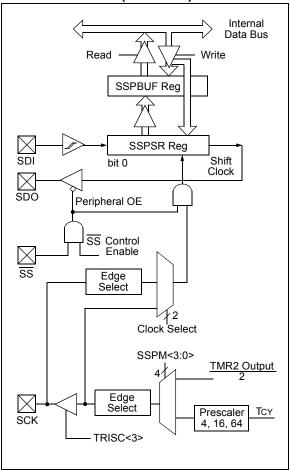

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear bit SSPEN, reinitialize the SSPCON register and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- Serial Data Out (SDO) RC7/RX/DT/SDO or RD1/SDO

- SDI must have TRISC<4> or TRISD<2> set

- SDO must have TRISC<7> or TRISD<1> cleared

- SCK (Master mode) must have TRISC<5> or TRISD<3> cleared

- SCK (Slave mode) must have TRISC<5> or TRISD<3> set

- SS must have TRISA<6> set

- Note 1: When the SPI is in Slave mode, with the SS pin control enabled, (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = 1, then the  $\overline{SS}$  pin control must be enabled.

- 3: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the state of the SS pin can affect the state read back from the TRISC<6> bit. The peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<6> bit (see Section 11.3 "PORTC, TRISC and LATC Registers" for information on PORTC). If Read-Modify-Write instructions, such as BSF, are performed on the TRISC register while the SS pin is high, this will cause the TRISC<6> bit to be set, thus disabling the SDO output.

#### 19.3.1.3 Transmission

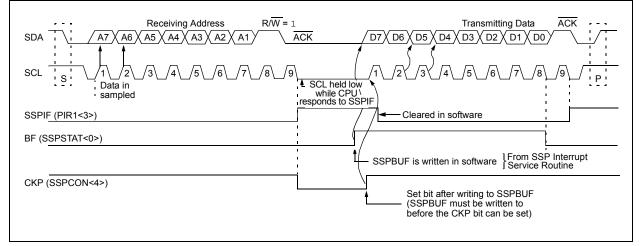

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin, SCK/SCL, is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin, SCK/SCL, should be enabled by setting bit, CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 19-7). An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF, must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit, SSPIF, is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin, SCK/SCL, should be enabled by setting bit CKP.

| U-0        | R-1                                            | U-0                                                                                                                                                                                                                                                    | R/W-1           | R/W-0                                    | U-0            | R/W-0           | R/W-0           |  |  |  |  |

|------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------|----------------|-----------------|-----------------|--|--|--|--|

| —          | RCIDL                                          |                                                                                                                                                                                                                                                        | SCKP            | BRG16                                    | —              | WUE             | ABDEN           |  |  |  |  |

| bit 7      |                                                |                                                                                                                                                                                                                                                        |                 |                                          |                |                 | bit             |  |  |  |  |

|            |                                                |                                                                                                                                                                                                                                                        |                 |                                          |                |                 |                 |  |  |  |  |

| Legend:    |                                                |                                                                                                                                                                                                                                                        |                 |                                          |                |                 |                 |  |  |  |  |

| R = Read   | able bit                                       | W = Writable                                                                                                                                                                                                                                           | bit             | U = Unimplem                             | ented bit, rea | d as '0'        |                 |  |  |  |  |

| -n = Value | e at POR                                       | '1' = Bit is se                                                                                                                                                                                                                                        | t               | '0' = Bit is clea                        | ared           | x = Bit is unki | nown            |  |  |  |  |

| bit 7      | Unimplemen                                     | ted: Read as                                                                                                                                                                                                                                           | 0'              |                                          |                |                 |                 |  |  |  |  |

| bit 6      | RCIDL: Rece                                    | ive Operation                                                                                                                                                                                                                                          | Idle Status bit |                                          |                |                 |                 |  |  |  |  |

|            | 1 = Receiver<br>0 = Receive i                  |                                                                                                                                                                                                                                                        |                 |                                          |                |                 |                 |  |  |  |  |

| bit 5      |                                                | ited: Read as '                                                                                                                                                                                                                                        | 0'              |                                          |                |                 |                 |  |  |  |  |

| bit 4      | -                                              | nronous Clock                                                                                                                                                                                                                                          |                 | t bit                                    |                |                 |                 |  |  |  |  |

|            | <u>Asynchronou</u><br>Unused in thi            |                                                                                                                                                                                                                                                        | ·               |                                          |                |                 |                 |  |  |  |  |

|            |                                                | for clock (CK)                                                                                                                                                                                                                                         |                 |                                          |                |                 |                 |  |  |  |  |

| L:1 0      |                                                | for clock (CK)                                                                                                                                                                                                                                         |                 | - 1-14                                   |                |                 |                 |  |  |  |  |

| bit 3      | 1 = 16-bit Ba                                  |                                                                                                                                                                                                                                                        | ator – SPBRG    | e bit<br>H and SPBRG<br>only (Compatible | mode) SPBI     | RGH value iono  | ored            |  |  |  |  |

| bit 2      |                                                | ted: Read as                                                                                                                                                                                                                                           |                 |                                          |                |                 | , ou            |  |  |  |  |

| bit 1      | WUE: Wake-                                     |                                                                                                                                                                                                                                                        |                 |                                          |                |                 |                 |  |  |  |  |

|            | hardware<br>0 = RX pin n<br><u>Synchronous</u> | will continue<br>on following r<br>ot monitored o<br><u>mode:</u>                                                                                                                                                                                      | ising edge      | RX pin – interru<br>etected              | pt generated   | on falling edge | ; bit cleared i |  |  |  |  |

|            | Unused in thi                                  |                                                                                                                                                                                                                                                        |                 |                                          |                |                 |                 |  |  |  |  |

| bit 0      |                                                | o-Baud Detect                                                                                                                                                                                                                                          | Enable bit      |                                          |                |                 |                 |  |  |  |  |

|            | 1 = Enable b<br>cleared in                     | <ul> <li><u>Asynchronous mode:</u></li> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) cleared in hardware upon completion.</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |                 |                                          |                |                 |                 |  |  |  |  |

|            | <u>Synchronous</u><br>Unused in thi            | mode:                                                                                                                                                                                                                                                  |                 | -                                        |                |                 |                 |  |  |  |  |

#### REGISTER 23-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| U-0   | U | R/P-1   | R/P-1               | R/P-1               | R/P-1                 | U | U     |

|-------|---|---------|---------------------|---------------------|-----------------------|---|-------|

| _     | — | T1OSCMX | HPOL <sup>(1)</sup> | LPOL <sup>(1)</sup> | PWMPIN <sup>(3)</sup> | _ | —     |

| bit 7 |   |         |                     |                     |                       |   | bit 0 |

| Legend:                                                                    |                                          |                                                                    |  |  |  |  |  |  |

|----------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| R = Reada                                                                  | ble bit P = Programmable b               | ut U = Unimplemented bit, read as '0'                              |  |  |  |  |  |  |

| -n = Value when device is unprogrammed U = Unchanged from programmed state |                                          |                                                                    |  |  |  |  |  |  |

|                                                                            |                                          |                                                                    |  |  |  |  |  |  |

| bit 7-6                                                                    | it 7-6 <b>Unimplemented:</b> Read as '0' |                                                                    |  |  |  |  |  |  |

| bit 5                                                                      | T1OSCMX: Timer1 Oscillator Mode          |                                                                    |  |  |  |  |  |  |

|                                                                            | 1 = Low-power Timer1 operation w         | hen microcontroller is in Sleep mode                               |  |  |  |  |  |  |

|                                                                            | 0 = Standard (legacy) Timer1 oscil       | lator operation                                                    |  |  |  |  |  |  |

| bit 4                                                                      | HPOL: High Side Transistors Polar        | ity bit (i.e., Odd PWM Output Polarity Control bit) <sup>(1)</sup> |  |  |  |  |  |  |

|                                                                            | 1 = PWM1, 3, 5 and 7 are active-h        | iqh (default) <sup>(2)</sup>                                       |  |  |  |  |  |  |

|                                                                            | 0 = PWM1, 3, 5 and 7 are active-lo       | <sub>W</sub> (2)                                                   |  |  |  |  |  |  |

| bit 3                                                                      | LPOL: Low Side Transistors Polari        | ty bit (i.e., Even PWM Output Polarity Control bit) <sup>(1)</sup> |  |  |  |  |  |  |

|                                                                            | 1 = PWM0, 2, 4 and 6 are active-h        |                                                                    |  |  |  |  |  |  |

|                                                                            | 0 = PWM0, 2, 4 and 6 are active-lo       | <sub>W</sub> (2)                                                   |  |  |  |  |  |  |

| bit 2                                                                      | PWMPIN: PWM Output Pins Reset            | State Control bit <sup>(3)</sup>                                   |  |  |  |  |  |  |

|                                                                            | 1 = PWM outputs are disabled upo         | n Reset (default)                                                  |  |  |  |  |  |  |

|                                                                            | 0 = PWM outputs drive active state       |                                                                    |  |  |  |  |  |  |

| bit 1-0                                                                    | Unimplemented: Read as '0'               |                                                                    |  |  |  |  |  |  |

|                                                                            | -                                        | define PWM signal output active and inactive states; PWM states    |  |  |  |  |  |  |

- ote 1: Polarity control bits, HPOL and LPOL, define PWM signal output active and inactive states; PV generated by the Fault inputs or PWM manual override.

- 2: PWM6 and PWM7 output channels are only available on PIC18F4331/4431 devices.

- **3:** When PWMPIN = 0, PWMEN<2:0> = 101 if the device has eight PWM output pins (40 and 44-pin devices) and PWMEN<2:0> = 100 if the device has six PWM output pins (28-pin devices). PWM output polarity is defined by HPOL and LPOL.

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic, |                                 | Description                              | Cycles     | 16-Bit Instruction Word |              |      | Status       | Netza             |              |

|-----------|---------------------------------|------------------------------------------|------------|-------------------------|--------------|------|--------------|-------------------|--------------|

| Opera     | nds                             | Description                              | Cycles     | MSb                     |              |      | LSb          | Affected          | Notes        |

| BYTE-ORI  | ENTED F                         | ILE REGISTER OPERATIONS                  |            |                         |              |      |              |                   |              |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2         |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2         |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da         | ffff | ffff         | Z, N              | 1,2          |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110                    | 101a         | ffff | ffff         | Z                 | 2            |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001                    | 11da         | ffff | ffff         | Z, N              | 1, 2         |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a         | ffff | ffff         | None              | 4            |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a         | ffff | ffff         | None              | 4            |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a         | ffff | ffff         | None              | 1, 2         |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2, 3, 4   |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da         | ffff | ffff         | None              | 1, 2, 3, 4   |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da         | ffff | ffff         | None              | 1, 2         |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010                    | 10da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2, 3, 4   |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da         | ffff | ffff         | None              | 4            |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da         | ffff | ffff         | None              | 1, 2         |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da         | ffff | ffff         | Z, N              | 1, 2         |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101                    | 00da         | ffff | ffff         | Z, N              | 1            |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff         | ffff | ffff         | None              |              |

|           | υu                              | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff         | ffff | ffff         |                   |              |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a         | ffff | ffff         | None              |              |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a         | ffff | ffff         | None              |              |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110                    | 110a         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2         |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da         | ffff | ffff         | C, Z, N           | <i>`</i>     |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da         | ffff | ffff         | Z, N              | 1, 2         |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da         | ffff | ffff         | C, Z, N           | ,            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da         | ffff | ffff         | Z, N              |              |

| SETF      | f, a                            | Set f                                    | 1          | 0110                    | 100a         | ffff | ffff         | None              |              |

| SUBFWB    | f, d, a                         | Subtract f from WREG with                | 1          | 0101                    | 01da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2         |

|           | ., u, u                         | Borrow                                   | •          | 0101                    | 0100         |      |              | 0, 20, 2, 0, 1, 1 | ., _         |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da         | ffff | ffff         | C, DC, Z, OV, N   |              |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da         | ffff | ffff         | C, DC, Z, OV, N   | 1, 2         |

| CODIN D   | i, u, u                         | Borrow                                   |            | 0101                    | rouu         |      |              | 0, 00, 2, 00, 1   | 1, 2         |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da         | ffff | ffff         | None              | 4            |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a         | ffff | ffff         | None              | 1, 2         |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da         | ffff | ffff         | Z, N              | 1, 2         |

|           |                                 | E REGISTER OPERATIONS                    | 1          | 0001                    | IUUA         | LLLL | LTTT         | Ζ, Ν              |              |

| BCF       | f, b, a                         | Bit Clear f                              | 1          | 1001                    | bbbc         | ffff | ffff         | None              | 1, 2         |

| BSF       | f, b, a                         | Bit Set f                                | 1          | 1001                    | bbba<br>bbba | ffff | ffff         | None              | 1, 2         |

| BTFSC     |                                 | Bit Test f, Skip if Clear                | 1 (2 or 3) |                         |              |      |              |                   | 1, 2<br>3, 4 |

| BTFSC     | f, b, a<br>f, b, a              |                                          | `` '       | 1011                    | bbba<br>bbba | ffff | ffff<br>ffff | None<br>None      | 3, 4<br>3, 4 |

|           | , ,                             | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010                    | bbba         | ffff |              |                   |              |

| BTG       | f, b, a                         | Bit Toggle f                             | 1          | 0111                    | bbba         | ffff | ffff         | None              | 1, 2         |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**4:** Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| SLE   | EP                       | Enter Sleep Mode                                               |                                      | SUE        | BFWB        | Subtract        | f from W w           | ith Borrow                               |                      |

|-------|--------------------------|----------------------------------------------------------------|--------------------------------------|------------|-------------|-----------------|----------------------|------------------------------------------|----------------------|

| Synta | ax:                      | [ label ] SLEEP                                                |                                      | Synta      | ax:         | [ label ]       | SUBFWB f             | [,d [,a]]                                |                      |

| Oper  | ands:                    | None                                                           |                                      |            | Oper        | Operands: 0 s   |                      | 5                                        |                      |

| Oper  | ation:                   | $00h \rightarrow WE$                                           | DT,                                  |            |             |                 | d ∈ [0,1]            |                                          |                      |

|       |                          |                                                                | postscaler,                          |            |             |                 | a ∈ [0,1]            | <del>.</del>                             |                      |

|       |                          | $1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD}$ |                                      |            | •           | ation:          |                      | $(\overline{C}) \rightarrow \text{dest}$ |                      |

| Statu | s Affected:              | TO, PD                                                         |                                      |            |             | is Affected:    | N, OV, C,            |                                          |                      |

|       |                          |                                                                | 0000 000                             | 0 0011     | Enco        | oding:          | 0101                 |                                          | ff ffff              |

| Enco  | U U                      | 0000                                                           |                                      |            | Desc        | ription:        |                      | egister, 'f', and                        |                      |

| Desc  | ription:                 |                                                                | r-Down status<br>he Time-out sta     |            |             |                 |                      | om W (2's con<br>f 'd' is '0', the r     |                      |

|       |                          | is set. Wat                                                    | tchdog Timer a                       |            |             |                 | in W. If 'd'         | is '1', the resu                         | t is stored in       |

|       |                          | scaler are                                                     |                                      | Sloop modo |             |                 |                      |                                          | Access Bank          |

|       |                          |                                                                | ssor is put into<br>scillator stoppe |            |             |                 |                      | ected, overridir<br>' is '1', then the   |                      |

| Word  | s:                       | 1                                                              |                                      |            |             |                 |                      | s per the BSR                            |                      |

| Cycle |                          | 1                                                              |                                      |            | Word        | ls:             | 1                    |                                          |                      |

| -     | ycle Activity:           | ·                                                              |                                      |            | Cycle       | es:             | 1                    |                                          |                      |

| Q U   | Q1                       | Q2                                                             | Q3                                   | Q4         | QC          | ycle Activity:  |                      |                                          |                      |

|       | Decode                   | No                                                             | Process                              | Go to      |             | Q1              | Q2                   | Q3                                       | Q4                   |

|       |                          | operation                                                      | Data                                 | Sleep      |             | Decode          | Read<br>register 'f' | Process<br>Data                          | Write to destination |

| Exam  | <u>nple:</u>             | SLEEP                                                          |                                      |            | Exan        | nple 1:         | SUBFWB 1             |                                          | 4000                 |

|       | Before Instruc           | ction                                                          |                                      |            |             | Before Instru   | ction                |                                          |                      |

|       | <u>TO</u> =              | ?                                                              |                                      |            |             | REG             | = 0x03               |                                          |                      |

|       | PD =                     | ?                                                              |                                      |            |             | W<br>C          | = 0x02<br>= 0x01     |                                          |                      |

|       | After Instructio<br>TO = | on<br>1†                                                       |                                      |            |             | After Instructi |                      |                                          |                      |