Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, Power Control PWM, QEI, POR, PWM, WDT         |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 9x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4431-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

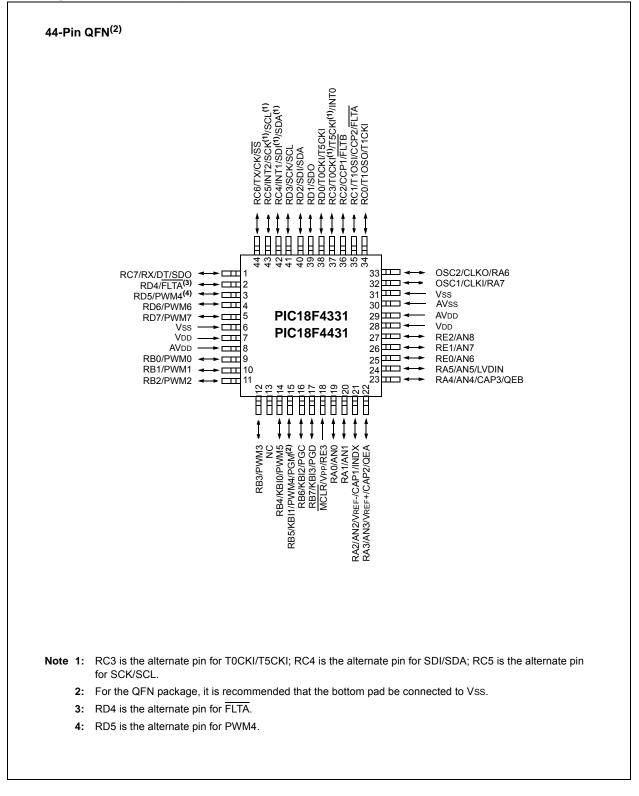

### **Pin Diagrams (Continued)**

## **Table of Contents**

| 20       Guidelines for Getting Started with PIC18F Microcontrollers.         30       Oscillator Configurations         40       Power-Managed Modes         50       Reset         60       Memory Organization         70       Data EEPROM Memory         80       Flash Program Memory         90       8 x 8 Hardware Multiplier.         100       Interrupts.         110       I/O Ports         120       Timert Module         130       Timert Module         140       Timerz Module         150       Timerf Module         161       Capture/Compare/PWM (CCP) Modules         170       Motion Feedback Module         180       Power Control PWM Module         190       Synchronous Serial Port (SSP) Module         201       Enhanced Universal Synchronous Receiver Transmitter (EUSART)         210       Instruction Set Lynch         211       U-Bit High-Speed Analog-to-Digital Converter (A/D) Module         222       Low-Voltage Detect (LVD)         233       Special Features of the CPU         240       Instruction Set Summary         250       Development Support.         260       Electrical Characteristics                                                                                                                                                                                                                       | 1.0   | Device Overview                                             |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------|-----|

| 4.0       Power-Managed Modes         50       Reset         60       Memory Organization         7.0       Data EEPROM Memory         80       Flash Program Memory         90       8 x 8 Hardware Multiplier         100       Interrupts         110       I/O Ports         120       Timer0 Module         130       Timer1 Module         140       Timer5 Module         150       Capture/Compare/PVM (CCP) Modules         161       Capture/Compare/PVM Module         170       Motion Feedback Module         180       Power Control PVM Module         190       Synchronous Serial Port (SSP) Module         201       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         210       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         220       Low-Voltage Detect (LVD)         230       Special Features of the CPU         240       Instruction Set Summary         250                                                                                                                                                                                                                                       | 2.0   | Guidelines for Getting Started with PIC18F Microcontrollers |     |

| 5.0       Reset         6.0       Memory Organization         7.0       Data EEPROM Memory         8.0       Flash Program Memory         9.0       8 x 8 Hardware Multiplier         10.0       Interrupts         11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer1 Module         16.0       Capture/Compare/PVM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PVM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       Low-Voltage Detect (LVD)         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information.         Appendix R: Revision History.         Appendix B: Device Differences.         Appendix C: Conversion Considerations         Appendix D: Migration from Mid-Range to E                                                                                                                                                                                                     | 3.0   | Oscillator Configurations                                   |     |

| 6.0       Memory Organization         7.0       Data EEPROM Memory         8.0       Flash Program Memory         9.0       8 x 8 Hardware Multiplier         10.0       Interrupts         11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Receiver Transmitter (EUSART)         21.0       10-Bit High>Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History         Appendix B: Device Differences         Appendix B: Device Differences         Appendix C: Conversion Considerations         Appendix D: Migrat                                                                                                                                                                                            | 4.0   | Power-Managed Modes                                         |     |

| 7.0       Data ÉEPRÓM Memory         8.0       Flash Program Memory         9.0       8 x 8 Hardware Multiplier         10.0       Interrupts         11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer1 Module         15.0       Timer1 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix R: Nevision History,         Appendix R: Neigration From Mid-Range to Enhanced Devices.         Appendix D: Migration From Mid-Range to Enhanced Devices.         Appendix F: Migration From Mid-Range to Enhanced Devices.         Appendix F: Mig                                                                                                                                                         | 5.0   | Reset                                                       |     |

| <ul> <li>8.0 Flash Program Memory</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.0   | Memory Organization                                         | 61  |

| 9.0       8 x 8 Hardware Multiplier.         10.0       Interrupts         11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       Io-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Delectrical Characteristics         27.0       Packaging Information         Appendix A: Revision History         Appendix C Conversion Considerations         Appendix C: Conversion Considerations         Appendix C: Migration From Mid-Range to Enhanced Devices         Appendix C: Migration From High-End to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices         Appendix                                                                                                                                        | 7.0   | Data EEPROM Memory                                          |     |

| 10.0       Interrupts         11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix B: Device Differences.         Appendix C: Conversion Considerations.         Appendix C: Conversion Considerations.         Appendix D: Migration from Baseline to Enhanced Devices.         Appendix F: Migration From Mid-Range to Enhanced Devices.         Appendix F: Migration From Mid-Range to Enhanced Devices.         Appendix F: Migration From Migh-End to Enhanced Devices.                                                                                                                            | 8.0   | Flash Program Memory                                        | 85  |

| 11.0       I/O Ports         12.0       Timer0 Module         13.0       Timer1 Module         13.0       Timer2 Module         15.0       Timer5 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix C Conversion Considerations         Appendix C: Conversion Considerations       Appendix C Conversion Considerations         Appendix C: Migration from Baseline to Enhanced Devices       Appendix F Migration From High-End to Enhanced Devices         NDEX       Mitorcohip Web Site       Mitorcohip Web Site         Customer Change Notification Service       Cust                                                                                                      | 9.0   | 8 x 8 Hardware Multiplier                                   |     |

| 12.0       Timer0 Module         13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix B: Device Differences       Appendix B: Device Differences         Appendix B: Device Differences       Appendix C: Conversion Considerations         Appendix B: Migration From Mid-Range to Enhanced Devices       Appendix E: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       Appendix E: Migration From High-End to Enhanced Devices         INDEX       The Microchip Web Site       Customer Change Notification Service         Customer Suppo                                                          | 10.0  | Interrupts                                                  |     |

| 13.0       Timer1 Module         14.0       Timer2 Module         15.0       Timer5 Module         15.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix R: Revision History       Appendix R         Appendix B: Device Differences       Appendix C Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix E         Appendix F: Migration From Mid-Range to Enhanced Devices       Appendix E         NDEX       The Microchip Web Site       Customer Change Notification Service         Customer Support       Customer Support       Reader Response                                                                                                                                                               | 11.0  | I/O Ports                                                   | 113 |

| 14.0       Timer2 Module         15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART).         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD).         23.0       Special Features of the CPU         24.0       Instruction Set Summary.         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information.         Appendix A: Revision History.         Appendix A: Revision History.         Appendix B: Device Differences.         Appendix C: Conversion Considerations         Appendix C: Conversion Considerations         Appendix F: Migration From Mid-Range to Enhanced Devices.         Appendix F: Migration From High-End to Enhanced Devices.         Appendix F: Migration From High-End to Enhanced Devices.         NDEX.         The Microchip Web Site         Customer Change Notification                                                                                                   |       |                                                             |     |

| 15.0       Timer5 Module         16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History         Appendix A: Revision History         Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices         Appendix F: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices         Customer Change Notification Service         Customer Change Notification Service         Customer Support </td <td>13.0</td> <td>Timer1 Module</td> <td> 131</td> | 13.0  | Timer1 Module                                               | 131 |

| 16.0       Capture/Compare/PWM (CCP) Modules         17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix A: Revision History         Appendix B: Device Differences.       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices.       Appendix E: Migration From High-End to Enhanced Devices.         Appendix F: Migration From High-End to Enhanced Devices       Appendix F: Migration From High-End to Enhanced Devices         INDEX       The Microchip Web Site       Customer Change Notification Service         Customer Change Notification Service       Customer Support         Reader Response       Service       Service                                                                                               | 14.0  | Timer2 Module                                               | 136 |

| 17.0       Motion Feedback Module         18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix B: Device Differences         Appendix C: Conversion Considerations       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix F: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       INDEX         The Microchip Web Site       Customer Change Notification Service         Customer Support       Customer Support         Reader Response       Mideation Service                                                                                                                                                                                                                                   |       |                                                             |     |

| 18.0       Power Control PWM Module         19.0       Synchronous Serial Port (SSP) Module         20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix A: Revision History         Appendix C: Conversion Considerations       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix F: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       INDEX         The Microchip Web Site       Customer Change Notification Service         Customer Change Notification Service       Customer Support         Reader Response       Reader Response                                                                                                                                                                                                                                                              |       |                                                             |     |

| 19.0       Synchronous Serial Port (SSP) Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                             |     |

| 20.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)         21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix A: Revision History         Appendix B: Device Differences       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix E: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       INDEX         The Microchip Web Site       Customer Change Notification Service         Customer Change Notification Service       Customer Support         Reader Response       Service                                                                                                                                                                                                                                                                                                                                                                                 |       |                                                             |     |

| 21.0       10-Bit High-Speed Analog-to-Digital Converter (A/D) Module         22.0       Low-Voltage Detect (LVD)         23.0       Special Features of the CPU         24.0       Instruction Set Summary         25.0       Development Support.         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix B: Device Differences.         Appendix B: Device Differences       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix E: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       INDEX         The Microchip Web Site       Customer Change Notification Service         Customer Support       Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                             |     |

| 22.0 Low-Voltage Detect (LVD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                             |     |

| 23.0 Special Features of the CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21.0  | 10-Bit High-Speed Analog-to-Digital Converter (A/D) Module  |     |

| 24.0       Instruction Set Summary         25.0       Development Support         26.0       Electrical Characteristics         27.0       Packaging Information         Appendix A: Revision History       Appendix B: Device Differences         Appendix B: Device Differences       Appendix C: Conversion Considerations         Appendix D: Migration from Baseline to Enhanced Devices       Appendix E: Migration From Mid-Range to Enhanced Devices         Appendix F: Migration From High-End to Enhanced Devices       INDEX         The Microchip Web Site       Customer Change Notification Service         Customer Support       Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | •                                                           |     |

| 25.0 Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                             |     |

| 26.0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24.0  | Instruction Set Summary                                     | 283 |

| 27.0 Packaging Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25.0  | Development Support                                         |     |

| Appendix A: Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                             |     |

| Appendix B: Device Differences<br>Appendix C: Conversion Considerations<br>Appendix D: Migration from Baseline to Enhanced Devices<br>Appendix E: Migration From Mid-Range to Enhanced Devices<br>Appendix F: Migration From High-End to Enhanced Devices<br>INDEX<br>The Microchip Web Site<br>Customer Change Notification Service<br>Customer Support<br>Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27.0  | Packaging Information                                       |     |

| Appendix C: Conversion Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | ,                                                           |     |

| Appendix D: Migration from Baseline to Enhanced Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                             |     |

| Appendix E: Migration From Mid-Range to Enhanced Devices<br>Appendix F: Migration From High-End to Enhanced Devices<br>INDEX<br>The Microchip Web Site<br>Customer Change Notification Service<br>Customer Support<br>Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Appe  | ndix C: Conversion Considerations                           |     |

| Appendix F: Migration From High-End to Enhanced Devices<br>INDEX<br>The Microchip Web Site<br>Customer Change Notification Service<br>Customer Support<br>Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | •                                                           |     |

| INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                                                             |     |

| The Microchip Web Site<br>Customer Change Notification Service<br>Customer Support<br>Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Appe  | ndix F: Migration From High-End to Enhanced Devices         |     |

| Customer Change Notification Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INDE  | X                                                           |     |

| Customer Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                                                             |     |

| Reader Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                             |     |

| Product Identification System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Produ | uct Identification System                                   | 391 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

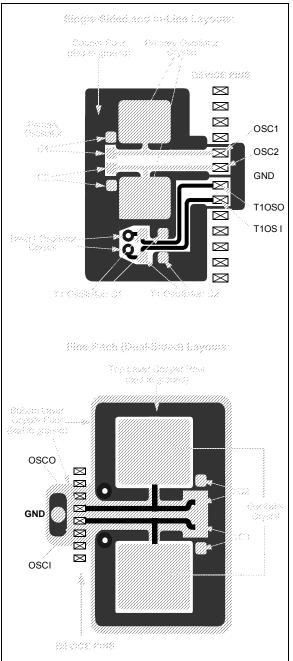

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

## 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| R/W-0         | R/W-0                                                                                                    | R/W-0                                                  | R/W-0            | R <sup>(1)</sup>                                                  | R-0              | R/W-0           | R/W-0 |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|-------------------------------------------------------------------|------------------|-----------------|-------|

| IDLEN         | IRCF2                                                                                                    | IRCF1                                                  | IRCF0            | OSTS                                                              | IOFS             | SCS1            | SCS0  |

| bit 7         |                                                                                                          |                                                        |                  |                                                                   |                  | •               | bit 0 |

| Legend:       |                                                                                                          |                                                        |                  |                                                                   |                  |                 |       |

| R = Readabl   | e bit                                                                                                    | W = Writable                                           | bit              | U = Unimpler                                                      | nented bit, read | d as '0'        |       |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                                       |                  | '0' = Bit is clea                                                 | ared             | x = Bit is unkr | iown  |

| bit 7         |                                                                                                          | le enabled; CPl                                        |                  | ocked in power-<br>ked in power-ma                                | •                | les             |       |

| bit 6-4       | 111 = 8 MHz<br>110 = 4 MHz<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kH<br>010 = 250 kH<br>001 = 125 kH | z<br>z<br>Hz<br>Hz                                     | e drives clock o | directly)                                                         |                  |                 |       |

| bit 3         | 1 = Oscillato                                                                                            |                                                        | r time-out has   | Status bit <sup>(1)</sup><br>expired; primar<br>inning; primary o |                  | U U             |       |

| bit 2         | 1 = INTOSC                                                                                               | SC Frequency S<br>frequency is st<br>frequency is no   | able             |                                                                   |                  |                 |       |

| bit 1-0       | 1x = Internal                                                                                            | System Clock So<br>oscillator block<br>ary (Timer1) os |                  |                                                                   |                  |                 |       |

### REGISTER 3-2: OSCCON: OSCILLATOR CONTROL REGISTER

2: Default output frequency of INTOSC on Reset.

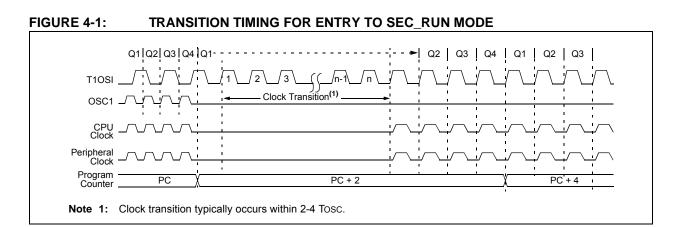

### 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer. In this mode, the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive or do not require high-speed clocks at all times.

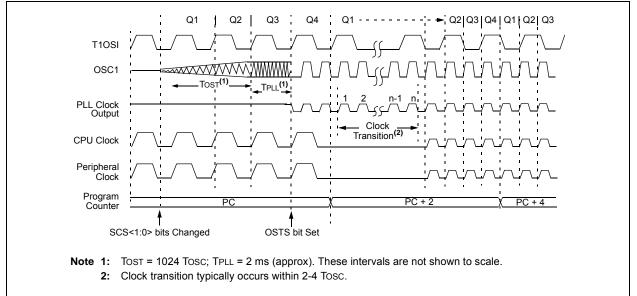

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

## 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte (PCH register) contains the PC<15:8> bits and is not directly readable or writable.

Updates to the PCH register are performed through the PCLATH register. The upper byte is the PCU register and contains the bits, PC<20:16>. This register is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes to the PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO**").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of the PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, with the Stack Pointer initialized to 00000b after all Resets. There is no RAM associated with Stack Pointer, 00000b. This is only a Reset value. During a CALL type instruction, causing a push onto the stack, the Stack Pointer is first incremented and the RAM location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction, causing a pop from the stack, the contents of the RAM location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The stack space is not part of either program or data space. The Stack Pointer is readable and writable, and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from, the stack using the Top-of-Stack SFRs. Status bits indicate if the stack is full, has overflowed or underflowed.

### 6.1.2.1 Top-of-Stack Access

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

## 6.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. At Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 23.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

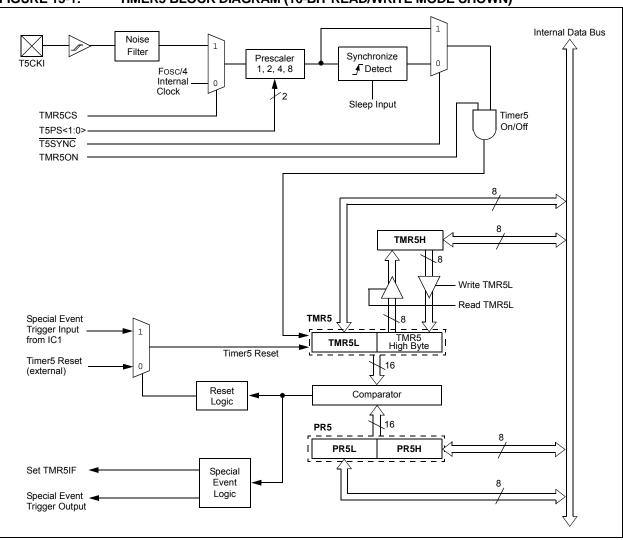

### FIGURE 15-1: TIMER5 BLOCK DIAGRAM (16-BIT READ/WRITE MODE SHOWN)

## 15.1 Timer5 Operation

Timer5 combines two 8-bit registers to function as a 16-bit timer. The TMR5L register is the actual low byte of the timer; it can be read and written to directly. The high byte is contained in an unmapped register; it is read and written to through TMR5H, which serves as a buffer. Each register increments from 00h to FFh.

A second register pair, PR5H and PR5L, serves as the Period register; it sets the maximum count for the TMR5 register pair. When TMR5 reaches the value of PR5, the timer rolls over to 00h and sets the TMR5IF interrupt flag. A simplified block diagram of the Timer5 module is shown in Figure 2-1.

| Note: |      |            | nay be used   |             |          |

|-------|------|------------|---------------|-------------|----------|

|       | pose | e timer an | d as the time | base reso   | ource to |

|       | the  | Motion     | Feedback      | Module      | (Input   |

|       | Capt | ure or Qu  | adrature En   | coder Inter | rface).  |

Timer5 supports three configurations:

- 16-Bit Synchronous Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

In Synchronous Timer configuration, the timer is clocked by the internal device clock. The optional Timer5 prescaler divides the input by 2, 4, 8 or not at all (1:1). The TMR5 register pair increments on Q1. Clearing TMR5CS (= 0) selects the internal device clock as the timer sampling clock.

| R/W-0        | R/W-0                                      | R/W-0                | R/W-0           | R/W-0                                               | U-0              | R/W-0           | R/W-0 |

|--------------|--------------------------------------------|----------------------|-----------------|-----------------------------------------------------|------------------|-----------------|-------|

| SEVOPS3      | SEVOPS2                                    | SEVOPS1              | SEVOPS0         | SEVTDIR                                             | —                | UDIS            | OSYNC |

| bit 7        |                                            |                      |                 |                                                     |                  |                 | bit 0 |

| Legend:      |                                            |                      |                 |                                                     |                  |                 |       |

| R = Readab   | le bit                                     | W = Writable I       | bit             | U = Unimplem                                        | nented bit, read | as '0'          |       |

| -n = Value a | t POR                                      | '1' = Bit is set     |                 | '0' = Bit is clea                                   | ared             | x = Bit is unkn | own   |

| bit 7-4      | SEVOPS<3:0<br>0000 = 1:1 P<br>0001 = 1:2 P | ostscale<br>ostscale | n Event mgge    | r Output Postsc                                     |                  |                 |       |

| bit 3        | 1 = A Special                              | ••                   | will occur wher | e Direction bit<br>I the PWM time<br>I the PWM time |                  | •               |       |

| bit 2        | Unimplement                                | ted: Read as '0      | ,               |                                                     |                  |                 |       |

| bit 1        | UDIS: PWM L                                | Jpdate Disable       | bit             |                                                     |                  |                 |       |

|              | •                                          |                      |                 | uffer registers a<br>uffer registers a              |                  |                 |       |

| bit 0        | OSYNC: PWN                                 | / Output Overri      | de Synchroniz   | ation bit                                           |                  |                 |       |

|              |                                            |                      | 0               | ster are synchro<br>ster are asynch                 |                  | WM time base    |       |

#### REGISTER 18-4: PWMCON1: PWM CONTROL REGISTER 1

18.3.1 FREE-RUNNING MODE

In the Free-Running mode, the PWM Time Base registers (PTMRL and PTMRH) will begin counting upwards until the value in the PWM Time Base Period register, PTPER (PTPERL and PTPERH), is matched. The PTMR registers will be reset on the following input clock edge and the time base will continue counting upwards as long as the PTEN bit remains set.

### 18.3.2 SINGLE-SHOT MODE

In the Single-Shot mode, the PWM time base will begin counting upwards when the PTEN bit is set. When the value in the PTMR register matches the PTPER register, the PTMR register will be reset on the following input clock edge and the PTEN bit will be cleared by the hardware to halt the time base.

#### 18.3.3 CONTINUOUS UP/DOWN COUNT MODES