Welcome to **E-XFL.COM**

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 12MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LVD, POR, WDT                                                              |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                               |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c20134-12sxi |

# **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and by lowering inventory costs. These configurable resources, called PSoC Blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is summarized in four steps:

- 1. Select User Modules.

- 2. Configure User Modules.

- 3. Organize and Connect.

- 4. Generate, Verify, and Debug.

### **Select User Modules**

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

#### **Configure User Modules**

Each user module that you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a PWM User Module configures one or more digital PSoC blocks, one for each 8 bits of resolution. The user module parameters permit you to establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the user module and provide performance specifications. Each datasheet describes the use of each user module parameter, and other information you may need to successfully implement your design.

### **Organize and Connect**

You build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. You perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, you perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides application programming interfaces (APIs) with high-level functions to control and respond to hardware events at run-time and interrupt service routines that you can adapt as needed.

A complete code development environment allows you to develop and customize your applications in either C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's debugger (access by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint, and watch-variable features, the debug interface provides a large trace buffer and allows you to define complex breakpoint events. These include monitoring address and data bus values, memory locations, and external signals.

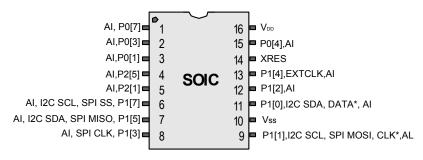

# **16-Pin SOIC Pinout**

Figure 4. CY8C20234-12SXI 16-Pin SOIC Pinout

Table 3. Pin Definitions - CY8C20234 16-Pin (SOIC)

| Pin No. | Digital | Analog | Name     | Description                                                     |

|---------|---------|--------|----------|-----------------------------------------------------------------|

| 1       | I/O     | I      | P0[7]    | Analog column mux input                                         |

| 2       | I/O     | I      | P0[3]    | Analog column mux input and column input, integrating input     |

| 3       | I/O     | I      | P0[1]    | Analog column mux input, integrating input                      |

| 4       | I/O     | I      | P2[5]    | Analog column mux input                                         |

| 5       | I/O     | I      | P2[1]    | Analog column mux input                                         |

| 6       | I/O     | I      | P1[7]    | I2C serial clock (SCL), SPI SS                                  |

| 7       | I/O     | I      | P1[5]    | I2C serial data (SDA),SPI MISO                                  |

| 8       | I/O     | I      | P1[3]    | Analog column mux input, SPI CLK                                |

| 9       | I/O     | I      | P1[1]    | I2C serial clock (SCL), ISSP-SCLK,SPI MOSI                      |

| 10      | Power   | •      | $V_{SS}$ | Ground connection                                               |

| 11      | I/O     | I      | P1[0]    | I2C serial data (SDA), ISSP-SDATA                               |

| 12      | I/O     | I      | P1[2]    | Analog column mux input                                         |

| 13      | I/O     | I      | P1[4]    | Analog column mux input, optional external clock input (EXTCLK) |

| 14      | I/O     | I      | XRES     | XRES                                                            |

| 15      | I/O     | I      | P0[4]    | Analog column mux input                                         |

| 16      | Power   | -      | $V_{DD}$ | Supply voltage                                                  |

A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive.

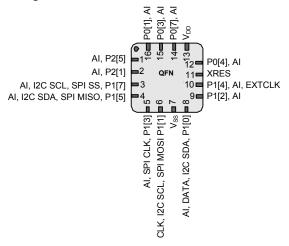

## **16-Pin Part Pinout**

Figure 6. CY8C20234 16-Pin PSoC Device

Table 5. Pin Definitions - CY8C20234 16-Pin (QFN no e-pad)

| Pin No.  | T               | уре    | Name     | Description                                         |  |  |  |  |

|----------|-----------------|--------|----------|-----------------------------------------------------|--|--|--|--|

| FIII NO. | Digital         | Analog | Ivallie  | Description                                         |  |  |  |  |

| 1        | I/O             | Į      | P2[5]    |                                                     |  |  |  |  |

| 2        | I/O             | Į      | P2[1]    |                                                     |  |  |  |  |

| 3        | I <sub>OH</sub> | I      | P1[7]    | I <sup>2</sup> C SCL, SPI SS                        |  |  |  |  |

| 4        | I <sub>OH</sub> | I      | P1[5]    | I <sup>2</sup> C SDA, SPI MISO                      |  |  |  |  |

| 5        | I <sub>OH</sub> | I      | P1[3]    | SPI CLK                                             |  |  |  |  |

| 6        | I <sub>OH</sub> | I      | P1[1]    | CLK <sup>[6]</sup> , I <sup>2</sup> C SCL, SPI MOSI |  |  |  |  |

| 7        | Power           |        | $V_{SS}$ | Ground connection                                   |  |  |  |  |

| 8        | I <sub>OH</sub> | I      | P1[0]    | DATA <sup>[6]</sup> , I <sup>2</sup> C SDA          |  |  |  |  |

| 9        | I <sub>OH</sub> | I      | P1[2]    |                                                     |  |  |  |  |

| 10       | I <sub>OH</sub> | Į      | P1[4]    | Optional external clock input (EXTCLK)              |  |  |  |  |

| 11       | Input           | •      | XRES     | Active high external reset with internal pull-down  |  |  |  |  |

| 12       | I/O             | I      | P0[4]    |                                                     |  |  |  |  |

| 13       | Power           |        | $V_{DD}$ | Supply voltage                                      |  |  |  |  |

| 14       | I/O             | I      | P0[7]    |                                                     |  |  |  |  |

| 15       | I/O             | I      | P0[3]    | Integrating Input                                   |  |  |  |  |

| 16       | I/O             | I      | P0[1]    |                                                     |  |  |  |  |

A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive

<sup>6.</sup> These are the ISSP pins, that are not High Z at POR (Power-on-Reset). See the PSoC Technical Reference Manual for details.

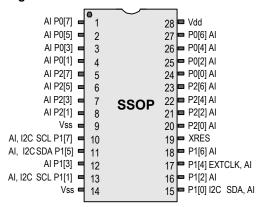

## 28-Pin Part Pinout

Figure 9. CY8C20534 28-Pin PSoC Device

Table 8. Pin Definitions - CY8C20534 28-Pin (SSOP)

|         | ype    | Name     | Description                                                  |

|---------|--------|----------|--------------------------------------------------------------|

| Digital | Analog | Name     | Description                                                  |

| I/O     | I      | P0[7]    | Analog column mux input                                      |

| I/O     | I      | P0[5]    | Analog column mux input and column output                    |

| I/O     | I      | P0[3]    | Analog column mux input and column output, integrating input |

| I/O     | I      | P0[1]    | Analog column mux input, integrating input                   |

| I/O     | I      | P2[7]    |                                                              |

| I/O     | I      | P2[5]    |                                                              |

| I/O     | I      | P2[3]    | Direct switched capacitor block input                        |

| I/O     | I      | P2[1]    | Direct switched capacitor block input                        |

| Power   | ı      | $V_{SS}$ | Ground connection <sup>[13]</sup>                            |

| I/O     | I      | P1[7]    | I2C serial clock (SCL)                                       |

| I/O     | I      | P1[5]    | I2C serial data (SDA)                                        |

| I/O     | I      | P1[3]    |                                                              |

| I/O     | I      | P1[1]    | I2C serial clock (SCL), ISSP-SCLK <sup>[14]</sup>            |

| Power   |        | $V_{SS}$ | Ground connection                                            |

| I/O     | I      | P1[0]    | I2C serial data (SDA), ISSP-SDATA <sup>[14]</sup>            |

| I/O     | I      | P1[2]    |                                                              |

| I/O     | I      | P1[4]    | Optional external clock input (EXTCLK)                       |

| I/O     | I      | P1[6]    |                                                              |

| Input   | •      | XRES     | Active high external reset with internal pull-down           |

| I/O     | I      | P2[0]    | Direct switched capacitor block input                        |

| I/O     | I      | P2[2]    | Direct switched capacitor block input                        |

| I/O     | I      | P2[4]    |                                                              |

| I/O     | I      | P2[6]    |                                                              |

| I/O     | I      | P0[0]    | Analog column mux input                                      |

| I/O     | I      | P0[2]    | Analog column mux input                                      |

| I/O     | I      | P0[4]    | Analog column mux input                                      |

| I/O     | I      | P0[6]    | Analog column mux input                                      |

| Power   | •      | $V_{DD}$ | Supply voltage                                               |

|         | I/O    | /O       | Digital   Analog                                             |

A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive.

#### Notes

<sup>13.</sup> All  $V_{SS}$  pins should be brought out to one common GND plane.

<sup>14.</sup> These are the ISSP pins, that are not High Z at POR (Power-on-Reset). See the PSoC Technical Reference Manual for details.

Table 13. 5-V and 3.3-V DC GPIO Specifications

| Symbol            | Description                                                         | Min | Тур | Max  | Units | Notes                                                                                                                                                                                      |

|-------------------|---------------------------------------------------------------------|-----|-----|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OH7</sub>  | High output voltage<br>Port 1 pins with 2.4 V LDO regulator enabled | 2.1 | 2.4 | 2.7  | V     | $I_{OH}\!<\!10\mu\text{A}, V_{DD}\!\ge\!3.0\text{V}$ , maximum of 20 mA source current in all I/Os.                                                                                        |

| V <sub>OH8</sub>  | High output voltage<br>Port 1 pins with 2.4 V LDO regulator enabled | 2.0 | _   | _    | V     | $I_{OH}$ < 200 μA, $V_{DD} \ge$ 3.0 V, maximum of 20 mA source current in all I/Os.                                                                                                        |

| V <sub>OH9</sub>  | High output voltage<br>Port 1 pins with 1.8 V LDO regulator enabled | 1.6 | 1.8 | 2.0  | V     | $I_{OH}$ < 10 $\mu A$ $3.0 V \le V_{DD} \le 3.6 \ V$ $0 \ ^{\circ}C \le T_A \le 85 \ ^{\circ}C$ Maximum of 20 mA source current in all I/Os.                                               |

| V <sub>OH10</sub> | High output voltage<br>Port 1 pins with 1.8 V LDO regulator enabled | 1.5 | _   | _    | V     | $I_{OH}$ < 100 μA.<br>3.0V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V.<br>0 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C.<br>Maximum of 20 mA source current in all I/Os.                                |

| V <sub>OL</sub>   | Low output voltage                                                  | -   | -   | 0.75 | V     | $I_{OL}$ = 20 mA, $V_{DD}$ > 3.0 V, maximum of 60 mA sink current on even port pins (for example, P0[2] and P1[4]) and 60 mA sink current on odd port pins (for example, P0[3] and P1[5]). |

| I <sub>OH</sub>   | High level source current                                           | _   | -   | 20   | mA    | $V_{OH} = V_{DD} - 0.9$ . See the limitations of the total current in the Notes for $V_{OH}$ .                                                                                             |

| I <sub>OH2</sub>  | High level source current port 0, 2, or 3 pins                      | 1   | _   | _    | mA    | $V_{OH}$ = $V_{DD}$ – 0.9, for the limitations of the total current and $I_{OH}$ at other $V_{OH}$ levels, see the Notes for $V_{OH}$ .                                                    |

| I <sub>OH4</sub>  | High level source current port 1 Pins with LDO regulator disabled   | 5   | _   | _    | mA    | $V_{OH}$ = $V_{DD}$ – 0.9, for the limitations of the total current and $I_{OH}$ at other $V_{OH}$ levels, see the Notes for $V_{OH}$ .                                                    |

| I <sub>OL</sub>   | Low level sink current                                              | 20  | _   | _    | mA    | $V_{OL}$ = 0.75 V, see the limitations of the total current in the Notes for $V_{OL}$                                                                                                      |

| V <sub>IL</sub>   | Input low voltage                                                   | _   | _   | 0.8  | V     | $3.6~V \leq V_{DD} \leq 5.25~V$                                                                                                                                                            |

| V <sub>IH</sub>   | Input high voltage                                                  | 2.0 | _   | _    | V     | $3.6 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$                                                                                                                                       |

| V <sub>H</sub>    | Input hysteresis voltage                                            |     | 140 | _    | mV    |                                                                                                                                                                                            |

| I <sub>IL</sub>   | Input leakage (absolute value)                                      |     | 1   | _    | nA    | Gross tested to 1 µA                                                                                                                                                                       |

| C <sub>IN</sub>   | Capacitive load on pins as input                                    | 0.5 | 1.7 | 5    | pF    | Package and pin dependent<br>Temperature = 25 °C                                                                                                                                           |

| C <sub>OUT</sub>  | Capacitive load on pins as output                                   | 0.5 | 1.7 | 5    | pF    | Package and pin dependent<br>Temperature = 25 °C                                                                                                                                           |

Document Number: 001-05356 Rev. \*T Page 21 of 50

# DC Programming Specifications

Table 17 lists the guaranteed minimum and maximum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , 3.0 V to 3.6 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , or 2.4 V to 3.0 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at 25 °C. These are for design guidance only. Flash endurance and retention specifications with the use of the EEPROM User Module are valid only within the range: 25 °C +/-20 C during the Flash Write operation. Reference the EEPROM User Module datasheet instructions for EEPROM flash write requirements outside of the 25 °C +/-20 °C temperature window.

**Table 17. DC Programming Specifications**

| Symbol                | Description                                                                                 | Min                    | Тур | Max                    | Units | Notes                                                                                  |

|-----------------------|---------------------------------------------------------------------------------------------|------------------------|-----|------------------------|-------|----------------------------------------------------------------------------------------|

| $V_{\mathrm{DDP}}$    | V <sub>DD</sub> for programming and erase                                                   | 4.5                    | 5   | 5.5                    | V     | This specification applies to the functional requirements of external programmer tools |

| $V_{DDLV}$            | Low V <sub>DD</sub> for verify                                                              | 2.4                    | 2.5 | 2.6                    | V     | This specification applies to the functional requirements of external programmer tools |

| $V_{\rm DDHV}$        | High $V_{DD}$ for verify                                                                    | 5.1                    | 5.2 | 5.3                    | V     | This specification applies to the functional requirements of external programmer tools |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                                    | 2.7                    | _   | 5.25                   | V     | This specification applies to this device when it is executing internal flash writes   |

| I <sub>DDP</sub>      | Supply current during programming or verify                                                 | _                      | 5   | 25                     | mA    |                                                                                        |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                              | _                      | _   | 0.8                    | V     |                                                                                        |

| V <sub>IHP</sub>      | Input high voltage during programming or verify                                             | 2.2                    | _   | _                      | V     |                                                                                        |

| I <sub>ILP</sub>      | Input current when applying V <sub>ILP</sub> to P1[0] or P1[1] during programming or verify | _                      | -   | 0.2                    | mA    | Driving internal pull-down resistor.                                                   |

| I <sub>IHP</sub>      | Input current when applying V <sub>IHP</sub> to P1[0] or P1[1] during programming or verify | _                      | -   | 1.5                    | mA    | Driving internal pull-down resistor.                                                   |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                             | _                      | -   | V <sub>SS</sub> + 0.75 | V     |                                                                                        |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                            | V <sub>DD</sub> – 1.0  | _   | $V_{DD}$               | V     |                                                                                        |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                                 | 50,000 <sup>[21]</sup> | _   | -                      | _     | Erase/write cycles per block.                                                          |

| Flash <sub>ENT</sub>  | Flash endurance (total)[20]                                                                 | 1,800,000              | _   | -                      | _     | Erase/write cycles.                                                                    |

| Flash <sub>DR</sub>   | Flash data retention                                                                        | 10                     | _   | _                      | Years |                                                                                        |

#### Notes

<sup>20.</sup> A maximum of 36 × 50,000 block endurance cycles is allowed. This is balanced between operations on 36 × 1 blocks of 50,000 maximum cycles each, 36 × 2 blocks of 25,000 maximum cycles each, or 36 × 4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36 × 50,000 and that no single block ever sees more than 50,000 cycles).

<sup>21.</sup> The 50,000 cycle flash endurance per block is only guaranteed if the flash is operating within one voltage range. Voltage ranges are 2.4 V to 3.0 V, 3.0 V to 3.6 V and 4.75 V to 5.25 V.

#### DC I<sup>2</sup>C Specifications

Table 18 lists the guaranteed minimum and maximum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , 3.0V to 3.6 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at 25 °C. These are for design guidance only. Flash endurance and retention specifications with the use of the EEPROM user module are valid only within the range: 25 °C +/-20C during the Flash Write operation. Reference the EEPROM User Module datasheet instructions for EEPROM flash Write requirements outside of the 25 °C +/-20 °C temperature window.

Table 18. DC I<sup>2</sup>C Specifications<sup>[22]</sup>

| Symbol             | Description      | Min                 | Тур | Max                  | Units | Notes                                                 |

|--------------------|------------------|---------------------|-----|----------------------|-------|-------------------------------------------------------|

| V <sub>ILI2C</sub> | Input low level  | -                   | _   | $0.3 \times V_{DD}$  | V     | $2.4 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$   |

|                    |                  | _                   | -   | $0.25 \times V_{DD}$ | V     | $4.75 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$ |

| V <sub>IHI2C</sub> | Input high level | $0.7 \times V_{DD}$ | _   | _                    | V     | $2.4 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$  |

#### **AC Electrical Characteristics**

#### AC Chip Level Specifications

Table 19, Table 20, and Table 21 list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , 3.0 V to 3.6 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , or 2.4 V to 3.0 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$  respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at 25 °C. These are for design guidance only.

Table 19. 5-V and 3.3-V AC Chip-Level Specifications

| Symbol                    | Description                                                                            | Min  | Тур | Max  | Units | Notes                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------|------|-----|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>CPU1</sub>         | CPU frequency (3.3 V nominal)                                                          | 0.75 | _   | 12.6 | MHz   | 12 MHz only for SLIMO Mode = 0.                                                                                                                                          |

| F <sub>32K1</sub>         | Internal low speed oscillator frequency                                                | 15   | 32  | 64   | kHz   |                                                                                                                                                                          |

| F <sub>32K_U</sub>        | Internal low speed oscillator (ILO) untrimmed frequency                                | 5    | _   | 100  | kHz   | After a reset and before the M8C starts to run, the ILO is not trimmed. See the System Resets section of the PSoC Technical Reference Manual for details on this timing. |

| F <sub>IMO12</sub>        | Internal main oscillator stability for 12 MHz (commercial temperature) <sup>[23]</sup> | 11.4 | 12  | 12.6 | MHz   | Trimmed for 3.3 V operation using factory trim values. See Figure 11 on page 19, SLIMO mode = 0.                                                                         |

| F <sub>IMO6</sub>         | Internal main oscillator stability for 6 MHz (commercial temperature)                  | 5.5  | 6.0 | 6.5  | MHz   | Trimmed for 3.3 V operation using factory trim values. See Figure 11 on page 19, SLIMO mode = 1.                                                                         |

| DC <sub>IMO</sub>         | Duty cycle of IMO                                                                      | 40   | 50  | 60   | %     |                                                                                                                                                                          |

| DC <sub>ILO</sub>         | Internal low speed oscillator duty cycle                                               | 20   | 50  | 80   | %     |                                                                                                                                                                          |

| t <sub>XRST</sub>         | External reset pulse width                                                             | 10   | _   | -    | μS    |                                                                                                                                                                          |

| t <sub>POWERUP</sub>      | Time from end of POR to CPU executing code                                             | _    | 16  | 100  | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                           |

| SR <sub>POWER_UP</sub>    | Power supply slew rate                                                                 | _    | _   | 250  | V/ms  |                                                                                                                                                                          |

| t <sub>jit_IMO</sub> [24] | 12 MHz IMO cycle-to-cycle jitter (RMS)                                                 | -    | 200 | 1600 | ps    |                                                                                                                                                                          |

| _                         | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)                                     | _    | 600 | 1400 | ps    | N = 32                                                                                                                                                                   |

|                           | 12 MHz IMO period jitter (RMS)                                                         | -    | 100 | 900  | ps    |                                                                                                                                                                          |

<sup>22.</sup> All GPIO meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO Specifications sections. The I<sup>2</sup>C GPIO pins also meet the above specs. 23.0 to 70 °C ambient, V<sub>DD</sub> = 3.3 V.

24. Refer to Cypress Jitter Specifications Application Note – AN5054 at http://www.cypress.com for more information.

Table 20. 2.7-V AC Chip Level Specifications

| Symbol                    | Description                                                       | Min  | Тур | Max  | Units | Notes                                                                                                                                                                    |

|---------------------------|-------------------------------------------------------------------|------|-----|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>CPU1</sub>         | CPU Frequency (2.7 V nominal)                                     | 0.75 | -   | 3.25 | MHz   | SLIMO mode = 0                                                                                                                                                           |

| F <sub>32K1</sub>         | Internal low speed oscillator frequency                           | 8    | 32  | 96   | kHz   |                                                                                                                                                                          |

| F <sub>32K_U</sub>        | Internal low speed oscillator (ILO) untrimmed frequency           | 5    | ı   | 100  | kHz   | After a reset and before the M8C starts to run, the ILO is not trimmed. See the System Resets section of the PSoC Technical Reference Manual for details on this timing. |

| F <sub>IMO12</sub>        | IMO stability for 12 MHz (commercial temperature) <sup>[25]</sup> | 11.0 | 12  | 12.9 | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 11 on page 19, SLIMO mode = 0.                                                                         |

| F <sub>IMO6</sub>         | IMO stability for 6 MHz<br>(commercial temperature)               | 5.5  | 6.0 | 6.5  | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 11 on page 19, SLIMO mode = 1.                                                                         |

| DC <sub>IMO</sub>         | Duty cycle of IMO                                                 | 40   | 50  | 60   | %     |                                                                                                                                                                          |

| DC <sub>ILO</sub>         | Internal low speed oscillator duty cycle                          | 20   | 50  | 80   | %     |                                                                                                                                                                          |

| t <sub>XRST</sub>         | External reset pulse width                                        | 10   | _   | -    | μs    |                                                                                                                                                                          |

| t <sub>POWERUP</sub>      | Time from end of POR to CPU executing code                        | -    | 16  | 100  | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC Technical<br>Reference Manual                                                                            |

| SR <sub>POWER_UP</sub>    | Power supply slew rate                                            | -    | _   | 250  | V/ms  |                                                                                                                                                                          |

| t <sub>JIT_IMO</sub> [26] | 12 MHz IMO cycle-to-cycle jitter (RMS)                            | _    | 500 | 900  | ps    |                                                                                                                                                                          |

|                           | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)                | _    | 800 | 1400 | ps    | N = 32                                                                                                                                                                   |

|                           | 12 MHz IMO period jitter (RMS)                                    | _    | 300 | 500  | ps    |                                                                                                                                                                          |

### AC Programming Specifications

Table 28 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , 3.0 V to 3.6 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , or 2.4 V to 3.0 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$  respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at 25 °C. These are for design guidance only.

**Table 28. AC Programming Specifications**

| Symbol                    | Description                                | Min | Тур | Max | Units | Notes                                          |

|---------------------------|--------------------------------------------|-----|-----|-----|-------|------------------------------------------------|

| t <sub>RSCLK</sub>        | Rise time of SCLK                          | 1   | _   | 20  | ns    |                                                |

| t <sub>FSCLK</sub>        | Fall time of SCLK                          | 1   | _   | 20  | ns    |                                                |

| t <sub>SSCLK</sub>        | Data setup time to falling edge of SCLK    | 40  | _   | _   | ns    |                                                |

| t <sub>HSCLK</sub>        | Data hold time from falling edge of SCLK   | 40  | _   | _   | ns    |                                                |

| F <sub>SCLK</sub>         | Frequency of SCLK                          | 0   | _   | 8   | MHz   |                                                |

| t <sub>ERASEB</sub>       | Flash erase time (Block)                   | _   | 10  | _   | ms    |                                                |

| t <sub>WRITE</sub>        | Flash block write time                     | _   | 40  | _   | ms    |                                                |

| t <sub>DSCLK</sub>        | Data out delay from falling edge of SCLK   | _   | _   | 45  | ns    | 3.6 < V <sub>DD</sub>                          |

| t <sub>DSCLK3</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 50  | ns    | $3.0 \le V_{DD} \le 3.6$                       |

| t <sub>DSCLK2</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 70  | ns    | $2.4 \le V_{DD} \le 3.0$                       |

| t <sub>ERASEALL</sub>     | Flash erase time (Bulk)                    | _   | 20  | _   | ms    | Erase all blocks and protection fields at once |

| t <sub>PROGRAM_HOT</sub>  | Flash block erase + flash block write time | _   | _   | 100 | ms    | 0 °C ≤ T <sub>j</sub> ≤ 100 °C                 |

| t <sub>PROGRAM_COLD</sub> | Flash block erase + flash block write time | _   | _   | 200 | ms    | –40 °C ≤ T <sub>j</sub> ≤ 0 °C                 |

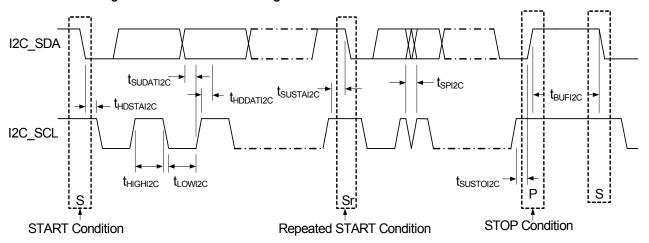

# AC I<sup>2</sup>C Specifications

Table 29 and Table 30 list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 ^{\circ}\text{C} \leq \text{T}_{A} \leq 85 ^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40 ^{\circ}\text{C} \leq \text{T}_{A} \leq 85 ^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40 ^{\circ}\text{C} \leq \text{T}_{A} \leq 85 ^{\circ}\text{C}$  respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at  $25 ^{\circ}\text{C}$ . These are for design guidance only.

Table 29. AC Characteristics of the I<sup>2</sup>C SDA and SCL Pins for  $V_{DD} \ge 3.0 \text{ V}$

| Cumbal                | Description                                                                                 | Standa | rd Mode | Fast                | Units |       |

|-----------------------|---------------------------------------------------------------------------------------------|--------|---------|---------------------|-------|-------|

| Symbol                | Description                                                                                 | Min    | Max     | Min                 | Max   | Units |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                         | 0      | 100     | 0                   | 400   | kHz   |

| t <sub>HDSTAI2C</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 4.0    | -       | 0.6                 | -     | μs    |

| t <sub>LOWI2C</sub>   | LOW period of the SCL clock                                                                 | 4.7    | _       | 1.3                 | _     | μs    |

| t <sub>HIGHI2C</sub>  | HIGH period of the SCL clock                                                                | 4.0    | _       | 0.6                 | _     | μs    |

| t <sub>SUSTAI2C</sub> | Setup time for a repeated START condition                                                   | 4.7    | _       | 0.6                 | _     | μs    |

| t <sub>HDDATI2C</sub> | Data hold time                                                                              | 0      | _       | 0                   | _     | μs    |

| t <sub>SUDATI2C</sub> | Data setup time                                                                             | 250    | _       | 100 <sup>[27]</sup> | _     | ns    |

| t <sub>SUSTOI2C</sub> | Setup time for STOP condition                                                               | 4.0    | _       | 0.6                 | _     | μs    |

| t <sub>BUFI2C</sub>   | Bus free time between a STOP and START condition                                            | 4.7    | _       | 1.3                 | _     | μs    |

| t <sub>SPI2C</sub>    | Pulse width of spikes are suppressed by the input filter                                    | _      | _       | 0                   | 50    | ns    |

#### Note

Document Number: 001-05356 Rev. \*T Page 29 of 50

<sup>27.</sup>A Fast Mode I<sup>2</sup>C bus device is used in a Standard Mode I<sup>2</sup>C bus system but the requirement tSU; DAT ≥ 250 ns is met. This automatically is the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line trmax + tSU; DAT = 1000 + 250 = 1250 ns (according to the Standard Mode I<sup>2</sup>C bus specification) before the SCL line is released.

Page 30 of 50

Table 30. 2.7-V AC Characteristics of the I<sup>2</sup>C SDA and SCL Pins (Fast Mode not Supported)

| Symbol                | Description                                                                                 | Standa | rd Mode | Fast | Mode | Units  |

|-----------------------|---------------------------------------------------------------------------------------------|--------|---------|------|------|--------|

| Symbol                | Description                                                                                 | Min    | Max     | Min  | Max  | Ullits |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                         | 0      | 100     | _    | _    | kHz    |

| t <sub>HDSTAI2C</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 4.0    | _       | _    | _    | μs     |

| t <sub>LOWI2C</sub>   | LOW period of the SCL clock                                                                 | 4.7    | _       | _    | _    | μs     |

| t <sub>HIGHI2C</sub>  | HIGH period of the SCL clock                                                                | 4.0    | _       | _    | _    | μs     |

| t <sub>SUSTAI2C</sub> | Setup time for a repeated start condition                                                   | 4.7    | _       | _    | _    | μs     |

| t <sub>HDDATI2C</sub> | Data hold time                                                                              | 0      | _       | _    | _    | μs     |

| t <sub>SUDATI2C</sub> | Data setup time                                                                             | 250    | _       | _    | _    | ns     |

| t <sub>SUSTOI2C</sub> | Setup time for STOP condition                                                               | 4.0    | _       | _    | _    | μs     |

| t <sub>BUFI2C</sub>   | Bus free time between a STOP and START condition                                            | 4.7    | _       | _    | _    | μs     |

| t <sub>SPI2C</sub>    | Pulse width of spikes are suppressed by the input filter                                    | _      | _       | _    | _    | ns     |

Figure 13. Definition for Timing for Fast/Standard Mode on the I<sup>2</sup>C Bus

# AC SPI Specifications

Table 31 and Table 32 list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  respectively. Typical parameters apply to 5 V, 3.3 V, or 2.7 V at 25  $^{\circ}\text{C}$ . These are for design guidance only.

Table 31. SPI Master AC Specifications

| Symbol               | Parameter               | Conditions | Min | Тур | Max | Units |

|----------------------|-------------------------|------------|-----|-----|-----|-------|

| F <sub>SCLK</sub>    | SCLK clock frequency    | _          | _   | _   | 12  | MHz   |

| DC <sub>SCLK</sub>   | SCLK duty cycle         | _          | _   | 50  | -   | %     |

| t <sub>SETUP</sub>   | MISO to SCLK setup time | _          | 40  | _   | -   | ns    |

| t <sub>HOLD</sub>    | SCLK to MISO hold time  | _          | 40  | _   | -   | ns    |

| t <sub>OUT_VAL</sub> | SCLK to MOSI valid time | _          | _   | _   | 40  | ns    |

| t <sub>OUT_H</sub>   | MOSI high time          | _          | 40  | ı   | _   | ns    |

Table 32. SPI Slave AC Specifications

| Symbol                 | Parameter                      | Conditions | Min                 | Тур | Max | Units |

|------------------------|--------------------------------|------------|---------------------|-----|-----|-------|

| F <sub>SCLK</sub>      | SCLK clock frequency           | _          | _                   | -   | 4   | MHz   |

| t <sub>LOW</sub>       | SCLK low time                  | _          | 41.67               | _   | _   | ns    |

| t <sub>HIGH</sub>      | SCLK high time                 | _          | 41.67               | _   | _   | ns    |

| t <sub>SETUP</sub>     | MOSI to SCLK setup time        | _          | 30                  | _   | -   | ns    |

| t <sub>HOLD</sub>      | SCLK to MOSI hold time         | _          | 50                  | _   | -   | ns    |

| t <sub>SS_MISO</sub>   | SS low to MISO valid           | _          | _                   | -   | 153 | ns    |

| t <sub>SCLK_MISO</sub> | SCLK to MISO valid             | _          | _                   | -   | 125 | ns    |

| t <sub>SS_HIGH</sub>   | SS high time                   | _          | 50                  | -   | -   | ns    |

| t <sub>SS_SCLK</sub>   | Time from SS low to first SCLK | _          | 2/F <sub>SCLK</sub> | -   | _   | ns    |

| t <sub>SCLK_SS</sub>   | Time from last SCLK to SS high | _          | 2/F <sub>SCLK</sub> | -   | -   | ns    |

Document Number: 001-05356 Rev. \*T Page 31 of 50

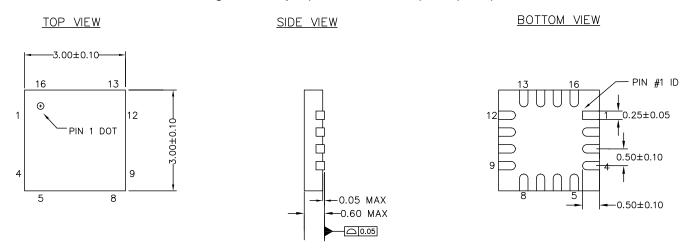

Figure 17. 16-pin (3 × 3 mm × 0.6 Max) COL (Sawn)

#### NOTES

- 1. REFERENCE JEDEC # MO-220

- 2. ALL DIMENSIONS ARE IN MILLIMETERS

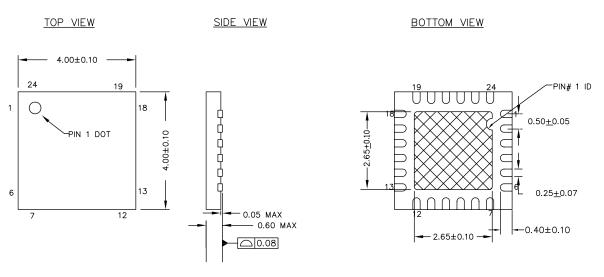

Figure 18. 24-pin QFN (4 × 4 × 0.55 mm) Sawn

#### NOTES:

- 1. 💢 HATCH IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC # MO-248

- 3. PACKAGE WEIGHT:  $29 \pm 3 \text{ mg}$

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-13937 \*F

Document Number: 001-05356 Rev. \*T

001-09116 \*J

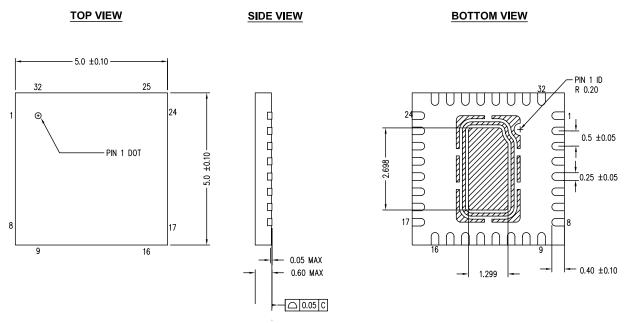

Figure 19. 32-Pin QFN 5 × 5 × 0.55 mm (Sawn)

## NOTES:

- 1. ZZZZ HATCH AREA IS SOLDERABLE EXPOSED PAD

- 2. BASED ON REF JEDEC # MO-248

- 3. PACKAGE WEIGHT:  $38mg \pm 4 mg$

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-48913 \*D

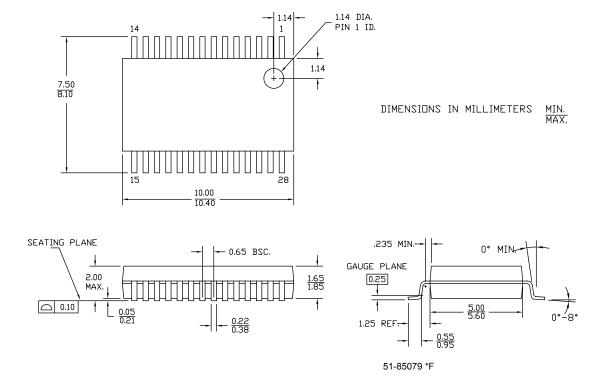

Figure 20. 28-pin SSOP (210 Mils)

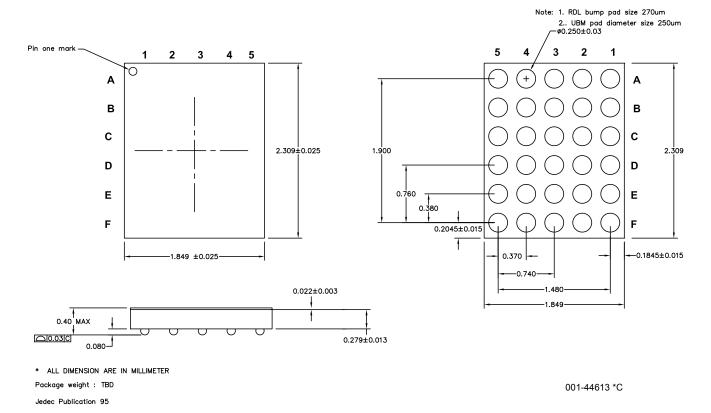

Figure 21. 30-Ball (1.85 × 2.31 × 0.40 mm) WLCSP

Important Note For information on the preferred dimensions for mounting the QFN packages, see the application note *Design Guidelines for Cypress Quad Flat No Extended Lead (QFN) Packaged Devices – AN72845* available at http://www.cypress.com. It is important to note that pinned vias for thermal conduction are not required for the low power 24, 32, and 48-pin QFN PSoC devices.

# **Development Tool Selection**

#### Software

#### PSoC Designer™

At the core of the PSoC development software suite is PSoC Designer, used to generate PSoC firmware applications. PSoC Designer is available free of charge at http://www.cypress.com and includes a free C compiler.

#### PSoC Programmer

PSoC Programmer is flexible enough and is used on the bench in development and also suitable for factory programming. PSoC Programmer works either as a standalone programming application or operates directly from PSoC Designer. PSoC Programmer software is compatible with both PSoC ICE Cube In-Circuit Emulator and PSoC MiniProg. PSoC programmer is available free of charge at http://www.cypress.com.

#### **Development Kits**

All development kits are sold at the Cypress Online Store.

#### CY3215-DK Basic Development Kit

The CY3215-DK is for prototyping and development with PSoC Designer. This kit supports in-circuit emulation and the software interface enables users to run, halt, and single step the processor and view the content of specific memory locations. PSoC Designer supports the advance emulation features also. The kit includes:

- PSoC Designer Software CD

- ICE-Cube In-Circuit Emulator

- ICE Flex-Pod for CY8C29x66 Family

- Cat-5 Adapter

- Mini-Eval Programming Board

- 110 ~ 240V Power Supply, Euro-Plug Adapter

- iMAGEcraft C Compiler (Registration Required)

- ISSP Cable

- USB 2.0 Cable and Blue Cat-5 Cable

- 2 CY8C29466-24PXI 28-PDIP Chip Samples

## **Evaluation Tools**

All evaluation tools are sold at the Cypress Online Store.

#### CY3210-MiniProg1

The CY3210-MiniProg1 kit enables the user to program PSoC devices via the MiniProg1 programming unit. The MiniProg is a small, compact prototyping programmer that connects to the PC via a provided USB 2.0 cable. The kit includes:

- MiniProg Programming Unit

- MiniEval Socket Programming and Evaluation Board

- 28-Pin CY8C29466-24PXI PDIP PSoC Device Sample

- 28-Pin CY8C27443-24PXI PDIP PSoC Device Sample

- PSoC Designer Software CD

- Getting Started Guide

- USB 2.0 Cable

#### CY3210-PSoCEval1

The CY3210-PSoCEval1 kit features an evaluation board and the MiniProg1 programming unit. The evaluation board includes an LCD module, potentiometer, LEDs, and plenty of breadboarding space to meet all of your evaluation needs. The kit includes:

- Evaluation Board with LCD Module

- MiniProg Programming Unit

- 28-Pin CY8C29466-24PXI PDIP PSoC Device Sample (2)

- PSoC Designer Software CD

- Getting Started Guide

- USB 2.0 Cable

#### CY3214-PSoCEvalUSB

The CY3214-PSoCEvalUSB evaluation kit features a development board for the CY8C24794-24LFXI PSoC device. Special features of the board include both USB and capacitive sensing development and debugging support. This evaluation board also includes an LCD module, potentiometer, LEDs, an enunciator and plenty of bread boarding space to meet all of your evaluation needs. The kit includes:

- PSoCEvalUSB Board

- LCD Module

- MIniProg Programming Unit

- Mini USB Cable

- PSoC Designer and Example Projects CD

- Getting Started Guide

- Wire Pack

# **Device Programmers**

All device programmers are purchased from the Cypress Online Store.

#### CY3216 Modular Programmer

The CY3216 Modular Programmer kit features a modular programmer and the MiniProg1 programming unit. The modular programmer includes three programming module cards and supports multiple Cypress products. The kit includes:

- Modular Programmer Base

- 3 Programming Module Cards

- MiniProg Programming Unit

- PSoC Designer Software CD

- Getting Started Guide

- USB 2.0 Cable

# CY3207ISSP In-System Serial Programmer (ISSP)

The CY3207ISSP is a production programmer. It includes protection circuitry and an industrial case that is more robust than the MiniProg in a production programming environment. Note that CY3207ISSP needs special software and is not compatible with PSoC Programmer. The kit includes:

- CY3207 Programmer Unit

- PSoC ISSP Software CD

- 110 ~ 240V Power Supply, Euro-Plug Adapter

- USB 2.0 Cable

# **Accessories (Emulation and Programming)**

Table 35. Emulation and Programming Accessories

| Part Number      | Pin<br>Package | Flex-Pod Kit [31] | Foot Kit [32]   | Prototyping<br>Module | Adapter [33]    |

|------------------|----------------|-------------------|-----------------|-----------------------|-----------------|

| CY8C20234-12LKXI | 16 QFN         | Not Available     | CY3250-16QFN-FK | CY3210-20X34          | Not Available   |

| CY8C20334-12LQXI | 24 QFN         | CY3250-20334QFN   | CY3250-24QFN-FK | CY3210-20X34          | AS-24-28-01ML-6 |

| CY8C20634-12FDXI | 30 WLCSP       | Not available     |                 | CY3210-20X34          | Not Available   |

- 31. Dual function Digital I/O Pins also connect to the common analog mux.

- 32. This part may be used for in-circuit debugging. It is NOT available for production.

- 33. Programming adapter converts non-DIP package to DIP footprint. Specific details and ordering information for each of the adapters is available at <a href="http://www.emulation.com">http://www.emulation.com</a>.

# Acronyms

## **Acronyms Used**

Table 37 lists the acronyms that are used in this document.

Table 37. Acronyms Used in this Datasheet

| Acronym | Description                                         | Acronym          | Description                     |

|---------|-----------------------------------------------------|------------------|---------------------------------|

| AC      | alternating current                                 | MIPS             | million instructions per second |

| ADC     | analog-to-digital converter                         | OCD              | on-chip debug                   |

| API     | application programming interface                   | PCB              | printed circuit board           |

| CMOS    | complementary metal oxide semiconductor             | PGA              | programmable gain amplifier     |

| CPU     | central processing unit                             | POR              | power on reset                  |

| EEPROM  | electrically erasable programmable read-only memory | PPOR             | precision power on reset        |

| GPIO    | general purpose I/O                                 | PSoC®            | Programmable System-on-Chip     |

| ICE     | in-circuit emulator                                 | PWM              | pulse width modulator           |

| IDAC    | current DAC                                         | QFN              | quad flat no leads              |

| IDE     | integrated development environment                  | SLIMO            | slow IMO                        |

| ILO     | internal low speed oscillator                       | SPI <sup>™</sup> | serial peripheral interface     |

| IMO     | internal main oscillator                            | SRAM             | static random access memory     |

| I/O     | input/output                                        | SROM             | supervisory read only memory    |

| ISSP    | in-system serial programming                        | SSOP             | shrink small-outline package    |

| LCD     | liquid crystal display                              | USB              | universal serial bus            |

| LDO     |                                                     | WDT              | watchdog timer                  |

| LED     | light-emitting diode                                | WLCSP            | wafer level chip scale package  |

| LVD     | low voltage detect                                  | XRES             | external reset                  |

| MCU     | microcontroller unit                                |                  | •                               |

# **Reference Documents**

$PSoC^{\$}$  CY8C20x34 and  $PSoC^{\$}$  CY8C20x24 Technical Reference Manual (TRM) – 001-13033 Design Aids – Reading and Writing  $PSoC^{\$}$  Flash - AN2015 (001-40459)

Design Guidelines for Cypress Quad Flat No Extended Lead (QFN) Packaged Devices – AN72845 available at http://www.cypress.com.

Document Number: 001-05356 Rev. \*T Page 41 of 50

# Glossary

**External Reset** (XRES)

An active high signal that is driven into the PSoC device. It causes all operation of the CPU and blocks to stop and return to a pre-defined state.

Flash

An electrically programmable and erasable, non-volatile technology that provides you the programmability and data storage of EPROMs, plus in-system erasability. Non-volatile means that the data is retained when power is

Flash block

The smallest amount of Flash ROM space that may be programmed at one time and the smallest amount of Flash space that may be protected. A Flash block holds 64 bytes.

frequency

The number of cycles or events per unit of time, for a periodic function.

gain

The ratio of output current, voltage, or power to input current, voltage, or power, respectively. Gain is usually expressed in dB.

I<sup>2</sup>C

A two-wire serial computer bus by Philips Semiconductors (now NXP Semiconductors). I2C is an Inter-Integrated Circuit. It is used to connect low-speed peripherals in an embedded system. The original system was created in the early 1980s as a battery control interface, but it was later used as a simple internal bus system for building control electronics. I2C uses only two bi-directional pins, clock and data, both running at +5V and pulled high with resistors. The bus operates at 100 kbits/second in standard mode and 400 kbits/second in fast mode.

ICE

The in-circuit emulator that allows you to test the project in a hardware environment, while viewing the debugging device activity in a software environment (PSoC Designer).

input/output (I/O) A device that introduces data into or extracts data from a system.

interrupt

A suspension of a process, such as the execution of a computer program, caused by an event external to that process, and performed in such a way that the process can be resumed.

interrupt service routine (ISR)

A block of code that normal code execution is diverted to when the M8C receives a hardware interrupt. Many interrupt sources may each exist with its own priority and individual ISR code block. Each ISR code block ends with the RETI instruction, returning the device to the point in the program where it left normal program execution.

jitter

- 1. A misplacement of the timing of a transition from its ideal position. A typical form of corruption that occurs on serial data streams.

- The abrupt and unwanted variations of one or more signal characteristics, such as the interval between successive pulses, the amplitude of successive cycles, or the frequency or phase of successive cycles.

low-voltage detect. A circuit that senses V<sub>DD</sub> and provides an interrupt to the system when V<sub>DD</sub> falls lower than a selected threshold. (LVD)

M8C

An 8-bit Harvard-architecture microprocessor. The microprocessor coordinates all activity inside a PSoC by interfacing to the Flash, SRAM, and register space.

master device

A device that controls the timing for data exchanges between two devices. Or when devices are cascaded in width, the master device is the one that controls the timing for data exchanges between the cascaded devices and an external interface. The controlled device is called the slave device.

microcontroller

An integrated circuit chip that is designed primarily for control systems and products. In addition to a CPU, a microcontroller typically includes memory, timing circuits, and IO circuitry. The reason for this is to permit the realization of a controller with a minimal quantity of chips, thus achieving maximal possible miniaturization. This in turn, reduces the volume and the cost of the controller. The microcontroller is normally not used for general-purpose computation as is a microprocessor.

mixed-signal

The reference to a circuit containing both analog and digital techniques and components.

# **Glossary**

modulator A device that imposes a signal on a carrier.

noise 1. A disturbance that affects a signal and that may distort the information carried by the signal.

2. The random variations of one or more characteristics of any entity such as voltage, current, or data.

oscillator A circuit that may be crystal controlled and is used to generate a clock frequency.

parity A technique for testing transmitting data. Typically, a binary digit is added to the data to make the sum of all the

digits of the binary data either always even (even parity) or always odd (odd parity).

Phase-locked loop (PLL)

An electronic circuit that controls an **oscillator** so that it maintains a constant phase angle relative to a reference

signal.

pinouts The pin number assignment: the relation between the logical inputs and outputs of the PSoC device and their

physical counterparts in the printed circuit board (PCB) package. Pinouts involve pin numbers as a link between

schematic and PCB design (both being computer generated files) and may also involve pin names.

port A group of pins, usually eight.

Power on reset (POR)

A circuit that forces the PSoC device to reset when the voltage is lower than a pre-set level. This is a type of

hardware reset.

PSoC<sup>®</sup> Cypress Semiconductor's PSoC<sup>®</sup> is a registered trademark and Programmable System-on-Chip™ is a trademark

of Cypress.

PSoC Designer™ The software for Cypress' Programmable System-on-Chip technology.

pulse width modulator (PWM)

An output in the form of duty cycle which varies as a function of the applied measurand

RAM An acronym for random access memory. A data-storage device from which data can be read out and new data

can be written in.

register A storage device with a specific capacity, such as a bit or byte.

reset A means of bringing a system back to a know state. See hardware reset and software reset.

ROM An acronym for read only memory. A data-storage device from which data can be read out, but new data cannot

be written in.

serial 1. Pertaining to a process in which all events occur one after the other.

2. Pertaining to the sequential or consecutive occurrence of two or more related activities in a single device or

channel.

settling time The time it takes for an output signal or value to stabilize after the input has changed from one value to another.

shift register A memory storage device that sequentially shifts a word either left or right to output a stream of serial data.

slave device A device that allows another device to control the timing for data exchanges between two devices. Or when

devices are cascaded in width, the slave device is the one that allows another device to control the timing of data exchanges between the cascaded devices and an external interface. The controlling device is called the master

device.

# **Document History Page**

Document Title: CY8C20134/CY8C20234/CY8C20334/CY8C20434/CY8C20534/CY8C20634, PSoC<sup>®</sup> Programmable System-on-Chip™

| Revision | ECN     | Orig. of<br>Change             | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|--------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 404571  | HMT                            | See ECN            | New silicon and document (Revision **).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *A       | 418513  | НМТ                            | See ECN            | Updated Electrical Specifications, including Storage Temperature and Maximum Input Clock Frequency. Updated Features and Analog System Overview. Modified 32-pin QFN E-PAD dimensions. Added new 32-pin QFN. Add High Output Drive indicator to all P1[x] pinouts. Updated trademarks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *B       | 490071  | HMT                            | See ECN            | Made datasheet "Final". Added new Development Tool section. Added OCD pinout and package diagram. Added 16-pin QFN. Updated 24-pin and 32-pin QFN package diagrams to 0.60 max thickness. Changed from commercial to industrial temperature range. Updated Storage Temperature specification and notes. Updated thermal resistance data. Added development tool kit part numbers. Finetuned features and electrical specifications.                                                                                                                                                                                                                                                                                                                                                                               |

| *C       | 788177  | НМТ                            | See ECN            | Added CapSense SNR requirement reference. Added Low Power Comparator (LPC) AC/DC electrical specifications tables. Added 2.7V minimum specifications. Updated figure standards. Updated Technical Training paragraph. Added QFN package clarifications and dimensions. Updated ECN-ed Amkor dimensioned QFN package diagram revisions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *D       | 1356805 | HMT /<br>SFVTMP3/<br>HCL / SFV | See ECN            | Updated 24-pin QFN Theta JA. Added External Reset Pulse Width, TXRST, specification. Fixed 48-pin QFN.vsd. Updated the table introduction and high output voltage description in section two. The sentence: "Exceeding maximum ratings may shorten the battery life of the device." does not apply to all datasheets. Therefore, the word "battery" is changed to "useful." Took out tabs after table and figure numbers in titles and added two hard spaces. Updated the section, DC GPIO Specifications on page 20 with new text. Updated VOH5 and VOH6 to say, "High Output Voltage, Port 1 Pins with 3.0V LDO Regulator Enabled." Updated VOH7 and VOH8 with the text, "maximum of 20 mA source current in all I/Os."Added 28-pin SSOP part, pinout, package. Updated specs. Modified dev. tool part numbers. |

| *E       | 2197347 | UVS /<br>AESA                  | See ECN            | Added 32-pin Sawn QFN Pin diagram Removed package diagram: 32-Pin (5 × 5 mm) SAWN QFN(001-42168 *A) Updated Ordering Information table with CY8C20434-12LQXI and CY8C20434-12LQXIT ordering details. Corrected Table 16. DC Programming Specifications - Included above the table "Flash Endurance and Retention specifications with the use of the EEPROM User Module are valid only within the range: 25 °C +/-20C during the Flash Write operation. Refer the EEPROM User Module datasheet instruc- tions for EEPROM Flash Write requirements outside of the 25 °C +/-20 °C temperature window."                                                                                                                                                                                                               |

| *F       | 2542938 | RLRM /<br>AESA                 | 07/30/2008         | Corrected Ordering Information format. Updated package diagrams 001-13937 and 001-30999. Updated datasheet template. Corrected Figure 6 (28-pin diagram).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *G       | 2610469 | SNV /<br>PYRS                  | 11/20/08           | Updated $V_{OH5}$ , $V_{OH7}$ , and $V_{OH9}$ specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *H       | 2693024 | DPT /<br>PYRS                  | 04/16/2009         | Changed title from PSoC <sup>®</sup> Mixed Signal Array to PSoC <sup>®</sup> Programmable System-on-Chip™ Replaced package outline drawing for 32-Pin Sawn QFN Updated "Development Tool Selection" on page 38 Updated "Development Tools" on page 7 and "Designing with PSoC Designer" on page 8 Updated "Getting Started" on page 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |