Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

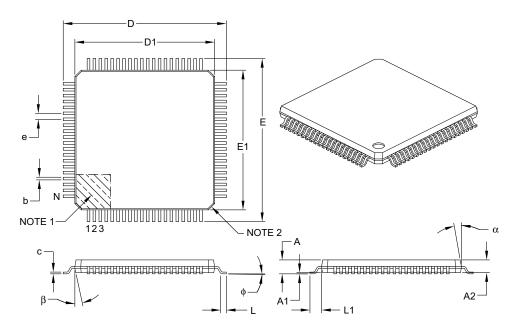

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6527t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.6.5.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high. To adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low. To compensate, increment OSCTUNE to increase the clock frequency.

#### 2.6.5.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is much greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

### 2.6.5.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast. To compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow. To compensate, increment the OSCTUNE register.

#### 2.7 Clock Sources and Oscillator Switching

The PIC18F8722 family of devices includes a feature that allows the device clock source to be switched from the main oscillator to an alternate clock source. These devices also offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary oscillators

- Secondary oscillators

- Internal oscillator block

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<3:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

The PIC18F8722 family of devices offers the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a real-time clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

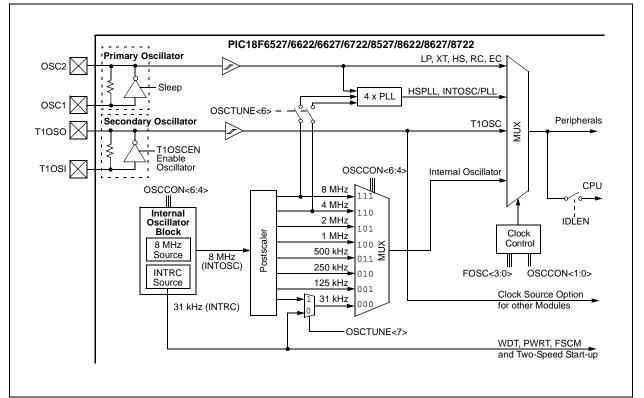

The clock sources for the PIC18F8722 family of devices are shown in Figure 2-11. See **Section 25.0** "**Special Features of the CPU**" for Configuration register details.

FIGURE 2-11: PIC18F8722 FAMILY CLOCK DIAGRAM

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |  |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|--|

|                                | LP, XT, HS                    |                                       |                                    |  |

| Primary Device Clock           | HSPLL                         | Tcsd <sup>(1)</sup>                   | OSTS                               |  |

| (PRI_IDLE mode)                | EC, RC                        | 10.30 ( )                             |                                    |  |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| T1OSC or INTRC                 | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

|                                | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |  |

| INTOSC <sup>(2)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

| (Sleep mode)                   | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

Note 1: TCSD (parameter 38, Table 28-12) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies. On Reset, INTOSC defaults to 1 MHz.

**3:** TOST is the Oscillator Start-up Timer (parameter 32, Table 28-12). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12, Table 28-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 28-12), the INTOSC stabilization period.

### 4.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In the PIC18F8722 family of devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See Section 11.5 "PORTE, TRISE and LATE Registers" for more information.

#### 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

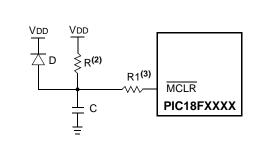

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004, "Section **28.2** "**DC Characteristics: Power-Down and Supply Current**"). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

#### FIGURE 4-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)<sup>(1)</sup>

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

#### 5.1.5.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

#### 5.2 PIC18 Instruction Cycle

#### 5.2.1 CLOCKING SCHEME

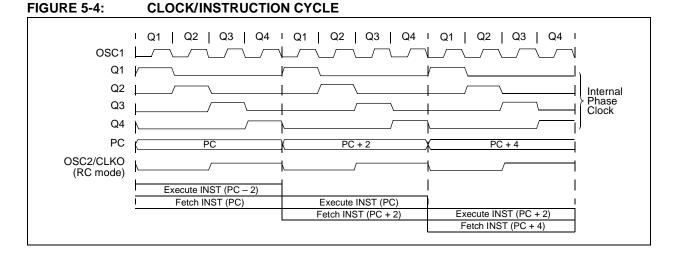

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-4.

#### 5.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

| _                        | Тсү0       | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|--------------------------|------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h             | Fetch 1    | Execute 1 |           |           |             |               |

| 2. MOVWF PORTB           |            | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA SUB_1             |            |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (Fo   | orced NOP) |           |           | Fetch 4   | Flush (NOP) |               |

| 5. Instruction @ address | s SUB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

NOTES:

### 7.0 EXTERNAL MEMORY BUS

Note: The External Memory Bus is not implemented on PIC18F6527/6622/6627/6722 (64-pin) devices.

The External Memory Bus (EMB) allows the device to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory. It supports both 8-bit and 16-bit Data Width modes and four address widths from 8 to 20 bits. The bus is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals.

A list of the pins and their functions is provided in Table 7-1.

| TABLE 7-1: | PIC18F8527/8622/8627/8722 EXTERNAL BUS – I/O PORT FUNCTIONS |

|------------|-------------------------------------------------------------|

|            |                                                             |

| Name     | Port  | Bit | External Memory Bus Function           |

|----------|-------|-----|----------------------------------------|

| RD0/AD0  | PORTD | 0   | Address bit 0 or Data bit 0            |

| RD1/AD1  | PORTD | 1   | Address bit 1 or Data bit 1            |

| RD2/AD2  | PORTD | 2   | Address bit 2 or Data bit 2            |

| RD3/AD3  | PORTD | 3   | Address bit 3 or Data bit 3            |

| RD4/AD4  | PORTD | 4   | Address bit 4 or Data bit 4            |

| RD5/AD5  | PORTD | 5   | Address bit 5 or Data bit 5            |

| RD6/AD6  | PORTD | 6   | Address bit 6 or Data bit 6            |

| RD7/AD7  | PORTD | 7   | Address bit 7 or Data bit 7            |

| RE0/AD8  | PORTE | 0   | Address bit 8 or Data bit 8            |

| RE1/AD9  | PORTE | 1   | Address bit 9 or Data bit 9            |

| RE2/AD10 | PORTE | 2   | Address bit 10 or Data bit 10          |

| RE3/AD11 | PORTE | 3   | Address bit 11 or Data bit 11          |

| RE4/AD12 | PORTE | 4   | Address bit 12 or Data bit 12          |

| RE5/AD13 | PORTE | 5   | Address bit 13 or Data bit 13          |

| RE6/AD14 | PORTE | 6   | Address bit 14 or Data bit 14          |

| RE7/AD15 | PORTE | 7   | Address bit 15 or Data bit 15          |

| RH0/A16  | PORTH | 0   | Address bit 16                         |

| RH1/A17  | PORTH | 1   | Address bit 17                         |

| RH2/A18  | PORTH | 2   | Address bit 18                         |

| RH3/A19  | PORTH | 3   | Address bit 19                         |

| RJ0/ALE  | PORTJ | 0   | Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | 1   | Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | 2   | Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | 3   | Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | 4   | Byte Address bit 0 (BA0)               |

| RJ5/CE   | PORTJ | 5   | Chip Enable (CE) Control pin           |

| RJ6/LB   | PORTJ | 6   | Lower Byte Enable (LB) Control pin     |

| RJ7/UB   | PORTJ | 7   | Upper Byte Enable (UB) Control pin     |

**Note:** For the sake of clarity, only I/O port and external bus assignments are shown here. One or more additional multiplexed features may be available on some pins.

| Pin Name      | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                                     |

|---------------|----------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT0/FLT0 | RB0                  | 0               | 0   | DIG         | LATB<0> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | INT0                 | 1               | I   | ST          | External interrupt 0 input.                                                                                                                     |

|               | FLT0                 | 1               | Ι   | ST          | ECCPx PWM Fault input, enabled in software.                                                                                                     |

| RB1/INT1      | RB1                  | 0               | 0   | DIG         | LATB<1> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<1> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | INT1                 | 1               | I   | ST          | External interrupt 1 input.                                                                                                                     |

| RB2/INT2      | RB2                  | 0               | 0   | DIG         | LATB<2> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<2> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | INT2                 | 1               | I   | ST          | External interrupt 2 input.                                                                                                                     |

| RB3/INT3/     | RB3                  | 0               | 0   | DIG         | LATB<3> data output.                                                                                                                            |

| ECCP2/P2A     |                      | 1               | I   | TTL         | PORTB<3> data input; weak pull-up when RBPU bit is cleared and capture input is disabled.                                                       |

|               | INT3                 | 1               | I   | ST          | External interrupt 3 input.                                                                                                                     |

|               | ECCP2 <sup>(1)</sup> | 0               | 0   | DIG         | ECCP2 compare output and ECCP2 PWM output. Takes priority over port data.                                                                       |

|               |                      | 1               | I   | ST          | ECCP2 capture input.                                                                                                                            |

|               | P2A <sup>(1)</sup>   | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, channel A. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

| RB4/KBI0      | RB4                  | 0               | 0   | DIG         | LATB<4> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | KBI0                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

| RB5/KBI1/PGM  | RB5                  | 0               | 0   | DIG         | LATB<5> data output                                                                                                                             |

|               |                      | 1               | I   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | KBI1                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|               | PGM                  | x               | I   | ST          | Single-Supply Programming mode entry (ICSP). Enabled by LVP Configuration bit; all other pin functions disabled.                                |

| RB6/KBI2/PGC  | RB6                  | 0               | 0   | DIG         | LATB<6> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | KBI2                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|               | PGC                  | х               | I   | ST          | Serial execution (ICSP <sup>™</sup> ) clock input for ICSP and ICD operation <sup>(2)</sup> .                                                   |

| RB7/KBI3/PGD  | RB7                  | 0               | 0   | DIG         | LATB<7> data output.                                                                                                                            |

|               |                      | 1               | I   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|               | KBI3                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|               | PGD                  | х               | 0   | DIG         | Serial execution data output for ICSP and ICD operation <sup>(2)</sup> .                                                                        |

|               |                      | х               | I   | ST          | Serial execution data input for ICSP and ICD operation <sup>(2)</sup> .                                                                         |

#### TABLE 11-3: PORTB FUNCTIONS

Legend: PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared (Microprocessor, Extended Microcontroller and Microcontroller with Boot Block modes, 80-pin devices only). Default assignment is RC1.

2: All other pin functions are disabled when ICSP or ICD operations are enabled.

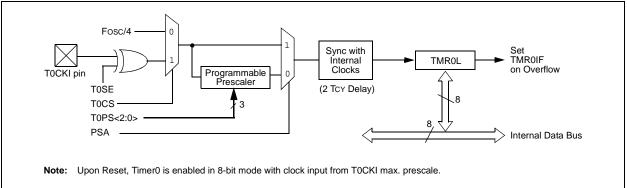

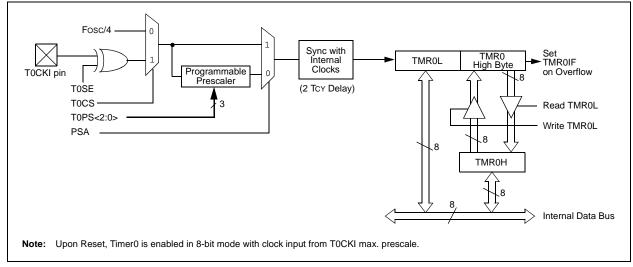

### 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (T0CON<5>). In Timer mode (T0CS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the TOCS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

## 12.2 Timer0 Reads and Writes in 16-bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 12-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

#### FIGURE 12-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

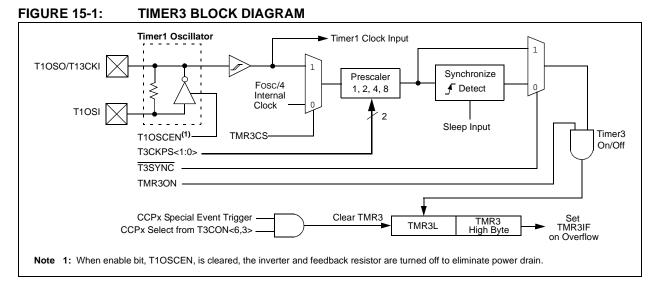

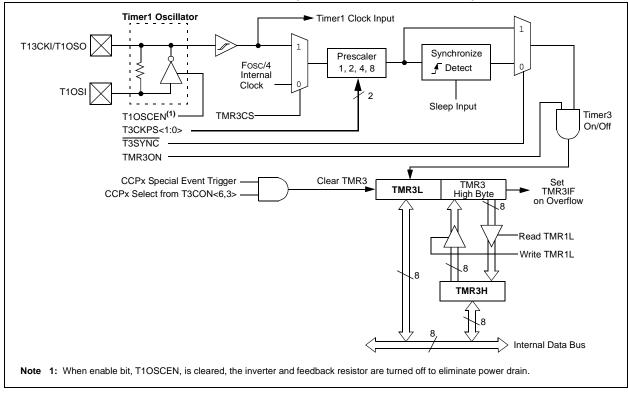

#### 15.1 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

As with Timer1, the RC1/T1OSI and RC0/T1OSO/ T13CKI pins become inputs when the Timer1 oscillator is enabled. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

#### FIGURE 15-2: TIMER3 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

#### REGISTER 18-3: ECCPxAS: ENHANCED CCP AUTO-SHUTDOWN CONFIGURATION REGISTER

| SxBD0 |

|-------|

| bit ( |

|       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | <b>ECCPxASE:</b> ECCP Auto-Shutdown Event Status bit<br>0 = ECCP outputs are operating<br>1 = A shutdown event has occurred; ECCP outputs are in shutdown state                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits<br>000 = Auto-shutdown is disabled<br>001 = Comparator 1 output<br>010 = Comparator 2 output<br>011 = Either Comparator 1 or 2<br>100 = FLT0<br>101 = FLT0 or Comparator 1<br>110 = FLT0 or Comparator 2<br>111 = FLT0 or Comparator 1 or Comparator 2 |

| bit 3-2 | <b>PSSxAC&lt;1:0&gt;:</b> Pins A and C Shutdown State Control bits<br>00 = Drive pins A and C to '0'<br>01 = Drive pins A and C to '1'<br>1x = Pins A and C tri-state                                                                                                                                      |

| bit 1-0 | <b>PSSxBD&lt;1:0&gt;:</b> Pins B and D Shutdown State Control bits<br>00 = Drive pins B and D to '0'<br>01 = Drive pins B and D to '1'<br>1x = Pins B and D tri-state                                                                                                                                      |

| BRG Value                | XXXXh                    | 0000h                                            | XXXXXXXXXXXXXXX001Ch                                                     |

|--------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------------|

| RXx pin                  |                          | Edge #1 Edge #2<br>Start Bit 0 Bit 1 Bit 2 Bit 3 | Edge #3   Edge #4   Edge #5     Bit 4   Bit 5   Bit 6   Bit 7   Stop Bit |

| BRG Clock                | ົມທານທານສາມທານສາມທານກໍ່າ | www.iwwwwwwww                                    |                                                                          |

| ABDEN bit                | Set by User —            |                                                  | Auto-Cleared                                                             |

| RCxIF bit<br>(Interrupt) |                          |                                                  |                                                                          |

| Read<br>RCREGx           |                          |                                                  |                                                                          |

| SPBRGx                   |                          | XXXXh                                            | X 1Ch                                                                    |

| SPBRGHx                  |                          | XXXXh                                            | ∑ 00h                                                                    |

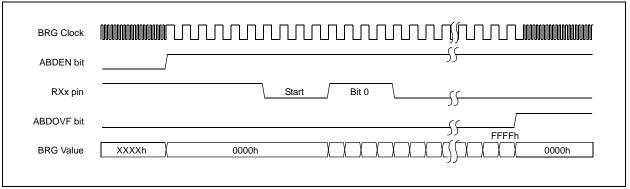

#### FIGURE 20-2: BRG OVERFLOW SEQUENCE

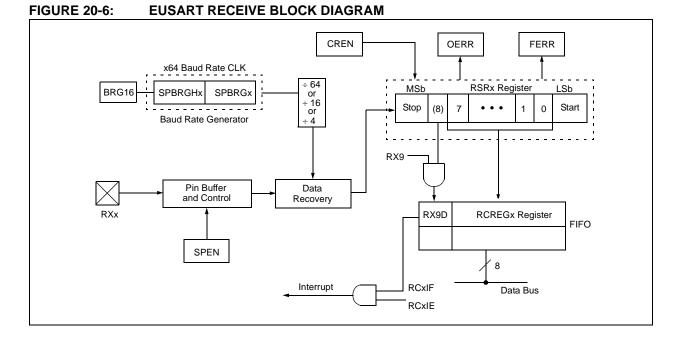

#### 20.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 20-6. The data is received on the RXx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCxIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- Flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 20.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If interrupts are required, set the RCEN bit and select the desired priority level with the RCxIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

| BNC                                                     | Branch if N                                           | lot Carry                                          |                                       | BNN                                                      | Branch if I                               | Not Negative                    | e                          |  |

|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------------|-------------------------------------------|---------------------------------|----------------------------|--|

| Syntax:                                                 | BNC n                                                 |                                                    | Syntax:                               | BNN n                                                    | BNN n                                     |                                 |                            |  |

| Operands:                                               | -128 ≤ n ≤ ′                                          | $-128 \le n \le 127$                               |                                       | Operands:                                                | -128 ≤ n ≤                                | $-128 \le n \le 127$            |                            |  |

| Operation:                                              | if Carry bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                    | Operation:                            | if Negative bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC |                                           |                                 |                            |  |

| Status Affected:                                        | None                                                  |                                                    |                                       | Status Affected:                                         | None                                      |                                 |                            |  |

| Encoding:                                               | 1110                                                  | 0011 nn:                                           | nn nnnn                               | Encoding:                                                | 1110                                      | 0111 n                          | nnn nnnn                   |  |

| Description:                                            | If the Carry will branch.                             | bit is '0', then                                   | the program                           | Description:                                             | If the Nega<br>program w                  | tive bit is '0',<br>ill branch. | , then the                 |  |

|                                                         | added to th<br>incremente<br>instruction,             | d to fetch the<br>the new addre<br>n. This instruc | e PC will have<br>next<br>ess will be |                                                          | added to th<br>incremente<br>instruction, | d to fetch the<br>the new add   | the PC will have<br>e next |  |

| Words:                                                  | 1                                                     |                                                    |                                       | Words:                                                   | 1                                         |                                 |                            |  |

| Cycles:                                                 | 1(2)                                                  |                                                    |                                       | Cycles:                                                  | 1(2)                                      |                                 |                            |  |

| Q Cycle Activity:<br>If Jump:                           |                                                       |                                                    |                                       | Q Cycle Activity:<br>If Jump:                            |                                           |                                 |                            |  |

| Q1                                                      | Q2                                                    | Q3                                                 | Q4                                    | Q1                                                       | Q2                                        | Q3                              | Q4                         |  |

| Decode                                                  | Read literal<br>'n'                                   | Process<br>Data                                    | Write to<br>PC                        | Decode                                                   | Read literal<br>'n'                       | Process<br>Data                 | Write to<br>PC             |  |

| No                                                      | No                                                    | No                                                 | No                                    | No                                                       | No                                        | No                              | No                         |  |

| operation                                               | operation                                             | operation                                          | operation                             | operation                                                | operation                                 | operation                       | operation                  |  |

| If No Jump:                                             |                                                       |                                                    |                                       | If No Jump:                                              |                                           |                                 |                            |  |

| Q1                                                      | Q2                                                    | Q3                                                 | Q4                                    | Q1                                                       | Q2                                        | Q3                              | Q4                         |  |

| Decode                                                  | Read literal<br>'n'                                   | Process<br>Data                                    | No<br>operation                       | Decode                                                   | Read literal<br>'n'                       | Process<br>Data                 | No<br>operation            |  |

| Example:                                                | HERE                                                  | BNC Jump                                           |                                       | Example:                                                 | HERE                                      | BNN Jun                         | np                         |  |

| Before Instru<br>PC<br>After Instruct<br>If Carry<br>PC | = ad<br>ion<br>= 0;                                   | dress (HERE                                        |                                       | Before Instru<br>PC<br>After Instruct<br>If Negat<br>PC  | = ac<br>ion<br>ive = 0;                   | ldress (HER                     |                            |  |

|                                                         | C = ad<br>= 1;                                        | dress (Jump)<br>dress (HERE                        |                                       |                                                          | ; = ac<br>ive = 1;                        | ldress (Jum<br>ldress (HER      | - /                        |  |

| SUB         | WFB                              | Subtract                                                                                                                                                                                                                                                                             | W from f                                         | with Bor                                                                                                                                    | ·ow            |  |  |  |  |  |

|-------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| Synta       | ax:                              | SUBWFB                                                                                                                                                                                                                                                                               | f {,d {,a}                                       | }                                                                                                                                           |                |  |  |  |  |  |

|             | ands:                            | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                  |                                                  |                                                                                                                                             |                |  |  |  |  |  |

| •           | ation:                           |                                                                                                                                                                                                                                                                                      | $-(\overline{C}) \rightarrow de$                 | st                                                                                                                                          |                |  |  |  |  |  |

|             | s Affected:                      |                                                                                                                                                                                                                                                                                      | N, OV, C, DC, Z                                  |                                                                                                                                             |                |  |  |  |  |  |

| Enco        | -                                | 0101                                                                                                                                                                                                                                                                                 | 10da                                             | ffff                                                                                                                                        | ffff           |  |  |  |  |  |

| Desc        | ription:                         | from regis<br>method).<br>in W. If 'd'                                                                                                                                                                                                                                               | ster 'f' (2's<br>If 'd' is '0',<br>is '1', the i | and the Carry flag (borrow)<br>er 'f' (2's complement<br>'d' is '0', the result is stored<br>'1', the result is stored back<br>' (default). |                |  |  |  |  |  |

|             |                                  | If 'a' is '1',                                                                                                                                                                                                                                                                       |                                                  | e Access Bank is selected.<br>e BSR is used to select the<br>default).                                                                      |                |  |  |  |  |  |

|             |                                  | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                  |                                                                                                                                             |                |  |  |  |  |  |

| Word        | ls:                              | 1                                                                                                                                                                                                                                                                                    |                                                  |                                                                                                                                             |                |  |  |  |  |  |

| Cycle       |                                  | 1                                                                                                                                                                                                                                                                                    |                                                  |                                                                                                                                             |                |  |  |  |  |  |

| QC          | ycle Activity:                   | 0.0                                                                                                                                                                                                                                                                                  |                                                  | _                                                                                                                                           | <b>.</b>       |  |  |  |  |  |

|             | Q1<br>Decode                     | Q2<br>Read                                                                                                                                                                                                                                                                           | Q:<br>Proce                                      |                                                                                                                                             | Q4<br>Write to |  |  |  |  |  |

|             | Decoue                           | register 'f'                                                                                                                                                                                                                                                                         | Dat                                              |                                                                                                                                             | estination     |  |  |  |  |  |

| <u>Exan</u> | nple 1:                          | SUBWFB                                                                                                                                                                                                                                                                               | REG,                                             | 1, 0                                                                                                                                        |                |  |  |  |  |  |

|             | Before Instruct                  | ion                                                                                                                                                                                                                                                                                  |                                                  |                                                                                                                                             |                |  |  |  |  |  |

|             | REG<br>W<br>C                    | = 19h<br>= 0Dh<br>= 1                                                                                                                                                                                                                                                                | (000<br>(000                                     | 1 1001)<br>0 1101)                                                                                                                          |                |  |  |  |  |  |

|             | After Instructio                 |                                                                                                                                                                                                                                                                                      |                                                  |                                                                                                                                             |                |  |  |  |  |  |

|             | REG<br>W<br>C<br>Z               | = 0Ch<br>= 0Dh<br>= 1<br>= 0                                                                                                                                                                                                                                                         | (000<br>(000                                     | 0 1011)<br>0 1101)                                                                                                                          |                |  |  |  |  |  |

|             | N                                | = 0<br>= 0                                                                                                                                                                                                                                                                           | ; result is positive                             |                                                                                                                                             |                |  |  |  |  |  |

| Exan        | nple 2:                          | SUBWFB                                                                                                                                                                                                                                                                               | REG, 0                                           | , 0                                                                                                                                         |                |  |  |  |  |  |

|             | Before Instruct                  |                                                                                                                                                                                                                                                                                      |                                                  |                                                                                                                                             |                |  |  |  |  |  |

|             | REG<br>W<br>C                    | = 1Bh<br>= 1Ah<br>= 0                                                                                                                                                                                                                                                                |                                                  | 1 1011)<br>1 1010)                                                                                                                          |                |  |  |  |  |  |

|             | After Instructio<br>REG<br>W     | = 1Bh<br>= 00h                                                                                                                                                                                                                                                                       | (000                                             | 1 1011)                                                                                                                                     |                |  |  |  |  |  |

|             | C<br>Z<br>N                      | = 1<br>= 1<br>= 0                                                                                                                                                                                                                                                                    | ; resu                                           | lt is zero                                                                                                                                  |                |  |  |  |  |  |

|             | nple 3:                          | SUBWFB                                                                                                                                                                                                                                                                               | REG,                                             | 1, 0                                                                                                                                        |                |  |  |  |  |  |

|             | Before Instruct<br>REG<br>W<br>C | ion<br>= 03h<br>= 0Eh<br>= 1                                                                                                                                                                                                                                                         |                                                  | 0 0011)<br>0 1101)                                                                                                                          |                |  |  |  |  |  |

|             | After Instructio<br>REG          | = F5h                                                                                                                                                                                                                                                                                |                                                  | 1 0100)<br>comp]                                                                                                                            |                |  |  |  |  |  |

|             | W<br>C<br>Z<br>N                 | = 0Eh<br>= 0<br>= 0                                                                                                                                                                                                                                                                  | (000                                             | 0 1101)                                                                                                                                     |                |  |  |  |  |  |

|             | N                                | = 1                                                                                                                                                                                                                                                                                  | ; resu                                           | lt is nega                                                                                                                                  | tive           |  |  |  |  |  |

| SWAPF                          | Swap f                                                                                                 |                                                                 |                                                                   |                                                |

|--------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|

| Syntax:                        | SWAPF f                                                                                                | {,d {,a}}                                                       |                                                                   |                                                |

| Operands:                      | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                    |                                                                 |                                                                   |                                                |

| Operation:                     | (f<3:0>) →<br>(f<7:4>) →                                                                               |                                                                 |                                                                   |                                                |

| Status Affected:               | None                                                                                                   |                                                                 |                                                                   |                                                |

| Encoding:                      | 0011                                                                                                   | 10da                                                            | ffff                                                              | ffff                                           |

| Description:                   | The upper<br>'f' are exch<br>is placed ir<br>placed in re                                              | anged. If<br>wW. If 'd'                                         | 'd' is '0', t<br>is '1', the                                      | he result                                      |

|                                | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank                                                       | he BSR                                                          | is used to                                                        |                                                |

|                                | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 26<br>Bit-Oriento<br>Literal Offi | led, this i<br>Literal O<br>never f ≤<br>5.2.3 "By<br>ed Instru | nstruction<br>ffset Addro<br>95 (5Fh).<br>te-Oriento<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:                         | 1                                                                                                      |                                                                 |                                                                   |                                                |

| Cycles:                        | 1                                                                                                      |                                                                 |                                                                   |                                                |

| Q Cycle Activity:              |                                                                                                        |                                                                 |                                                                   |                                                |

| Q1                             | Q2                                                                                                     | Q3                                                              | 3                                                                 | Q4                                             |

| Decode                         | Read<br>register 'f'                                                                                   | Proce<br>Data                                                   |                                                                   | Vrite to<br>stination                          |

| Example:                       | SWAPF I                                                                                                | REG, 1,                                                         | 0                                                                 |                                                |

| Before Instruc                 |                                                                                                        |                                                                 |                                                                   |                                                |

| REG<br>After Instructio<br>REG | = 53h<br>on<br>= 35h                                                                                   |                                                                 |                                                                   |                                                |

### 27.11 PICSTART<sup>®</sup> Plus Development Programmer

The PICSTART<sup>®</sup> Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

#### 27.12 PICkit<sup>™</sup> 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 27.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

| DC CH/       | ARACTE | ERISTICS                                                            |      |      |     |       | unless otherwise stated)<br>≤ +85°C for industrial               |

|--------------|--------|---------------------------------------------------------------------|------|------|-----|-------|------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                                                      | Min  | Тур† | Max | Units | Conditions                                                       |

|              |        | Data EEPROM Memory                                                  |      |      |     |       |                                                                  |

| D120         | ED     | Byte Endurance                                                      | 100K | 1M   | —   | E/W   | -40°C to +85°C                                                   |

| D121         | Vdrw   | VDD for Read/Write                                                  | Vmin | _    | 5.5 | V     | Using EECON to read/write<br>VMIN = Minimum operating<br>voltage |

| D122         | TDEW   | Erase/Write Cycle Time                                              | _    | 4    | —   | ms    |                                                                  |

| D123         | TRETD  | Characteristic Retention                                            | 40   | —    | —   | Year  | Provided no other specifications are violated                    |

| D124         | Tref   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(1)</sup> | 1M   | 10M  | —   | E/W   | -40°C to +85°C                                                   |

| D125         | IDDP   | Supply Current during<br>Programming                                | _    | 10   | —   | mA    |                                                                  |

|              |        | Program Flash Memory                                                |      |      |     |       |                                                                  |

| D130         | Eр     | Cell Endurance                                                      | 10K  | 100K | —   | E/W   | -40°C to +85°C                                                   |

| D131         | Vpr    | VDD for Read                                                        | VMIN | —    | 5.5 | V     | VMIN = Minimum operating voltage                                 |

| D132B        | Vpew   | VDD for Self-Timed Write and Row Erase                              | VMIN | —    | 5.5 | V     | VMIN = Minimum operating voltage                                 |

| D133A        | Tiw    | Self-Timed Write Cycle Time                                         | _    | 2    | —   | ms    |                                                                  |

| D134         | TRETD  | Characteristic Retention                                            | 40   | 100  | -   | Year  | Provided no other specifications are violated                    |

| D135         | Iddp   | Supply Current during<br>Programming                                | _    | 10   | —   | mA    |                                                                  |

| TABLE 28-1: | MEMORY PROGRAMMING REQUIREMENTS |

|-------------|---------------------------------|

|-------------|---------------------------------|

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Refer to Section 8.8 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

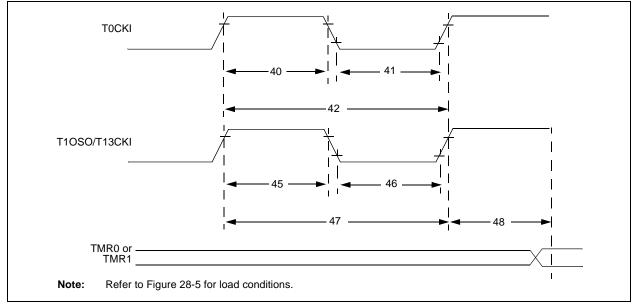

#### FIGURE 28-12: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Symbol    |                           | Characterist            | ic             | Min                                     | Max    | Units | Conditions                               |

|--------------|-----------|---------------------------|-------------------------|----------------|-----------------------------------------|--------|-------|------------------------------------------|

| 40           | T⊤0H      | T0CKI High                | Pulse Width             | No prescaler   | 0.5 Tcy + 20                            | —      | ns    |                                          |

|              |           |                           |                         | With prescaler | 10                                      | —      | ns    |                                          |

| 41           | T⊤0L      | T0CKI Low                 | Pulse Width             | No prescaler   | 0.5 Tcy + 20                            | —      | ns    |                                          |

|              |           |                           |                         | With prescaler | 10                                      | —      | ns    |                                          |

| 42           | T⊤0P      | T0CKI Peri                | bd                      | No prescaler   | Tcy + 10                                | —      | ns    |                                          |

|              |           |                           |                         | With prescaler | Greater of:<br>20 ns or<br>(TcY + 40)/N |        | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |

| 45           | T⊤1H      | T13CKI                    | Synchronous, no         | o prescaler    | 0.5 Tcy + 20                            | —      | ns    |                                          |

|              | High Time |                           | Synchronous,            | PIC18FXXXX     | 10                                      | —      | ns    |                                          |

|              |           |                           | with prescaler          | PIC18LFXXXX    | 25                                      | —      | ns    | VDD = 2.0V                               |

|              |           |                           | Asynchronous            | PIC18FXXXX     | 30                                      | _      | ns    |                                          |

|              |           |                           |                         | PIC18LFXXXX    | 50                                      | _      | ns    | VDD = 2.0V                               |

| 46           | T⊤1L      | T13CKI                    | Synchronous, no         | o prescaler    | 0.5 TCY + 5                             | _      | ns    |                                          |

|              |           | Low Time                  | Synchronous,            | PIC18FXXXX     | 10                                      | _      | ns    |                                          |

|              |           |                           | with prescaler          | PIC18LFXXXX    | 25                                      | _      | ns    | VDD = 2.0V                               |

|              |           |                           | Asynchronous            | PIC18FXXXX     | 30                                      | _      | ns    |                                          |

|              |           |                           |                         | PIC18LFXXXX    | 50                                      | _      | ns    | VDD = 2.0V                               |