Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

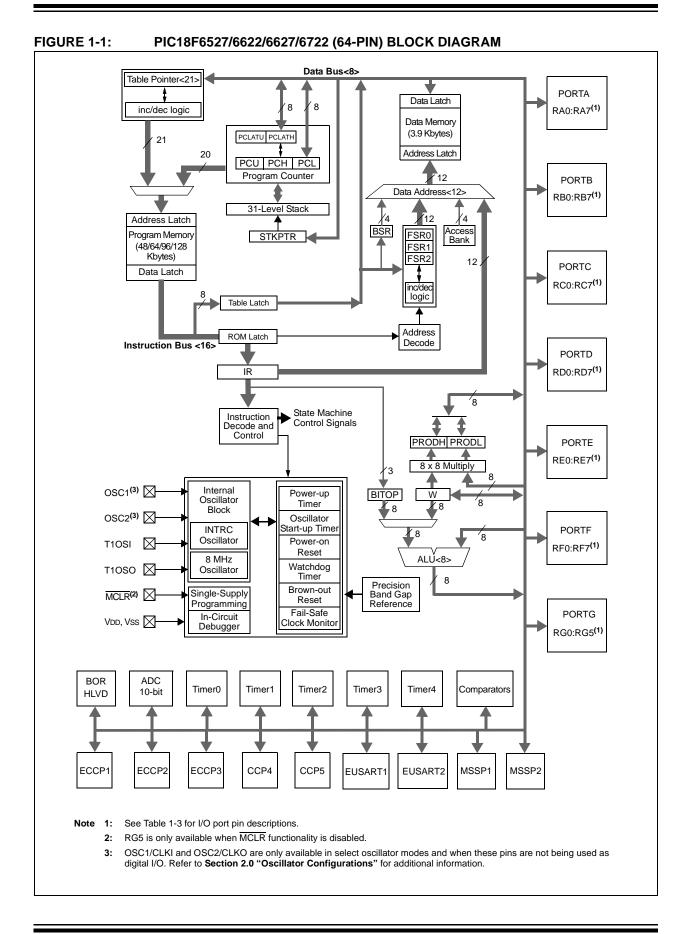

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

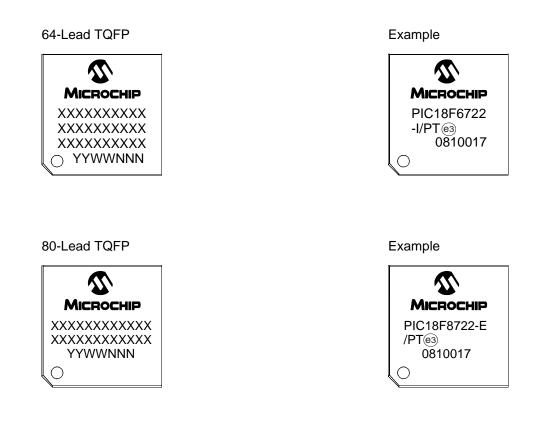

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6622-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                        | Pin Number | Pin           | Buffer         | Description                                                                                                                          |  |

|-------------------------------------------------------------------------------------------------|------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                                                                        | TQFP       | Туре          | Туре           | Description                                                                                                                          |  |

|                                                                                                 |            |               |                | PORTE is a bidirectional I/O port.                                                                                                   |  |

| RE0/RD/P2D<br>RE0<br>RD<br>P2D                                                                  | 2          | I/O<br>I<br>O | ST<br>TTL      | Digital I/O.<br>Read control for Parallel Slave Port.<br>ECCP2 PWM output D.                                                         |  |

| RE1/WR/P2C<br>RE1<br>WR<br>P2C                                                                  | 1          | I/O<br>I<br>O | ST<br>TTL      | Digital I/O.<br>Write control for Parallel Slave Port.<br>ECCP2 PWM output C.                                                        |  |

| RE2/CS/P2B<br>RE2<br>CS<br>P2B                                                                  | 64         | I/O<br>I<br>O | ST<br>TTL      | Digital I/O.<br>Chip select control for Parallel Slave Port.<br>ECCP2 PWM output B.                                                  |  |

| RE3/P3C<br>RE3<br>P3C                                                                           | 63         | I/O<br>O      | ST<br>—        | Digital I/O.<br>ECCP3 PWM output C.                                                                                                  |  |

| RE4/P3B<br>RE4<br>P3B                                                                           | 62         | I/O<br>O      | ST<br>—        | Digital I/O.<br>ECCP3 PWM output B.                                                                                                  |  |

| RE5/P1C<br>RE5<br>P1C                                                                           | 61         | I/O<br>O      | ST<br>—        | Digital I/O.<br>ECCP1 PWM output C.                                                                                                  |  |

| RE6/P1B<br>RE6<br>P1B                                                                           | 60         | I/O<br>O      | ST<br>—        | Digital I/O.<br>ECCP1 PWM output B.                                                                                                  |  |

| RE7/ECCP2/P2A<br>RE7<br>ECCP2 <sup>(2)</sup>                                                    | 59         | I/O<br>I/O    | ST<br>ST       | Digital I/O.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.                                                          |  |

| P2A <sup>(2)</sup>                                                                              |            | 0             |                | ECCP2 PWM output A.                                                                                                                  |  |

| Legend: TTL = TTL compatible input<br>ST = Schmitt Trigger input with<br>I = Input<br>P = Power |            |               | S<br>OS levels | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>I<sup>2</sup>C/SMBus input buffer</li> </ul> |  |

#### TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

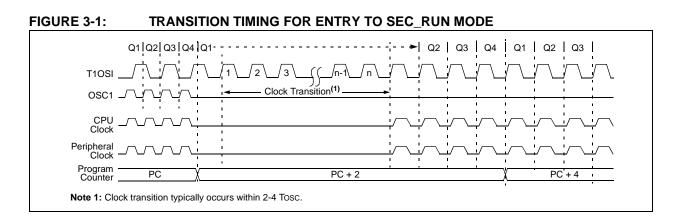

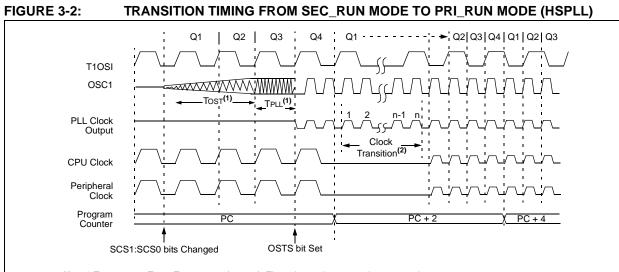

Note1:TOST = 1024 TOSC; TPLL = 2 ms (approx). These intervals are not shown to scale. 2: Clock transition typically occurs within 2-4 TOSC.

# 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer. In this mode, the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

# 5.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 6.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 8.0 "Data EEPROM Memory"**.

## 5.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F6527 and PIC18F8527 each have 48 Kbytes of Flash memory and can store up to 24,576 single-word instructions.

The PIC18F6622 and PIC18F8622 each have 64 Kbytes of Flash memory and can store up to 32,768 single-word instructions.

The PIC18F6627 and PIC18F8627 each have 96 Kbytes of Flash memory and can store up to 49,152 single-word instructions.

The PIC18F6722 and PIC18F8722 each have 128 Kbytes of Flash memory and can store up to 65,536 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for the PIC18F8722 family of devices is shown in Figure 5-1.

### 5.1.1 PIC18F8527/8622/8627/8722 PROGRAM MEMORY MODES

PIC18F8527/8622/8627/8722 devices differ significantly from their PIC18 predecessors in their utilization of program memory. In addition to available on-chip Flash program memory, these controllers can also address up to 2 Mbytes of external program memory through the external memory interface. There are four distinct operating modes available to the controllers:

- Microprocessor (MP)

- Microprocessor with Boot Block (MPBB)

- Extended Microcontroller (EMC)

- Microcontroller (MC)

The program memory mode is determined by setting the two Least Significant bits of the Configuration Register 3L (CONFIG3L) as shown in Register 25-4 (see **Section 25.1 "Configuration Bits**" for additional details on the device Configuration bits).

The program memory modes operate as follows:

- The Microprocessor Mode permits access only to external program memory; the contents of the on-chip Flash memory are ignored. The 21-bit program counter permits access to a 2-Mbyte linear program memory space.

- The Microprocessor with Boot Block Mode accesses on-chip Flash memory from the boot block. Above this, external program memory is accessed all the way up to the 2-Mbyte limit. Program execution automatically switches between the two memories as required. The boot block is configurable to 1, 2 or 4 Kbytes.

- The Microcontroller Mode accesses only on-chip Flash memory. Attempts to read above the physical limit of the on-chip Flash (0BFFFh for the PIC18F8527, 0FFFFh for the PIC18F8622, 17FFFh for the PIC18F8627, 1FFFFh for the PIC18F8722) causes a read of all '0's (a NOP instruction).

The Microcontroller mode is also the only operating mode available to PIC18F6527/6622/6627/6722 devices.

The Extended Microcontroller Mode allows access to both internal and external program memories as a single block. The device can access its entire on-chip Flash memory; above this, the device accesses external program memory up to the 2-Mbyte program space limit. As with Boot Block mode, execution automatically switches between the two memories as required.

In all modes, the microcontroller has complete access to data RAM and EEPROM.

Figure 5-2 compares the memory maps of the different program memory modes. The differences between on-chip and external memory access limitations are more fully explained in Table 5-1.

# 7.0 EXTERNAL MEMORY BUS

Note: The External Memory Bus is not implemented on PIC18F6527/6622/6627/6722 (64-pin) devices.

The External Memory Bus (EMB) allows the device to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory. It supports both 8-bit and 16-bit Data Width modes and four address widths from 8 to 20 bits. The bus is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals.

A list of the pins and their functions is provided in Table 7-1.

| TABLE 7-1: | PIC18F8527/8622/8627/8722 EXTERNAL BUS – I/O PORT FUNCTIONS |

|------------|-------------------------------------------------------------|

|            |                                                             |

| Name     | Port  | Bit | External Memory Bus Function           |

|----------|-------|-----|----------------------------------------|

| RD0/AD0  | PORTD | 0   | Address bit 0 or Data bit 0            |

| RD1/AD1  | PORTD | 1   | Address bit 1 or Data bit 1            |

| RD2/AD2  | PORTD | 2   | Address bit 2 or Data bit 2            |

| RD3/AD3  | PORTD | 3   | Address bit 3 or Data bit 3            |

| RD4/AD4  | PORTD | 4   | Address bit 4 or Data bit 4            |

| RD5/AD5  | PORTD | 5   | Address bit 5 or Data bit 5            |

| RD6/AD6  | PORTD | 6   | Address bit 6 or Data bit 6            |

| RD7/AD7  | PORTD | 7   | Address bit 7 or Data bit 7            |

| RE0/AD8  | PORTE | 0   | Address bit 8 or Data bit 8            |

| RE1/AD9  | PORTE | 1   | Address bit 9 or Data bit 9            |

| RE2/AD10 | PORTE | 2   | Address bit 10 or Data bit 10          |

| RE3/AD11 | PORTE | 3   | Address bit 11 or Data bit 11          |

| RE4/AD12 | PORTE | 4   | Address bit 12 or Data bit 12          |

| RE5/AD13 | PORTE | 5   | Address bit 13 or Data bit 13          |

| RE6/AD14 | PORTE | 6   | Address bit 14 or Data bit 14          |

| RE7/AD15 | PORTE | 7   | Address bit 15 or Data bit 15          |

| RH0/A16  | PORTH | 0   | Address bit 16                         |

| RH1/A17  | PORTH | 1   | Address bit 17                         |

| RH2/A18  | PORTH | 2   | Address bit 18                         |

| RH3/A19  | PORTH | 3   | Address bit 19                         |

| RJ0/ALE  | PORTJ | 0   | Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | 1   | Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | 2   | Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | 3   | Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | 4   | Byte Address bit 0 (BA0)               |

| RJ5/CE   | PORTJ | 5   | Chip Enable (CE) Control pin           |

| RJ6/LB   | PORTJ | 6   | Lower Byte Enable (LB) Control pin     |

| RJ7/UB   | PORTJ | 7   | Upper Byte Enable (UB) Control pin     |

**Note:** For the sake of clarity, only I/O port and external bus assignments are shown here. One or more additional multiplexed features may be available on some pins.

NOTES:

| Pin Name       | Function | TRIS<br>Setting | I/O | I/О<br>Туре | Description                                                                              |

|----------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------|

| RA0/AN0        | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                       |

|                |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                 |

|                | AN0      | 1               | Ι   | ANA         | A/D input channel 0. Default input configuration on POR; does not affect digital output. |

| RA1/AN1        | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                 |

|                | AN1      | 1               | I   | ANA         | A/D input channel 1. Default input configuration on POR; does not affect digital output. |

| RA2/AN2/VREF-  | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled.                             |

|                | AN2      | 1               | Ι   | ANA         | A/D input channel 2. Default input configuration on POR.                                 |

|                | VREF-    | 1               | Ι   | ANA         | Comparator voltage reference low input and A/D voltage reference low input               |

| RA3/AN3/VREF+  | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                 |

|                | AN3      | 1               | Ι   | ANA         | A/D input channel 3. Default input configuration on POR.                                 |

|                | Vref+    | 1               | I   | ANA         | Comparator voltage reference high input and A/D voltage reference high input.            |

| RA4/T0CKI      | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                     |

|                |          | 1               | Ι   | ST          | PORTA<4> data input; default configuration on POR.                                       |

|                | T0CKI    | х               | Ι   | ST          | Timer0 clock input.                                                                      |

| RA5/AN4/HLVDIN | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                 |

|                | AN4      | 1               | Ι   | ANA         | A/D input channel 4. Default configuration on POR.                                       |

|                | HLVDIN   | 1               | I   | ANA         | High/Low-Voltage Detect external trip point input.                                       |

| OSC2/CLKO/RA6  | OSC2     | х               | 0   | ANA         | Main oscillator feedback output connection (XT, HS, HSPLL and LP modes)                  |

|                | CLKO     | x               | 0   | DIG         | System cycle clock output (Fosc/4) in all oscillator modes except RC, INTIO7 and EC.     |

|                | RA6      | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                        |

|                |          | 1               | Ι   | TTL         | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                        |

| OSC1/CLKI/RA7  | OSC1     | х               | I   | ANA         | Main oscillator input connection.                                                        |

|                | CLKI     | x               | Ι   | ANA         | Main clock input connection.                                                             |

|                | RA7      | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                              |

|                |          | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                              |

# TABLE 11-1:PORTA FUNCTIONS

Legend:PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST= Schmitt Buffer Input,<br/>TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| <b>TABLE 11-2:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|--------------------|--------------------------------------------|

|--------------------|--------------------------------------------|

| Name   | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 61                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 60                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 60                         |

| ADCON1 | _                     | —                     | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 59                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

# 17.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The PIC18F8722 family of devices all have a total of five CCP (Capture/Compare/PWM) modules. Two of these (CCP4 and CCP5) implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes and are discussed in this section. The other three modules (ECCP1, ECCP2, ECCP3) implement standard Capture and Compare modes, as well as Enhanced PWM modes. These are discussed in Section 18.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Each CCP/ECCP module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operations in the following sections are described with respect to CCP4, but are equally applicable to CCP5. Capture and Compare operations described in this chapter apply to all standard and Enhanced CCP modules. The operations of PWM mode described in **Section 17.4** "**PWM Mode**" apply to CCP4 and CCP5 only.

Note: Throughout this section and Section 18.0 "Enhanced Capture/Compare/PWM (ECCP) Module", references to register and bit names that may be associated with a specific CCP module are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP4 or CCP5, or ECCP1, ECCP2 or ECCP3. "CCPxCON" is used throughout these sections to refer to the module control register, regardless of whether the CCP module is a standard or enhanced implementation.

## **REGISTER 17-1: CCPxCON: CCPx CONTROL REGISTER (CCP4 AND CCP5 MODULES)**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     |     | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | <b>DCxB&lt;1:0&gt;</b> : PWM Duty Cycle bit 1 and bit 0 for CCP Module x                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Capture mode:                                                                                                                                                                   |

|         | Unused.                                                                                                                                                                         |

|         | Compare mode:                                                                                                                                                                   |

|         | Unused.                                                                                                                                                                         |

|         | PWM mode:                                                                                                                                                                       |

|         | These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCx<9:2>) of the duty cycle are found in CCPRxL. |

| bit 3-0 | CCPxM<3:0>: CCP Module x Mode Select bits                                                                                                                                       |

|         | 0000 = Capture/Compare/PWM disabled; resets CCPx module                                                                                                                         |

|         | 0001 = Reserved                                                                                                                                                                 |

|         | 0010 = Compare mode, toggle output on match; CCPxIF bit is set                                                                                                                  |

|         | 0011 = Reserved                                                                                                                                                                 |

|         | 0100 = Capture mode, every falling edge                                                                                                                                         |

|         | 0101 = Capture mode, every rising edge                                                                                                                                          |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                                      |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                                     |

|         | 1000 = Compare mode, initialize CCPx pin low; on compare match, force CCPx pin high; CCPxIF bit is set                                                                          |

|         | 1001 = Compare mode, initialize CCPx pin high; on compare match, force CCPx pin low; CCPxIF bit is set                                                                          |

|         | 1010 = Compare mode, generate software interrupt on compare match; CCPxIF bit is set; CCPx pin reflects I/O state                                                               |

|         | 1011 = Compare mode, trigger special event; CCPxIF bit is set, CCPx pin is unaffected (For the effects of the trigger, see Section 17.3.4 "Special Event Trigger".)             |

|         | 11xx = PWM mode                                                                                                                                                                 |

## 17.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 17.1.1 CCP MODULES AND TIMER RESOURCES

The CCP/ECCP modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

# TABLE 17-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer1 or Timer3 |

| PWM      | Timer2 or Timer4 |

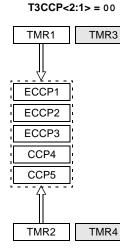

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 15-1). Depending on the configuration selected, up to four timers may be active at once, with modules in the same configuration (Capture/Compare or PWM) sharing timer resources. The possible configurations are shown in Figure 17-1.

#### 17.1.2 ECCP2 PIN ASSIGNMENT

The pin assignment for ECCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin ECCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, ECCP2 is multiplexed with RE7 in Microcontroller mode, or RE3 in all other modes.

Changing the pin assignment of ECCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for ECCP2 operation regardless of where it is located.

#### FIGURE 17-1: CCP AND TIMER INTERCONNECT CONFIGURATIONS

TMR1

ECCP1

TMR2

T3CCP<2:1> = 01

TMR3

ECCP2

ECCP3

CCP4

CCP5

TMR4

Timer1 is used for all Capture and Compare operations for all CCP modules. Timer2 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer3 and Timer4 are not available.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 only (depending on selected mode).

All other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/ Compare or PWM modes.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 and ECCP2 only (depending on the mode selected for each module). Both modules may use a timer as a common time base if they are both in Capture/Compare or PWM modes.

The other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/ Compare or PWM modes. Timer3 is used for all Capture and Compare operations for all CCP modules. Timer4 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer1 and Timer2 are not available.

#### 19.3.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock can be from the primary clock source, the secondary clock (Timer1 oscillator) or the INTOSC source. See Section 2.7 "Clock Sources and Oscillator Switching" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

#### 19.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 19.3.10 BUS MODE COMPATIBILITY

Table 19-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| TABLE 19-1: | SPI BUS MODES |

|-------------|---------------|

|-------------|---------------|

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also an SMP bit which controls when the data is sampled.

#### 19.3.11 SPI CLOCK SPEED AND MODULE INTERACTIONS

Because MSSP1 and MSSP2 are independent modules, they can operate simultaneously at different data rates. Setting the SSPM3:SSPM0 bits of the SSPxCON register determines the rate for the corresponding module.

An exception is when both modules use Timer2 as a time base in Master mode. In this instance, any changes to the Timer2 module's operation will affect both MSSP modules equally. If different bit rates are required for each module, the user should select one of the other three time base options for one of the modules.

#### 19.4.14 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 19.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 19.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 19.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

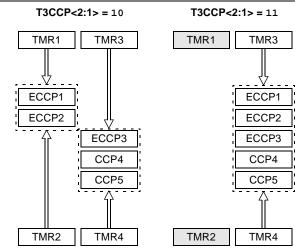

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the  $I^2C$  port to its Idle state (Figure 19-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 19-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# 24.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 24.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG               |                       | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 58                         |

| INTCON  | GIE/GIEH              | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR2    | OSCFIF                | CMIF                  | —      | EEIF   | BCL1IF | HLVDIF | TMR3IF | CCP2IF | 60                         |

| PIE2    | OSCFIE                | CMIE                  | —      | EEIE   | BCL1IE | HLVDIE | TMR3IE | CCP2IE | 60                         |

| IPR2    | OSCFIP                | CMIP                  | _      | EEIP   | BCL1IP | HLVDIP | TMR3IP | CCP2IP | 60                         |

| TRISA   | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 60                         |

#### TABLE 24-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

| U-0                                                                                                                                                             | U-0             | U-0              | R/P-1                | R/P-1                | R/P-1                 | R/P-1                 | R/P-1                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|

| _                                                                                                                                                               | —               | _                | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7                                                                                                                                                           |                 |                  |                      |                      | I                     |                       | bit 0                 |

|                                                                                                                                                                 |                 |                  |                      |                      |                       |                       |                       |

| Legend:                                                                                                                                                         |                 |                  |                      |                      |                       |                       |                       |

| R = Readab                                                                                                                                                      | le bit          | W = Writable     | bit                  | U = Unimpler         | mented bit, read      | l as '0'              |                       |

| -n = Value a                                                                                                                                                    | t POR           | '1' = Bit is set |                      | '0' = Bit is cle     | ared                  | x = Bit is unkr       | Iown                  |

|                                                                                                                                                                 |                 |                  |                      |                      |                       |                       |                       |

| bit 7-5                                                                                                                                                         | Unimplemen      | ted: Read as '   | י'                   |                      |                       |                       |                       |

| bit 4-3                                                                                                                                                         | BORV<1:0>:      | Brown-out Res    | et Voltage bit       | <sub>S</sub> (1)     |                       |                       |                       |

|                                                                                                                                                                 | 11 = Minimun    | n setting        |                      |                      |                       |                       |                       |

|                                                                                                                                                                 |                 |                  |                      |                      |                       |                       |                       |

|                                                                                                                                                                 |                 |                  |                      |                      |                       |                       |                       |

|                                                                                                                                                                 | 00 = Maximur    | n setting        |                      |                      |                       |                       |                       |

| bit 2-1                                                                                                                                                         | (0)             |                  |                      |                      |                       |                       |                       |

|                                                                                                                                                                 | 11 = Brown-     | out Reset enab   | oled in hardwa       | are only (SBOF       | REN is disabled       | )                     |                       |

|                                                                                                                                                                 |                 |                  |                      |                      | sabled in Sleep       |                       | N is disabled)        |

| <ul> <li>01 = Brown-out Reset enabled and controlled by software (SBOREN is enabled)</li> <li>00 = Brown-out Reset disabled in hardware and software</li> </ul> |                 |                  |                      |                      |                       |                       |                       |

| bit 0                                                                                                                                                           |                 |                  |                      |                      |                       |                       |                       |

| 1 = PWRT disabled                                                                                                                                               |                 |                  |                      |                      |                       |                       |                       |

|                                                                                                                                                                 | 0 = PWRT en     |                  |                      |                      |                       |                       |                       |

|                                                                                                                                                                 |                 |                  |                      | h . Ma Ka            |                       |                       |                       |

| Note 1: S                                                                                                                                                       | ee Section 28.1 | Characte         | ristics: Supp        | iy voltage" to       | r specifications.     |                       |                       |

# REGISTER 25-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

| R/P-1        | R/P-1                                           | R/P-1                                   | R/P-1          | U-0              | U-0             | R/P-1           | R/P-1 |  |  |  |

|--------------|-------------------------------------------------|-----------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| WAIT         | BW                                              | ABW1                                    | ABW0           | —                | —               | PM1             | PM0   |  |  |  |

| bit 7        |                                                 |                                         |                |                  |                 |                 | bit C |  |  |  |

| Legend:      |                                                 |                                         |                |                  |                 |                 |       |  |  |  |

| R = Readab   | le bit                                          | W = Writable                            | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | t POR                                           | '1' = Bit is set                        | :              | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |  |  |  |

|              |                                                 |                                         |                |                  |                 |                 |       |  |  |  |

| bit 7        | WAIT: Extern                                    | al Bus Data Wa                          | ait Enable bit |                  |                 |                 |       |  |  |  |

|              |                                                 |                                         |                | ble reads and t  |                 |                 |       |  |  |  |

|              | 0 = Wait sele                                   | ections for table                       | e reads and ta | ble writes are o | determined by   | the WAIT<1:0>   | bits  |  |  |  |

| bit 6        | BW: Data Bu                                     | BW: Data Bus Width Select bit           |                |                  |                 |                 |       |  |  |  |

|              |                                                 | ternal Bus mod                          |                |                  |                 |                 |       |  |  |  |

|              | 0 = 8-bit Exte                                  | ernal Bus mode                          | e              |                  |                 |                 |       |  |  |  |

| bit 5-4      | ABW<1:0>: /                                     | ABW<1:0>: Address Bus Width Select bits |                |                  |                 |                 |       |  |  |  |

|              | 11 = 20-bit address bus                         |                                         |                |                  |                 |                 |       |  |  |  |

|              | 10 = 16-bit a                                   |                                         |                |                  |                 |                 |       |  |  |  |

|              | 01 = 12-bit address bus                         |                                         |                |                  |                 |                 |       |  |  |  |

|              | 00 = 8-bit a                                    |                                         |                |                  |                 |                 |       |  |  |  |

| bit 3-2      | Unimplemen                                      | ted: Read as '                          | 0'             |                  |                 |                 |       |  |  |  |

| bit 1-0      | PM<1:0>: Processor Data Memory Mode Select bits |                                         |                |                  |                 |                 |       |  |  |  |

|              | 11 = Microco                                    | ontroller mode                          |                |                  |                 |                 |       |  |  |  |

|              |                                                 |                                         |                |                  |                 |                 |       |  |  |  |

|              | 10 = Micropr                                    | ocessor mode<br>ocessor with B          |                |                  |                 |                 |       |  |  |  |

# REGISTER 25-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)<sup>(1)</sup>

Note 1: This register is unimplemented in PIC18F6527/6622/6627/6722 devices.

ADD W to f

$\begin{array}{l} 0 \leq f \leq 255 \\ d \, \in \, [0,1] \end{array}$

$a \in [0,1]$

ADDWF f {,d {,a}}

## 26.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                        | ADD Literal to W                  |                |     |    | ADDWF         |  |                                                        |

|--------------------------------------------------------------|-----------------------------------|----------------|-----|----|---------------|--|--------------------------------------------------------|

| Syntax:                                                      | ADDLW                             | ADDLW k        |     |    |               |  | Syntax:                                                |

| Operands:                                                    | $0 \le k \le 255$                 |                |     |    |               |  | Operands:                                              |

| Operation:                                                   | $(W) + k \rightarrow V$           | N              |     |    |               |  |                                                        |

| Status Affected:                                             | N, OV, C, D                       | 0C, Z          |     |    |               |  | Operation:                                             |

| Encoding:                                                    | 0000                              | 1111           | kk} | ck | kkkk          |  | Status Affected:                                       |

| Description:                                                 | The conten<br>8-bit literal<br>W. |                |     |    |               |  | Encoding:<br>Description:                              |

| Words:                                                       | 1                                 |                |     |    |               |  |                                                        |

| Cycles:                                                      | 1                                 |                |     |    |               |  |                                                        |

| Q Cycle Activity:                                            |                                   |                |     |    |               |  |                                                        |

| Q1                                                           | Q2                                | Q3             |     |    | Q4            |  |                                                        |

| Decode                                                       | Read<br>literal 'k'               | Proces<br>Data |     | N  | /rite to<br>W |  |                                                        |

| <u>Example:</u><br>Before Instruc<br>W =<br>After Instructio | tion<br>10h                       | .5h            |     |    |               |  |                                                        |

| W =                                                          | 25h                               |                |     |    |               |  | Words:                                                 |

|                                                              |                                   |                |     |    |               |  | Cycles:                                                |

|                                                              |                                   |                |     |    |               |  | Q Cycle Activity:                                      |

|                                                              |                                   |                |     |    |               |  | Q1                                                     |

|                                                              |                                   |                |     |    |               |  | Decode                                                 |

|                                                              |                                   |                |     |    |               |  | Example:                                               |

|                                                              |                                   |                |     |    |               |  | Before Instructio<br>W =<br>REG =<br>After Instruction |

|                                                              |                                   |                |     |    |               |  | W                                                      |

| Operation:                                     | $(W) + (f) \rightarrow$                                                                                                                                                                                                                                                              | (W) + (f) $\rightarrow$ dest |           |       |                       |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------|-------|-----------------------|--|--|--|

| Status Affected:                               | N, OV, C, [                                                                                                                                                                                                                                                                          | N, OV, C, DC, Z              |           |       |                       |  |  |  |

| Encoding:                                      | 0010                                                                                                                                                                                                                                                                                 | 01da                         | fff       | f     | ffff                  |  |  |  |

| Description:                                   | Add W to r<br>result is sto<br>result is sto<br>(default).                                                                                                                                                                                                                           | ored in W                    | '. If 'd' | is '1 | ', the                |  |  |  |

|                                                | If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                                                                                                                                    |                              |           |       |                       |  |  |  |

|                                                | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                              |           |       |                       |  |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                                                                    |                              |           |       |                       |  |  |  |

| Cycles:                                        | 1                                                                                                                                                                                                                                                                                    |                              |           |       |                       |  |  |  |

| Q Cycle Activity:                              |                                                                                                                                                                                                                                                                                      |                              |           |       |                       |  |  |  |

| Q1                                             | Q2                                                                                                                                                                                                                                                                                   | Q3                           | 3         |       | Q4                    |  |  |  |

| Decode                                         | Read<br>register 'f'                                                                                                                                                                                                                                                                 | Proce<br>Data                |           |       | /rite to<br>stination |  |  |  |

| Example:                                       | ADDWF                                                                                                                                                                                                                                                                                | REG,                         | 0, 0      |       |                       |  |  |  |

| Before Instruc<br>W<br>REG<br>After Instructio | = 17h<br>= 0C2h                                                                                                                                                                                                                                                                      |                              |           |       |                       |  |  |  |

| W<br>REG                                       | = 0D9h<br>= 0C2h                                                                                                                                                                                                                                                                     |                              |           |       |                       |  |  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| ANDWF                                                                  | AND W wit                                                                                               | h f                                                                                                                |                                                      |                                                |  |  |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|--|--|

| Syntax:                                                                | ANDWF                                                                                                   | f {,d {,a}}                                                                                                        |                                                      |                                                |  |  |

| Operands:                                                              | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                          |                                                                                                                    |                                                      |                                                |  |  |

| Operation:                                                             | (W) .AND. (                                                                                             | (f) $\rightarrow$ dest                                                                                             |                                                      |                                                |  |  |

| Status Affected:                                                       | N, Z                                                                                                    |                                                                                                                    |                                                      |                                                |  |  |

| Encoding:                                                              | 0001                                                                                                    | 01da                                                                                                               | ffff                                                 | ffff                                           |  |  |

| Description:                                                           | The conten<br>register 'f'. I<br>in W. If 'd' is<br>in register 'f                                      | f 'd' is '0', th<br>s '1', the res                                                                                 | ne resul                                             | t is stored                                    |  |  |

|                                                                        | lf 'a' is '1', t                                                                                        | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default). |                                                      |                                                |  |  |

|                                                                        | If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 26<br>Bit-Oriente<br>Literal Offs | ed, this ins<br>Literal Offse<br>ever f ≤ 95<br>.2.3 "Byte-<br>ed Instructi                                        | truction<br>et Addre<br>(5Fh).<br>Oriente<br>ions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |

| Words:                                                                 | 1                                                                                                       |                                                                                                                    |                                                      |                                                |  |  |

| Cycles:                                                                | 1                                                                                                       |                                                                                                                    |                                                      |                                                |  |  |

| Q Cycle Activity:                                                      |                                                                                                         |                                                                                                                    |                                                      |                                                |  |  |

| Q1                                                                     | Q2                                                                                                      | Q3                                                                                                                 |                                                      | Q4                                             |  |  |

| Decode                                                                 | Read<br>register 'f'                                                                                    | Process<br>Data                                                                                                    | -                                                    | Vrite to<br>stination                          |  |  |

| Example:<br>Before Instruc<br>W<br>REG<br>After Instructic<br>W<br>REG | = 17h<br>= C2h                                                                                          | REG, 0,                                                                                                            | 0                                                    |                                                |  |  |

вс **Branch if Carry** BC n Syntax: Operands:  $\textbf{-128} \leq n \leq 127$ Operation: if Carry bit is '1'  $(PC) + 2 + 2n \rightarrow PC$ Status Affected: None Encoding: 1110 0010 nnnn nnnn Description: If the Carry bit is '1', then the program will branch. The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a two-cycle instruction. Words: 1 Cycles: 1(2) Q Cycle Activity: If Jump: Q1 Q2 Q3 Q4 Decode Read literal Process Write to PC 'n' Data No No No No operation operation operation operation If No Jump: Q1 Q2 Q3 Q4 Decode Process No Read literal 'n' Data operation Example: HERE BC 5 **Before Instruction** address (HERE) PC = After Instruction If Carry PC

1: =

=

=

=

If Carry PC

address (HERE + 12)

0; address (HERE + 2)

| RCA   | LL             | Relative Call                                                                                                                                                                                                                                                                                                                    |               |     |     |          |  |  |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|----------|--|--|

| Synta | ax:            | RCALL n                                                                                                                                                                                                                                                                                                                          |               |     |     |          |  |  |

| Oper  | ands:          | -1024 ≤ n ≤                                                                                                                                                                                                                                                                                                                      | 1023          |     |     |          |  |  |

| Oper  | ation:         | $(PC) + 2 \rightarrow (PC) + 2 + 2$                                                                                                                                                                                                                                                                                              | ,             | ;   |     |          |  |  |

| Statu | s Affected:    | None                                                                                                                                                                                                                                                                                                                             |               |     |     |          |  |  |

| Enco  | ding:          | 1101                                                                                                                                                                                                                                                                                                                             | 1nnn          | nnn | n   | nnnn     |  |  |

| Desc  | ription:       | Subroutine call with a jump up to 1K from the current location. First, return address (PC + 2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a two-cycle instruction. |               |     |     |          |  |  |

| Cycle |                | 1                                                                                                                                                                                                                                                                                                                                |               |     |     |          |  |  |

| ,     | ycle Activity: | ۷                                                                                                                                                                                                                                                                                                                                |               |     |     |          |  |  |

|       | Q1             | Q2                                                                                                                                                                                                                                                                                                                               | Q3            | 5   |     | Q4       |  |  |

|       | Decode         | Read literal<br>'n'<br>PUSH PC                                                                                                                                                                                                                                                                                                   | Proce<br>Data | 00  | Wri | te to PC |  |  |

|       |                | to stack                                                                                                                                                                                                                                                                                                                         |               |     |     |          |  |  |

|       | No             | No                                                                                                                                                                                                                                                                                                                               | No            |     |     | No       |  |  |

operation

operation

Example: HERE RCALL Jump

operation

Before Instruction

operation

PC = Address (HERE) After Instruction PC = TOS = Address (Jump) Address (HERE + 2)

| RES   | ET             | Reset                                                            |                                                                      |       |          |  |  |

|-------|----------------|------------------------------------------------------------------|----------------------------------------------------------------------|-------|----------|--|--|

| Synta | ax:            | RESET                                                            |                                                                      |       |          |  |  |