Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6622t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 64/80-Pin, 1-Mbit, Enhanced Flash Microcontrollers with 10-Bit A/D and nanoWatt Technology

#### **Power Management Features:**

- Run: CPU On, Peripherals On

- Idle: CPU Off, Peripherals On

- Sleep: CPU Off, Peripherals Off

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 25  $\mu\text{A}$  Typical

- Idle mode Currents Down to 6.8 µA Typical

- Sleep mode Current Down to 120 nA Typical

- Timer1 Oscillator: 900 nA, 32 kHz, 2V

- Watchdog Timer: 1.6 μA, 2V Typical

- Two-Speed Oscillator Start-up

#### Flexible Oscillator Structure:

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) Available for Crystal and Internal Oscillators

- Internal Oscillator Block:

- Fast wake from Sleep and Idle, 1  $\mu s$  typical

- Provides a complete range of clock speeds

- from 31 kHz to 32 MHz when used with PLL

- User-tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three Programmable External Interrupts

- Four Input Change Interrupts

- Enhanced Capture/Compare/PWM (ECCP) module (40/44-pin devices only):

- One, two or four PWM outputs

- Programmable dead time

- Auto-shutdown and auto-restart

### **Peripheral Highlights (Continued):**

- Up to 2 Capture/Compare/PWM (CCP) modules, one with Auto-Shutdown (28-pin devices)

- Master Synchronous Serial Port (MSSP) module Supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- RS-232 operation using internal oscillator block (no external crystal required)

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

- Programmable 16-Level High/Low-Voltage Detection (HLVD) module

### **Special Microcontroller Features:**

- C Compiler Optimized Architecture

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

- Flash/Data EEPROM Retention: 100 Years Typical

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

- Programmable Brown-out Reset (BOR) with Software Enable Option

|            | Prog             | ram Memory                    | Data Memory     |                   |     | 10-Bit | CCP/          |   | MSSI | c                           | E     | tors        | it s               | Bus      |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|--------|---------------|---|------|-----------------------------|-------|-------------|--------------------|----------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D    | ECCP<br>(PWM) |   | SPI  | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External |

| PIC18F6527 | 48K              | 24576                         | 3936            | 1024              | 54  | 12     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6622 | 64K              | 32768                         | 3936            | 1024              | 54  | 12     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6627 | 96K              | 49152                         | 3936            | 1024              | 54  | 12     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6722 | 128K             | 65536                         | 3936            | 1024              | 54  | 12     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F8527 | 48K              | 24576                         | 3936            | 1024              | 70  | 16     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8622 | 64K              | 32768                         | 3936            | 1024              | 70  | 16     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8627 | 96K              | 49152                         | 3936            | 1024              | 70  | 16     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8722 | 128K             | 65536                         | 3936            | 1024              | 70  | 16     | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| Din Nama              | Pin Number       | Pin                    | Buffer       | Description                                                           |

|-----------------------|------------------|------------------------|--------------|-----------------------------------------------------------------------|

| Pin Name              | TQFP             | Туре                   | Туре         | Description                                                           |

|                       |                  |                        |              | PORTF is a bidirectional I/O port.                                    |

| RF0/AN5               | 18               |                        |              |                                                                       |

| RF0                   |                  | I/O                    | ST           | Digital I/O.                                                          |

| AN5                   |                  | I                      | Analog       | Analog input 5.                                                       |

| RF1/AN6/C2OUT         | 17               | 1/0                    | 07           |                                                                       |

| RF1<br>AN6            |                  | I/O<br>I               | ST<br>Analog | Digital I/O.<br>Analog input 6.                                       |

| C2OUT                 |                  | 0                      | Analog       | Comparator 2 output.                                                  |

|                       | 10               | Ŭ                      |              |                                                                       |

| RF2/AN7/C1OUT<br>RF2  | 16               | I/O                    | ST           | Digital I/O.                                                          |

| AN7                   |                  | 1/0                    | Analog       | Analog input 7.                                                       |

| C1OUT                 |                  | ò                      |              | Comparator 1 output.                                                  |

| RF3/AN8               | 15               |                        |              |                                                                       |

| RF3                   | 15               | I/O                    | ST           | Digital I/O.                                                          |

| AN8                   |                  | 1/0                    | Analog       | Analog input 8.                                                       |

| RF4/AN9               | 14               |                        | Ű            |                                                                       |

| RF4                   | 14               | I/O                    | ST           | Digital I/O.                                                          |

| AN9                   |                  | "U                     | Analog       | Analog input 9.                                                       |

| RF5/AN10/CVREF        | 13               |                        | 5            |                                                                       |

| RF5                   | 13               | I/O                    | ST           | Digital I/O.                                                          |

| AN10                  |                  | "."<br>I               | Analog       | Analog input 10.                                                      |

| CVREF                 |                  | 0                      | Analog       | Comparator reference voltage output.                                  |

| RF6/AN11              | 12               |                        |              |                                                                       |

| RF6                   |                  | I/O                    | ST           | Digital I/O.                                                          |

| AN11                  |                  | I                      | Analog       | Analog input 11.                                                      |

| RF7/SS1               | 11               |                        |              |                                                                       |

| RF7                   |                  | I/O                    | ST           | Digital I/O.                                                          |

| SS1                   |                  | I                      | TTL          | SPI slave select input.                                               |

|                       | compatible input | CMO                    |              | = CMOS compatible input or output                                     |

|                       |                  | -                      | OS levels    | Analog= Analog input                                                  |

| I = Input<br>P = Powe |                  | O<br>I <sup>2</sup> C™ |              | <ul> <li>Output</li> <li>I<sup>2</sup>C/SMBus input buffer</li> </ul> |

|                       |                  |                        |              | ion bit, CCP2MX, is set.                                              |

| TABLE 1-3: | PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|---------------------------------------------------------------|

| IADLL I-J. |                                                               |

1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set. Note

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

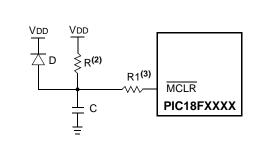

# 4.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In the PIC18F8722 family of devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See Section 11.5 "PORTE, TRISE and LATE Registers" for more information.

### 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004, "Section **28.2** "**DC Characteristics: Power-Down and Supply Current**"). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

#### FIGURE 4-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)<sup>(1)</sup>

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

### 4.4 Brown-out Reset (BOR)

The PIC18F8722 family of devices implements a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR (parameter D005, **Section 28.1 "DC Characteristics"**) for greater than TBOR (parameter 35, Table 28-12) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33, Table 28-12). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling BOR Reset does not automatically enable the PWRT.

#### 4.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,<br>the BOR Reset voltage level is still set by |

|-------|-----------------------------------------------------------------------------------------|

|       | the BORV<1:0> Configuration bits. It cannot be changed in software.                     |

### 4.4.2 DETECTING BOR

When BOR is enabled, the BOR bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any POR event. If BOR is '0' while POR is '1', it can be reliably assumed that a BOR event has occurred.

### 4.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Configuration |        | Status of           |                                                                                    |

|-------------------|--------|---------------------|------------------------------------------------------------------------------------|

| BOREN1            | BOREN0 | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0                 | 0      | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0                 | 1      | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1                 | 0      | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1                 | 1      | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 4-1: BOR CONFIGURATIONS

NOTES:

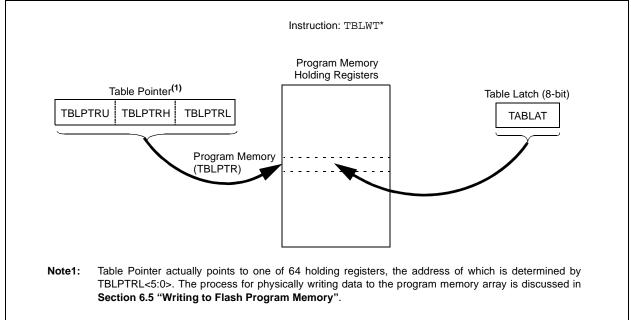

### FIGURE 6-2: TABLE WRITE OPERATION

# 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 25.0** "**Special Features of the CPU**"). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

| Pin Name    | Function | TRIS<br>Setting | I/O | I/O Type | Description                                                                                                   |

|-------------|----------|-----------------|-----|----------|---------------------------------------------------------------------------------------------------------------|

| RC6/TX1/CK1 | RC6      | 0               | 0   | DIG      | LATC<6> data output.                                                                                          |

|             |          | 1               | Ι   | ST       | PORTC<6> data input.                                                                                          |

|             | TX1      | 0               | 0   | DIG      | Asynchronous serial transmit data output (EUSART1 module). Takes priority over port data.                     |

|             | CK1      | 0               | 0   | DIG      | Synchronous serial clock output (EUSART1 module). Takes priority over port data.                              |

|             |          | 1               | Ι   | ST       | Synchronous serial clock input (EUSART1 module).                                                              |

| RC7/RX1/DT1 | RC7      | 0               | 0   | DIG      | LATC<7> data output.                                                                                          |

|             |          | 1               | Ι   | ST       | PORTC<7> data input.                                                                                          |

|             | RX1      | 1               | Ι   | ST       | Asynchronous serial receive data input (EUSART1 module)                                                       |

|             | DT1      | 1               | 0   | DIG      | Synchronous serial data output (EUSART1 module). Takes priority over port data. User must configure as input. |

|             |          | 1               | I   | ST       | Synchronous serial data input (EUSART1 module). User must configure as an input.                              |

### TABLE 11-5: PORTC FUNCTIONS (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when CCP2MX Configuration bit is set.

| TABLE 11-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 60                         |

| LATC  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 60                         |

| TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 60                         |

#### 11.9 PORTJ, TRISJ and LATJ Registers

| Note: | PORTJ   | is     | available    | only       | on |

|-------|---------|--------|--------------|------------|----|

|       | PIC18F8 | 527/86 | 22/8627/8722 | 2 devices. |    |

PORTJ is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISJ. Setting a TRISJ bit (= 1) will make the corresponding PORTJ pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISJ bit (= 0) will make the corresponding PORTJ pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATJ) is also memory mapped. Read-modify-write operations on the LATJ register, read and write the latched output value for PORTJ.

All pins on PORTJ are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note:                         | On a Power-on Reset, these pins ar | е |  |  |  |  |  |

|-------------------------------|------------------------------------|---|--|--|--|--|--|

| configured as digital inputs. |                                    |   |  |  |  |  |  |

When the external memory interface is enabled, all of the PORTJ pins function as control outputs for the interface. This occurs automatically when the interface is enabled by clearing the EBDIS control bit (MEMCON<7>). The TRISJ bits are also overridden.

| EXAMPLE 11-9:   | INITIALIZING PORTJ |

|-----------------|--------------------|

| EAAIVIFLE II-9. |                    |

| CLRF  | PORTJ | ; | Initialize PORTJ by   |

|-------|-------|---|-----------------------|

|       |       | ; | clearing output       |

|       |       | ; | data latches          |

| CLRF  | LATJ  | ; | Alternate method      |

|       |       | ; | to clear output       |

|       |       | ; | data latches          |

| MOVLW | 0xCF  | ; | Value used to         |

|       |       | ; | initialize data       |

|       |       | ; | direction             |

| MOVWF | TRISJ | ; | Set RJ3:RJ0 as inputs |

|       |       | ; | RJ5:RJ4 as output     |

|       |       | ; | RJ7:RJ6 as inputs     |

|       |       |   |                       |

| Name    | Bit 7      | Bit 6                                            | Bit 5     | Bit 4         | Bit 3    | Bit 2  | Bit 1         | Bit 0   | Reset<br>Values<br>on page |

|---------|------------|--------------------------------------------------|-----------|---------------|----------|--------|---------------|---------|----------------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL                                        | TMR0IE    | <b>INTOIE</b> | RBIE     | TMR0IF | <b>INT0IF</b> | RBIF    | 57                         |

| RCON    | IPEN       | SBOREN                                           | _         | RI            | TO       | PD     | POR           | BOR     | 56                         |

| PIR1    | PSPIF      | ADIF                                             | RC1IF     | TX1IF         | SSP1IF   | CCP1IF | TMR2IF        | TMR1IF  | 60                         |

| PIE1    | PSPIE      | ADIE                                             | RC1IE     | TX1IE         | SSP1IE   | CCP1IE | TMR2IE        | TMR1IE  | 60                         |

| IPR1    | PSPIP      | ADIP                                             | RC1IP     | TX1IP         | SSP1IP   | CCP1IP | TMR2IP        | TMR1IP  | 60                         |

| PIR3    | SSP2IF     | BCL2IF                                           | RC2IF     | TX2IF         | TMR4IF   | CCP5IF | CCP4IF        | CCP3IF  | 60                         |

| PIE3    | SSP2IE     | BCL2IF                                           | RC2IE     | TX2IE         | TMR4IE   | CCP5IE | CCP4IE        | CCP3IE  | 60                         |

| IPR3    | SSP2IP     | BCL2IP                                           | RC2IP     | TX2IP         | TMR4IP   | CCP5IP | CCP4IP        | CCP3IP  | 60                         |

| TMR2    | Timer2 Re  | gister                                           |           |               |          |        |               |         | 58                         |

| PR2     | Timer2 Per | riod Register                                    |           |               |          |        |               |         | 58                         |

| T2CON   | —          | T2OUTPS3                                         | T2OUTPS2  | T2OUTPS1      | T2OUTPS0 | TMR2ON | T2CKPS1       | T2CKPS0 | 58                         |

| TMR4    | Timer4 Re  | gister                                           |           |               |          |        |               |         | 61                         |

| PR4     | Timer4 Per | riod Register                                    |           |               |          |        |               |         | 61                         |

| T4CON   | _          | T4OUTPS3                                         | T4OUTPS2  | T4OUTPS1      | T4OUTPS0 | TMR4ON | T4CKPS1       | T4CKPS0 | 61                         |

| CCPR1L  | Enhanced   | Capture/Cor                                      | mpare/PWM | Register 1 Lo | ow Byte  |        |               |         | 59                         |

| CCPR1H  | Enhanced   | Capture/Cor                                      | mpare/PWM | Register 1 H  | igh Byte |        |               |         | 59                         |

| CCPR2L  | Enhanced   | Enhanced Capture/Compare/PWM Register 2 Low Byte |           |               |          |        |               |         |                            |

| CCPR2H  | Enhanced   | Capture/Cor                                      | mpare/PWM | Register 2 H  | igh Byte |        |               |         | 59                         |

| CCP4CON | —          |                                                  | DC4B1     | DC4B0         | CCP4M3   | CCP4M2 | CCP4M1        | CCP4M0  | 61                         |

| CCP5CON |            |                                                  | DC5B1     | DC5B0         | CCP5M3   | CCP5M2 | CCP5M1        | CCP5M0  | 61                         |

# TABLE 17-4: REGISTERS ASSOCIATED WITH PWM, TIMER2 AND TIMER4

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PWM, Timer2 or Timer4.

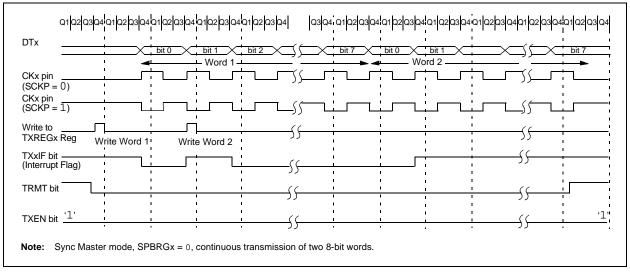

#### 20.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTAx<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTAx<4>). In addition, enable bit SPEN (RCSTAx<7>) is set in order to configure the TXx and RXx pins to CKx (clock) and DTx (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CKx line. Clock polarity is selected with the SCKP bit (BAUDCONx<4>); setting SCKP sets the Idle state on CKx as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSRx). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSRx register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSRx is loaded with new data from the TXREGx (if available). Once the TXREGx register transfers the data to the TSRx register (occurs in one TcY), the TXREGx is empty and the TXxIF flag bit is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF is set regardless of the state of enable bit TXxIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register.

While flag bit TXxIF indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSRx register. TRMT is a read-only bit which is set when the TSRx is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSRx register is empty. The TSRx is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXxIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-11: SYNCHRONOUS TRANSMISSION

| R/W-0        | U-0                                | R/W-0            | R/W-0         | R/W-0                    | R/W-0            | R/W-0          | R/W-0 |

|--------------|------------------------------------|------------------|---------------|--------------------------|------------------|----------------|-------|

| ADFM         |                                    | ACQT2            | ACQT1         | ACQT0                    | ADCS2            | ADCS1          | ADCS0 |

| bit 7        |                                    |                  |               |                          |                  |                | bit ( |

| Legend:      |                                    |                  |               |                          |                  |                |       |

| R = Readab   | le bit                             | W = Writable     | bit           | U = Unimplen             | nented bit, read | d as '0'       |       |

| -n = Value a | t POR                              | '1' = Bit is set |               | '0' = Bit is clea        |                  | x = Bit is unk | nown  |

| bit 7        | ADFM: A/D F                        | Result Format S  | Select bit    |                          |                  |                |       |

|              | 1 = Right just<br>0 = Left justifi |                  |               |                          |                  |                |       |

| bit 6        | Unimplemen                         | ted: Read as '   | 0'            |                          |                  |                |       |

| bit 5-3      | ACQT<2:0>:                         | A/D Acquisitio   | n Time Select | bits                     |                  |                |       |

|              | 111 = 20 TAD                       | )                |               |                          |                  |                |       |

|              | 110 = 16 TAD                       |                  |               |                          |                  |                |       |

|              | 101 = <b>12</b> TAD                | )                |               |                          |                  |                |       |

|              | 100 = 8 TAD<br>011 = 6 TAD         |                  |               |                          |                  |                |       |

|              | 011 = 0 TAD<br>010 = 4 TAD         |                  |               |                          |                  |                |       |

|              | 010 = 4 TAD<br>001 = 2 TAD         |                  |               |                          |                  |                |       |

|              | 000 = 0 TAD <sup>(1)</sup>         | 1)               |               |                          |                  |                |       |

| bit 2-0      | ADCS<2:0>:                         | A/D Conversio    | n Clock Seled | ct bits                  |                  |                |       |

|              | 111 = FRC (C                       | lock derived fro | m A/D RC os   | cillator) <sup>(1)</sup> |                  |                |       |

|              | 110 = Fosc/6                       |                  |               | ,                        |                  |                |       |

|              | 101 = Fosc/1                       | -                |               |                          |                  |                |       |

|              | 100 = Fosc/4                       |                  |               |                          |                  |                |       |

|              |                                    | lock derived fro | om A/D RC os  | scillator)(1)            |                  |                |       |

|              | 010 = Fosc/3<br>001 = Fosc/8       |                  |               |                          |                  |                |       |

|              | 001 = FOSC/2<br>000 = FOSC/2       |                  |               |                          |                  |                |       |

# **Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

#### REGISTER 21-3: ADCON2: A/D CONTROL REGISTER 2

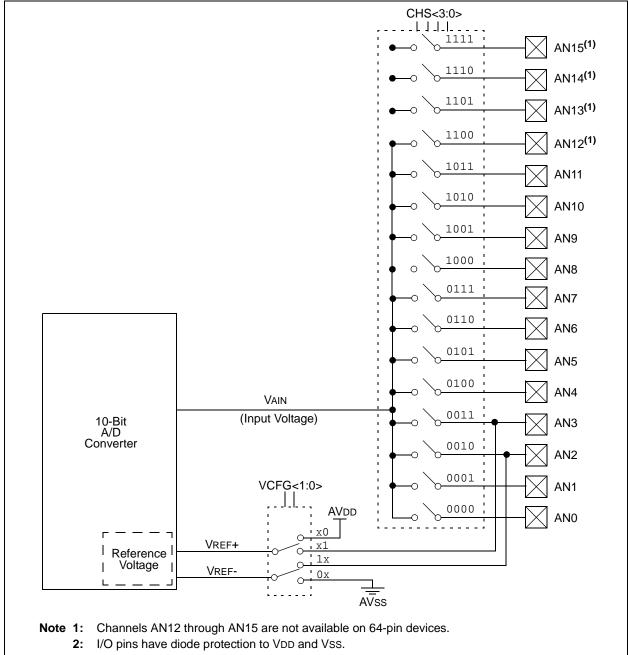

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ and RA2/AN2/VREF- pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input, or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF (PIR1<6>), is set. The block diagram of the A/D module is shown in Figure 21-1.

#### FIGURE 21-1: A/D BLOCK DIAGRAM

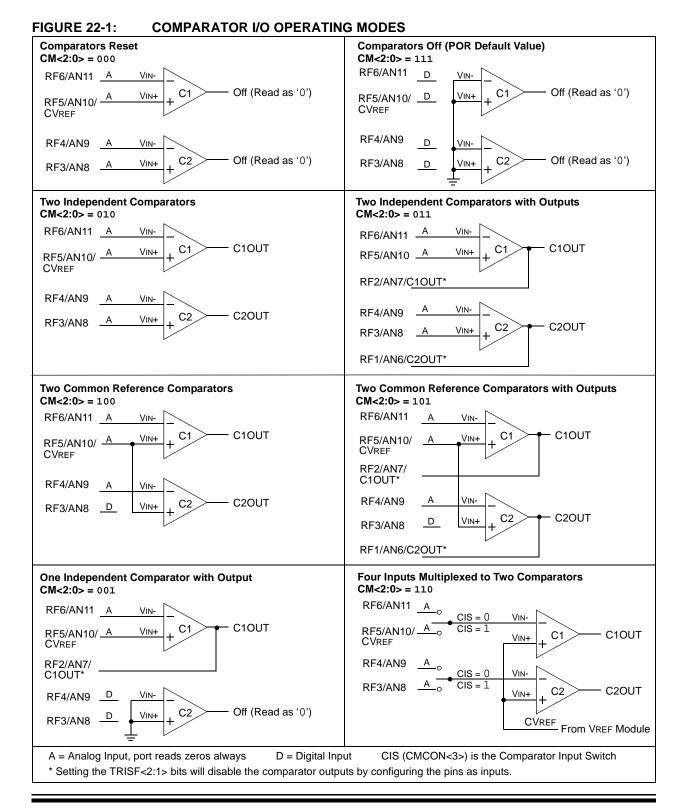

### 22.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 22-1. Bits CM<2:0> of the CMCON register are used to select these modes. The TRISF register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in **Section 28.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

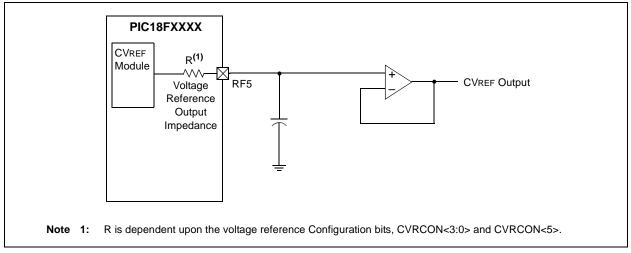

#### FIGURE 23-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 23-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN  | CVROE  | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 59                         |

| CMCON  | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 59                         |

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 60                         |

Legend: Shaded cells are not used with the comparator voltage reference.

| DEC         | FSZ                    | Decrement                                                          | f, Skip if 0                                                                                                                         |                                                                                      |

|-------------|------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Synta       | ax:                    | DECFSZ f                                                           | {,d {,a}}                                                                                                                            |                                                                                      |

| Oper        | ands:                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                |                                                                                                                                      |                                                                                      |

| Oper        | ation:                 | (f) – 1 $\rightarrow$ de skip if result                            | -                                                                                                                                    |                                                                                      |

| Statu       | is Affected:           | None                                                               |                                                                                                                                      |                                                                                      |

| Enco        | oding:                 | 0010                                                               | 11da fff                                                                                                                             | f ffff                                                                               |

| Desc        | ription:               | decremente<br>placed in W                                          | ts of register 'f<br>ed. If 'd' is '0', '<br>/. If 'd' is '1', th<br>< in register 'f'                                               | the result is<br>le result is                                                        |

|             |                        | which is alre                                                      | is '0', the nex<br>eady fetched i<br>s executed ins<br>le instruction.                                                               | s discarded                                                                          |

|             |                        |                                                                    | ne Access Bar<br>ne BSR is use<br>(default).                                                                                         |                                                                                      |

|             |                        | set is enablin Indexed I<br>mode when<br>Section 26<br>Bit-Oriente | nd the extended<br>ed, this instruct<br>Literal Offset A<br>lever $f \le 95$ (50<br>.2.3 "Byte-Or<br>ad Instruction<br>set Mode" for | ction operates<br>Addressing<br>Fh). See<br><b>iented and</b><br><b>s in Indexed</b> |

| Word        | ls:                    | 1                                                                  |                                                                                                                                      |                                                                                      |

| Cycle       | es:                    |                                                                    | rcles if skip an<br>2-word instru                                                                                                    |                                                                                      |

| QC          | ycle Activity:         |                                                                    |                                                                                                                                      |                                                                                      |

|             | Q1                     | Q2                                                                 | Q3                                                                                                                                   | Q4                                                                                   |

|             | Decode                 | Read<br>register 'f'                                               | Process<br>Data                                                                                                                      | Write to<br>destination                                                              |

| lf sk       | in:                    | register i                                                         | Dala                                                                                                                                 | uestination                                                                          |

|             | Q1                     | Q2                                                                 | Q3                                                                                                                                   | Q4                                                                                   |

|             | No                     | No                                                                 | No                                                                                                                                   | No                                                                                   |

|             | operation              | operation                                                          | operation                                                                                                                            | operation                                                                            |

| lf sk       |                        | d by 2-word in:                                                    |                                                                                                                                      | 04                                                                                   |

|             | Q1<br>No               | Q2<br>No                                                           | Q3<br>No                                                                                                                             | Q4<br>No                                                                             |

|             | operation              | operation                                                          | operation                                                                                                                            | operation                                                                            |

|             | No                     | No                                                                 | No                                                                                                                                   | No                                                                                   |

|             | operation              | operation                                                          | operation                                                                                                                            | operation                                                                            |

| <u>Exar</u> | nple:                  | HERE                                                               | DECFSZ<br>GOTO                                                                                                                       | CNT, 1, 1<br>LOOP                                                                    |

|             | Before Instruc         | CONTINUE                                                           |                                                                                                                                      |                                                                                      |

|             | PC<br>After Instructio | = Address                                                          | (HERE)                                                                                                                               |                                                                                      |

|             | CNT<br>If CNT          | = CNT - 1<br>= 0;                                                  |                                                                                                                                      |                                                                                      |

|             | PC<br>If CNT           | = Address<br>$\neq$ 0;                                             |                                                                                                                                      |                                                                                      |

|             | PC                     | = Address                                                          | 6 (HERE + 2                                                                                                                          | )                                                                                    |

| DCF         | SNZ                    | Decrement                                                    | t f, Skip if not                                                                                                                                                                                                                                    | : 0                           |  |  |  |

|-------------|------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| Synta       | ax:                    | DCFSNZ                                                       | f {,d {,a}}                                                                                                                                                                                                                                         |                               |  |  |  |

| Oper        | ands:                  | $0 \le f \le 255$                                            |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             |                        | d ∈ [0,1]<br>a ∈ [0,1]                                       |                                                                                                                                                                                                                                                     |                               |  |  |  |

| Oper        | ation:                 | (f) – 1 $\rightarrow$ de skip if resul                       |                                                                                                                                                                                                                                                     |                               |  |  |  |

| Statu       | is Affected:           | None                                                         |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             |                        | 0100                                                         | 11da ffi                                                                                                                                                                                                                                            |                               |  |  |  |

|             | oding:                 |                                                              |                                                                                                                                                                                                                                                     |                               |  |  |  |

| Desc        | cription:              | decremente<br>placed in V                                    | ts of register 'f<br>ed. If 'd' is '0',<br>/. If 'd' is '1', th<br>k in register 'f'                                                                                                                                                                | the result is<br>ne result is |  |  |  |

|             |                        | instruction<br>discarded a                                   | is not '0', the<br>which is alread<br>and a NOP is e<br>aking it a two-o                                                                                                                                                                            | dy fetched is<br>xecuted      |  |  |  |

|             |                        | ,                                                            | he Access Baı<br>he BSR is use<br>(default).                                                                                                                                                                                                        |                               |  |  |  |

|             |                        | set is enabl<br>in Indexed<br>mode wher<br><b>Section 26</b> | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                               |  |  |  |

| More        | 40.                    | 1                                                            |                                                                                                                                                                                                                                                     | details.                      |  |  |  |

| Word        |                        | -                                                            |                                                                                                                                                                                                                                                     |                               |  |  |  |

| Cycle       | 95.                    |                                                              | ycles if skip a<br>a 2-word instr                                                                                                                                                                                                                   |                               |  |  |  |

| QC          | ycle Activity:         |                                                              |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             | Q1                     | Q2                                                           | Q3                                                                                                                                                                                                                                                  | Q4                            |  |  |  |

|             | Decode                 | Read                                                         | Process                                                                                                                                                                                                                                             | Write to                      |  |  |  |

|             | •                      | register 'f'                                                 | Data                                                                                                                                                                                                                                                | destination                   |  |  |  |

| lf sk       |                        | 02                                                           | 02                                                                                                                                                                                                                                                  | 04                            |  |  |  |

|             | Q1<br>No               | Q2<br>No                                                     | Q3<br>No                                                                                                                                                                                                                                            | Q4<br>No                      |  |  |  |

|             | operation              | operation                                                    | operation                                                                                                                                                                                                                                           | operation                     |  |  |  |

| lf sk       | ip and followed        | d by 2-word in                                               |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             | Q1                     | Q2                                                           | Q3                                                                                                                                                                                                                                                  | Q4                            |  |  |  |

|             | No                     | No                                                           | No                                                                                                                                                                                                                                                  | No                            |  |  |  |

|             | operation              | operation                                                    | operation                                                                                                                                                                                                                                           | operation                     |  |  |  |

|             | No                     | No                                                           | No                                                                                                                                                                                                                                                  | No                            |  |  |  |

|             | operation              | operation                                                    | operation                                                                                                                                                                                                                                           | operation                     |  |  |  |

| <u>Exan</u> | nple:                  | ZERO                                                         | DCFSNZ TEN<br>:<br>:                                                                                                                                                                                                                                | MP, 1, 0                      |  |  |  |

|             | Before Instruc<br>TEMP | =                                                            | ?                                                                                                                                                                                                                                                   |                               |  |  |  |

|             | After Instructio       |                                                              |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             | TEMP<br>If TEMP        | =                                                            | TEMP – 1,<br>0;                                                                                                                                                                                                                                     |                               |  |  |  |

|             |                        |                                                              |                                                                                                                                                                                                                                                     |                               |  |  |  |

|             | PC                     | =                                                            | Address (                                                                                                                                                                                                                                           | ZERO)                         |  |  |  |

|             |                        | =<br>≠                                                       |                                                                                                                                                                                                                                                     |                               |  |  |  |

| GOTO                                   |                   | Unconditi                                                       | onal Brai                               | nch               |                |                                   |  |

|----------------------------------------|-------------------|-----------------------------------------------------------------|-----------------------------------------|-------------------|----------------|-----------------------------------|--|

| Syntax:                                |                   | GOTO k                                                          |                                         |                   |                |                                   |  |

| Operands:                              |                   | $0 \le k \le 10^4$                                              | ≤ k ≤ 1048575                           |                   |                |                                   |  |

| Operation:                             |                   | $k \rightarrow PC<2$                                            | 0:1>                                    |                   |                |                                   |  |

| Status Affe                            | cted:             | None                                                            |                                         |                   |                |                                   |  |

| Encoding:<br>1st word (k<br>2nd word(k | ,                 | 1110<br>1111                                                    | 1111<br>k19kkk                          | k7kł<br>kkk       |                | kkkk0<br>kkkk8                    |  |

| Description                            | 1:                | GOTO allow<br>anywhere<br>range. The<br>PC<20:1><br>instruction | within enti<br>20-bit va<br>. GOTO is a | re 2-M<br>lue 'k' | lbyte<br>is lo | e memory<br>aded into             |  |

| Words:                                 |                   | 2                                                               |                                         |                   |                |                                   |  |

| Cycles:                                |                   | 2                                                               |                                         |                   |                |                                   |  |

| Q Cycle A                              | ctivity:          |                                                                 |                                         |                   |                |                                   |  |

| (                                      | Q1                | Q2                                                              | Q3                                      |                   |                | Q4                                |  |

| Dec                                    | code              | Read literal<br>'k'<7:0>,                                       | No<br>operat                            | ion               | 'k'•           | ad literal<br><19:8>,<br>te to PC |  |

|                                        | No<br>ration      | No<br>operation                                                 | No<br>operat                            | ion               | ор             | No<br>eration                     |  |

|                                        | nstructic<br>PC = | GOTO THE<br>on<br>Address (1                                    |                                         |                   |                |                                   |  |

| INCF                                                                        | Increment                                                           | f                                                                                                                                                                                                                                                                                        |                    |                |                       |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-----------------------|--|

| Syntax:                                                                     | INCF f {,c                                                          | d {,a}}                                                                                                                                                                                                                                                                                  |                    |                |                       |  |

| Operands:                                                                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                 | d ∈ [0,1]                                                                                                                                                                                                                                                                                |                    |                |                       |  |

| Operation:                                                                  | (f) + 1 $\rightarrow$ de                                            | est                                                                                                                                                                                                                                                                                      |                    |                |                       |  |

| Status Affected:                                                            | C, DC, N,                                                           | OV, Z                                                                                                                                                                                                                                                                                    |                    |                |                       |  |

| Encoding:                                                                   | 0010                                                                | 10da                                                                                                                                                                                                                                                                                     | fff                | f              | ffff                  |  |

| Description:                                                                | The conten<br>incremente<br>placed in V<br>placed bac               | d. If 'd' is<br>V. If 'd' is                                                                                                                                                                                                                                                             | '0', th<br>'1', th | ne re<br>e re: | esult is<br>sult is   |  |

|                                                                             | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank                    | he BSR i                                                                                                                                                                                                                                                                                 |                    |                |                       |  |

|                                                                             | set is enab<br>in Indexed<br>mode wher<br>Section 26<br>Bit-Oriente | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                    |                |                       |  |

| Words:                                                                      | 1                                                                   |                                                                                                                                                                                                                                                                                          |                    |                |                       |  |

| Cycles:                                                                     | 1                                                                   |                                                                                                                                                                                                                                                                                          |                    |                |                       |  |

| Q Cycle Activity:                                                           |                                                                     |                                                                                                                                                                                                                                                                                          |                    |                |                       |  |

| Q1                                                                          | Q2                                                                  | Q3                                                                                                                                                                                                                                                                                       |                    |                | Q4                    |  |