Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 96KB (48K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6627-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                    | Pin Number        | Pin                                       | Buffer    | Description                                                                                                                          |  |  |

|-------------------------------------------------------------|-------------------|-------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                    | TQFP              | Туре                                      | Туре      | Description                                                                                                                          |  |  |

|                                                             |                   |                                           |           | PORTE is a bidirectional I/O port.                                                                                                   |  |  |

| RE0/RD/P2D<br>RE0<br>RD<br>P2D                              | 2                 | I/O<br>I<br>O                             | ST<br>TTL | Digital I/O.<br>Read control for Parallel Slave Port.<br>ECCP2 PWM output D.                                                         |  |  |

| RE1/WR/P2C<br>RE1<br>WR<br>P2C                              | 1                 | I/O<br>I<br>O                             | ST<br>TTL | Digital I/O.<br>Write control for Parallel Slave Port.<br>ECCP2 PWM output C.                                                        |  |  |

| RE2/CS/P2B<br>RE2<br>CS<br>P2B                              | 64                | I/O<br>I<br>O                             | ST<br>TTL | Digital I/O.<br>Chip select control for Parallel Slave Port.<br>ECCP2 PWM output B.                                                  |  |  |

| RE3/P3C<br>RE3<br>P3C                                       | 63                | I/O<br>O                                  | ST<br>—   | Digital I/O.<br>ECCP3 PWM output C.                                                                                                  |  |  |

| RE4/P3B<br>RE4<br>P3B                                       | 62                | I/O<br>O                                  | ST<br>—   | Digital I/O.<br>ECCP3 PWM output B.                                                                                                  |  |  |

| RE5/P1C<br>RE5<br>P1C                                       | 61                | I/O<br>O                                  | ST<br>—   | Digital I/O.<br>ECCP1 PWM output C.                                                                                                  |  |  |

| RE6/P1B<br>RE6<br>P1B                                       | 60                | I/O<br>O                                  | ST<br>—   | Digital I/O.<br>ECCP1 PWM output B.                                                                                                  |  |  |

| RE7/ECCP2/P2A<br>RE7<br>ECCP2 <sup>(2)</sup>                | 59                | I/O<br>I/O                                | ST<br>ST  | Digital I/O.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.                                                          |  |  |

| P2A <sup>(2)</sup>                                          |                   | 0                                         |           | ECCP2 PWM output A.                                                                                                                  |  |  |

| Legend: $TTL = TTL c$<br>ST = Schm<br>I = Input<br>P = Powe | itt Trigger input | CMO<br>with CM0<br>O<br>I <sup>2</sup> C™ |           | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>I<sup>2</sup>C/SMBus input buffer</li> </ul> |  |  |

### TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                                                                                                                                                                                                     | Pin Number | Pin           | Buffer                 | Description                                                              |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|------------------------|--------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                              | TQFP       | Туре          | Туре                   | Description                                                              |  |  |

|                                                                                                                                                                                                              |            |               |                        | PORTF is a bidirectional I/O port.                                       |  |  |

| RF0/AN5<br>RF0<br>AN5                                                                                                                                                                                        | 24         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 5.                                          |  |  |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT                                                                                                                                                                         | 23         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 6.<br>Comparator 2 output.                  |  |  |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT                                                                                                                                                                         | 18         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 7.<br>Comparator 1 output.                  |  |  |

| RF3/AN8<br>RF3<br>AN8                                                                                                                                                                                        | 17         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 8.                                          |  |  |

| RF4/AN9<br>RF4<br>AN9                                                                                                                                                                                        | 16         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 9.                                          |  |  |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF                                                                                                                                                                       | 15         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog input 10.<br>Comparator reference voltage output. |  |  |

| RF6/AN11<br>RF6<br>AN11                                                                                                                                                                                      | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 11.                                         |  |  |

| RF7/SS1<br><u>RF7</u><br>SS1                                                                                                                                                                                 | 13         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                  |  |  |

| Legend:TTL = TTL compatible inputCMOS= CMOS compatible input or outputST = Schmitt Trigger input with CMOS levels AnalogAnalog inputI = InputO= OutputP = Power $I^2C^{TM}/SMB$ = $I^2C/SMB$ us input buffer |            |               |                        |                                                                          |  |  |

| TABLE 1-4: | PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS ( |  |

|------------|-----------------------------------------------------|--|

|            |                                                     |  |

**Note 1:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

### 2.0 OSCILLATOR CONFIGURATIONS

### 2.1 Oscillator Types

The PIC18F8722 family of devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL enabled

- 5. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 output

- 10. ECIO External Clock with I/O on RA6

### 2.2 Crystal Oscillator/Ceramic Resonators

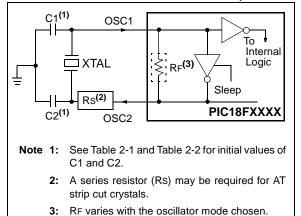

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

Note: Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

### FIGURE 2-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

### TABLE 2-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Typical Capacitor Values Used:                   |          |       |       |  |  |  |

|--------------------------------------------------|----------|-------|-------|--|--|--|

| Mode                                             | Freq     | OSC1  | OSC2  |  |  |  |

| ХТ                                               | 3.58 MHz | 22 pF | 22 pF |  |  |  |

| Osenselten verkens and fan deslam mulden as anke |          |       |       |  |  |  |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588 PIC<sup>®</sup> Microcontroller Oscillator Design Guide

- AN826 Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices

- AN849 Basic PIC<sup>®</sup> Oscillator Design

- AN943 Practical PIC<sup>®</sup> Oscillator Analysis and Design

- AN949 Making Your Oscillator Work

See the notes following Table 2-2 for additional information.

When using resonators with frequencies Note: above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor may be placed between the OSC2 pin and the resonator. good starting point, As а the recommended value of Rs is 330Ω.

### 14.0 TIMER2 MODULE

The Timer2 timer module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSPx module

The module is controlled through the T2CON register (Register 14-1), which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 14-1.

### 14.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options; these are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>). The value of TMR2 is compared to that of the period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see **Section 14.2 "Timer2 Interrupt**").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                                                     |                    |  |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |

|                   |                  |                                                     |                    |  |  |  |

|         | Onimplemented. Read as 0                          |

|---------|---------------------------------------------------|

| bit 6-3 | T2OUTPS<3:0>: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         | •                                                 |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMR2ON: Timer2 On bit                             |

|         | 1 = Timer2 is on                                  |

|         | 0 = Timer2 is off                                 |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 1x = Prescaler is 16                              |

|         |                                                   |

Inimplemented Read as '0'

hit 7

### 17.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

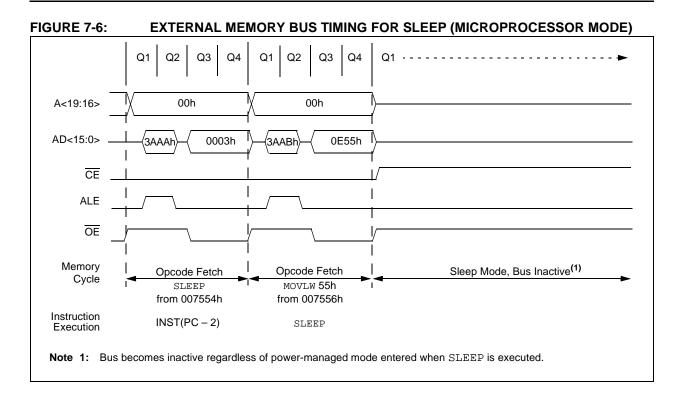

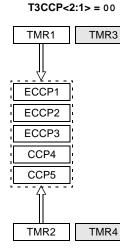

#### 17.1.1 CCP MODULES AND TIMER RESOURCES

The CCP/ECCP modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

### TABLE 17-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode | Timer Resource   |  |  |  |  |

|----------|------------------|--|--|--|--|

| Capture  | Timer1 or Timer3 |  |  |  |  |

| Compare  | Timer1 or Timer3 |  |  |  |  |

| PWM      | Timer2 or Timer4 |  |  |  |  |

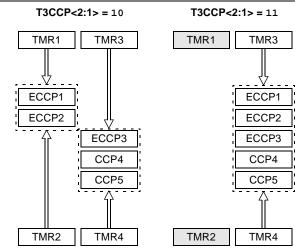

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 15-1). Depending on the configuration selected, up to four timers may be active at once, with modules in the same configuration (Capture/Compare or PWM) sharing timer resources. The possible configurations are shown in Figure 17-1.

#### 17.1.2 ECCP2 PIN ASSIGNMENT

The pin assignment for ECCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin ECCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, ECCP2 is multiplexed with RE7 in Microcontroller mode, or RE3 in all other modes.

Changing the pin assignment of ECCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for ECCP2 operation regardless of where it is located.

### FIGURE 17-1: CCP AND TIMER INTERCONNECT CONFIGURATIONS

TMR1

ECCP1

TMR2

T3CCP<2:1> = 01

TMR3

ECCP2

ECCP3

CCP4

CCP5

TMR4

Timer1 is used for all Capture and Compare operations for all CCP modules. Timer2 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer3 and Timer4 are not available.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 only (depending on selected mode).

All other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/ Compare or PWM modes.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 and ECCP2 only (depending on the mode selected for each module). Both modules may use a timer as a common time base if they are both in Capture/Compare or PWM modes.

The other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/ Compare or PWM modes. Timer3 is used for all Capture and Compare operations for all CCP modules. Timer4 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer1 and Timer2 are not available.

| R/W-0         | R/W-0                                                                                                                                             | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R-1            | R/W-0 |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|------------------|------------------|----------------|-------|--|--|--|--|--|

| CSRC          | TX9                                                                                                                                               | TXEN                              | SYNC            | SENDB            | BRGH             | TRMT           | TX9D  |  |  |  |  |  |

| bit 7         | -                                                                                                                                                 |                                   |                 |                  |                  |                | bit   |  |  |  |  |  |

|               |                                                                                                                                                   |                                   |                 |                  |                  |                |       |  |  |  |  |  |

| Legend:       |                                                                                                                                                   |                                   |                 |                  |                  |                |       |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                             | W = Writable                      |                 | -                | mented bit, read | d as '0'       |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                               | '1' = Bit is se                   | et              | '0' = Bit is cle | eared            | x = Bit is unk | nown  |  |  |  |  |  |

| bit 7         | CSRC: Cloc                                                                                                                                        | k Source Selec                    | t bit           |                  |                  |                |       |  |  |  |  |  |

|               | Asynchrono                                                                                                                                        |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Don't care.                                                                                                                                       |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Synchronou                                                                                                                                        |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   | node (clock ge<br>ode (clock from |                 |                  |                  |                |       |  |  |  |  |  |

| bit 6         |                                                                                                                                                   | ransmit Enable                    |                 | ,                |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   | 9-bit transmissi                  |                 |                  |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   | 8-bit transmissi                  | on              |                  |                  |                |       |  |  |  |  |  |

| bit 5         | <b>TXEN:</b> Transmit Enable bit<br>1 = Transmit enabled                                                                                          |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | 1 = Transmi0 = Transmi                                                                                                                            |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Note:                                                                                                                                             | SREN/CREN o                       | verrides TXEN   | l in Sync mode   |                  |                |       |  |  |  |  |  |

| bit 4         | SYNC: EUS                                                                                                                                         | ART Mode Sel                      | ect bit         |                  |                  |                |       |  |  |  |  |  |

|               | 1 = Synchro<br>0 = Asynchr                                                                                                                        | nous mode<br>onous mode           |                 |                  |                  |                |       |  |  |  |  |  |

| bit 3         | SENDB: Se                                                                                                                                         | nd Break Chara                    | acter bit       |                  |                  |                |       |  |  |  |  |  |

|               | Asynchronous mode:                                                                                                                                |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | <ul> <li>1 = Send Sync Break on next transmission (cleared by hardware upon completion)</li> <li>0 = Sync Break transmission completed</li> </ul> |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Synchronous mode:                                                                                                                                 |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Don't care.                                                                                                                                       |                                   |                 |                  |                  |                |       |  |  |  |  |  |

| bit 2         | -                                                                                                                                                 | n Baud Rate Se                    | lect bit        |                  |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   | Asynchronous mode:                |                 |                  |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   | 1 = High speed<br>0 = Low speed   |                 |                  |                  |                |       |  |  |  |  |  |

|               | <u>Synchronou</u>                                                                                                                                 |                                   |                 |                  |                  |                |       |  |  |  |  |  |

|               | Unused in th                                                                                                                                      |                                   |                 |                  |                  |                |       |  |  |  |  |  |

| bit 1         |                                                                                                                                                   | smit Shift Regis                  | ster Status bit |                  |                  |                |       |  |  |  |  |  |

|               | 1 = TSRx er<br>0 = TSRx fu                                                                                                                        |                                   |                 |                  |                  |                |       |  |  |  |  |  |

| bit 0         |                                                                                                                                                   | bit of Transmit                   | Data            |                  |                  |                |       |  |  |  |  |  |

|               | Can be add                                                                                                                                        | ress/data bit or                  | a parity bit.   |                  |                  |                |       |  |  |  |  |  |

|               |                                                                                                                                                   |                                   |                 |                  |                  |                |       |  |  |  |  |  |

### REGISTER 20-1: TXSTAx: TRANSMIT STATUS AND CONTROL REGISTER

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | FOSC = 40.000 MHZ     |                               | Fosc                        | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | —                     | _                             | _                           |                       | _          | _                           |                       | _          | _                           |                       | _          | _                           |

| 1.2         | —                     | _                             | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | —                     | —          | —                           |

| 57.6        | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _          | —                           |

| 115.2       | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | —                     | _          | _                           |

### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|             | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fos                           | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                         | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2         | 1.202                         | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4         | 2.404                         | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | —          | —                           |

| 9.6         | 8.929                         | -6.99      | 6                           | —                     | _          | _                           | _                     | _          | —                           |

| 19.2        | 20.833                        | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6        | 62.500                        | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2       | 62.500                        | -45.75     | 0                           | _                     | —          | —                           | _                     | —          |                             |

|             |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |                      |     |                       |            |                             |                       |            |                             |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|----------------------|-----|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |                      |     | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | e <sup>%</sup> value |     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3         | —                     | _                             | _                           | _                     | _                    | _   | _                     |            | _                           | _                     | _          | _                           |  |

| 1.2         | —                     | —                             | —                           | —                     | —                    | —   | —                     |            | —                           | —                     | —          | —                           |  |

| 2.4         | —                     | —                             | —                           | —                     | _                    | —   | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |

| 9.6         | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16                 | 129 | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |

| 19.2        | 19.231                | 0.16                          | 129                         | 19.231                | 0.16                 | 64  | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |

| 57.6        | 58.140                | 0.94                          | 42                          | 56.818                | -1.36                | 21  | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |

| 115.2       | 113.636               | -1.36                         | 21                          | 113.636               | -1.36                | 10  | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Foso                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | _                     |                               | _                           | _                     | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | —                           |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | —                           | _                     | _          | —                           |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           | _                     | —          | —                           |                       | —          | —                           |  |  |

© 2008 Microchip Technology Inc.

| R/P-1        | R/P-1                                   | R/P-1                                                                        | R/P-1          | U-0                                 | U-0             | R/P-1           | R/P-1 |  |  |  |  |  |

|--------------|-----------------------------------------|------------------------------------------------------------------------------|----------------|-------------------------------------|-----------------|-----------------|-------|--|--|--|--|--|

| WAIT         | BW                                      | ABW1                                                                         | ABW0           | _                                   | —               | PM1             | PM0   |  |  |  |  |  |

| bit 7        |                                         |                                                                              |                |                                     |                 |                 | bit C |  |  |  |  |  |

| Legend:      |                                         |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

| R = Readal   | ble bit                                 | W = Writable                                                                 | bit            | U = Unimpler                        | nented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a | at POR                                  | '1' = Bit is set                                                             |                | '0' = Bit is cle                    | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

|              |                                         |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

| bit 7        | WAIT: Extern                            | nal Bus Data W                                                               | ait Enable bit |                                     |                 |                 |       |  |  |  |  |  |

|              |                                         |                                                                              |                | ble reads and t<br>ble writes are o |                 | the WAIT<1:0>   | bits  |  |  |  |  |  |

| bit 6        |                                         | is Width Select                                                              |                |                                     | ,               |                 |       |  |  |  |  |  |

|              | 1 = 16-bit Ex                           | kternal Bus mo                                                               | de             |                                     |                 |                 |       |  |  |  |  |  |

|              | 0 = 8-bit Ext                           | ernal Bus mode                                                               | 9              |                                     |                 |                 |       |  |  |  |  |  |

| bit 5-4      | ABW<1:0>: Address Bus Width Select bits |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

|              |                                         | 11 = 20-bit address bus                                                      |                |                                     |                 |                 |       |  |  |  |  |  |

|              | 10 = 16-bit                             |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

|              | 01 = 12-bit<br>00 = 8-bit a             |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

| bit 3-2      |                                         |                                                                              | 0'             |                                     |                 |                 |       |  |  |  |  |  |

| bit 1-0      | -                                       | Unimplemented: Read as '0'                                                   |                |                                     |                 |                 |       |  |  |  |  |  |

| DIL 1-0      |                                         | PM<1:0>: Processor Data Memory Mode Select bits<br>11 = Microcontroller mode |                |                                     |                 |                 |       |  |  |  |  |  |

|              |                                         | rocessor mode                                                                |                |                                     |                 |                 |       |  |  |  |  |  |

|              |                                         |                                                                              |                |                                     |                 |                 |       |  |  |  |  |  |

|              |                                         | rocessor with B                                                              | oot Block mo   | de                                  |                 |                 |       |  |  |  |  |  |

### REGISTER 25-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)<sup>(1)</sup>

Note 1: This register is unimplemented in PIC18F6527/6622/6627/6722 devices.

| MOVFF                                                | Move f to f                                                                   |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------|--|--|--|--|--|

| Syntax:                                              | MOVFF f <sub>s</sub>                                                          | ,f <sub>d</sub>                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_{s} \leq 409 \\ 0 \leq f_{d} \leq 409 \end{array}$ |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Operation:                                           | $(f_{S}) \to f_{d}$                                                           | $(f_s) \rightarrow f_d$                                                                                                                                                                                                                                               |              |                                |  |  |  |  |  |

| Status Affected:                                     | None                                                                          |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                  | ffff<br>ffff                                                                                                                                                                                                                                                          | ffff<br>ffff | ffffs<br>ffffd                 |  |  |  |  |  |

| Description:                                         | moved to d<br>Location of<br>in the 4096<br>FFFh) and                         | The contents of source register ' $f_s$ ' are<br>moved to destination register ' $f_d$ '.<br>Location of source ' $f_s$ ' can be anywhere<br>in the 4096-byte data space (000h to<br>FFFh) and location of destination ' $f_d$ '<br>can also be anywhere from 000h to |              |                                |  |  |  |  |  |

|                                                      |                                                                               | Either source or destination can be W (a useful special situation).                                                                                                                                                                                                   |              |                                |  |  |  |  |  |

|                                                      | transferring<br>peripheral r                                                  | MOVFF is particularly useful for<br>transferring a data memory location to a<br>peripheral register (such as the transmit<br>buffer or an I/O port).                                                                                                                  |              |                                |  |  |  |  |  |

|                                                      | The MOVFF<br>PCL, TOSU<br>destination                                         | J, TOSH                                                                                                                                                                                                                                                               |              |                                |  |  |  |  |  |

| Words:                                               | 2                                                                             |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Cycles:                                              | 2 (3)                                                                         |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Q Cycle Activity:                                    |                                                                               |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

| Q1                                                   | Q2                                                                            | Q3                                                                                                                                                                                                                                                                    |              | Q4                             |  |  |  |  |  |

| Decode                                               | Read<br>register 'f'<br>(src)                                                 | Proce<br>Data                                                                                                                                                                                                                                                         |              | No<br>peration                 |  |  |  |  |  |

| Decode                                               | No<br>operation<br>No dummy<br>read                                           | No<br>operat                                                                                                                                                                                                                                                          |              | Write<br>egister 'f'<br>(dest) |  |  |  |  |  |

| Example:                                             |                                                                               | REG1, F                                                                                                                                                                                                                                                               | EG2          |                                |  |  |  |  |  |

| Before Instruc<br>REG1<br>REG2                       | = 33<br>= 11                                                                  |                                                                                                                                                                                                                                                                       |              |                                |  |  |  |  |  |

33h 33h

= =

| MOVLB                     | Move Liter                | ral to Lo                                                                                                                                                         | w Nibl | ble i | n BSR                |  |  |  |

|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------------|--|--|--|

| Syntax:                   | MOVLW F                   | (                                                                                                                                                                 |        |       |                      |  |  |  |

| Operands:                 | $0 \le k \le 255$         |                                                                                                                                                                   |        |       |                      |  |  |  |

| Operation:                | $k \to BSR$               |                                                                                                                                                                   |        |       |                      |  |  |  |

| Status Affected:          | None                      | None                                                                                                                                                              |        |       |                      |  |  |  |

| Encoding:                 | 0000                      | 0001                                                                                                                                                              | kkk    | k     | kkkk                 |  |  |  |

| Description:              | Bank Select<br>of BSR<7:4 | The eight-bit literal 'k' is loaded into the<br>Bank Select Register (BSR). The value<br>of BSR<7:4> always remains '0'<br>regardless of the value of $k_7:k_4$ . |        |       |                      |  |  |  |

| Words:                    | 1                         | 1                                                                                                                                                                 |        |       |                      |  |  |  |

| Cycles:                   | 1                         | 1                                                                                                                                                                 |        |       |                      |  |  |  |

| Q Cycle Activity:         |                           |                                                                                                                                                                   |        |       |                      |  |  |  |

| Q1                        | Q2                        | Q3                                                                                                                                                                | 3      |       | Q4                   |  |  |  |

| Decode                    | Read<br>literal 'k'       | Proce<br>Data                                                                                                                                                     |        |       | te literal<br>to BSR |  |  |  |

| Example:                  | MOVLB                     | 5                                                                                                                                                                 |        |       |                      |  |  |  |

| Before Instruc<br>BSR Reg |                           | !h                                                                                                                                                                |        |       |                      |  |  |  |

After Instruction BSR Register = 05h

After Instruction REG1 REG2

| RLNCF                                                          | Rotate Left f (no carry)                                                                                                                                                                                                               | RRCF              | Rotate Right f through Carry                                                                                                                                                                                                                                                        |  |  |  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                        | RLNCF f {,d {,a}}                                                                                                                                                                                                                      | Syntax:           | RRCF f {,d {,a}}                                                                                                                                                                                                                                                                    |  |  |  |

| Operands:                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                     | Operands:         | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                 |  |  |  |

| Operation:                                                     | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                          | Operation:        | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow C,$<br>$(C) \rightarrow dest < 7 >$                                                                                                                                                                               |  |  |  |

| Status Affected:                                               | N, Z                                                                                                                                                                                                                                   | Status Affected:  |                                                                                                                                                                                                                                                                                     |  |  |  |

| Encoding:                                                      | 0100 01da ffff ffff                                                                                                                                                                                                                    |                   | C, N, Z                                                                                                                                                                                                                                                                             |  |  |  |

| Description:                                                   | The contents of register 'f' are rotated                                                                                                                                                                                               | Encoding:         | 0011 00da ffff ffff                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                | one bit to the left. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.                                                | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in W.<br>If 'd' is '1', the result is placed back in                                                                                                |  |  |  |

|                                                                | If 'a' is '1', the BSR is used to select the                                                                                                                                                                                           |                   | register 'f' (default).                                                                                                                                                                                                                                                             |  |  |  |

| GPR bank (default).<br>If 'a' is '0' and the extended instruct |                                                                                                                                                                                                                                        |                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                                                                                                                                  |  |  |  |

|                                                                | set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                   | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |  |  |  |

| Words:                                                         | 1                                                                                                                                                                                                                                      |                   | C→ register f                                                                                                                                                                                                                                                                       |  |  |  |

| Cycles:                                                        | 1                                                                                                                                                                                                                                      |                   |                                                                                                                                                                                                                                                                                     |  |  |  |

| Q Cycle Activity:                                              |                                                                                                                                                                                                                                        | Words:            | 1                                                                                                                                                                                                                                                                                   |  |  |  |

| Q Cycle Activity.                                              | Q2 Q3 Q4                                                                                                                                                                                                                               | Cycles:           | 1                                                                                                                                                                                                                                                                                   |  |  |  |

| Decode                                                         | Read Process Write to                                                                                                                                                                                                                  | Q Cycle Activity: |                                                                                                                                                                                                                                                                                     |  |  |  |

| Dooddo                                                         | register 'f' Data destination                                                                                                                                                                                                          | Q1                | Q2 Q3 Q4                                                                                                                                                                                                                                                                            |  |  |  |

|                                                                |                                                                                                                                                                                                                                        | Decode            | Read Process Write to                                                                                                                                                                                                                                                               |  |  |  |

| Example:                                                       | RLNCF REG, 1, 0                                                                                                                                                                                                                        |                   | register 'f' Data destination                                                                                                                                                                                                                                                       |  |  |  |

| Before Instru                                                  | ction                                                                                                                                                                                                                                  |                   |                                                                                                                                                                                                                                                                                     |  |  |  |

| REG                                                            | = 1010 1011                                                                                                                                                                                                                            | Example:          | RRCF REG, 0, 0                                                                                                                                                                                                                                                                      |  |  |  |

| After Instruct                                                 | ion                                                                                                                                                                                                                                    | Before Instruc    | ction                                                                                                                                                                                                                                                                               |  |  |  |