Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6627t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                  | Pin Number            | Pin                    | Buffer           | Description                                                                                                                         |  |  |  |

|-----------------------------------------------------------|-----------------------|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                  | TQFP                  | Туре                   | Туре             | Description                                                                                                                         |  |  |  |

|                                                           |                       |                        |                  | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                       |  |  |  |

| RB0/INT0/FLT0<br>RB0<br>INT0<br>FLT0                      | 58                    | I/O<br>I<br>I          | TTL<br>ST<br>ST  | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for ECCPx.                                                                 |  |  |  |

| RB1/INT1<br>RB1<br>INT1                                   | 57                    | I/O<br>I               | TTL<br>ST        | Digital I/O.<br>External interrupt 1.                                                                                               |  |  |  |

| RB2/INT2<br>RB2<br>INT2                                   | 56                    | I/O<br>I               | TTL<br>ST        | Digital I/O.<br>External interrupt 2.                                                                                               |  |  |  |

| RB3/INT3/ECCP2/P2A<br>RB3<br>INT3<br>ECCP2 <sup>(1)</sup> | 55                    | I/O<br>I<br>O          | TTL<br>ST<br>—   | Digital I/O.<br>External interrupt 3.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.                                |  |  |  |

| P2A <sup>(1)</sup>                                        |                       | 0                      | _                | ECCP2 PWM output A.                                                                                                                 |  |  |  |

| RB4/KBI0<br>RB4<br>KBI0                                   | 54                    | I/O<br>I               | TTL<br>TTL       | Digital I/O.<br>Interrupt-on-change pin.                                                                                            |  |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                        | 53                    | I/O<br>I<br>I/O        | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                                               |  |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                        | 52                    | I/O<br>I<br>I/O        | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pir                                     |  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                        | 47<br>ompatible input | I/O<br>I<br>I/O<br>CMC | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.<br>= CMOS compatible input or output |  |  |  |

#### TABLE 1-4. PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

= Schmitt Trigger input with CMOS levels Analog= Analog input ST

| • | - 00111111 | ingger input man enree level | o / malog = / malog mput              |

|---|------------|------------------------------|---------------------------------------|

|   | = Input    | 0                            | = Output                              |

|   | = Power    | I <sup>2</sup> C™/SMB        | = I <sup>2</sup> C/SMBus input buffer |

$$P = Power \qquad I^2 C^{TM}/SMB$$

Note 1: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

- 2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

- 3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

- 4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

- 5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

Т

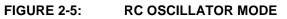

## 2.4 RC Oscillator

For timing insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of REXT and CEXT

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-5 shows how the R/C combination is connected.

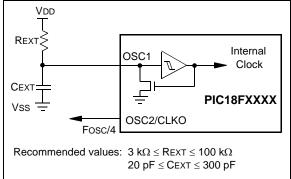

The RCIO Oscillator mode (Figure 2-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

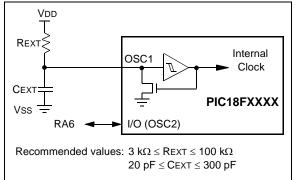

## 2.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 2.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available when this mode is configured as the primary clock source.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

### 2.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 2.6.4 "PLL in INTOSC Modes"**.

## 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the device clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after either of the SCS<1:0> bits are changed, following a brief clock transition interval. The SCS bits are reset on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source (31 kHz), the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source derived from the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source and disables the INTOSC to reduce current consumption.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Additionally, the INTOSC source will already be stable should a switch to a higher frequency be needed quickly. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer and PLL Start-up Timer (if enabled) have timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable.

The IDLEN bit controls whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 3.0** "Power-Managed Modes".

| Note 1: | The Timer1 oscillator must be enabled to<br>select the secondary clock source. The<br>Timer1 oscillator is enabled by setting the<br>T1OSCEN bit in the Timer1 Control regis- |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | ter (T1CON<3>). If the Timer1 control regis-<br>is not enabled, then any attempt to select<br>a secondary clock source will be ignored.                                       |  |  |  |  |  |

| 2:      | It is recommended that the Timer1 oscillator be operating and stable before                                                                                                   |  |  |  |  |  |

2: It is recommended that the filmer oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

### 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F8722 family of devices contains circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes**".

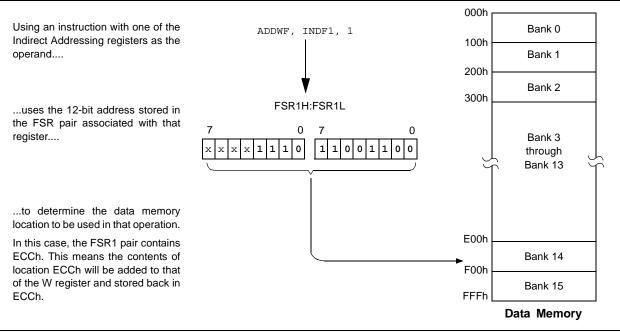

## 5.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### 5.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by the value in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

## 7.0 EXTERNAL MEMORY BUS

Note: The External Memory Bus is not implemented on PIC18F6527/6622/6627/6722 (64-pin) devices.

The External Memory Bus (EMB) allows the device to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory. It supports both 8-bit and 16-bit Data Width modes and four address widths from 8 to 20 bits. The bus is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals.

A list of the pins and their functions is provided in Table 7-1.

| TABLE 7-1: | PIC18F8527/8622/8627/8722 EXTERNAL BUS – I/O PORT FUNCTIONS |

|------------|-------------------------------------------------------------|

|            |                                                             |

| Name     | Port  | Bit | External Memory Bus Function           |

|----------|-------|-----|----------------------------------------|

| RD0/AD0  | PORTD | 0   | Address bit 0 or Data bit 0            |

| RD1/AD1  | PORTD | 1   | Address bit 1 or Data bit 1            |

| RD2/AD2  | PORTD | 2   | Address bit 2 or Data bit 2            |

| RD3/AD3  | PORTD | 3   | Address bit 3 or Data bit 3            |

| RD4/AD4  | PORTD | 4   | Address bit 4 or Data bit 4            |

| RD5/AD5  | PORTD | 5   | Address bit 5 or Data bit 5            |

| RD6/AD6  | PORTD | 6   | Address bit 6 or Data bit 6            |

| RD7/AD7  | PORTD | 7   | Address bit 7 or Data bit 7            |

| RE0/AD8  | PORTE | 0   | Address bit 8 or Data bit 8            |

| RE1/AD9  | PORTE | 1   | Address bit 9 or Data bit 9            |

| RE2/AD10 | PORTE | 2   | Address bit 10 or Data bit 10          |

| RE3/AD11 | PORTE | 3   | Address bit 11 or Data bit 11          |

| RE4/AD12 | PORTE | 4   | Address bit 12 or Data bit 12          |

| RE5/AD13 | PORTE | 5   | Address bit 13 or Data bit 13          |

| RE6/AD14 | PORTE | 6   | Address bit 14 or Data bit 14          |

| RE7/AD15 | PORTE | 7   | Address bit 15 or Data bit 15          |

| RH0/A16  | PORTH | 0   | Address bit 16                         |

| RH1/A17  | PORTH | 1   | Address bit 17                         |

| RH2/A18  | PORTH | 2   | Address bit 18                         |

| RH3/A19  | PORTH | 3   | Address bit 19                         |

| RJ0/ALE  | PORTJ | 0   | Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | 1   | Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | 2   | Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | 3   | Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | 4   | Byte Address bit 0 (BA0)               |

| RJ5/CE   | PORTJ | 5   | Chip Enable (CE) Control pin           |

| RJ6/LB   | PORTJ | 6   | Lower Byte Enable (LB) Control pin     |

| RJ7/UB   | PORTJ | 7   | Upper Byte Enable (UB) Control pin     |

**Note:** For the sake of clarity, only I/O port and external bus assignments are shown here. One or more additional multiplexed features may be available on some pins.

| Name   | Bit 7                            | Bit 6         | Bit 5         | Bit 4       | Bit 3    | Bit 2  | Bit 1                     | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------------------|---------------|---------------|-------------|----------|--------|---------------------------|--------|----------------------------|

| INTCON | GIE/GIEH                         | PEIE/GIEL     | TMR0IE        | INT0IE      | RBIE     | TMR0IF | INT0IF                    | RBIF   | 57                         |

| EEADRH | —                                | —             | —             | —           | —        | —      | EEPROM Ac<br>Register Hig |        | 59                         |

| EEADR  | EEPROM Address Register Low Byte |               |               |             |          |        |                           | 59     |                            |

| EEDATA | EEPROM Data Register             |               |               |             |          |        |                           | 59     |                            |

| EECON2 | EEPROM                           | Control Regis | ster 2 (not a | physical re | egister) |        |                           |        | 59                         |

| EECON1 | EEPGD                            | CFGS          | _             | FREE        | WRERR    | WREN   | WR                        | RD     | 59                         |

| IPR2   | OSCFIP                           | CMIP          | —             | EEIP        | BCL1IP   | HLVDIP | TMR3IP                    | CCP2IP | 60                         |

| PIR2   | OSCFIF                           | CMIF          | —             | EEIF        | BCL1IF   | HLVDIF | TMR3IF                    | CCP2IF | 60                         |

| PIE2   | OSCFIE                           | CMIE          | —             | EEIE        | BCL1IE   | HLVDIE | TMR3IE                    | CCP2IE | 60                         |

TABLE 8-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count, but will not change the prescaler    |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                 | Bit 6                     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------|---------------------------|--------|--------|--------|--------|---------------|--------|----------------------------|

| TMR0L  | Timer0 Reg            | Timer0 Register Low Byte  |        |        |        |        |               |        |                            |

| TMR0H  | Timer0 Reg            | Timer0 Register High Byte |        |        |        |        |               |        | 58                         |

| INTCON | GIE/GIEH              | PEIE/GIEL                 | TMR0IE | INT0IE | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 57                         |

| T0CON  | TMR0ON                | T08BIT                    | TOCS   | TOSE   | PSA    | T0PS2  | T0PS1         | T0PS0  | 58                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup>     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1        | TRISA0 | 60                         |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

#### 15.2 Timer3 16-bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer3 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

#### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If any of the CCP modules are configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. ECCP2 can also start an A/D conversion if the A/D module is enabled (see **Section 17.3.4 "Special Event Trigger"** for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

**Note:** The Special Event Triggers from the CCPx module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR2   | OSCFIF                    | CMIF      | _       | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 60                         |

| PIE2   | OSCFIE                    | CMIE      | _       | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 60                         |

| IPR2   | OSCFIP                    | CMIP      | _       | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 60                         |

| TMR3L  | Timer3 Register Low Byte  |           |         |         |         |        |        | 59     |                            |

| TMR3H  | Timer3 Register High Byte |           |         |         |         |        | 59     |        |                            |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 58                         |

| T3CON  | RD16                      | T3CCP2    | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 59                         |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

| Name                 | Bit 7      | Bit 6         | Bit 5     | Bit 4        | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|------------|---------------|-----------|--------------|-----------|--------|--------|--------|----------------------------|

| INTCON               | GIE/GIEH   | PEIE/GIEL     | TMR0IE    | INT0IE       | RBIE      | TMR0IF | INT0IF | RBIF   | 57                         |

| RCON                 | IPEN       | SBOREN        | _         | RI           | TO        | PD     | POR    | BOR    | 56                         |

| PIR1                 | PSPIF      | ADIF          | RC1IF     | TX1IF        | SSP1IF    | CCP1IF | TMR2IF | TMR1IF | 60                         |

| PIE1                 | PSPIE      | ADIE          | RC1IE     | TX1IE        | SSP1IE    | CCP1IE | TMR2IE | TMR1IE | 60                         |

| IPR1                 | PSPIP      | ADIP          | RC1IP     | TX1IP        | SSP1IP    | CCP1IP | TMR2IP | TMR1IP | 60                         |

| PIR2                 | OSCFIF     | CMIF          | _         | EEIF         | BCL1IF    | HLVDIF | TMR3IF | CCP2IF | 60                         |

| PIE2                 | OSCFIE     | CMIE          | _         | EEIE         | BCL1IE    | HLVDIE | TMR3IE | CCP2IE | 60                         |

| IPR2                 | OSCFIP     | CMIP          | _         | EEIP         | BCL1IP    | HLVDIP | TMR3IP | CCP2IP | 60                         |

| PIR3                 | SSP2IF     | BCL2IF        | RC2IF     | TX2IF        | TMR4IF    | CCP5IF | CCP4IF | CCP3IF | 60                         |

| PIE3                 | SSP2IE     | BCL2IE        | RC2IE     | TX2IE        | TMR4IE    | CCP5IE | CCP4IE | CCP3IE | 60                         |

| IPR3                 | SSP2IP     | BCL2IP        | RC2IP     | TX2IP        | TMR4IP    | CCP5IP | CCP4IP | CCP3IP | 60                         |

| TRISB                | TRISB7     | TRISB6        | TRISB5    | TRISB4       | TRISB3    | TRISB2 | TRISB1 | TRISB0 | 60                         |

| TRISC                | TRISC7     | TRISC6        | TRISC5    | TRISC4       | TRISC3    | TRISC2 | TRISC1 | TRISC0 | 60                         |

| TRISE                | TRISE7     | TRISE6        | TRISE5    | TRISE4       | TRISE3    | TRISE2 | TRISE1 | TRISE0 | 60                         |

| TRISG                |            | _             | _         | TRISG4       | TRISG3    | TRISG2 | TRISG1 | TRISG0 | 60                         |

| TRISH <sup>(1)</sup> | TRISH7     | TRISH6        | TRISH5    | TRISH4       | TRISH3    | TRISH2 | TRISH1 | TRISH0 | 60                         |

| TMR1L                | Timer1 Reg | gister Low B  | yte       |              |           |        |        |        | 58                         |

| TMR1H                | Timer1 Reg | gister High E | Byte      |              |           |        |        |        | 58                         |

| T1CON                | RD16       | T1RUN         | T1CKPS1   | T1CKPS0      | T1OSCEN   | T1SYNC | TMR1CS | TMR10N | 58                         |

| TMR3H                | Timer3 Reg | gister High E | Byte      |              |           |        | 1      |        | 59                         |

| TMR3L                | Timer3 Reg | gister Low B  | yte       |              |           |        |        |        | 59                         |

| T3CON                | RD16       | T3CCP2        | T3CKPS1   | T3CKPS0      | T3CCP1    | T3SYNC | TMR3CS | TMR3ON | 59                         |

| CCPR1L               | Enhanced   | Capture/Cor   | mpare/PWN | Register 1   | Low Byte  |        |        |        | 59                         |

| CCPR1H               | Enhanced   | Capture/Cor   | mpare/PWN | 1 Register 1 | High Byte |        |        |        | 59                         |

| CCP1CON              | P1M1       | P1M0          | DC1B1     | DC1B0        | CCP1M3    | CCP1M2 | CCP1M1 | CCP1M0 | 59                         |

| CCPR2L               | Enhanced   | Capture/Cor   | mpare/PWN | I Register 2 | Low Byte  |        | 1      |        | 59                         |

| CCPR2H               | Enhanced   | Capture/Cor   | mpare/PWN | I Register 2 | High Byte |        |        |        | 59                         |

| CCP2CON              | P2M1       | P2M0          | DC2B1     | DC2B0        | CCP2M3    | CCP2M2 | CCP2M1 | CCP2M0 | 59                         |

| CCP3CON              | P3M1       | P3M0          | DC3B1     | DC3B0        | CCP3M3    | CCP3M2 | CCP3M1 | CCP3M0 | 59                         |

| CCP4CON              | —          | —             | DC4B1     | DC4B0        | CCP4M3    | CCP4M2 | CCP4M1 | CCP4M0 | 61                         |

| CCP5CON              | —          | —             | DC5B1     | DC5B0        | CCP5M3    | CCP5M2 | CCP5M1 | CCP5M0 | 61                         |

| TABI F 17-2.                        | REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3  |

|-------------------------------------|----------------------------------------------------------------|

| $I \land D \sqcup \sqcup I I = Z$ . | REGISTERS ACCOUNTED WITH OAT TORE, COMINARE, TIMERT AND TIMERS |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

Note 1: Implemented on 80-pin devices only.

| CCP3CON<br>Configuration                                                       | RG0                                                                                                                                                                                                                                                         | RE4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RH4                                                                                                                  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                | PIC18F                                                                                                                                                                                                                                                      | 6527/6622/662                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7/6722 Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |  |  |  |  |  |  |

| 00xx 11xx                                                                      | ECCP3                                                                                                                                                                                                                                                       | RE4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N/A                                                                                                                  |  |  |  |  |  |  |

| 10xx 11xx                                                                      | P3A                                                                                                                                                                                                                                                         | P3B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N/A                                                                                                                  |  |  |  |  |  |  |

| x1xx 11xx                                                                      | P3A                                                                                                                                                                                                                                                         | P3B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CCP4/P3D <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N/A                                                                                                                  |  |  |  |  |  |  |

| PIC18F8527/                                                                    | 8622/8627/872                                                                                                                                                                                                                                               | 22 Devices, EC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPMX = 1, Mi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | crocontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |  |  |  |  |  |  |

| 00xx 11xx                                                                      | ECCP3                                                                                                                                                                                                                                                       | RE4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RH5/AN13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RH4/AN12                                                                                                             |  |  |  |  |  |  |