Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6722-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                | LP, XT, HS                    |                                       |                                    |

| Primary Device Clock           | HSPLL                         | Tcsd <sup>(1)</sup>                   | OSTS                               |

| (PRI_IDLE mode)                | EC, RC                        | 10.30 ( )                             |                                    |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| T1OSC or INTRC                 | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

| INTOSC <sup>(2)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

| (Sleep mode)                   | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

Note 1: TCSD (parameter 38, Table 28-12) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies. On Reset, INTOSC defaults to 1 MHz.

**3:** TOST is the Oscillator Start-up Timer (parameter 32, Table 28-12). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12, Table 28-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 28-12), the INTOSC stabilization period.

| R/W-0                        | R/W-1 <sup>(1)</sup>                                                                               | U-0                                                                                                                                          | R/W-1                    | R-1               | R-1             | R/W-0 <sup>(2)</sup> | R/W-0      |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|-----------------|----------------------|------------|--|--|--|

| IPEN                         | SBOREN                                                                                             | —                                                                                                                                            | RI                       | TO                | PD              | POR                  | BOR        |  |  |  |

| bit 7                        |                                                                                                    |                                                                                                                                              |                          |                   |                 |                      | bit        |  |  |  |

|                              |                                                                                                    |                                                                                                                                              |                          |                   |                 |                      |            |  |  |  |

| <b>Legend:</b><br>R = Readat | hle hit                                                                                            | W = Writable                                                                                                                                 | hit                      | II – I Inimpler   | nented bit, rea | ad as 'O'            |            |  |  |  |

| -n = Value a                 |                                                                                                    | '1' = Bit is se                                                                                                                              |                          | 0' = Bit is cle   |                 | x = Bit is unkn      | own        |  |  |  |

|                              |                                                                                                    |                                                                                                                                              |                          |                   |                 |                      | 0111       |  |  |  |

| bit 7                        | IPEN: Interru                                                                                      | pt Priority Ena                                                                                                                              | ble bit                  |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | iority levels or                                                                                                                             |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    |                                                                                                                                              |                          | IC16CXXX Co       | mpatibility mod | de)                  |            |  |  |  |

| bit 6                        |                                                                                                    | OR Software E                                                                                                                                | nable bit <sup>(1)</sup> |                   |                 |                      |            |  |  |  |

|                              | <u>If BOREN&lt;1:</u>                                                                              |                                                                                                                                              |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | 1 = BOR is enabled<br>0 = BOR is disabled                                                                                                    |                          |                   |                 |                      |            |  |  |  |

|                              | If BOREN<1:                                                                                        | 0> = <u>00, 10 or</u>                                                                                                                        | <u>11:</u>               |                   |                 |                      |            |  |  |  |

|                              | Bit is disabled                                                                                    | d and read as '                                                                                                                              | 0'                       |                   |                 |                      |            |  |  |  |

| bit 5                        | Unimplemen                                                                                         | ted: Read as                                                                                                                                 | '0'                      |                   |                 |                      |            |  |  |  |

| bit 4                        |                                                                                                    | struction Flag                                                                                                                               |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | 1 = The RESET instruction was not executed (set by firmware only)                                                                            |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | <ul> <li>0 = The RESET instruction was executed causing a device Reset (must be set in software after<br/>Brown-out Reset occurs)</li> </ul> |                          |                   |                 |                      |            |  |  |  |

| bit 3                        |                                                                                                    |                                                                                                                                              |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | <b>TO:</b> Watchdog Time-out Flag bit<br>1 = Set by power-up, CLRWDT instruction or SLEEP instruction                                        |                          |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | ime-out occurr                                                                                                                               |                          |                   |                 |                      |            |  |  |  |

| bit 2                        |                                                                                                    | own Detection                                                                                                                                | •                        |                   |                 |                      |            |  |  |  |

|                              |                                                                                                    | 1 = Set by power-up or by the CLRWDT instruction                                                                                             |                          |                   |                 |                      |            |  |  |  |

| <b>L</b> :L 4                | 0 = Set by execution of the SLEEP instruction <b>POR:</b> Power-on Reset Status bit <sup>(2)</sup> |                                                                                                                                              |                          |                   |                 |                      |            |  |  |  |

| bit 1                        |                                                                                                    |                                                                                                                                              |                          | (set by firmwar   |                 |                      |            |  |  |  |

|                              |                                                                                                    |                                                                                                                                              |                          |                   |                 | er-on Reset occur    | s)         |  |  |  |

| bit 0                        |                                                                                                    | out Reset Stat                                                                                                                               |                          |                   |                 |                      | ,          |  |  |  |

|                              | 1 = A Brown                                                                                        | 1 = A Brown-out Reset has not occurred (set by firmware only)                                                                                |                          |                   |                 |                      |            |  |  |  |

|                              | 0 = A Brown                                                                                        | -out Reset occ                                                                                                                               | urred (must b            | e set in softwar  | e after a Brow  | n-out Reset occu     | ırs)       |  |  |  |

| Note 1:                      | If SBOREN is ena                                                                                   | bled, its Reset                                                                                                                              | state is '1': ot         | herwise, it is '0 |                 |                      |            |  |  |  |

|                              | The actual Reset                                                                                   |                                                                                                                                              |                          |                   |                 | See the notes foll   | owing this |  |  |  |

| r                            | register and Secti                                                                                 | on 4.6 "Reset                                                                                                                                | State of Reg             | isters" for add   | itional informa | ition.               | -          |  |  |  |

#### REGISTER 4-1: RCON: RESET CONTROL REGISTER

**Note 1:** It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after POR).

#### 5.1.3.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 25.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st PUSH will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st PUSH and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st PUSH and STKPTR will remain at 31. When the stack has been popped enough times to unload the stack, the next POP will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                |

#### 5.1.3.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

### REGISTER 5-1: STKPTR: STACK POINTER REGISTER

| R/C-0                 | R/C-0                                                                                       | U-0                                                               | R/W-0                                                  | R/W-0            | R/W-0            | R/W-0           | R/W-0          |  |

|-----------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|------------------|------------------|-----------------|----------------|--|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup>                                                                       | _                                                                 | SP4                                                    | SP3              | SP2              | SP1             | SP0            |  |

| bit 7                 |                                                                                             |                                                                   |                                                        |                  |                  |                 | bit (          |  |

|                       |                                                                                             |                                                                   |                                                        |                  |                  |                 |                |  |

| Legend:               |                                                                                             |                                                                   |                                                        |                  |                  |                 |                |  |

| R = Readable          | bit                                                                                         | W = Writable                                                      | bit                                                    | U = Unimpler     | nented bit, read | d as '0'        |                |  |

| -n = Value at I       | POR                                                                                         | '1' = Bit is set                                                  | t                                                      | '0' = Bit is cle | ared             | x = Bit is unkr | Bit is unknown |  |

| bit 7<br>bit 6        | 1 = Stack bec<br>0 = Stack has<br>STKUNF: Sta                                               | ck Full Flag bit<br>ame full or ove<br>not become funck Underflow | erflowed<br>ull or overflow<br>Flag bit <sup>(1)</sup> | ed               |                  |                 |                |  |

|                       | <ol> <li>1 = Stack underflow occurred</li> <li>0 = Stack underflow did not occur</li> </ol> |                                                                   |                                                        |                  |                  |                 |                |  |

| bit 5                 | Unimplemen                                                                                  | ted: Read as '                                                    | ʻ0'                                                    |                  |                  |                 |                |  |

| bit 4-0               | <b>SP&lt;4:0&gt;:</b> Sta                                                                   | ck Pointer Loc                                                    | ation bits                                             |                  |                  |                 |                |  |

|                       |                                                                                             |                                                                   |                                                        |                  |                  |                 |                |  |

#### 5.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.4 FAST REGISTER STACK

A fast register stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, | FAST | ;STATUS, WREG, BSR      |

|------------|------|-------------------------|

|            |      | ;SAVED IN FAST REGISTER |

|            |      | ; STACK                 |

| •          |      |                         |

| •          |      |                         |

|            |      |                         |

| SUB1 •     |      |                         |

| •          |      |                         |

| RETURN,    | FAST | ;RESTORE VALUES SAVED   |

|            |      | ;IN FAST REGISTER STACK |

#### 5.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of  ${\tt RETLW}\ {\tt nn}$  instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

PCL" instruction does not The "ADDWF Note: update the PCLATH and PCLATU registers. A read operation on PCL must be performed to update PCLATH and PCLATU.

| EXAMPLE 5-2: |                                                  | COMPU                           | ITED GC | TO USING AN OFFSET VALUE                                                                                                                            |

|--------------|--------------------------------------------------|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| MAIN:        | ORG<br>MOVLW<br>CALL                             | 0x0000<br>0x00<br>TABLE         |         |                                                                                                                                                     |

| <br>TABLE    | ORG<br>MOVF<br>RLNCF<br>ADDWF                    | 0x8000<br>PCL, F<br>W, W<br>PCL | ;       | A simple read of PCL will update PCLATH, PCLATU<br>Multiply by 2 to get correct offset in table<br>Add the modified offset to force jump into table |

|              | RETLW<br>RETLW<br>RETLW<br>RETLW<br>RETLW<br>END | `A'<br>`B'<br>`C'<br>`D'<br>`E' |         |                                                                                                                                                     |

###

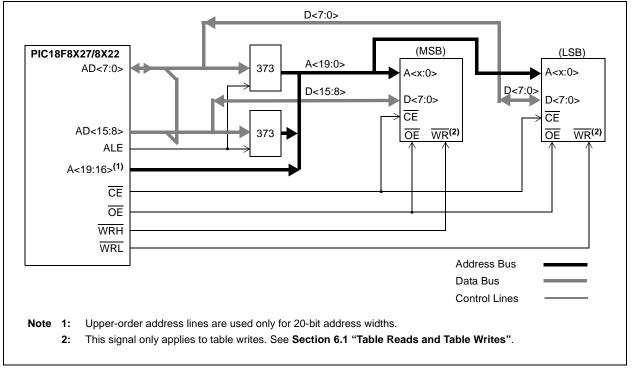

#### 7.5.1 16-BIT BYTE WRITE MODE

Figure 7-1 shows an example of 16-bit Byte Write mode for PIC18F8527/8622/8627/8722 devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

#### 7.7 Operation in Power-Managed Modes

In alternate power-managed Run modes, the external bus continues to operate normally. If a clock source with a lower speed is selected, bus operations will run at that speed. In these cases, excessive access times for the external memory may result if wait states have been enabled and added to external memory operations. If operations in a lower power Run mode are anticipated, users should provide in their applications for adjusting memory access times at the lower clock speeds. In Sleep and Idle modes, the microcontroller core does not need to access data; bus operations are suspended. The state of the external bus is frozen with the address/data pins and most of the control pins holding at the same state they were in when the mode was invoked. The only potential changes are the  $\overline{CE}$ ,  $\overline{LB}$ and  $\overline{UB}$  pins which are held at logic high.

| Name                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1                 | Bit 0  | Reset<br>Values<br>on page |

|-------------------------|-------|-------|-------|-------|-------|---------|-----------------------|--------|----------------------------|

| MEMCON <sup>(1)</sup>   | EBDIS | _     | WAIT1 | WAIT0 |       | —       | WM1                   | WM0    | 60                         |

| CONFIG3L <sup>(2)</sup> | WAIT  | BW    | ABW1  | ABW0  | _     | —       | PM1                   | PM0    | 302                        |

| CONFIG3H                | MCLRE |       |       | —     | _     | LPT1OSC | ECCPMX <sup>(2)</sup> | CCP2MX | 303                        |

#### TABLE 7-3: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-MANAGED MODES

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the External Memory Bus.

Note 1: This register is not implemented on 64-pin devices.

2: Unimplemented in PIC18F6527/6622/6627/6722 devices.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-1           | R/W-1           | R/W-1            | R/W-1            | R/W-1           | R/W-1  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|-----------------|--------|--|--|--|

| SSP2IP        | BCL2IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RC2IP           | TX2IP           | TMR4IP           | CCP5IP           | CCP4IP          | CCP3IP |  |  |  |

| bit 7         | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •               | ·               |                  |                  |                 | bit 0  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                 |                  |                  |                 |        |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | <b>F</b> .14    |                  |                  | -1 (0)          |        |  |  |  |

| R = Readabl   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable    |                 |                  | mented bit, read |                 |        |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is se | t               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |

| bit 7         | SSP2IP: MS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SP2 Interrupt F | Priority hit    |                  |                  |                 |        |  |  |  |

| Sit 1         | 1 = High price                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •               | nonty bit       |                  |                  |                 |        |  |  |  |

|               | 0 = Low prio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |                  |                  |                 |        |  |  |  |

| bit 6         | BCL2IP: MS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SP2 Bus Collis  | ion Interrupt F | Priority bit     |                  |                 |        |  |  |  |

|               | 1 = High priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                 |                  |                  |                 |        |  |  |  |

|               | 0 = Low prio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •               |                 |                  |                  |                 |        |  |  |  |

| bit 5         | RC2IP: EUSART2 Receive Interrupt Priority bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                 |                  |                  |                 |        |  |  |  |

|               | 1 = High priority<br>0 = Low priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                 |                  |                  |                 |        |  |  |  |

| bit 4         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •               | Interrunt Prio  | rity bit         |                  |                 |        |  |  |  |

|               | <b>TX2IP:</b> EUSART2 Transmit Interrupt Priority bit<br>1 = High priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                 |                  |                  |                 |        |  |  |  |

|               | 0 = Low priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                 |                  |                  |                 |        |  |  |  |

| bit 3         | TMR4IP: TM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R4 to PR4 Mat   | ch Interrupt P  | riority bit      |                  |                 |        |  |  |  |