Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8527t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                  | Pin Number            | Pin                    | Buffer           | Description                                                                                                                         |  |  |  |

|-----------------------------------------------------------|-----------------------|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                  | TQFP                  | Туре                   | Туре             | Description                                                                                                                         |  |  |  |

|                                                           |                       |                        |                  | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                       |  |  |  |

| RB0/INT0/FLT0<br>RB0<br>INT0<br>FLT0                      | 58                    | I/O<br>I<br>I          | TTL<br>ST<br>ST  | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for ECCPx.                                                                 |  |  |  |

| RB1/INT1<br>RB1<br>INT1                                   | 57                    | I/O<br>I               | TTL<br>ST        | Digital I/O.<br>External interrupt 1.                                                                                               |  |  |  |

| RB2/INT2<br>RB2<br>INT2                                   | 56                    | I/O<br>I               | TTL<br>ST        | Digital I/O.<br>External interrupt 2.                                                                                               |  |  |  |

| RB3/INT3/ECCP2/P2A<br>RB3<br>INT3<br>ECCP2 <sup>(1)</sup> | 55                    | I/O<br>I<br>O          | TTL<br>ST<br>—   | Digital I/O.<br>External interrupt 3.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.                                |  |  |  |

| P2A <sup>(1)</sup>                                        |                       | 0                      | _                | ECCP2 PWM output A.                                                                                                                 |  |  |  |

| RB4/KBI0<br>RB4<br>KBI0                                   | 54                    | I/O<br>I               | TTL<br>TTL       | Digital I/O.<br>Interrupt-on-change pin.                                                                                            |  |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                        | 53                    | I/O<br>I<br>I/O        | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                                               |  |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                        | 52                    | I/O<br>I<br>I/O        | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pir                                     |  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                        | 47<br>ompatible input | I/O<br>I<br>I/O<br>CMC | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.<br>= CMOS compatible input or output |  |  |  |

#### TABLE 1-4. PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

= Schmitt Trigger input with CMOS levels Analog= Analog input ST

| • | - 00111111 | ingger input man enree level | o / malog = / malog mput              |

|---|------------|------------------------------|---------------------------------------|

|   | = Input    | 0                            | = Output                              |

|   | = Power    | I <sup>2</sup> C™/SMB        | = I <sup>2</sup> C/SMBus input buffer |

$$P = Power \qquad I^2 C^{TM}/SMB$$

Note 1: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

- 2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

- 3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

- 4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

- 5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

Т

| Pin Name                                                         | Pin Number | Pin                      | Buffer                                         | Description                                                                                                                                                                                             |  |  |

|------------------------------------------------------------------|------------|--------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                         | TQFP       | Туре                     | Туре                                           | Description                                                                                                                                                                                             |  |  |

|                                                                  |            |                          |                                                | PORTD is a bidirectional I/O port.                                                                                                                                                                      |  |  |

| RD0/AD0/PSP0<br>RD0<br>AD0<br>PSP0                               | 72         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL                               | Digital I/O.<br>External memory address/data 0.<br>Parallel Slave Port data.                                                                                                                            |  |  |

| RD1/AD1/PSP1<br>RD1<br>AD1<br>PSP1                               | 69         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL                               | Digital I/O.<br>External memory address/data 1.<br>Parallel Slave Port data.                                                                                                                            |  |  |

| RD2/AD2/PSP2<br>RD2<br>AD2<br>PSP2                               | 68         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL                               | Digital I/O.<br>External memory address/data 2.<br>Parallel Slave Port data.                                                                                                                            |  |  |

| RD3/AD3/PSP3<br>RD3<br>AD3<br>PSP3                               | 67         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL                               | Digital I/O.<br>External memory address/data 3.<br>Parallel Slave Port data.                                                                                                                            |  |  |

| RD4/AD4/PSP4/SDO2<br>RD4<br>AD4<br>PSP4<br>SDO2                  | 66         | I/O<br>I/O<br>I/O<br>O   | ST<br>TTL<br>TTL<br>—                          | Digital I/O.<br>External memory address/data 4.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                           |  |  |

| RD5/AD5/PSP5/<br>SDI2/SDA2<br>RD5<br>AD5<br>PSP5<br>SDI2<br>SDA2 | 65         | I/O<br>I/O<br>I/O<br>I   | ST<br>TTL<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>External memory address/data 5.<br>Parallel Slave Port data.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |  |  |

| RD6/AD6/PSP6/<br>SCK2/SCL2<br>RD6<br>AD6<br>PSP6<br>SCK2<br>SCL2 | 64         | I/O<br>I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>External memory address/data 6.<br>Parallel Slave Port data.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |

| RD7/AD7/PSP7/SS2<br>RD7<br>AD7<br><u>PSP</u> 7<br>SS2            | 63         | I/O<br>I/O<br>I/O<br>I   | ST<br>TTL<br>TTL<br>TTL                        | Digital I/O.<br>External memory address/data 7.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                 |  |  |

|                                                                  |            | 0                        |                                                | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>I<sup>2</sup>C/SMBus input buffer</li> </ul>                                                                    |  |  |

#### TABLE 1-4: PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

- 2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

- 3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                | LP, XT, HS                    |                                       |                                    |

| Primary Device Clock           | HSPLL                         | Tcsd <sup>(1)</sup>                   | OSTS                               |

| (PRI_IDLE mode)                | EC, RC                        | 10.30 ( )                             |                                    |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| T1OSC or INTRC                 | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

| INTOSC <sup>(2)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

| (Sleep mode)                   | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

Note 1: TCSD (parameter 38, Table 28-12) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies. On Reset, INTOSC defaults to 1 MHz.

**3:** TOST is the Oscillator Start-up Timer (parameter 32, Table 28-12). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12, Table 28-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 28-12), the INTOSC stabilization period.

## 5.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has 8 two-word instructions: CALL, MOVFF, GOTO, LSFR, ADDULNK, CALLW, MOVSS and SUBULNK. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 5-4 shows how this works.

Note: See Section 5.6 "PIC18 Instruction Execution and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

| CASE 1:             |                                           |

|---------------------|-------------------------------------------|

| Object Code         | Source Code                               |

| 0110 0110 0000 0000 | TSTFSZ REG1 ; is RAM location 0?          |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 ; No, skip this word     |

| 1111 0100 0101 0110 | ; Execute this word as a NOP              |

| 0010 0100 0000 0000 | ADDWF REG3 ; continue code                |

| CASE 2:             |                                           |

| Object Code         | Source Code                               |

| 0110 0110 0000 0000 | TSTFSZ REG1 ; is RAM location 0?          |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 ; Yes, execute this word |

| 1111 0100 0101 0110 | ; 2nd word of instruction                 |

| 0010 0100 0000 0000 | ADDWF REG3 ; continue code                |

EXAMPLE 5-4: TWO-WORD INSTRUCTIONS

## 6.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

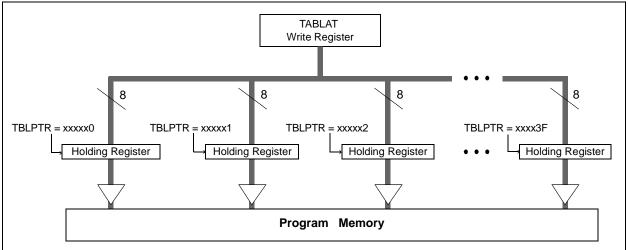

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 holding registers before executing a write operation.

## FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

## 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the row erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

An example of the required code is shown in Example 6-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

## 8.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADRH:EEADR register pair, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available on the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 8-1.

## 8.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADRH:EEADR register pair and the data written to the EEDATA register. The sequence in Example 8-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, EECON1, EEADRH:EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

## 8.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

EXAMPLE 8-1: DATA EEPROM READ

| MOVLW<br>MOVWF | DATA_EE_ADDRH<br>EEADRH | ;<br>; Upper bits of Data Memory Address to read |

|----------------|-------------------------|--------------------------------------------------|

| MOVLW          | DATA_EE_ADDR            | ;                                                |

| MOVWF          | EEADR                   | ; Lower bits of Data Memory Address to read      |

| BCF            | EECON1, EEPGD           | ; Point to DATA memory                           |

| BCF            | EECON1, CFGS            | ; Access EEPROM                                  |

| BSF            | EECON1, RD              | ; EEPROM Read                                    |

| MOVF           | EEDATA, W               | ; W = EEDATA                                     |

|                |                         |                                                  |

| EXAMPLE 8-2: | DATA EEPROM WRITE |

|--------------|-------------------|

|              |                   |

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | ;                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EPGD  | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | i                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | 0AAh          | ;                                             |

|          | MOVWF | EECON2        | ; Write OAAh                                  |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

|          |       |               |                                               |

## TABLE 11-13: PORTG FUNCTIONS

| Pin Name      | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                               |  |  |

|---------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RG0/ECCP3/P3A | RG0      | 0               | 0   | DIG         | LATG<0> data output.                                                                                                                      |  |  |

|               |          | 1               | I   | ST          | PORTG<0> data input.                                                                                                                      |  |  |

|               | ECCP3    | 0               | 0   | DIG         | ECCP3 compare and ECCP3 PWM output. Takes priority over port data.                                                                        |  |  |

|               |          | 1               | Ι   | ST          | ECCP3 capture input.                                                                                                                      |  |  |

|               | P3A      | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, channel B. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |  |  |

| RG1/TX2/CK2   | RG1      | 0               | 0   | DIG         | LATG<1> data output.                                                                                                                      |  |  |

|               |          | 1               | Ι   | ST          | PORTG<1> data input.                                                                                                                      |  |  |

|               | TX2      | 0               | 0   | DIG         | Asynchronous serial transmit data output (EUSART2 module). Takes priority over port data.                                                 |  |  |

|               | CK2      | 0               | 0   | DIG         | Synchronous serial clock output (EUSART2 module). Takes priority over port data.                                                          |  |  |

|               |          | 1               | Ι   | ST          | Synchronous serial clock input (EUSART2 module).                                                                                          |  |  |

| RG2/RX2/DT2   | RG2      | 0               | 0   | DIG         | LATG<2> data output.                                                                                                                      |  |  |

|               |          | 1               | Ι   | ST          | PORTG<2> data input.                                                                                                                      |  |  |

|               | RX2      | 1               | I   | ST          | Asynchronous serial receive data input (EUSART2 module).                                                                                  |  |  |

|               | DT2      | 1               | 0   | DIG         | Synchronous serial data output (EUSART2 module). Takes priority over port data. User must configure as an input.                          |  |  |

|               |          | 1               | Ι   | ST          | Synchronous serial data input (EUSART2 module). User must configure as an input.                                                          |  |  |

| RG3/CCP4/P3D  | RG3      | 0               | 0   | DIG         | LATG<3> data output.                                                                                                                      |  |  |

|               |          | 1               | Ι   | ST          | PORTG<3> data input.                                                                                                                      |  |  |

|               | CCP4     | 0               | 0   | DIG         | CCP4 compare and PWM output; takes priority over port data and P3D function.                                                              |  |  |

|               |          | 1               | Ι   | ST          | CCP4 capture input.                                                                                                                       |  |  |

|               | P3D      | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, channel D. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |  |  |

| RG4/CCP5/P1D  | RG4      | 0               | 0   | DIG         | LATG<4> data output.                                                                                                                      |  |  |

|               |          | 1               | Ι   | ST          | PORTG<4> data input.                                                                                                                      |  |  |

|               | CCP5     | 0               | 0   | DIG         | CCP5 compare and PWM output. Takes priority over port data and P1D function.                                                              |  |  |

|               |          | 1               | Ι   | ST          | CCP5 capture input.                                                                                                                       |  |  |

|               | P1D      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel B. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |  |  |

| RG5/MCLR/Vpp  | RG5      | (1)             | I   | ST          | PORTG<5> data input; enabled when MCLRE Configuration bit is clear.                                                                       |  |  |

|               | MCLR     | _               | I   | ST          | External Master Clear input; enabled when MCLRE Configuration bit is set.                                                                 |  |  |

|               | Vpp      | _               | Ι   | ANA         | High-voltage detection; used for ICSP <sup>™</sup> mode entry detection.<br>Always available regardless of pin mode.                      |  |  |

Legend: PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** RG5 does not have a corresponding TRISG bit.

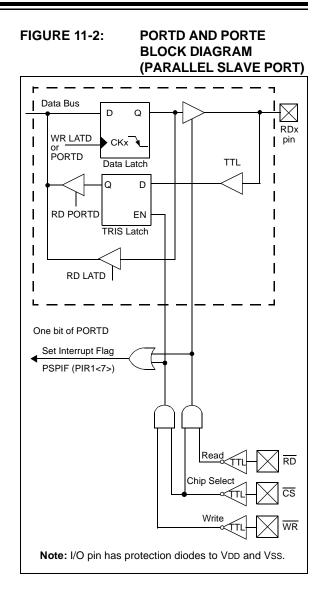

## 11.10 Parallel Slave Port

PORTD can also function as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (PSPCON<4>) is set. It is asynchronously readable and writable by the external world through the RD and  $\overline{WR}$  control input pins.

| Note: | For PIC18F8527/8622/8627/8722 devices,       |

|-------|----------------------------------------------|

|       | the Parallel Slave Port is available only in |

|       | Microcontroller mode.                        |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 11-3 and Figure 11-4, respectively.

## 18.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation using Timer2:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required do the following:

- Disable auto-shutdown (ECCP1AS = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the dead-band delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCP1AS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSS1AC<1:0> and PSS1BD<1:0> bits.

- Set the ECCP1ASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the P1RSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCP1ASE bit (ECCP1AS<7>).

## 18.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 or Timer4 will not increment and the state of the module will not change. If the ECCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP1 module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2 or Timer4. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 18.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP1 will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

## 18.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

## REGISTER 19-2: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| R/W-0      | R/W-0                                  | R/W-0                                                                                                                      | R/W-0          | R/W-0                         | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

|------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|----------------------|----------------------|----------------------|--|--|--|--|

| WCOL       | SSPOV <sup>(1)</sup>                   | SSPEN <sup>(2)</sup>                                                                                                       | CKP            | SSPM3 <sup>(3)</sup>          | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |  |  |  |  |

| bit 7      |                                        |                                                                                                                            |                |                               |                      |                      | bit (                |  |  |  |  |

|            |                                        |                                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

| Legend:    |                                        |                                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

| R = Reada  | able bit                               | W = Writable                                                                                                               | oit            | -                             | nented bit, rea      | d as '0'             |                      |  |  |  |  |

| -n = Value | at POR                                 | '1' = Bit is set                                                                                                           |                | '0' = Bit is cle              | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

| bit 7      | WCOL: Write                            | e Collision Dete                                                                                                           | ct bit         |                               |                      |                      |                      |  |  |  |  |

|            | (must be                               | cleared in softv                                                                                                           |                | le it is still transı         | mitting the prev     | vious word           |                      |  |  |  |  |

|            | 0 = No collis                          |                                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

| bit 6      | SSPOV: Rec                             | SSPOV: Receive Overflow Indicator bit <sup>(1)</sup>                                                                       |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        | SPI Slave mode:                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        |                                                                                                                            |                | PxBUF register                |                      |                      |                      |  |  |  |  |

|            |                                        |                                                                                                                            |                | Overflow can or               |                      |                      |                      |  |  |  |  |

|            | the SSP)<br>ware).                     | XBUF, even if o                                                                                                            | nly transmitti | ing data, to avo              | ad setting over      | flow (must be c      | cleared in soft      |  |  |  |  |

|            | 0 = No overfl                          | low                                                                                                                        |                |                               |                      |                      |                      |  |  |  |  |

| bit 5      |                                        | SSPEN: Synchronous Serial Port Enable bit <sup>(2)</sup>                                                                   |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        | 1 = Enables serial port and configures SCKx, SDOx, SDIx and SSx as serial port pins                                        |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        | •                                                                                                                          | •              | iese pins as I/O              |                      |                      |                      |  |  |  |  |

| bit 4      |                                        | <b>CKP:</b> Clock Polarity Select bit                                                                                      |                |                               |                      |                      |                      |  |  |  |  |

|            | 1 = Idle state                         | 1 = Idle state for clock is a high level                                                                                   |                |                               |                      |                      |                      |  |  |  |  |

|            | 0 = Idle state                         | for clock is a lo                                                                                                          | w level        |                               |                      |                      |                      |  |  |  |  |

| bit 3-0    | SSPM<3:0>:                             | Synchronous S                                                                                                              | Serial Port M  | ode Select bits <sup>(3</sup> | 3)                   |                      |                      |  |  |  |  |

|            |                                        | $0101 = $ SPI Slave mode, clock = SCKx pin, $\overline{SSx}$ pin control disabled, $\overline{SSx}$ can be used as I/O pin |                |                               |                      |                      |                      |  |  |  |  |

|            | 0100 = SPI S                           | Slave mode, clo                                                                                                            | ck = SCKx p    | in, SSx pin cont              | trol enabled         |                      |                      |  |  |  |  |

|            |                                        | Master mode, cl                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        | Master mode, cl                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

|            |                                        | Master mode, cl                                                                                                            |                |                               |                      |                      |                      |  |  |  |  |

|            | 0000 = SPI N                           | Master mode, cl                                                                                                            | ock = Fosc/4   | 4                             |                      |                      |                      |  |  |  |  |

| Note 1:    | In Master mode, the writing to the SSP |                                                                                                                            | s not set sind | ce each new rec               | ception (and tra     | ansmission) is ir    | nitiated by          |  |  |  |  |

| 2:         | When enabled, the                      | •                                                                                                                          | e properly co  | onfigured as inn              | ut or output         |                      |                      |  |  |  |  |

|            |                                        |                                                                                                                            | C property of  |                               |                      |                      |                      |  |  |  |  |

**3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

### 19.4.14 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 19.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

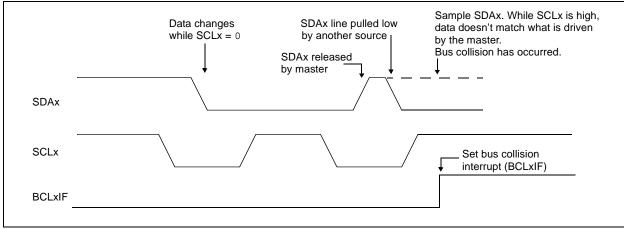

#### 19.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 19.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the  $I^2C$  port to its Idle state (Figure 19-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 19-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

## 20.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCONx<3>) selects 16-bit mode.

The SPBRGHx:SPBRGx register pair controls the period of a free running timer. In Asynchronous mode, bits BRGH (TXSTAx<2>) and BRG16 (BAUDCONx<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 20-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGHx:SPBRGx registers can be calculated using the formulas in Table 20-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 20-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 20-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGHx:SPBRGx registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

## 20.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRGx register pair.

## 20.1.2 SAMPLING

The data on the RXx pin (either RC7/RX1/DT1 or RG2/ RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RXx pin.

| Configuration Bits |       |      | BRG/EUSART Mode     | Baud Rate Formula     |  |

|--------------------|-------|------|---------------------|-----------------------|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Bauu Kate Formula     |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n + 1)]     |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  | $E_{0000}/[16.(n+1)]$ |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n + 1)]     |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                       |  |

| 1                  | 0     | x    | 8-bit/Synchronous   | Fosc/[4 (n + 1)]      |  |

| 1                  | 1     | x    | 16-bit/Synchronous  |                       |  |

#### TABLE 20-1: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGHx:SPBRGx register pair

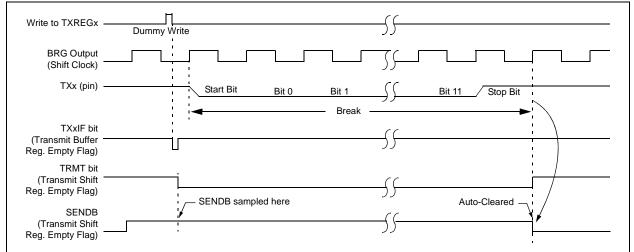

## 20.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The frame Break character is sent whenever the SENDB and TXEN bits (TXSTAx<3> and TXSTAx<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREGx will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREGx for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-10 for the timing of the Break character sequence.

20.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREGx with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREGx to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREGx becomes empty, as indicated by the TXxIF, the next data byte can be written to TXREGx.

### 20.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 20.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RXx/DTx, cause an RCxIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXxIF interrupt is observed.

## FIGURE 20-10: SEND BREAK CHARACTER SEQUENCE

### 20.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

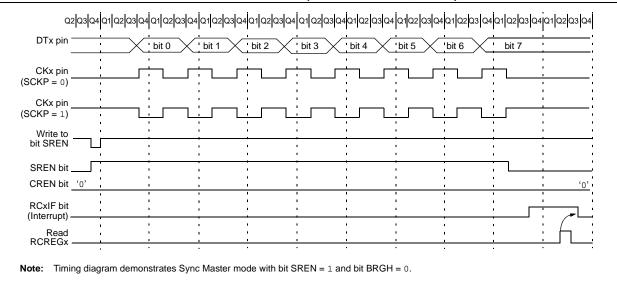

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| IADLE 20              |         | TC INFAAAA INSTRUCTION SI       |        |                         | ,    |      |      |                 |       |

|-----------------------|---------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Mnemonic,<br>Operands |         | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | Notes |

|                       |         | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL C             | OPERA   | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW                 | k       | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k       | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k       | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f, k    | Move Literal (12-bit) 2nd word  | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |         | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB                 | k       | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW                 | k       | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k       | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k       | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k       | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k       | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN              | /IORY ← | PROGRAM MEMORY OPERATION        | ONS    |                         |      |      |      |                 |       |

| TBLRD*                |         | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |         | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |         | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |         | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |         | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            | 5     |

| TBLWT*+               |         | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            | 5     |

| TBLWT*-               |         | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            | 5     |

| TBLWT+*               |         | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            | 5     |

## TABLE 26-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| BNC                                                             | Branch if N                               | Not Carry                                          |                                       | BNN                                         | Branch if                                                          | Not Negative                                       | e                          |  |

|-----------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|---------------------------------------|---------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|----------------------------|--|

| Syntax:                                                         | BNC n                                     |                                                    |                                       | Syntax:                                     | BNN n                                                              |                                                    |                            |  |

| Operands:                                                       | -128 ≤ n ≤ 1                              | 127                                                |                                       | Operands:                                   | -128 ≤ n ≤                                                         | 127                                                |                            |  |

| Operation:                                                      | if Carry bit<br>(PC) + 2 +                |                                                    |                                       | Operation:                                  | if Negative<br>(PC) + 2 +                                          |                                                    |                            |  |

| Status Affected                                                 | : None                                    |                                                    |                                       | Status Affected:                            | None                                                               |                                                    |                            |  |

| Encoding:                                                       | 1110                                      | 0011 nn:                                           | nn nnnn                               | Encoding:                                   | 1110                                                               | 0111 n                                             | nnn nnnn                   |  |

| Description:                                                    | If the Carry<br>will branch.              | bit is '0', then                                   | the program                           | Description:                                | If the Nega<br>program w                                           | ative bit is '0',<br>ill branch.                   | then the                   |  |

|                                                                 | added to th<br>incremente<br>instruction, | d to fetch the<br>the new addre<br>n. This instruc | e PC will have<br>next<br>ess will be |                                             | added to th<br>incremente<br>instruction,                          | ed to fetch the<br>, the new add<br>n. This instru | the PC will have<br>e next |  |

| Words:                                                          | 1                                         |                                                    |                                       | Words:                                      | 1                                                                  |                                                    |                            |  |

| Cycles:                                                         | 1(2)                                      |                                                    |                                       | Cycles:                                     | 1(2)                                                               |                                                    |                            |  |

| Q Cycle Activit<br>If Jump:                                     | ty:                                       |                                                    |                                       | Q Cycle Activit                             | y:                                                                 |                                                    |                            |  |

| Q1                                                              | Q2                                        | Q3                                                 | Q4                                    | Q1                                          | Q2                                                                 | Q3                                                 | Q4                         |  |

| Decode                                                          | e Read literal<br>'n'                     | Process<br>Data                                    | Write to<br>PC                        | Decode                                      | Read literal<br>'n'                                                | Process<br>Data                                    | Write to<br>PC             |  |

| No                                                              | No                                        | No                                                 | No                                    | No                                          | No                                                                 | No                                                 | No                         |  |

| operatio                                                        | n operation                               | operation                                          | operation                             | operation                                   | n operation                                                        | operation                                          | operation                  |  |

| If No Jump:                                                     |                                           |                                                    |                                       | If No Jump:                                 |                                                                    |                                                    |                            |  |

| Q1                                                              | Q2                                        | Q3                                                 | Q4                                    | Q1                                          | Q2                                                                 | Q3                                                 | Q4                         |  |

| Decode                                                          | e Read literal<br>'n'                     | Process<br>Data                                    | No<br>operation                       | Decode                                      | Read literal<br>'n'                                                | Process<br>Data                                    | No<br>operation            |  |

| Example:                                                        | HERE                                      | BNC Jump                                           |                                       | Example:                                    | HERE                                                               | BNN Jum                                            | qı                         |  |

| Before Ins<br>PC<br>After Instru<br>If Ca                       | = ad<br>uction<br>rry = 0;                | dress (HERE                                        |                                       | Before Inst<br>PC<br>After Instru<br>If Neg | = ac<br>action<br>gative = 0;                                      |                                                    |                            |  |

| PC = address (Jump)<br>If Carry = 1;<br>PC = address (HERE + 2) |                                           |                                                    |                                       | If Neg                                      | PC = address (Jump)<br>If Negative = 1;<br>PC = address (HERE + 2) |                                                    |                            |  |

| GOT                                                              | 0                                      | Unconditi                          | Unconditional Branch                                                                                                                                                               |                 |    |                                   |  |  |

|------------------------------------------------------------------|----------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|-----------------------------------|--|--|

| Synta                                                            | ax:                                    | GOTO k                             | GOTO k                                                                                                                                                                             |                 |    |                                   |  |  |

| Oper                                                             | ands:                                  | $0 \le k \le 10^4$                 | 48575                                                                                                                                                                              |                 |    |                                   |  |  |

| Oper                                                             | ation:                                 | $k \rightarrow PC<2$               | 0:1>                                                                                                                                                                               |                 |    |                                   |  |  |

| Statu                                                            | s Affected:                            | None                               |                                                                                                                                                                                    |                 |    |                                   |  |  |

|                                                                  | ding:<br>ord (k<7:0>)<br>vord(k<19:8>) | 1110<br>1111                       | 1111<br>k19kkk                                                                                                                                                                     | k7kł<br>kkk     |    | kkkk0<br>kkkk8                    |  |  |

| Desc                                                             | ription:                               | anywhere<br>range. The<br>PC<20:1> | GOTO allows an unconditional branch<br>anywhere within entire 2-Mbyte memory<br>range. The 20-bit value 'k' is loaded into<br>PC<20:1>. GOTO is always a two-cycle<br>instruction. |                 |    |                                   |  |  |

| Word                                                             | s:                                     | 2                                  | 2                                                                                                                                                                                  |                 |    |                                   |  |  |

| Cycle                                                            | es:                                    | 2                                  | 2                                                                                                                                                                                  |                 |    |                                   |  |  |

| QC                                                               | ycle Activity:                         |                                    |                                                                                                                                                                                    |                 |    |                                   |  |  |

| -                                                                | Q1                                     | Q2                                 | Q3                                                                                                                                                                                 | Q3              |    | Q4                                |  |  |