Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8622-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 64/80-Pin, 1-Mbit, Enhanced Flash Microcontrollers with 10-Bit A/D and nanoWatt Technology

#### **Power Management Features:**

- Run: CPU On, Peripherals On

- Idle: CPU Off, Peripherals On

- Sleep: CPU Off, Peripherals Off

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 25  $\mu\text{A}$  Typical

- Idle mode Currents Down to 6.8 µA Typical

- Sleep mode Current Down to 120 nA Typical

- Timer1 Oscillator: 900 nA, 32 kHz, 2V

- Watchdog Timer: 1.6 μA, 2V Typical

- Two-Speed Oscillator Start-up

### Flexible Oscillator Structure:

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) Available for Crystal and Internal Oscillators

- Internal Oscillator Block:

- Fast wake from Sleep and Idle, 1  $\mu s$  typical

- Provides a complete range of clock speeds

- from 31 kHz to 32 MHz when used with PLL

- User-tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three Programmable External Interrupts

- Four Input Change Interrupts

- Enhanced Capture/Compare/PWM (ECCP) module (40/44-pin devices only):

- One, two or four PWM outputs

- Programmable dead time

- Auto-shutdown and auto-restart

# **Peripheral Highlights (Continued):**

- Up to 2 Capture/Compare/PWM (CCP) modules, one with Auto-Shutdown (28-pin devices)

- Master Synchronous Serial Port (MSSP) module Supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- RS-232 operation using internal oscillator block (no external crystal required)

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

- Programmable 16-Level High/Low-Voltage Detection (HLVD) module

# **Special Microcontroller Features:**

- C Compiler Optimized Architecture

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

- Flash/Data EEPROM Retention: 100 Years Typical

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

- Programmable Brown-out Reset (BOR) with Software Enable Option

|            | Prog             | ram Memory                    | Data            | Memory            |     | 10-Bit   | CCP/          |   | MSSI | c                           | E     | tors        | it s               | Bus      |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|----------|---------------|---|------|-----------------------------|-------|-------------|--------------------|----------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | /O A/D E | ECCP<br>(PWM) |   | SPI  | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External |

| PIC18F6527 | 48K              | 24576                         | 3936            | 1024              | 54  | 12       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6622 | 64K              | 32768                         | 3936            | 1024              | 54  | 12       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6627 | 96K              | 49152                         | 3936            | 1024              | 54  | 12       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6722 | 128K             | 65536                         | 3936            | 1024              | 54  | 12       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F8527 | 48K              | 24576                         | 3936            | 1024              | 70  | 16       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8622 | 64K              | 32768                         | 3936            | 1024              | 70  | 16       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8627 | 96K              | 49152                         | 3936            | 1024              | 70  | 16       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8722 | 128K             | 65536                         | 3936            | 1024              | 70  | 16       | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| Pin Name      | Pin Number         | Pin      | Buffer    | Description                                                                                    |

|---------------|--------------------|----------|-----------|------------------------------------------------------------------------------------------------|

|               | TQFP               | Туре     | Туре      | Description                                                                                    |

| RG5/MCLR/Vpp  | 7                  |          |           | Master Clear (input) or programming voltage (input).                                           |

| RG5           |                    | I        | ST        | Digital input.                                                                                 |

| MCLR          |                    | I        | ST        | Master Clear (Reset) input. This pin is an active-low                                          |

| Vpp           |                    | Р        |           | Reset to the device.<br>Programming voltage input.                                             |

| OSC1/CLKI/RA7 | 39                 |          |           | Oscillator crystal or external clock input.                                                    |

| OSC1          |                    | I        | ST        | Oscillator crystal input or external clock source input.                                       |

|               |                    |          |           | ST buffer when configured in RC mode, CMOS                                                     |

| CLKI          |                    |          | смоз      | otherwise.                                                                                     |

|               |                    | 1        | CIVIOS    | External clock source input. Always associated with pin function OSC1. (See related OSC1/CLKI, |

| RA7           |                    | I/O      | TTL       | OSC2/CLKO pins.)<br>General purpose I/O pin.                                                   |

| OSC2/CLKO/RA6 | 40                 | 1/0      |           | Oscillator crystal or clock output.                                                            |

| OSC2          | 40                 | 0        | _         | Oscillator crystal output. Connects to crystal or                                              |

| 0002          |                    | Ũ        |           | resonator in Crystal Oscillator mode.                                                          |

| CLKO          |                    | 0        | _         | In RC mode, OSC2 pin outputs CLKO, which has                                                   |

|               |                    |          |           | 1/4 the frequency of OSC1 and denotes the                                                      |

|               |                    |          |           | instruction cycle rate.                                                                        |

| RA6           |                    | I/O      | TTL       | General purpose I/O pin.                                                                       |

|               | compatible input   |          |           | <ul> <li>CMOS compatible input or output</li> </ul>                                            |

| ST = Schm     | nitt Trigger input | with CM0 | OS levels | Analog= Analog input                                                                           |

| I = Input     |                    | 0        |           | = Output                                                                                       |

#### TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS

= Input O = O

= Power

$$l^2 C^{TM}$$

=  $l^2 l$

= I<sup>2</sup>C/SMBus input buffer

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

**2:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

Ρ

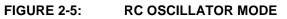

# 2.4 RC Oscillator

For timing insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of REXT and CEXT

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-5 shows how the R/C combination is connected.

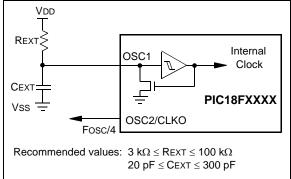

The RCIO Oscillator mode (Figure 2-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

# 2.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

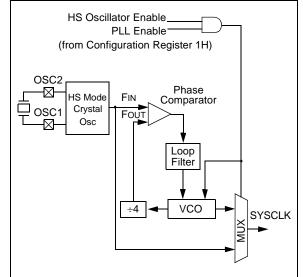

### 2.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available when this mode is configured as the primary clock source.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

# 2.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 2.6.4 "PLL in INTOSC Modes"**.

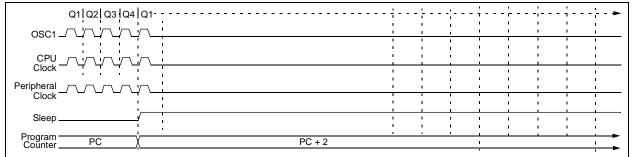

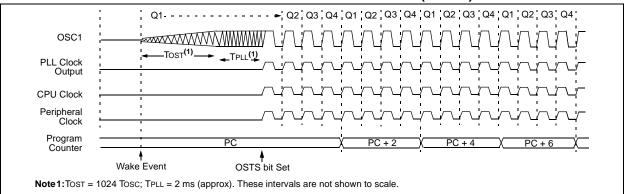

# 3.3 Sleep Mode

The power-managed Sleep mode in the PIC18F8722 family of devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 25.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

# 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 28-12) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

FIGURE 3-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

#### FIGURE 5-2: MEMORY MAPS FOR PIC18F8722 FAMILY PROGRAM MEMORY MODES

| _                       | Microprocessor<br>Mode               |                                                                                                                                                                                                                                                                  |                  |                                                                                                                                  | Microprocessor<br>with Boot Block<br>Mode |                                                                                                                                                                                                                                            |         | Microcontroller<br>Mode <sup>(5)</sup> |  |                              | ller             |

|-------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------|--|------------------------------|------------------|

| Program Space Execution | 000000h                              | On-Chip     Program       Memory     0007FFh(6) or       000FFFh(6) or     0007FFh(6) or       0001FFFh(6) or     001FFFh(6) or       000800h(6) or     001000h(6) or       001000h(6) or     002000h(6) or       Program     External       Memory     External |                  | 07FFh <sup>(6)</sup> or<br>0FFFh <sup>(6)</sup> or<br>1FFFh <sup>(6)</sup><br>0800h <sup>(6)</sup> or<br>1000h <sup>(6)</sup> or |                                           | 000000h<br>On-Chip<br>Program<br>0FFFh <sup>(1)</sup><br>017FFFh <sup>(2)</sup><br>017FFFh <sup>(3)</sup><br>01FFFFh <sup>(4)</sup><br>0C000h <sup>(1)</sup><br>010000h <sup>(2)</sup><br>018000h <sup>(3)</sup><br>020000h <sup>(4)</sup> |         | Prog                                   |  | On-Chip<br>Program<br>Memory |                  |

|                         | 1FFFFFh                              | External<br>Memory                                                                                                                                                                                                                                               | On-Chip<br>Flash | 1FFFFfh                                                                                                                          | External<br>Memory                        | On-Chip<br>Flash                                                                                                                                                                                                                           | 1FFFFFh | On-Chip<br>Flash                       |  | External<br>Memory           | On-Chip<br>Flash |

| No                      | ote 1:<br>2:<br>3:<br>4:<br>5:<br>6: | PIC18F66<br>PIC18F66<br>PIC18F67<br>This is the                                                                                                                                                                                                                  |                  | 8F8622.<br>8F8627.                                                                                                               |                                           |                                                                                                                                                                                                                                            |         |                                        |  |                              |                  |

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

| EXAIVIPLE 0-3: |                 | TING TO FLASH PROU     |                                       |

|----------------|-----------------|------------------------|---------------------------------------|

|                | MOVLW           | D'64'                  | ; number of bytes in erase block      |

|                | MOVWF           | COUNTER                |                                       |

|                | MOVLW           | BUFFER_ADDR_HIGH       | ; point to buffer                     |

|                | MOVWF           | FSR0H                  |                                       |

|                | MOVLW           | BUFFER_ADDR_LOW        |                                       |

|                | MOVWF           | FSROL                  |                                       |

|                | MOVLW           | CODE_ADDR_UPPER        | ; Load TBLPTR with the base           |

|                | MOVWF           | TBLPTRU                | ; address of the memory block         |

|                | MOVLW           | CODE_ADDR_HIGH         |                                       |

|                | MOVWF           | TBLPTRH                |                                       |

|                | MOVLW           | CODE_ADDR_LOW          |                                       |

|                | MOVWF           | TBLPTRL                |                                       |

| READ_BLOCK     |                 |                        |                                       |

|                | TBLRD*+         |                        | ; read into TABLAT, and inc           |

|                | MOVF            | TABLAT, W              | ; get data                            |

|                | MOVWF           |                        | ; store data                          |

|                |                 | COUNTER                | ; done?                               |

| MODIEN WODD    | BRA             | READ_BLOCK             | ; repeat                              |

| MODIFY_WORD    |                 | אייא אטטא מעעא         | ; point to buffer                     |

|                | MOVLWD<br>MOVWF | ATA_ADDR_HIGH<br>FSR0H | ; point to buffer                     |

|                | MOVWF           | DATA_ADDR_LOW          |                                       |

|                | MOVLW           | FSROL                  |                                       |

|                | MOVWP           | NEW_DATA_LOW           | ; update buffer word                  |

|                | MOVEW           | POSTINC0               | , aparte ballel word                  |

|                | MOVLW           | NEW_DATA_HIGH          |                                       |

|                | MOVWF           | INDF0                  |                                       |

| ERASE_BLOCK    | 110 1 111       | INDI 0                 |                                       |

|                | MOVLW           | CODE ADDR UPPER        | ; load TBLPTR with the base           |

|                | MOVWF           | TBLPTRU                | ; address of the memory block         |

|                | MOVLW           | CODE_ADDR_HIGH         | •                                     |

|                | MOVWF           | TBLPTRH                |                                       |

|                | MOVLW           | CODE_ADDR_LOW          |                                       |

|                | MOVWF           | TBLPTRL                |                                       |

|                | BSF             | EECON1, EEPGD          | ; point to Flash program memory       |

|                | BCF             | EECON1, CFGS           | ; access Flash program memory         |

|                | BSF             | EECON1, WREN           | ; enable write to memory              |

|                | BSF             | EECON1, FREE           | ; enable Row Erase operation          |

|                | BCF             | INTCON, GIE            | ; disable interrupts                  |

|                | MOVLW           | 55h                    |                                       |

| Required       | MOVWF           | EECON2                 | ; write 55h                           |

| Sequence       | MOVLW           | 0AAh                   |                                       |

|                | MOVWF           | EECON2                 | ; write OAAh                          |

|                | BSF             | EECON1, WR             | ; start erase (CPU stall)             |

|                | BSF             | INTCON, GIE            | ; re-enable interrupts                |

|                | TBLRD*-         |                        | ; dummy read decrement                |

|                | MOVLW           | BUFFER_ADDR_HIGH       | ; point to buffer                     |

|                | MOVWF           | FSROH                  |                                       |

|                | MOVLW<br>MOVWF  | BUFFER_ADDR_LOW        |                                       |

| WRITE_BUFFER_F |                 | FSROL                  |                                       |

| WRITE_BOFFER_I | MOVLW           | D'64'                  | ; number of bytes in holding register |

|                | MOVEW           | COUNTER                | , number of bytes in nording register |

| WRITE_BYTE_TO_ |                 |                        |                                       |

|                | MOVFF           | POSTINC0, WREG         | ; get low byte of buffer data         |

|                | MOVIF           | TABLAT                 | ; present data to table latch         |

|                | TBLWT+*         |                        | ; write data, perform a short write   |

|                |                 |                        | ; to internal TBLWT holding register. |

|                | DECFSZ          | COUNTER                | ; loop until buffers are full         |

|                | BRA             | WRITE_WORD_TO_HREGS    | -                                     |

|                |                 |                        |                                       |

# 11.5 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

All pins on PORTE are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power    | -on Reset,    | these | pins | are |

|-------|---------------|---------------|-------|------|-----|

|       | configured as | digital input | s.    |      |     |

When the device is operating in Microcontroller mode, pin RE7 can be configured as the alternate peripheral pin for the ECCP2 module. This is done by clearing the CCP2MX Configuration bit.

In 80-pin devices, PORTE is multiplexed with the system bus as part of the external memory interface. I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled (80-pin devices only), PORTE is the high-order byte of the multiplexed address/data bus (AD<15:8>). The TRISE bits are also overridden.

When the Parallel Slave Port is active on PORTD, three of the PORTE pins (RE0/AD8/RD/P2D, RE1/AD9/WR/P2C and RE2/AD10/CS/P2B) are configured as digital control inputs for the port. The control functions are summarized in Table 11-9. The reconfiguration occurs automatically when the PSPMODE control bit (PSPCON<4>) is set. Users must still make certain the corresponding TRISE bits are set to configure these pins as digital inputs.

| EXAMP | 'LE 11-5 | : INITIALIZING PORTE    |

|-------|----------|-------------------------|

| CLRF  | PORTE    | ; Initialize PORTE by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATE     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 03h      | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISE    | ; Set RE<1:0> as inputs |

|       |          | ; RE<7:2> as outputs    |

|       |          |                         |

#### EXAMPLE 11-5: INITIALIZING PORTE

| Pin Name  | Function           | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                                                               |

|-----------|--------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RH0/A16   | RH0                | 0               | 0   | DIG         | LATH<0> data output.                                                                                                                      |

|           |                    | 1               | I   | ST          | PORTH<0> data input.                                                                                                                      |

|           | A16                | x               | 0   | DIG         | External memory interface, address line 16. Takes priority over port data.                                                                |

| RH1/A17   | RH1                | 0               | 0   | DIG         | LATH<1> data output.                                                                                                                      |

|           |                    | 1               | I   | ST          | PORTH<1> data input.                                                                                                                      |

|           | A17                | x               | 0   | DIG         | External memory interface, address line 17. Takes priority over port data.                                                                |

| RH2/A18   | RH2                | 0               | 0   | DIG         | LATH<2> data output.                                                                                                                      |

|           |                    | 1               | I   | ST          | PORTH<2> data input.                                                                                                                      |

|           | A18                | x               | 0   | DIG         | External memory interface, address line 18. Takes priority over port data.                                                                |

| RH3/A19   | RH3                | 0               | 0   | DIG         | LATH<3> data output.                                                                                                                      |

|           |                    | 1               | I   | ST          | PORTH<3> data input.                                                                                                                      |

|           | A19                | x               | 0   | DIG         | External memory interface, address line 19. Takes priority over port data.                                                                |

| RH4/AN12/ | RH4                | 0               | 0   | DIG         | LATH<4> data output.                                                                                                                      |

| P3C       |                    | 1               | Ι   | ST          | PORTH<4> data input.                                                                                                                      |

|           | AN12               | 1               | Ι   | ANA         | A/D input channel 12. Default configuration on POR.                                                                                       |

|           | P3C <sup>(1)</sup> | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, channel C. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RH5/AN13/ | RH5                | 0               | 0   | DIG         | LATH<5> data output.                                                                                                                      |

| P3B       |                    | 1               | Ι   | ST          | PORTH<5> data input.                                                                                                                      |

|           | AN13               | 1               | I   | ANA         | A/D input channel 13. Default configuration on POR.                                                                                       |

|           | P3B <sup>(1)</sup> | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, channel B. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RH6/AN14/ | RH6                | 0               | 0   | DIG         | LATH<6> data output.                                                                                                                      |

| P1C       |                    | 1               | I   | ST          | PORTH<6> data input.                                                                                                                      |

|           | AN14               | 1               | I   | ANA         | A/D input channel 14. Default configuration on POR.                                                                                       |

|           | P1C <sup>(1)</sup> | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel C. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RH7/AN15/ | RH7                | 0               | 0   | DIG         | LATH<7> data output.                                                                                                                      |

| P1B       |                    | 1               | Ι   | ST          | PORTH<7> data input.                                                                                                                      |

|           | AN15               | 1               | I   | ANA         | A/D input channel 15. Default configuration on POR.                                                                                       |

|           | P1B <sup>(1)</sup> | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel B. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

TABLE 11-15: PORTH FUNCTIONS

**Legend:** PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

| TABLE 11-16: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTH |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| TRISH  | TRISH7 | TRISH6 | TRISH5 | TRISH4 | TRISH3 | TRISH2 | TRISH1 | TRISH0 | 60                         |

| PORTH  | RH7    | RH6    | RH5    | RH4    | RH3    | RH2    | RH1    | RH0    | 60                         |

| LATH   | LATH7  | LATH6  | LATH5  | LATH4  | LATH3  | LATH2  | LATH1  | LATH0  | 60                         |

| ADCON1 | _      | _      | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 59                         |

© 2008 Microchip Technology Inc.

#### 13.3.3 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 13-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the Timer1 oscillator, a grounded guard ring around the oscillator circuit may be helpful when used on a single-sided PCB or in addition to a ground plane.

# 13.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# 13.5 Resetting Timer1 Using the CCP Special Event Trigger

If any of the CCP modules are configured to use Timer1 and generate a Special Event Trigger in Compare mode (CCPxM<3:0>, this signal will reset Timer1. The trigger from the ECCP2 module will also start an A/D conversion if the A/D module is enabled (see **Section 17.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRH:CCPRL register pair effectively becomes a period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

**Note:** The Special Event Triggers from the CCPx module will not set the TMR1IF interrupt flag bit (PIR1<0>).

# 13.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 13.3 "Timer1 Oscillator"** above) gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 13-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

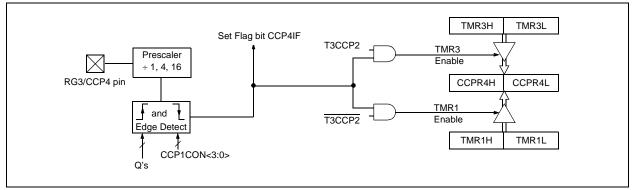

# 17.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding CCPx pin. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by the mode select bits, CCPxM<3:0> (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared in software. If another capture occurs before the value in the CCPRx registers is read, the old captured value is overwritten by the new captured value.

#### 17.2.1 CCPx PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If a CCPx pin is configured as an output, a |

|-------|---------------------------------------------|

|       | write to the port can cause a capture       |

|       | condition.                                  |

#### 17.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation will not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 17.1.1 "CCP Modules and Timer Resources").

# 17.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

# 17.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCPxM<3:0>). Whenever the CCP module is turned off, or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 17-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 17-1: CHANGING BETWEEN CAPTURE PRESCALERS (CCP5 SHOWN)

|       |             |   | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP5CON     | ; | Load CCP5CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

#### FIGURE 17-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

|    | CCP1CON<7:6>              | SIGNAL               | ← Duty<br>Cycle –        |                      | PR2 + 1    |

|----|---------------------------|----------------------|--------------------------|----------------------|------------|

|    |                           |                      | •                        | – Period –           |            |

| 00 | (Single Output)           | P1A Modulated        | <br>1                    |                      | I          |

|    |                           | P1A Modulated        |                          | Delay <sup>(1)</sup> | <br> <br>  |

| 10 | (Half-Bridge)             | P1B Modulated        | <br>Delay <sup>(1)</sup> |                      |            |

|    |                           | P1A Active           |                          |                      |            |

|    | (Full-Bridge,<br>Forward) | P1B Inactive         | <br>·<br>·<br>·          | 1<br>1               |            |

| 01 |                           | P1C Inactive         | <br>i<br>                | <br>                 |            |

|    |                           | P1D Modulated        |                          | [                    |            |

|    |                           | P1A Inactive         | <br>1<br>1<br>1          | 1<br>1<br>1          | 1<br> <br> |

| 11 | (Full-Bridge,             | P1B Modulated        | <br>-                    |                      |            |

| 11 | Reverse)                  | P1C Active           | <br>1<br>1               |                      |            |

|    |                           | P1D Inactive         | <br>1<br>                | 1<br>1<br>1          | · · · · ·  |

|    |                           |                      |                          |                      | 1          |

|    | ationships:               | PR2 + 1) * (TMR2 Pre | luo)                     |                      |            |

# FIGURE 18-3: PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

Note 1: Dead-band delay is programmed using the ECCP1DEL register (Section 18.4.6 "Programmable Dead-Band Delay").

# 19.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPxCON1)

- MSSP Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

# REGISTER 19-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| R/W-0         | R/W-0                                                                                                                                                            | R-0                                                                                                                                 | R-0             | R-0              | R-0             | R-0             | R-0   |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| SMP           | CKE                                                                                                                                                              | D/A                                                                                                                                 | Р               | S                | R/W             | UA              | BF    |  |  |  |  |  |

| bit 7         |                                                                                                                                                                  | •                                                                                                                                   | •               |                  | •               |                 | bit ( |  |  |  |  |  |

|               |                                                                                                                                                                  |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| Legend:       |                                                                                                                                                                  |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| R = Readabl   |                                                                                                                                                                  | W = Writable                                                                                                                        |                 | -                | mented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                              | '1' = Bit is set                                                                                                                    |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

|               |                                                                                                                                                                  |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 7         | SMP: Samp                                                                                                                                                        |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | SPI Master r                                                                                                                                                     |                                                                                                                                     | d of doto out   | aut time         |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                                                  | <ul> <li>1 = Input data sampled at end of data output time</li> <li>0 = Input data sampled at middle of data output time</li> </ul> |                 |                  |                 |                 |       |  |  |  |  |  |

|               | -                                                                                                                                                                | SPI Slave mode:                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                                                  | e cleared when                                                                                                                      | SPI is used in  | n Slave mode.    |                 |                 |       |  |  |  |  |  |

| bit 6         | CKE: SPI Clock Select bit                                                                                                                                        |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | <ul> <li>1 = Transmit occurs on transition from active to Idle clock state</li> <li>0 = Transmit occurs on transition from Idle to active clock state</li> </ul> |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Transmit                                                                                                                                                     | t occurs on trans                                                                                                                   | sition from Idl | e to active cloc | k state         |                 |       |  |  |  |  |  |

|               | Note:                                                                                                                                                            | Polarity of clock                                                                                                                   | state is set by | y the CKP bit (S | SSPxCON1<4>     | •).             |       |  |  |  |  |  |

| bit 5         | D/A: Data/Address bit                                                                                                                                            |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | Used in I <sup>2</sup> C                                                                                                                                         | mode only.                                                                                                                          |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 4         | P: Stop bit                                                                                                                                                      |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | Used in I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.                                                      |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | S: Start bit                                                                                                                                                     |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | Used in I <sup>2</sup> C                                                                                                                                         | •                                                                                                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 2         |                                                                                                                                                                  | Write Informatior                                                                                                                   | n bit           |                  |                 |                 |       |  |  |  |  |  |

|               | Used in I <sup>2</sup> C                                                                                                                                         | mode only.                                                                                                                          |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 1         | UA: Update                                                                                                                                                       |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | Used in I <sup>2</sup> C                                                                                                                                         |                                                                                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 0         |                                                                                                                                                                  | ull Status bit (Re                                                                                                                  |                 | only)            |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                                                  | complete, SSP>                                                                                                                      |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Receive                                                                                                                                                      | not complete, S                                                                                                                     | SPXBUF is e     | mpty             |                 |                 |       |  |  |  |  |  |

# 19.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Each MSSP module consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full detect bit, BF (SSPxSTAT<0>) and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 19-1 shows the loading of the SSPxBUF (SSPxSR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

|      | FLE 19- | I. LUADING   | The SSPIBUR (SSPISK) REGISTER                |

|------|---------|--------------|----------------------------------------------|

| LOOP | BTFSS   | SSP1STAT, BF | ;Has data been received (transmit complete)? |

|      | BRA     | LOOP         | ;No                                          |

|      | MOVF    | SSP1BUF, W   | ;WREG req = contents of SSP1BUF              |

|      | MOVWF   | RXDATA       | ;Save in user RAM, if data is meaningful     |

|      | MOVF    | TXDATA, W    | ;W reg = contents of TXDATA                  |

|      | MOVWF   | SSP1BUF      | ;New data to xmit                            |

### EXAMPLE 19-1: LOADING THE SSP1BUF (SSP1SR) REGISTER

NOTES:

# 25.5 Program Verification and Code Protection

The user program memory is divided into four blocks for PIC18F6527/8527 devices, five blocks for PIC18F6622/8622 devices, six blocks for PIC18F6627/ 8627 devices and eight blocks for PIC18F6722/8722 devices. One of these is a boot block of 2, 4 or 8 Kbytes. The remainder of the memory is divided into blocks on binary boundaries. Each of the blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 25-5 shows the program memory organization for 48, 64, 96 and 128-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 25-3.

# FIGURE 25-5: CODE-PROTECTED PROGRAM MEMORY FOR THE PIC18F8722 FAMILY

| 000000h   | Code Memory                      | •          |                            | MEM                       | ORY SIZE/DEVICE           | E                          |                                        |         |         |                                        |         |

|-----------|----------------------------------|------------|----------------------------|---------------------------|---------------------------|----------------------------|----------------------------------------|---------|---------|----------------------------------------|---------|

| 01FFFFh   |                                  | Ī          | 128 Kbytes<br>(PIC18FX722) | 96 Kbytes<br>(PIC18FX627) | 64 Kbytes<br>(PIC18FX622) | 48 Kbytes<br>(PIC18FX527)  | Address<br>Range                       |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            | 000000h                                |         |         |                                        |         |

|           | Unimplemented                    |            | Boot Block                 | Boot Block                | Boot Block                | Boot Block                 | 0007FFh* or<br>000FFFh* or<br>001FFFh* |         |         |                                        |         |

|           | Read as '0'                      |            |                            |                           |                           | Block 0                    | Block 0                                | Block 0 | Block 0 | 000800h* or<br>001000h* or<br>002000h* |         |

|           |                                  |            |                            |                           |                           |                            | 003FFFh                                |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            | 004000h                                |         |         |                                        |         |

|           |                                  |            | Block 1                    | Block 1                   | Block 1                   | Block 1                    |                                        |         |         |                                        |         |

| 0000001   |                                  |            |                            |                           |                           |                            | 007FFFh<br>008000h                     |         |         |                                        |         |

| 200000h   | Configuration<br>and ID<br>Space |            | Block 2                    | Block 2                   | Block 2                   | Block 2                    | 00000011                               |         |         |                                        |         |

|           |                                  |            | Block 2                    | Block 2                   | BIOCK 2                   | DIOCK 2                    |                                        |         |         |                                        |         |

|           |                                  | dID 🖌      |                            |                           |                           |                            | 00BFFFh<br>00C000h                     |         |         |                                        |         |

|           |                                  |            | Block 3                    | Block 3                   | Block 3                   |                            |                                        |         |         |                                        |         |

|           |                                  |            | BIOORO                     | Diooko                    | Bioon                     |                            | 00FFFFh                                |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            |                                        |         |         |                                        | 010000h |

|           |                                  |            | Block 4                    | Block 4                   |                           |                            |                                        |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            | 013FFFh                                |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            | 014000h                                |         |         |                                        |         |

|           |                                  |            | Block 5                    | Block 5                   |                           | Unimplemented<br>Read '0's |                                        |         |         |                                        |         |

| 3FFFFFh   |                                  |            |                            |                           | Unimplemented             | Neau 03                    | 017FFFh                                |         |         |                                        |         |

|           |                                  |            |                            |                           | Read '0's                 |                            | 018000h                                |         |         |                                        |         |

|           |                                  |            | Block 6                    |                           |                           |                            |                                        |         |         |                                        |         |

|           |                                  |            |                            | Unimplemented             |                           |                            | 01BFFFh                                |         |         |                                        |         |

|           |                                  |            |                            | Read '0's                 |                           |                            | 01C000h                                |         |         |                                        |         |

|           |                                  |            | Block 7                    |                           |                           |                            |                                        |         |         |                                        |         |

|           |                                  |            |                            |                           |                           |                            | 01FFFFh                                |         |         |                                        |         |

| Note: Siz | zes of memory area               | as are not | to scale.                  |                           |                           |                            | -                                      |         |         |                                        |         |

| * Bo      | oot block size is det            | ermined b  | by the BBSIZ<1:0>          | bits in CONFIG4L.         |                           |                            |                                        |         |         |                                        |         |

| DAW                   | Decimal A             | djust W Regis                      | ster       | DECF                  | Decremen                 | t f                                 |                 |

|-----------------------|-----------------------|------------------------------------|------------|-----------------------|--------------------------|-------------------------------------|-----------------|

| Syntax:               | DAW                   |                                    |            | Syntax:               | DECF f{,                 | d {,a}}                             |                 |

| Operands:             | None                  |                                    |            | Operands:             | $0 \leq f \leq 255$      |                                     |                 |

| Operation:            | lf [W<3:0> :          | > 9] or [DC = 1                    | ] then     |                       | d ∈ [0,1]                |                                     |                 |

|                       | . ,                   | $6 \rightarrow W < 3:0>;$          |            | On another            | a ∈ [0,1]                |                                     |                 |

|                       | else<br>(W<3:0>) –    | → W<3:0>                           |            | Operation:            | $(f) - 1 \rightarrow de$ |                                     |                 |

|                       | (11 10107)            |                                    |            | Status Affected:      | C, DC, N, (              |                                     |                 |

|                       |                       | > 9] or [C = 1]                    |            | Encoding:             | 0000                     |                                     | ff fff          |

|                       | (VV<7:4>) +<br>C = 1; | $6 \rightarrow W < 7:4>;$          |            | Description:          |                          | register 'f'. If<br>red in W. If 'd |                 |

|                       | else                  |                                    |            |                       |                          | red back in re                      | ,               |

|                       | (W<7:4>) –            | → W<7:4>                           |            |                       | (default).               |                                     | 0               |

| Status Affected:      | С                     |                                    |            |                       |                          | he Access Ba                        |                 |

| Encoding:             | 0000                  | 0000 000                           | 00 0111    |                       |                          | he BSR is use                       | ed to select th |

| Description:          | •                     | ts the eight-bit                   |            |                       | GPR bank                 |                                     | lad in atruatio |

|                       | •                     | om the earlier a<br>each in packed |            |                       |                          | nd the extend<br>led, this instru   |                 |

|                       |                       | es a correct pa                    |            |                       | in Indexed               | Literal Offset                      | Addressing      |

|                       | result.               |                                    |            |                       |                          | hever $f \le 95$ (5                 | ,               |

| Words:                | 1                     |                                    |            |                       |                          | .2.3 "Byte-Or<br>d Instruction      |                 |

| Cycles:               | 1                     |                                    |            |                       | Literal Off              | set Mode" for                       | details.        |

| Q Cycle Activity:     |                       |                                    |            | Words:                | 1                        |                                     |                 |

| Q1                    | Q2                    | Q3                                 | Q4         | Cycles:               | 1                        |                                     |                 |