Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8622t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 2-2:CAPACITOR SELECTION FOR<br/>QUARTZ CRYSTALS

| Osc Type | Crystal<br>Freq                     | Typical Capa<br>Tes                       | acitor Values<br>ted:                     |  |  |

|----------|-------------------------------------|-------------------------------------------|-------------------------------------------|--|--|

|          | Fieq                                | C1                                        | C2                                        |  |  |

| LP       | 32 kHz                              | 22 pF                                     | 22 pF                                     |  |  |

| XT       | 1 MHz<br>4 MHz                      | 22 pF<br>22 pF                            | 22 pF<br>22 pF                            |  |  |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF |  |  |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588 PIC<sup>®</sup> Microcontroller Oscillator Design Guide

- AN826 Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices

- AN849 Basic PIC<sup>®</sup> Oscillator Design

- AN943 Practical PIC<sup>®</sup> Oscillator Analysis and Design

- AN949 Making Your Oscillator Work

See the notes following this table for additional information.

**Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

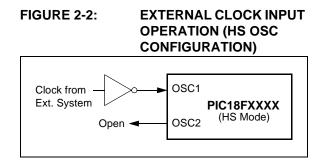

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2. When operated in this mode, parameters D033 and D043 apply.

### 2.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

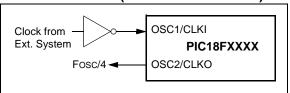

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

#### FIGURE 2-3:

#### EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

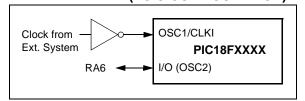

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode. When operated in this mode, parameters D033A and D043A apply.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

#### 5.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.4 FAST REGISTER STACK

A fast register stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, | FAST | ;STATUS, WREG, BSR      |

|------------|------|-------------------------|

|            |      | ;SAVED IN FAST REGISTER |

|            |      | ; STACK                 |

| •          |      |                         |

| •          |      |                         |

|            |      |                         |

| SUB1 •     |      |                         |

| •          |      |                         |

| RETURN,    | FAST | ;RESTORE VALUES SAVED   |

|            |      | ;IN FAST REGISTER STACK |

#### 5.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of  ${\tt RETLW}\ {\tt nn}$  instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

PCL" instruction does not The "ADDWF Note: update the PCLATH and PCLATU registers. A read operation on PCL must be performed to update PCLATH and PCLATU.

| EXAM      | PLE 5-2:                                         | COMPU                           | ITED GC | TO USING AN OFFSET VALUE                                                                                                                            |

|-----------|--------------------------------------------------|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| MAIN:     | ORG<br>MOVLW<br>CALL                             | 0x0000<br>0x00<br>TABLE         |         |                                                                                                                                                     |

| <br>TABLE | ORG<br>MOVF<br>RLNCF<br>ADDWF                    | 0x8000<br>PCL, F<br>W, W<br>PCL | ;       | A simple read of PCL will update PCLATH, PCLATU<br>Multiply by 2 to get correct offset in table<br>Add the modified offset to force jump into table |

|           | RETLW<br>RETLW<br>RETLW<br>RETLW<br>RETLW<br>END | `A'<br>`B'<br>`C'<br>`D'<br>`E' |         |                                                                                                                                                     |

####

### 5.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSb will always read '0' (see **Section 5.1.2 "Program Counter"**).

Figure 5-5 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 5-5 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 26.0 "Instruction Set Summary"** provides further details of the instruction set.

| FIGURE 5-5: | INSTRUCTIONS IN PROGRAM MEMORY |

|-------------|--------------------------------|

|             |                                |

|                |            |                    |      | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|------|----------------|---------|---------------------------|

|                | Program N  | lemory             |      |                |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |      |                |         | 000002h                   |

|                |            |                    |      |                |         | 000004h                   |

|                |            |                    |      |                |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               |      | 0Fh            | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              |      | EFh            | 03h     | 00000Ah                   |

|                |            |                    |      | F0h            | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 4            | 156h | C1h            | 23h     | 00000Eh                   |

|                |            |                    |      | F4h            | 56h     | 000010h                   |

|                |            |                    |      |                |         | 000012h                   |

|                |            |                    |      |                |         | 000014h                   |

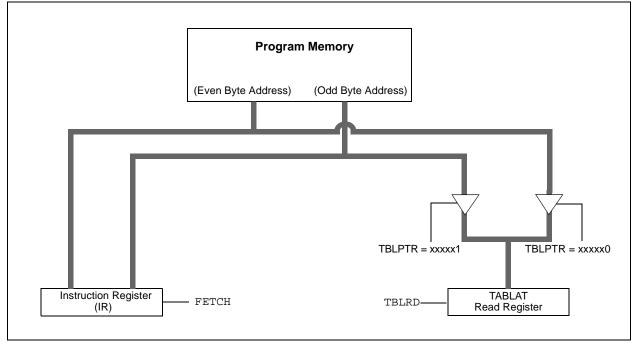

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

| MOT<br>MOT<br>MOT<br>MOT | /WF TBLPTRH<br>/LW CODE_ADDR_L | ;<br>IGH | Load TBLP<br>address o | TR with the<br>f the word | base      |

|--------------------------|--------------------------------|----------|------------------------|---------------------------|-----------|

| MOV                      | WF TBLPTRL                     |          |                        |                           |           |

| READ_WORD                |                                |          |                        |                           |           |

| TBI                      | JRD*+                          | ;        | read into              | TABLAT and                | increment |

| MOV                      | /F TABLAT, W                   | ;        | get data               |                           |           |

| MOV                      | WF WORD_EVEN                   |          |                        |                           |           |

| TBI                      | LRD*+                          | ;        | read into              | TABLAT and                | increment |

| MOV                      | /F TABLAT, W                   | ;        | get data               |                           |           |

| MOV                      | /F WORD_ODD                    |          |                        |                           |           |

|                          |                                |          |                        |                           |           |

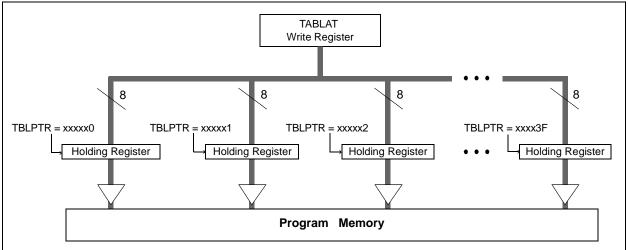

#### 6.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 holding registers before executing a write operation.

#### FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

## 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the row erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

An example of the required code is shown in Example 6-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

|                |       |         |       | · /                             |

|----------------|-------|---------|-------|---------------------------------|

| PROGRAM_MEMORY |       |         |       |                                 |

|                | BSF   | EECON1, | EEPGD | ; point to Flash program memory |

|                | BCF   | EECON1, | CFGS  | ; access Flash program memory   |

|                | BSF   | EECON1, | WREN  | ; enable write to memory        |

|                | BCF   | INTCON, | GIE   | ; disable interrupts            |

|                | MOVLW | 55h     |       |                                 |

| Required       | MOVWF | EECON2  |       | ; write 55h                     |

| Sequence       | MOVLW | 0AAh    |       |                                 |

|                | MOVWF | EECON2  |       | ; write OAAh                    |

|                | BSF   | EECON1, | WR    | ; start program (CPU stall)     |

|                | BSF   | INTCON, | GIE   | ; re-enable interrupts          |

|                | BCF   | EECON1, | WREN  | ; disable write to memory       |

|                |       |         |       |                                 |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 25.0 "Special Features of the CPU" for more detail.

#### 6.6 Flash Program Operation During Code Protection

See Section 25.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7      | Bit 6         | Bit 5                 | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|------------|---------------|-----------------------|---------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU |            | —             | bit 21 <sup>(1)</sup> | Program Me    | emory Table I | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 57                         |

| TBPLTRH | Program Me | emory Table   | Pointer H             | ligh Byte (TE | BLPTR<15:8    | S>)          |               |            | 57                         |

| TBLPTRL | Program Me | emory Table   | Pointer L             | ow Byte (TB   | LPTR<7:0>     | )            |               |            | 57                         |

| TABLAT  | Program Me | emory Table   | Latch                 |               |               |              |               |            | 57                         |

| INTCON  | GIE/GIEH   | PEIE/GIEL     | TMR0IE                | INT0IE        | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 57                         |

| EECON2  | EEPROM C   | Control Regis | ster 2 (not           | a physical r  | egister)      |              |               |            | 59                         |

| EECON1  | EEPGD      | CFGS          | -                     | FREE          | WRERR         | WREN         | WR            | RD         | 59                         |

| IPR2    | OSCFIP     | CMIP          | —                     | EEIP          | BCL1IP        | HLVDIP       | TMR3IP        | CCP2IP     | 60                         |

| PIR2    | OSCFIF     | CMIF          | —                     | EEIF          | BCL1IF        | HLVDIF       | TMR3IF        | CCP2IF     | 60                         |

| PIE2    | OSCFIE     | CMIE          | _                     | EEIE          | BCL1IE        | HLVDIE       | TMR3IE        | CCP2IE     | 60                         |

TABLE 6-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

**Note 1:** Bit 21 of TBLPTRU allows access to the device Configuration bits.

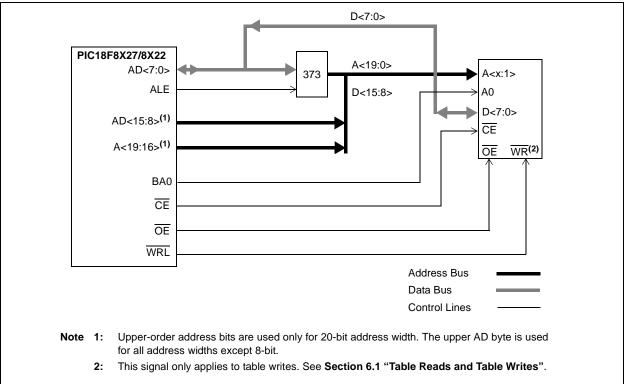

#### 7.6 8-Bit Data Width Modes

In 8-Bit Data Width mode, the External Memory Bus operates only in Multiplexed mode; that is, data shares the 8 least significant bits of the address bus.

Figure 7-7 shows an example of 8-bit Multiplexed mode for PIC18F8527/8622/8627/8722 devices. This mode is used for a single 8-bit memory connected for 16-bit operation. The instructions will be fetched as two 8-bit bytes on a shared data/address bus. The two bytes are sequentially fetched within one instruction cycle (TCY). Therefore, the designer must choose external memory devices according to timing calculations based on 1/2 TCY (2 times the instruction rate). For proper memory speed selection, glue logic propagation delay times must be considered along with setup and hold times. The Address Latch Enable (ALE) pin indicates that the address bits A<15:0> are available on the External Memory Interface bus. The Output Enable signal ( $\overline{OE}$ ) will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The least significant bit of the address, BA0, must be connected to the memory devices in this mode. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing; it is inactive (asserted high) whenever the device is in Sleep mode.

This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

The appropriate level of BA0 control line is strobed on the LSb of the TBLPTR.

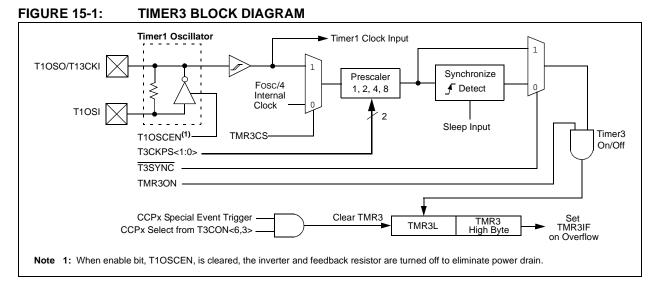

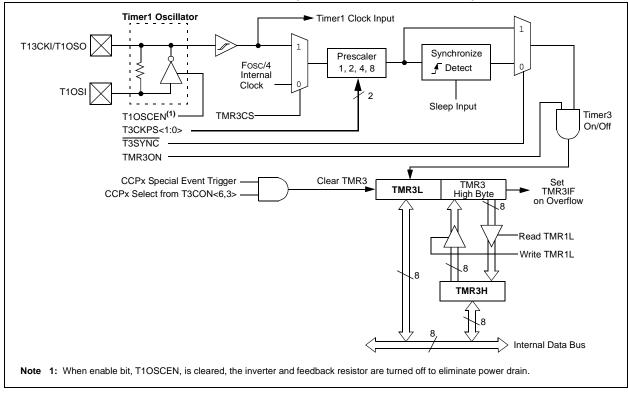

#### 15.1 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

As with Timer1, the RC1/T1OSI and RC0/T1OSO/ T13CKI pins become inputs when the Timer1 oscillator is enabled. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

#### FIGURE 15-2: TIMER3 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

### **18.1 ECCP Outputs and Configuration**

Each of the Enhanced CCP modules may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are multiplexed with various I/O pins. Some ECCPx pin assignments are constant, while others change based on device configuration. For those pins that do change, the controlling bits are:

- CCP2MX Configuration bit (CONFIG3H<0>)

- ECCPMX Configuration bit (CONFIG3H<1>)

- Program Memory mode (set by Configuration bits, CONFIG3L<1:0>)

The pin assignments for the Enhanced CCP modules are summarized in Table 18-1, Table 18-2 and Table 18-3. To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxMx and CCPxMx bits (CCPxCON<7:6> and <3:0>, respectively). The appropriate TRIS direction bits for the corresponding port pins must also be set as outputs.

#### 18.1.1 USE OF CCP4 AND CCP5 WITH ECCP1 AND ECCP3

Only the ECCP2 module has four dedicated output pins available for use. Assuming that the I/O ports or other multiplexed functions on those pins are not needed, they may be used whenever needed without interfering with any other CCP module.

ECCP1 and ECCP3, on the other hand, only have three dedicated output pins: ECCPx/P3A, PxB and PxC. Whenever these modules are configured for Quad PWM mode, the pin used for CCP4 or CCP5 takes priority over the D output pins for ECCP3 and ECCP1, respectively.

#### 18.1.2 ECCP MODULE OUTPUTS, PROGRAM MEMORY MODES AND EMB ADDRESS BUS WIDTH

For PIC18F8527/8622/8627/8722 devices, the program memory mode of the device (Section 7.2 "Address and Data Width" and Section 7.4 "Program Memory Modes and the External Memory Bus") impacts both pin multiplexing and the operation of the module.

The ECCP2 input/output (ECCP2/P2A) can be multiplexed to one of three pins. By default, this is RC1 for all devices; in this case, the default is in effect when CCP2MX is set and the device is operating in Microcontroller mode. With PIC18F8527/8622/8627/8722 devices, three other options exist. When CCP2MX is not set (= 0) and the device is in Microcontroller mode, ECCP2/P2A is multiplexed to RE7; in all other program memory modes, it is multiplexed to RB3.

Another option is for ECCPMX to be set while the device is operating in one of the three other program memory modes. In this case, ECCP1 and ECCP3 operate as compatible (i.e., single output) CCP modules. The pins used by their other outputs (PxB through PxD) are available for other multiplexed functions. ECCP2 continues to operate as an Enhanced CCP module regardless of the program memory mode.

The final option is that the ABW<1:0> Configuration bits can be used to select 8, 12, 16 or 20-bit EMB addressing. Pins not assigned to EMB address pins are available for peripheral or port functions.

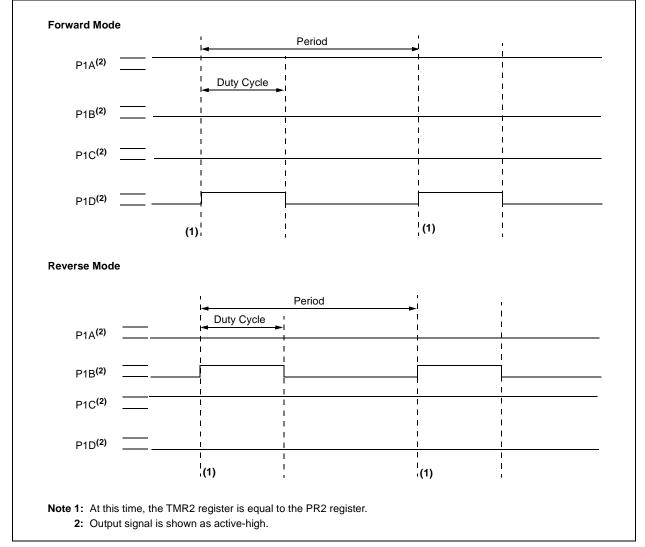

#### 18.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 18-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTC<2>, PORTE<6:5> and PORTG<4> data latches. Alternatively, P1B and P1C can be assigned to PORTH<7> and PORTH<6>, respectively, by programming the ECCPMX Configuration bit to '0'. See Table 18-1, Table 18-2 and Table 18-3 for more information. The associated bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

| <b>IABLE 18-5</b>       | REGIS        | IEK2 422      | OCIATED    |               |          | ES AND  |         | O TIMERA | 4                          |

|-------------------------|--------------|---------------|------------|---------------|----------|---------|---------|----------|----------------------------|

| Name                    | Bit 7        | Bit 6         | Bit 5      | Bit 4         | Bit 3    | Bit 2   | Bit 1   | Bit 0    | Reset<br>Values<br>on page |

| INTCON                  | GIE/GIEH     | PEIE/GIEL     | TMR0IE     | INT0IE        | RBIE     | TMR0IF  | INT0IF  | RBIF     | 57                         |

| RCON                    | IPEN         | SBOREN        | _          | RI            | TO       | PD      | POR     | BOR      | 58                         |

| PIR1                    | PSPIF        | ADIF          | RC1IF      | TX1IF         | SSP1IF   | CCP1IF  | TMR2IF  | TMR1IF   | 60                         |

| PIE1                    | PSPIE        | ADIE          | RC1IE      | TX1IE         | SSP1IE   | CCP1IE  | TMR2IE  | TMR1IE   | 60                         |

| IPR1                    | PSPIP        | ADIP          | RC1IP      | TX1IP         | SSP1IP   | CCP1IP  | TMR2IP  | TMR1IP   | 60                         |

| PIR2                    | OSCFIF       | CMIF          | _          | EEIF          | BCL1IF   | HLVDIF  | TMR3IF  | CCP2IF   | 60                         |

| PIE2                    | OSCFIE       | CMIE          | _          | EEIE          | BCL1IE   | HLVDIE  | TMR3IE  | CCP2IE   | 60                         |

| IPR2                    | OSCFIP       | CMIP          | _          | EEIP          | BCL1IP   | HLVDIP  | TMR3IP  | CCP2IP   | 60                         |

| PIR3                    | SSP2IF       | BCL2IF        | RC2IF      | TX2IF         | TMR4IF   | CCP5IF  | CCP4IF  | CCP3IF   | 60                         |

| PIE3                    | SSP2IE       | BCL2IE        | RC2IE      | TX2IE         | TMR4IE   | CCP5IE  | CCP4IE  | CCP3IE   | 60                         |

| IPR3                    | SSP2IP       | BCL2IP        | RC2IP      | TX2IP         | TMR4IP   | CCP5IP  | CCP4IP  | CCP3IP   | 60                         |

| TRISB                   | TRISB7       | TRISB6        | TRISB5     | TRISB4        | TRISB3   | TRISB2  | TRISB1  | TRISB0   | 60                         |

| TRISC                   | TRISC7       | TRISC6        | TRISC5     | TRISC4        | TRISC3   | TRISC2  | TRISC1  | TRISC0   | 60                         |

| TRISE                   | TRISE7       | TRISE6        | TRISE5     | TRISE4        | TRISE3   | TRISE2  | TRISE1  | TRISE0   | 60                         |

| TRISG                   | —            | —             | —          | TRISG4        | TRISG3   | TRISG2  | TRISG1  | TRISG0   | 60                         |

| TRISH <sup>(2)</sup>    | TRISH7       | TRISH6        | TRISH5     | TRISH4        | TRISH3   | TRISH2  | TRISH1  | TRISH0   | 60                         |

| TMR1L                   | Timer1 Regi  | ster Low Byte | )          |               |          |         |         |          | 58                         |

| TMR1H                   | Timer1 Regi  | ster High Byt | е          |               |          |         |         |          | 58                         |

| T1CON                   | RD16         | T1RUN         | T1CKPS1    | T1CKPS0       | T1OSCEN  | T1SYNC  | TMR1CS  | TMR10N   | 58                         |

| TMR2                    | Timer2 Regi  | ster          |            |               |          |         |         |          | 58                         |

| T2CON                   | _            | T2OUTPS3      | T2OUTPS2   | T2OUTPS1      | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0  | 58                         |

| PR2                     | Timer2 Peric | d Register    |            |               |          |         |         |          | 58                         |

| TMR3L                   | Timer3 Regi  | ster Low Byte | 9          |               |          |         |         |          | 59                         |

| TMR3H                   | Timer3 Regi  | ster High Byt | е          |               |          |         |         |          | 59                         |

| T3CON                   | RD16         | T3CCP2        | T3CKPS1    | T3CKPS0       | T3CCP1   | T3SYNC  | TMR3CS  | TMR3ON   | 59                         |

| TMR4                    | Timer4 Regi  | ster          |            |               |          |         |         |          | 61                         |

| T4CON                   | —            | T4OUTPS3      | T4OUTPS2   | T4OUTPS1      | T4OUTPS0 | TMR4ON  | T4CKPS1 | T4CKPS0  | 61                         |

| PR4                     | Timer4 Peric | d Register    |            |               |          |         |         |          | 61                         |

| CCPRxL <sup>(1)</sup>   | Enhanced C   | apture/Comp   | are/PWM Re | gister x Low  | Byte     |         |         |          | 59, 61                     |

| CCPRxH <sup>(1)</sup>   | Enhanced C   | apture/Comp   | are/PWM Re | gister x High | Byte     |         |         |          | 59, 61                     |

| CCPxCON <sup>(1)</sup>  | PxM1         | PxM0          | DCxB1      | DCxB0         | CCPxM3   | CCPxM2  | CCPxM1  | CCPxM0   | 59                         |

| ECCPxAS <sup>(1)</sup>  | ECCPxASE     | ECCPxAS2      | ECCPxAS1   | ECCPxAS0      | PSSxAC1  | PSSxAC0 | PSSxBD1 | PSSxBD0  | 59, 61                     |

| ECCPxDEL <sup>(1)</sup> | PxRSEN       | PxDC6         | PxDC5      | PxDC4         | PxDC3    | PxDC2   | PxDC1   | PxDC0    | 61                         |

#### TABLE 18-5: REGISTERS ASSOCIATED WITH ECCP MODULES AND TIMER1 TO TIMER4

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

**Note 1:** Generic term for all of the identical registers of this name for all Enhanced CCP modules, where 'x' identifies the individual module (ECCP1, ECCP2 or ECCP3). Bit assignments and Reset values for all registers of the same generic name are identical.

2: This register is not implemented on PIC18F6527/6622/6627/6722 devices.

| R/W-0        | R/W-0                                                                                                                | R-0              | R-0                                  | R-0              | R-0                        | R-0             | R-0  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|------------------|----------------------------|-----------------|------|--|--|--|--|--|

| SMP          | CKE                                                                                                                  | D/A              | P <sup>(1)</sup>                     | S <sup>(1)</sup> | R/W <sup>(2,3)</sup>       | UA              | BF   |  |  |  |  |  |

| bit 7        |                                                                                                                      |                  |                                      | ·                | ·                          |                 | bit  |  |  |  |  |  |

| Legend:      |                                                                                                                      |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

| R = Reada    | ble bit                                                                                                              | W = Writab       | ole bit                              | U = Unimpl       | emented bit, rea           | d as '0'        |      |  |  |  |  |  |

| -n = Value a | at POR                                                                                                               | '1' = Bit is s   | set                                  | '0' = Bit is c   | leared                     | x = Bit is unkr | nown |  |  |  |  |  |

|              |                                                                                                                      |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

| bit 7        |                                                                                                                      | Rate Control I   | bit                                  |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      | Slave mode:      | a la al fair. Otara da               | nd Cranadara     |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      |                  | abled for Standa                     |                  | de (100 kHz and<br>00 kHz) | TTMHZ)          |      |  |  |  |  |  |

| bit 6        | CKE: SMBu                                                                                                            |                  | 5 1                                  | ,                | ,                          |                 |      |  |  |  |  |  |

|              | In Master or                                                                                                         | Slave mode:      |                                      |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      | SMBus specif     |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | _                                                                                                                    | SMBus speci      | fic inputs                           |                  |                            |                 |      |  |  |  |  |  |

| bit 5        | D/A: Data/A                                                                                                          |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | <u>In Master m</u><br>Reserved.                                                                                      | <u>ode:</u>      |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | In Slave mo                                                                                                          | de:              |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | 1 = Indicate:                                                                                                        | s that the last  | byte received o                      |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      |                  | byte received o                      | r transmitted    | was address                |                 |      |  |  |  |  |  |

| bit 4        | P: Stop bit <sup>(1</sup>                                                                                            |                  |                                      | ( ( ) (          |                            |                 |      |  |  |  |  |  |

|              | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul> |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

| bit 3        | S: Start bit <sup>(1</sup>                                                                                           |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      |                  | bit has been det                     | ected last       |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      | was not dete     |                                      |                  |                            |                 |      |  |  |  |  |  |

| bit 2        |                                                                                                                      | Write Informa    | tion bit <sup>(2,3)</sup>            |                  |                            |                 |      |  |  |  |  |  |

|              | <u>In Slave mo</u><br>1 = Read                                                                                       | <u>de:</u>       |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | 1 = Read<br>0 = Write                                                                                                |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | In Master m                                                                                                          | ode:             |                                      |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      | t is in progres  |                                      |                  |                            |                 |      |  |  |  |  |  |

| L:1 4        |                                                                                                                      | t is not in proo | -                                    | الم معامل        |                            |                 |      |  |  |  |  |  |

| bit 1        | -                                                                                                                    |                  | 10-bit Slave mod<br>r peeds to updat |                  | s in the SSPxAD            | D register      |      |  |  |  |  |  |

|              |                                                                                                                      |                  | ed to be updated                     |                  |                            | Diegister       |      |  |  |  |  |  |

| bit 0        | BF: Buffer F                                                                                                         | ull Status bit   |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | In Transmit                                                                                                          |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | 1 = SSPxBL                                                                                                           |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              | 0 = SSPxBL<br>In Receive r                                                                                           |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

|              |                                                                                                                      |                  | s not include the                    | ACK and Sto      | op bits)                   |                 |      |  |  |  |  |  |

|              |                                                                                                                      |                  | loes not include                     |                  |                            |                 |      |  |  |  |  |  |

| Note 1:      | This bit is cleared                                                                                                  | d on Reset an    | d when SSPEN                         | is cleared.      |                            |                 |      |  |  |  |  |  |

|              | This bit holds the                                                                                                   |                  |                                      |                  |                            |                 |      |  |  |  |  |  |

### REGISTER 19-3: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

address match to the next Start bit, Stop bit or not ACK bit.

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Active mode.

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|----------|-------------|-------------|--------------|--------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR1     | PSPIF    | ADIF        | RC1IF       | TX1IF        | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 60                         |

| PIE1     | PSPIE    | ADIE        | RC1IE       | TX1IE        | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 60                         |

| IPR1     | PSPIP    | ADIP        | RC1IP       | TX1IP        | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 60                         |

| TRISC    | TRISC7   | TRISC6      | TRISC5      | TRISC4       | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 60                         |

| TRISG    |          |             | _           | TRISG4       | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 60                         |

| RCSTAx   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 59                         |

| TXREGx   | EUSARTx  | Transmit Re | gister      |              |        |        |        |        | 59                         |

| TXSTAx   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 59                         |

| BAUDCONx | ABDOVF   | RCIDL       | _           | SCKP         | BRG16  | _      | WUE    | ABDEN  | 61                         |

| SPBRGHx  | EUSARTx  | Baud Rate C | Generator R | egister High | n Byte |        |        |        | 61                         |

| SPBRGx   | EUSARTx  | Baud Rate C | Generator R | egister Low  | Byte   |        |        |        | 59                         |

#### TABLE 20-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

#### 20.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 20.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSRx register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSRx, the TXREGx register will transfer the second word to the TSRx and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7                                          | Bit 6        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|------------------------------------------------|--------------|--------|--------|--------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL    | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR1     | PSPIF                                          | ADIF         | RC1IF  | TX1IF  | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 60                         |

| PIE1     | PSPIE                                          | ADIE         | RC1IE  | TX1IE  | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 60                         |

| IPR1     | PSPIP                                          | ADIP         | RC1IP  | TX1IP  | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 60                         |

| TRISC    | TRISC7                                         | TRISC6       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 60                         |

| TRISG    | —                                              | —            | —      | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 60                         |

| RCSTAx   | SPEN                                           | RX9          | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 59                         |

| TXREGx   | EUSARTx                                        | Transmit Reg | gister |        |        |        |        |        | 59                         |

| TXSTAx   | CSRC                                           | TX9          | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 59                         |

| BAUDCONx | ABDOVF                                         | RCIDL        | _      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 61                         |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |              |        |        |        |        |        | 61     |                            |

| SPBRGx   | EUSARTx Baud Rate Generator Register Low Byte  |              |        |        |        |        |        | 59     |                            |

|          |                                                |              |        |        |        |        |        |        |                            |

#### TABLE 20-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

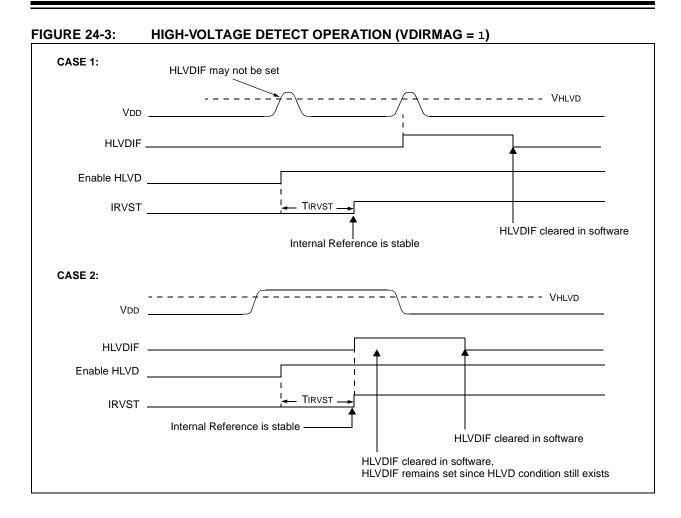

#### 24.5 Applications

In many applications, the ability to detect a drop below or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

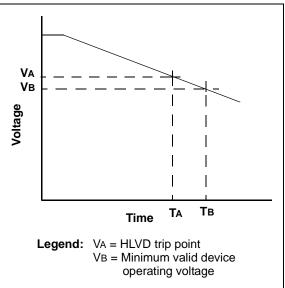

For general battery applications, Figure 24-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### FIGURE 24-4:

## TYPICAL LOW-VOLTAGE DETECT APPLICATION

| R/P-1             | R/P-0                                                                                                                                                                                                                               | R/P-0                                                                                     | R/P-0                                              | U-0                                | R/P-1                               | U-0             | R/P-1  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------|-------------------------------------|-----------------|--------|--|--|

| DEBUG             | XINST                                                                                                                                                                                                                               | BBSIZ1                                                                                    | BBSIZ0                                             | —                                  | LVP                                 | —               | STVREN |  |  |

| bit 7             |                                                                                                                                                                                                                                     | •<br>                                                                                     |                                                    |                                    | •                                   |                 | bit 0  |  |  |

| Legend:           |                                                                                                                                                                                                                                     |                                                                                           |                                                    |                                    |                                     |                 |        |  |  |

| R = Readable      | e bit                                                                                                                                                                                                                               | W = Writable                                                                              | bit                                                | U = Unimplemented bit, read as '0' |                                     |                 |        |  |  |

| -n = Value at POR |                                                                                                                                                                                                                                     | '1' = Bit is set                                                                          |                                                    | '0' = Bit is cle                   | ared                                | x = Bit is unkr | nown   |  |  |

| bit 7             | 1 = Backgrou                                                                                                                                                                                                                        | 00                                                                                        | isabled, RB6                                       | and RB7 config                     | gured as genera<br>edicated to In-C |                 | pins   |  |  |

| bit 6             | <ul> <li>XINST: Extended Instruction Set Enable bit</li> <li>1 = Instruction set extension and Indexed Addressing mode enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> </ul> |                                                                                           |                                                    |                                    |                                     |                 |        |  |  |

| bit 5-4           | 11 = 4K word<br>10 = 4K word<br>01 = 2K word                                                                                                                                                                                        | Boot Block Siz<br>s (8 Kbytes) bo<br>s (8 Kbytes) bo<br>s (4 Kbytes) bo<br>(2 Kbytes) boo | bot block size<br>bot block size<br>bot block size |                                    |                                     |                 |        |  |  |

| bit 3             | Unimplemen                                                                                                                                                                                                                          | ted: Read as '                                                                            | 0'                                                 |                                    |                                     |                 |        |  |  |

| bit 2             | 1 = Single-Su                                                                                                                                                                                                                       | Supply ICSP™<br>pply ICSP ena<br>pply ICSP disa                                           | bled                                               |                                    |                                     |                 |        |  |  |

| bit 1             | Unimplemen                                                                                                                                                                                                                          | ted: Read as '                                                                            | 0'                                                 |                                    |                                     |                 |        |  |  |

| bit 0             | 1 = Stack full/                                                                                                                                                                                                                     | ck Full/Underfl<br>underflow will<br>underflow will                                       | cause Reset                                        |                                    |                                     |                 |        |  |  |

### REGISTER 25-6: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

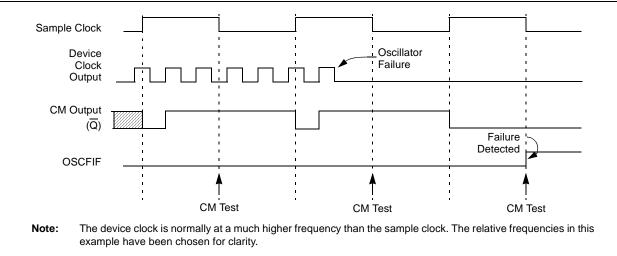

#### 25.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexor selects the clock source selected by the OSCCON register. Fail-Safe Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

#### 25.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events. For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR, or wake from Sleep, will also prevent the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in Section 25.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powermanaged mode is selected, the primary clock is disabled.

| Param.<br>No. | Symbol    | Charac                       | teristic                  | Min              | Max  | Units     | Conditions                   |

|---------------|-----------|------------------------------|---------------------------|------------------|------|-----------|------------------------------|

| 100           | Тнідн     | Clock High Time              | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        |                              |

|               |           |                              | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms        |                              |

| 101           | TLOW      | Clock Low Time               | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        |                              |

|               |           |                              | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms        |                              |

| 102           |           | SDAx and SCLx                | 100 kHz mode              |                  | 1000 | ns        | CB is specified to be from   |

|               |           | Rise Time                    | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns        | 10 to 400 pF                 |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | —                | 300  | ns        |                              |

| 103           | TF        | SDAx and SCLx                | 100 kHz mode              | —                | 300  | ns        | CB is specified to be from   |

|               | Fall Time | Fall Time                    | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns        | 10 to 400 pF                 |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | —                | 100  | ns        |                              |

| 90            | TSU:STA   | Start Condition              | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms        | Only relevant for            |

|               |           | Setup Time                   | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        | Repeated Start               |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms        | condition                    |

| 91            | THD:STA   | Start Condition<br>Hold Time | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms        | After this period, the first |

|               |           |                              | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        | clock pulse is generated     |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms        |                              |

| 106           | THD:DAT   | Data Input                   | 100 kHz mode              | 0                |      | ns        |                              |

|               |           | Hold Time                    | 400 kHz mode              | 0                | 0.9  | ms        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | TBD              |      | ns        |                              |

| 107           | TSU:DAT   | Data Input                   | 100 kHz mode              | 250              |      | ns        | (Note 2)                     |

|               |           | Setup Time                   | 400 kHz mode              | 100              |      | ns        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | TBD              |      | ns        |                              |

| 92            | Tsu:sto   | Stop Condition               | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms        |                              |

|               |           | Setup Time                   | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms        |                              |

| 109           | ΤΑΑ       | Output Valid                 | 100 kHz mode              |                  | 3500 | ns        |                              |

|               |           | from Clock                   | 400 kHz mode              | —                | 1000 | ns        |                              |

|               |           |                              | 1 MHz mode <sup>(1)</sup> |                  | _    | ns        |                              |

| 110           | TBUF      | Bus Free Time                | 100 kHz mode              | 4.7              | —    | ms        | Time the bus must be free    |

|               |           |                              | 400 kHz mode              | 1.3              | —    | ms        | before a new transmission    |

|               |           | 1 MHz mode <sup>(1)</sup>    | TBD                       | —                | ms   | can start |                              |

| D102          | Св        | Bus Capacitive Lo            | bading                    | _                | 400  | pF        |                              |

### TABLE 28-23: MASTER SSP I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

Legend: TBD = To Be Determined

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

2: A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but parameter #107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, parameter #102 + parameter #107 = 1000 + 250 = 1250 ns (for 100 kHz mode,) before the SCLx line is released.

## TABLE 28-26: A/D CONVERTER CHARACTERISTICS: PIC18F6X27/6X22/8X27/8X22 (INDUSTRIAL) PIC18LF6X27/6X22/8X27/8X22 (INDUSTRIAL)

| Param<br>No. | Symbol        | Charac                                            | teristic    | Min        | Тур      | Max              | Units                                  | Conditions                                                  |

|--------------|---------------|---------------------------------------------------|-------------|------------|----------|------------------|----------------------------------------|-------------------------------------------------------------|

| A01          | NR            | Resolution                                        |             | _          | _        | 10               | bit                                    | $\Delta \text{VREF} \geq 3.0 \text{V}$                      |

| A03          | EIL           | Integral Linearity                                | Error       | _          | _        | <±1              | LSb                                    | $\Delta VREF \geq 3.0V$                                     |

| A04          | Edl           | Differential Linea                                | _           | _          | <±1      | LSb              | $\Delta VREF \geq 3.0V$                |                                                             |

| A06          | EOFF          | Offset Error                                      |             |            | <±2      | LSb              | $\Delta \text{VREF} \geq 3.0 \text{V}$ |                                                             |

| A07          | Egn           | Gain Error                                        |             | _          |          | <±1              | LSb                                    | $\Delta VREF \ge 3.0V$                                      |

| A10          | _             | Monotonicity                                      |             | G          | uarantee | d <sup>(1)</sup> | _                                      | $VSS \leq VAIN \leq VREF$                                   |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)        |             | 1.8<br>3   | _        |                  | V<br>V                                 | $\begin{array}{l} VDD < 3.0V \\ VDD \geq 3.0V \end{array}$  |

| A21          | Vrefh         | Reference Voltage High                            |             | Vss        | _        | Vrefh            | V                                      |                                                             |

| A22          | Vrefl         | Reference Voltag                                  | ge Low      | Vss – 0.3V | _        | Vdd - 3.0V       | V                                      |                                                             |

| A25          | VAIN          | Analog Input Vol                                  | tage        | VREFL      |          | Vrefh            | V                                      |                                                             |

| A30          | ZAIN          | Recommended Impedance of<br>Analog Voltage Source |             | —          |          | 2.5              | kΩ                                     |                                                             |

| A40          | IAD           | A/D Current                                       | PIC18FXXXX  | _          | 180      |                  | μΑ                                     | Average current during                                      |

|              |               | from VDD                                          | PIC18LFXXXX | _          | 90       | _                | μΑ                                     | conversion                                                  |

| A50          | IREF          | VREF Input Current <sup>(2)</sup>                 |             |            |          | 5<br>150         | μΑ<br>μΑ                               | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

Note 1: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

2: VREFH current is from RA3/AN3/VREF+ pin or VDD, whichever is selected as the VREFH source. VREFL current is from RA2/AN2/VREF- pin or VSS, whichever is selected as the VREFL source.

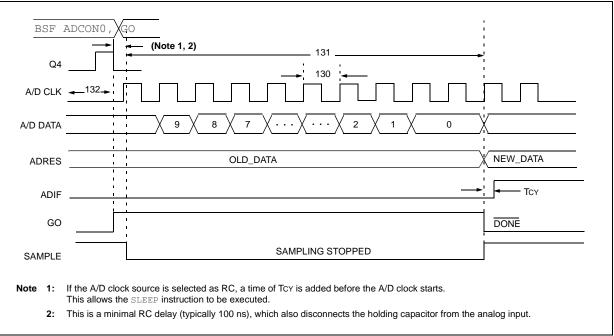

#### FIGURE 28-25: A/D CONVERSION TIMING

| 0    | - |    |

|------|---|----|

| - 51 | ρ | ρr |

|      |   |    |

| Sleep                                                                         |

|-------------------------------------------------------------------------------|

| OSC1 and OSC2 Pin States 40                                                   |

| Sleep Mode45                                                                  |

| Software Simulator (MPLAB SIM)                                                |

| Special Event Trigger. See Compare (CCP Mode).                                |

| Special Event Trigger. See Compare (ECCP Module).                             |

| Special Features of the CPU                                                   |

| Special Function Registers                                                    |

| Map                                                                           |

| •                                                                             |

| SPI Mode (MSSP)                                                               |

| Associated Registers                                                          |

| Bus Mode Compatibility                                                        |

| Clock Speed, Interactions                                                     |

| Effects of a Reset                                                            |

| Enabling SPI I/O209                                                           |

| Master Mode210                                                                |

| Master/Slave Connection209                                                    |