Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8627t-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                                          | Pin Number       | Pin Buffer    |                   |                                                           |  |  |

|---------------------------------------------------|------------------|---------------|-------------------|-----------------------------------------------------------|--|--|

| Pin Name                                          | TQFP             | Туре          | Туре              | Description                                               |  |  |

|                                                   |                  |               |                   | PORTH is a bidirectional I/O port.                        |  |  |

| RH0/A16<br>RH0<br>A16                             | 79               | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 16.          |  |  |

| RH1/A17<br>RH1<br>A17                             | 80               | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 17.          |  |  |

| RH2/A18<br>RH2<br>A18                             | 1                | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 18.          |  |  |

| RH3/A19<br>RH3<br>A19                             | 2                | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 19.          |  |  |

| RH4/AN12/P3C<br>RH4<br>AN12<br>P3C <sup>(5)</sup> | 22               | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 12.<br>ECCP3 PWM output C.   |  |  |

| RH5/AN13/P3B<br>RH5<br>AN13<br>P3B <sup>(5)</sup> | 21               | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 13.<br>ECCP3 PWM output B.   |  |  |

| RH6/AN14/P1C<br>RH6<br>AN14<br>P1C <sup>(5)</sup> | 20               | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 14.<br>ECCP1 PWM output C.   |  |  |

| RH7/AN15/P1B<br>RH7<br>AN15<br>P1B <sup>(5)</sup> | 19               | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 15.<br>ECCP1 PWM output B.   |  |  |

|                                                   | compatible input |               |                   | = CMOS compatible input or output<br>Analog= Analog input |  |  |

| I = Input                                         |                  | 0             |                   | = Output                                                  |  |  |

| TABLE 1-4: | PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|---------------------------------------------------------------|

|            |                                                               |

P = Power  $I^2C^{TM}/SMB = I^2C/SMBus input buffer$

**Note 1:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

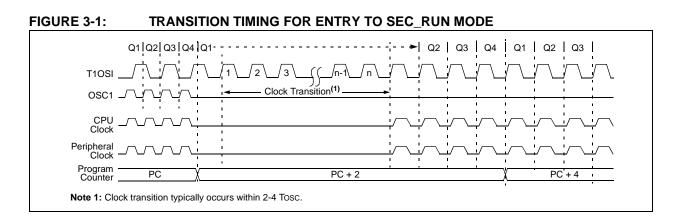

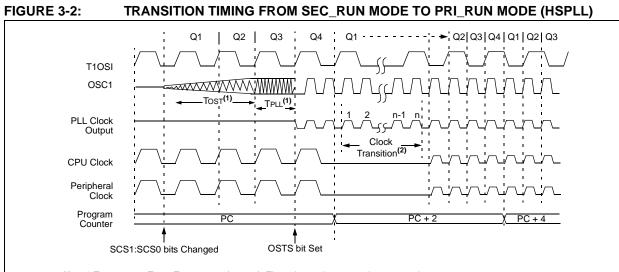

Note1:TOST = 1024 TOSC; TPLL = 2 ms (approx). These intervals are not shown to scale. 2: Clock transition typically occurs within 2-4 TOSC.

## 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer. In this mode, the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

## 7.2 Address and Data Width

PIC18F8527/8622/8627/8722 devices can be independently configured for different address and data widths on the same memory bus. Both address and data width are set by Configuration bits in the CONFIG3L register. As Configuration bits, this means that these options can only be configured by programming the device and are not controllable in software.

The BW bit selects an 8-bit or 16-bit data bus width. Setting this bit (default) selects a data width of 16 bits.

The ADW<1:0> bits determine the address bus width. The available options are 20-bit (default), 16-bit, 12-bit and 8-bit. Selecting any of the options other than 20-bit width makes a corresponding number of high-order lines available for I/O functions; these pins are no longer affected by the setting of the EBDIS bit. For example, selecting a 16-bit Address mode (ADW<1:0> = 10) disables A<19:16> and allows PORTH<3:0> to function without interruptions from the bus. Using smaller address widths allows users to tailor the memory bus to the size of the external memory space for a particular design while freeing up pins for dedicated I/O operation.

Because the ADW bits have the effect of disabling pins for memory bus operations, it is important to always select an address width at least equal to the data width. If 8-bit or 12-bit address widths are used with a 16-bit data width, the upper bits of data will not be available on the bus.

All combinations of address and data widths require multiplexing of address and data information on the same lines. The address and data multiplexing, as well as I/O ports made available by the use of smaller address widths, are summarized in Table 7-2.

## 7.2.1 21-BIT ADDRESSING

As an extension of 20-bit address width operation, the External Memory Bus can also fully address a 2 Mbyte memory space. This is done by using the Bus Address bit 0 (BA0) control line as the Least Significant bit of the address. The UB and LB control signals may also be used with certain memory devices to select the upper and lower bytes within a 16-bit wide data word.

This addressing mode is available in both 8-bit and certain 16-bit Data Width modes. Additional details are provided in Section 7.5.3 "16-bit Byte Select Mode" and Section 7.6 "8-Bit Data Width Modes".

## 7.3 Wait States

While it may be assumed that external memory devices will operate at the microcontroller clock rate, this is often not the case. In fact, many devices require longer times to write or retrieve data than the time allowed by the execution of table read or table write operations.

To compensate for this, the External Memory Bus can be configured to add a fixed delay to each table operation using the bus. Wait states are enabled by setting the WAITx bit. When enabled, the amount of delay is set by the WAIT<1:0> bits (MEMCON<5:4>). The delay is based on multiples of microcontroller instruction cycle time and are added following the instruction cycle when the table operation is executed. The range is from no delay to 3 Tcy (default value).

| Data Width | Address Width | Multiplexed Data and<br>Address Lines (and<br>Corresponding Ports) | Address-Only<br>Lines (and<br>Corresponding Ports) | Ports Available<br>for I/O  |

|------------|---------------|--------------------------------------------------------------------|----------------------------------------------------|-----------------------------|

|            | 8-bit         |                                                                    | _                                                  | All of PORTE and<br>PORTH   |

|            | 12-bit        | AD<7:0>                                                            | AD<11:8><br>(PORTE<3:0>)                           | PORTE<7:4>,<br>All of PORTH |

| 8-bit      | 16-bit        | (PORTD<7:0>)                                                       | AD<15:8><br>(PORTE<7:0>)                           | All of PORTH                |

|            | 20-bit        |                                                                    | A<19:16>, AD<15:8><br>(PORTH<3:0>,<br>PORTE<7:0>)  | _                           |

|            | 16-bit        | AD<15:0>                                                           | —                                                  | All of PORTH                |

| 16-bit     | 20-bit        | (PORTD<7:0>,<br>PORTE<7:0>)                                        | A<19:16><br>(PORTH<3:0>)                           | _                           |

## TABLE 7-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS

## 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

### REGISTER 10-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1         | R/W-1                      | R/W-1                                            | R/W-1            | R/W-1            | R/W-1           | R/W-1           | R/W-1  |  |  |

|---------------|----------------------------|--------------------------------------------------|------------------|------------------|-----------------|-----------------|--------|--|--|

| PSPIP         | ADIP                       | RC1IP                                            | TX1IP            | SSP1IP           | CCP1IP          | TMR2IP          | TMR1IP |  |  |

| bit 7         |                            |                                                  |                  |                  |                 |                 | bit 0  |  |  |

| Legend:       |                            |                                                  |                  |                  |                 |                 |        |  |  |

| R = Readab    | le hit                     | W = Writable                                     | hit              | II = Unimplei    | mented bit, rea | d as '0'        |        |  |  |

| -n = Value at |                            | '1' = Bit is set                                 |                  | '0' = Bit is cle |                 | x = Bit is unkr | nown   |  |  |

|               | ·                          |                                                  |                  |                  |                 |                 | -      |  |  |

| bit 7         | <b>PSPIP:</b> Para         | allel Slave Port F                               | Read/Write Int   | terrupt Priority | bit             |                 |        |  |  |

|               | 1 = High pr<br>0 = Low pri |                                                  |                  |                  |                 |                 |        |  |  |

| bit 6         | ADIP: A/D (                | Converter Interru                                | pt Priority bit  |                  |                 |                 |        |  |  |

|               | 1 = High pr<br>0 = Low pri |                                                  |                  |                  |                 |                 |        |  |  |

| bit 5         | RC1IP: EUS                 | SART1 Receive                                    | Interrupt Prior  | rity bit         |                 |                 |        |  |  |

|               | 0 1                        | 1 = High priority                                |                  |                  |                 |                 |        |  |  |

|               | 0 = Low pri                | •                                                |                  |                  |                 |                 |        |  |  |

| bit 4         |                            | SART1 Transmit                                   | Interrupt Prio   | rity bit         |                 |                 |        |  |  |

|               | 1 = High pr<br>0 = Low pri |                                                  |                  |                  |                 |                 |        |  |  |

| bit 3         | SSP1IP: MS                 | SSP1 Interrupt P                                 | riority bit      |                  |                 |                 |        |  |  |

|               | 1 = High pr                | •                                                |                  |                  |                 |                 |        |  |  |

|               | 0 = Low pri                | •                                                |                  |                  |                 |                 |        |  |  |

| bit 2         |                            | CCP1 Interrupt F                                 | riority bit      |                  |                 |                 |        |  |  |

|               | 1 = High pr<br>0 = Low pri |                                                  |                  |                  |                 |                 |        |  |  |

| bit 1         | -                          | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit |                  |                  |                 |                 |        |  |  |

|               | 1 = High pr                |                                                  |                  |                  |                 |                 |        |  |  |

|               | 0 = Low pri                | ority                                            |                  |                  |                 |                 |        |  |  |

| bit 0         |                            | /R1 Overflow In                                  | terrupt Priority | y bit            |                 |                 |        |  |  |

|               | 1 = High pr                | •                                                |                  |                  |                 |                 |        |  |  |

|               | 0 = Low pri                | onty                                             |                  |                  |                 |                 |        |  |  |

### REGISTER 10-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| R/W-1         | R/W-1                                                  | U-0                                                                      | R/W-1              | R/W-1             | R/W-1           | R/W-1           | R/W-1  |  |  |  |

|---------------|--------------------------------------------------------|--------------------------------------------------------------------------|--------------------|-------------------|-----------------|-----------------|--------|--|--|--|

| OSCFIP        | CMIP                                                   |                                                                          | EEIP               | BCL1IP            | HLVDIP          | TMR3IP          | CCP2IP |  |  |  |

| bit 7         |                                                        |                                                                          |                    |                   |                 |                 | bit C  |  |  |  |

|               |                                                        |                                                                          |                    |                   |                 |                 |        |  |  |  |

| Legend:       |                                                        |                                                                          |                    |                   |                 |                 |        |  |  |  |

| R = Readable  |                                                        | W = Writable                                                             |                    |                   | nented bit, rea |                 |        |  |  |  |

| -n = Value at | POR                                                    | '1' = Bit is set                                                         |                    | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |  |  |  |

| bit 7         | OSCFIP: Osc                                            | cillator Fail Inte                                                       | rrupt Priority b   | pit               |                 |                 |        |  |  |  |

|               | 1 = High prio                                          | •                                                                        |                    |                   |                 |                 |        |  |  |  |

| bit 6         | 0 = Low prior                                          | 5                                                                        | Driority bit       |                   |                 |                 |        |  |  |  |

|               |                                                        | <b>CMIP:</b> Comparator Interrupt Priority bit<br>1 = High priority      |                    |                   |                 |                 |        |  |  |  |

|               | 1 = High pho<br>0 = Low prior                          | •                                                                        |                    |                   |                 |                 |        |  |  |  |

| bit 5         | Unimplemen                                             | ted: Read as '                                                           | 0'                 |                   |                 |                 |        |  |  |  |

| bit 4         | EEIP: Interrup                                         | EEIP: Interrupt Priority bit                                             |                    |                   |                 |                 |        |  |  |  |

|               | 1 = High prio                                          |                                                                          |                    |                   |                 |                 |        |  |  |  |

|               | 0 = Low prior                                          | rity                                                                     |                    |                   |                 |                 |        |  |  |  |

| bit 3         | BCL1IP: MSSP1 Bus Collision Interrupt Priority bit     |                                                                          |                    |                   |                 |                 |        |  |  |  |

|               | 1 = High priority                                      |                                                                          |                    |                   |                 |                 |        |  |  |  |

| <b>L</b> : 0  | 0 = Low prior                                          | •                                                                        | Data at lista www. | nt Duinuitur hit  |                 |                 |        |  |  |  |

| bit 2         | HLVDIP: High/Low-Voltage Detect Interrupt Priority bit |                                                                          |                    |                   |                 |                 |        |  |  |  |

|               | 1 = High priority<br>0 = Low priority                  |                                                                          |                    |                   |                 |                 |        |  |  |  |

| bit 1         | •                                                      | -                                                                        | terrupt Priority   | / bit             |                 |                 |        |  |  |  |

|               |                                                        | <b>TMR3IP:</b> TMR3 Overflow Interrupt Priority bit<br>1 = High priority |                    |                   |                 |                 |        |  |  |  |

|               | 0 = Low prior                                          | •                                                                        |                    |                   |                 |                 |        |  |  |  |

| bit 0         | CCP2IP: ECO                                            | CP2 Interrupt F                                                          | riority bit        |                   |                 |                 |        |  |  |  |

|               | 1 = High prio                                          | •                                                                        |                    |                   |                 |                 |        |  |  |  |

|               | 0 = Low prior                                          | ritv                                                                     |                    |                   |                 |                 |        |  |  |  |

## **18.1 ECCP Outputs and Configuration**

Each of the Enhanced CCP modules may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are multiplexed with various I/O pins. Some ECCPx pin assignments are constant, while others change based on device configuration. For those pins that do change, the controlling bits are:

- CCP2MX Configuration bit (CONFIG3H<0>)

- ECCPMX Configuration bit (CONFIG3H<1>)

- Program Memory mode (set by Configuration bits, CONFIG3L<1:0>)

The pin assignments for the Enhanced CCP modules are summarized in Table 18-1, Table 18-2 and Table 18-3. To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxMx and CCPxMx bits (CCPxCON<7:6> and <3:0>, respectively). The appropriate TRIS direction bits for the corresponding port pins must also be set as outputs.

### 18.1.1 USE OF CCP4 AND CCP5 WITH ECCP1 AND ECCP3

Only the ECCP2 module has four dedicated output pins available for use. Assuming that the I/O ports or other multiplexed functions on those pins are not needed, they may be used whenever needed without interfering with any other CCP module.

ECCP1 and ECCP3, on the other hand, only have three dedicated output pins: ECCPx/P3A, PxB and PxC. Whenever these modules are configured for Quad PWM mode, the pin used for CCP4 or CCP5 takes priority over the D output pins for ECCP3 and ECCP1, respectively.

### 18.1.2 ECCP MODULE OUTPUTS, PROGRAM MEMORY MODES AND EMB ADDRESS BUS WIDTH

For PIC18F8527/8622/8627/8722 devices, the program memory mode of the device (Section 7.2 "Address and Data Width" and Section 7.4 "Program Memory Modes and the External Memory Bus") impacts both pin multiplexing and the operation of the module.

The ECCP2 input/output (ECCP2/P2A) can be multiplexed to one of three pins. By default, this is RC1 for all devices; in this case, the default is in effect when CCP2MX is set and the device is operating in Microcontroller mode. With PIC18F8527/8622/8627/8722 devices, three other options exist. When CCP2MX is not set (= 0) and the device is in Microcontroller mode, ECCP2/P2A is multiplexed to RE7; in all other program memory modes, it is multiplexed to RB3.

Another option is for ECCPMX to be set while the device is operating in one of the three other program memory modes. In this case, ECCP1 and ECCP3 operate as compatible (i.e., single output) CCP modules. The pins used by their other outputs (PxB through PxD) are available for other multiplexed functions. ECCP2 continues to operate as an Enhanced CCP module regardless of the program memory mode.

The final option is that the ABW<1:0> Configuration bits can be used to select 8, 12, 16 or 20-bit EMB addressing. Pins not assigned to EMB address pins are available for peripheral or port functions.

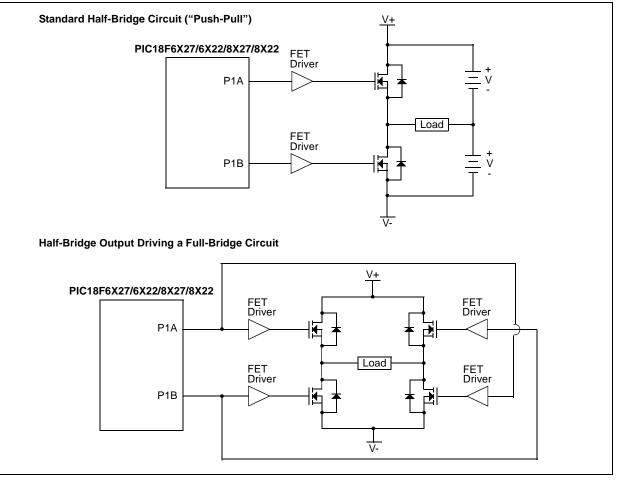

## 18.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 18-4). This mode can be used for half-bridge applications, as shown in Figure 18-5, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

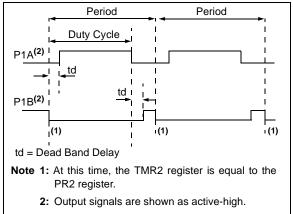

In Half-Bridge Output mode, the programmable dead-band delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, P1DC<6:0> sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 18.4.6** "**Programmable Dead-Band Delay**" for more details on dead-band delay operations.

The P1A and P1B outputs are multiplexed with the PORTC<2> and PORTE<6> data latches. Alternatively, P1B can be assigned to PORTH<7> by programming the ECCPMX Configuration bit to '0'. See Table 18-1, Table 18-2 and Table 18-3 for more information. The associated TRIS bit must be cleared to configure P1A and P1B as outputs.

FIGURE 18-4: HALF-BRIDGE PWM OUTPUT

### FIGURE 18-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

## 19.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPxCON1)

- MSSP Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

## REGISTER 19-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| R/W-0         | R/W-0                    | R-0                                                               | R-0             | R-0              | R-0             | R-0             | R-0         |  |  |  |

|---------------|--------------------------|-------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------------|--|--|--|

| SMP           | CKE                      | D/A                                                               | Р               | S                | R/W             | UA              | BF          |  |  |  |

| bit 7         |                          |                                                                   |                 |                  |                 |                 | bit (       |  |  |  |

|               |                          |                                                                   |                 |                  |                 |                 |             |  |  |  |

| Legend:       |                          |                                                                   |                 |                  |                 |                 |             |  |  |  |

| R = Readable  | e bit                    | W = Writable                                                      | bit             | U = Unimpler     | mented bit, rea | d as '0'        |             |  |  |  |

| -n = Value at | POR                      | '1' = Bit is set                                                  |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown        |  |  |  |

|               |                          |                                                                   |                 |                  |                 |                 |             |  |  |  |

| bit 7         | SMP: Sampl               |                                                                   |                 |                  |                 |                 |             |  |  |  |

|               | SPI Master r             |                                                                   |                 | in the second    |                 |                 |             |  |  |  |

|               |                          | ta sampled at er<br>ta sampled at m                               |                 |                  |                 |                 |             |  |  |  |

|               | <u>SPI Slave m</u>       | -                                                                 |                 | output time      |                 |                 |             |  |  |  |

|               |                          | e cleared when                                                    | SPI is used i   | n Slave mode.    |                 |                 |             |  |  |  |

| bit 6         | CKE: SPI CI              | ock Select bit                                                    |                 |                  |                 |                 |             |  |  |  |

|               |                          | 1 = Transmit occurs on transition from active to Idle clock state |                 |                  |                 |                 |             |  |  |  |

|               | 0 = Transmit             | occurs on trans                                                   | sition from Idl | e to active cloc | k state         |                 |             |  |  |  |

|               |                          | Polarity of clock                                                 | state is set by | y the CKP bit (S | SSPxCON1<4>     | ·).             |             |  |  |  |

| bit 5         | D/A: Data/A              | ddress bit                                                        |                 |                  |                 |                 |             |  |  |  |

|               | Used in I <sup>2</sup> C | mode only.                                                        |                 |                  |                 |                 |             |  |  |  |

| bit 4         | P: Stop bit              |                                                                   |                 |                  |                 |                 |             |  |  |  |

|               | Used in I <sup>2</sup> C | mode only. This                                                   | bit is cleared  | when the MSS     | SP module is di | sabled, SSPEN   | is cleared. |  |  |  |

| bit 3         | S: Start bit             |                                                                   |                 |                  |                 |                 |             |  |  |  |

|               | Used in I <sup>2</sup> C | -                                                                 |                 |                  |                 |                 |             |  |  |  |

| bit 2         |                          | Write Information                                                 | n bit           |                  |                 |                 |             |  |  |  |

|               | Used in I <sup>2</sup> C | mode only.                                                        |                 |                  |                 |                 |             |  |  |  |

| bit 1         | UA: Update               |                                                                   |                 |                  |                 |                 |             |  |  |  |

|               | Used in I <sup>2</sup> C | ,                                                                 |                 |                  |                 |                 |             |  |  |  |

| bit 0         |                          | ull Status bit (Re                                                |                 | only)            |                 |                 |             |  |  |  |

|               |                          | complete, SSP>                                                    |                 |                  |                 |                 |             |  |  |  |

|               | 0 = Receive              | not complete, S                                                   | SPXBUF is e     | mpty             |                 |                 |             |  |  |  |

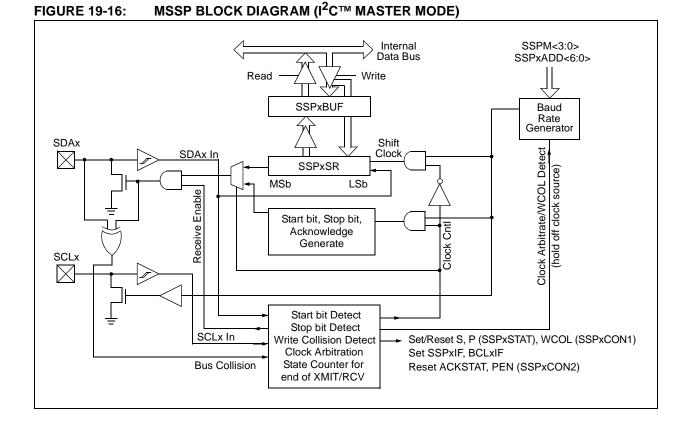

## 19.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPxCON1 and by setting the SSPEN bit. In Master mode, the SCLx and SDAx lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\rm I}^2{\rm C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Assert a Repeated Start condition on SDAx and SCLx.

- 3. Write to the SSPxBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDAx and SCLx.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (and SSP interrupt, if enabled):

- Start condition

- · Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

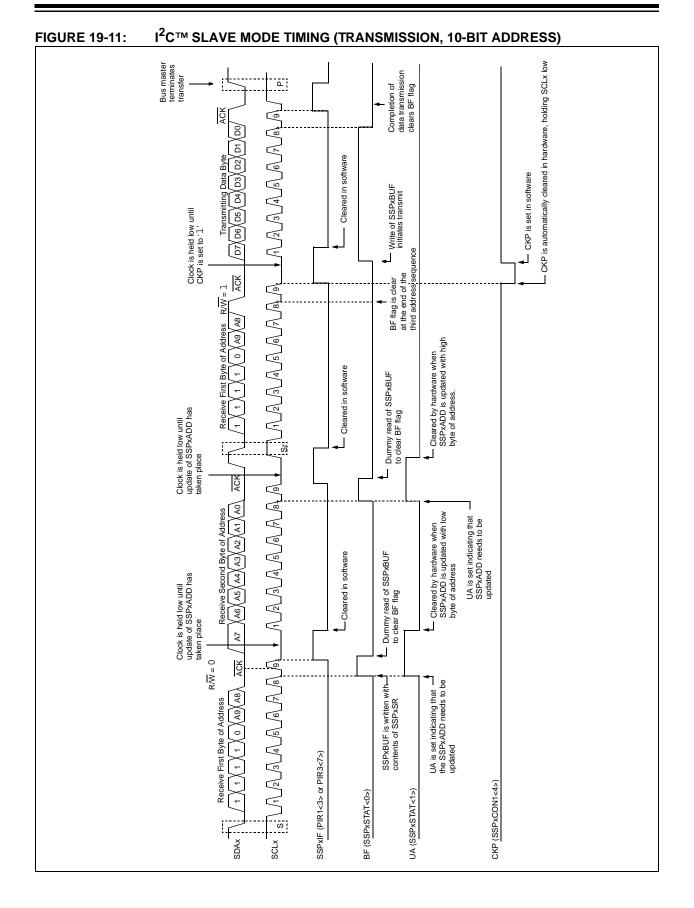

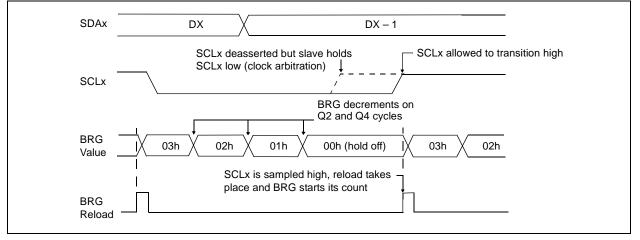

#### 19.4.7.2 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the

SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 19-18).

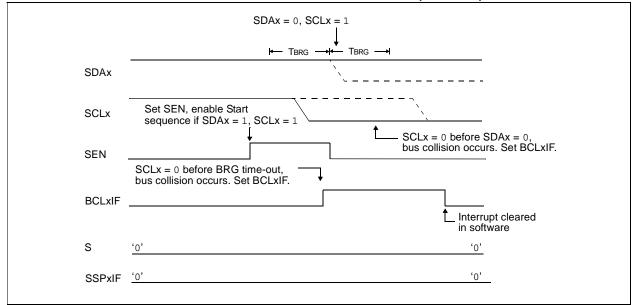

### FIGURE 19-27: BUS COLLISION DURING START CONDITION (SCLx = 0)

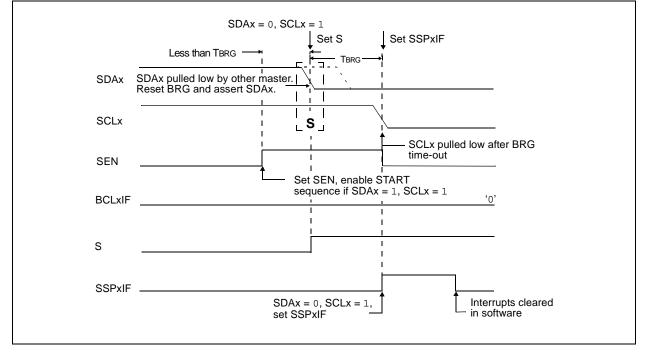

### FIGURE 19-28: BRG RESET DUE TO SDAX ARBITRATION DURING START CONDITION

| BRG Value                | XXXXh                    | 0000h                                            | XXXXXXXXXXXXXXX001Ch                                                                                               |

|--------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| RXx pin                  |                          | Edge #1 Edge #2<br>Start Bit 0 Bit 1 Bit 2 Bit 3 | Edge #3         Edge #4         Edge #5           Bit 4         Bit 5         Bit 6         Bit 7         Stop Bit |

| BRG Clock                | ົມທານທານສາມທານສາມທານກໍ່າ | www.iwwwwwwww                                    |                                                                                                                    |

| ABDEN bit                | Set by User —            |                                                  | Auto-Cleared                                                                                                       |

| RCxIF bit<br>(Interrupt) |                          |                                                  |                                                                                                                    |

| Read<br>RCREGx           |                          |                                                  |                                                                                                                    |

| SPBRGx                   |                          | XXXXh                                            | X 1Ch                                                                                                              |

| SPBRGHx                  |                          | XXXXh                                            | ∑ 00h                                                                                                              |

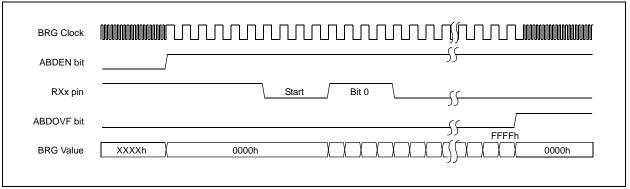

## FIGURE 20-2: BRG OVERFLOW SEQUENCE

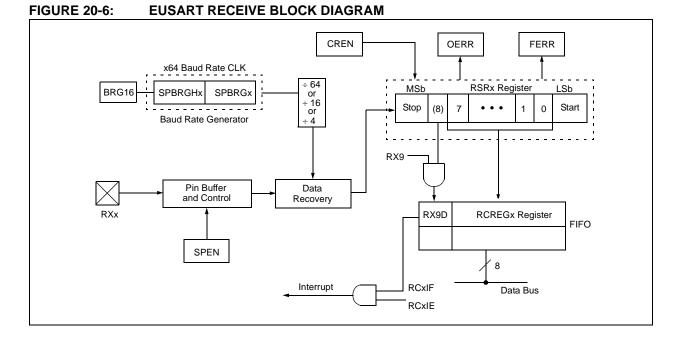

### 20.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 20-6. The data is received on the RXx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCxIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- Flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 20.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If interrupts are required, set the RCEN bit and select the desired priority level with the RCxIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

| R/P-1           | R/P-0                                                                                                    | R/P-0                                                                                                                                                                                                                                                                                                                                                              | R/P-0          | U-0              | R/P-1                               | U-0             | R/P-1  |  |

|-----------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-------------------------------------|-----------------|--------|--|

| DEBUG           | XINST                                                                                                    | BBSIZ1                                                                                                                                                                                                                                                                                                                                                             | BBSIZ0         | —                | LVP                                 | —               | STVREN |  |

| bit 7           |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                    | ·              |                  | •                                   |                 | bit 0  |  |

| Legend:         |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                    |                |                  |                                     |                 |        |  |

| R = Readable    | bit                                                                                                      | W = Writable                                                                                                                                                                                                                                                                                                                                                       | bit            | U = Unimpler     | mented bit, read                    | as '0'          |        |  |

| -n = Value at I | POR                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                   |                | '0' = Bit is cle | ared                                | x = Bit is unkr | nown   |  |

| bit 7           | 1 = Backgrou                                                                                             | 00                                                                                                                                                                                                                                                                                                                                                                 | isabled, RB6 a | and RB7 config   | gured as genera<br>edicated to In-C |                 | pins   |  |

| bit 6           | 1 = Instruction                                                                                          |                                                                                                                                                                                                                                                                                                                                                                    | and Indexed    | Addressing mo    |                                     | egacy mode)     |        |  |

| bit 5-4         | 11 = 4K word<br>10 = 4K word<br>01 = 2K word                                                             | <ul> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> <li>BBSIZ&lt;1:0&gt;: Boot Block Size Select bits</li> <li>11 = 4K words (8 Kbytes) boot block size</li> <li>10 = 4K words (8 Kbytes) boot block size</li> <li>01 = 2K words (4 Kbytes) boot block size</li> <li>00 = 1K word (2 Kbytes) boot block size</li> </ul> |                |                  |                                     |                 |        |  |

| bit 3           | Unimplemen                                                                                               | ted: Read as '                                                                                                                                                                                                                                                                                                                                                     | 0'             |                  |                                     |                 |        |  |

| bit 2           | LVP: Single-Supply ICSP™ Enable bit<br>1 = Single-Supply ICSP enabled<br>0 = Single-Supply ICSP disabled |                                                                                                                                                                                                                                                                                                                                                                    |                |                  |                                     |                 |        |  |

| bit 1           | Unimplemen                                                                                               | ted: Read as '                                                                                                                                                                                                                                                                                                                                                     | 0'             |                  |                                     |                 |        |  |

| bit 0           | 1 = Stack full/                                                                                          | ck Full/Underfl<br>underflow will<br>underflow will                                                                                                                                                                                                                                                                                                                | cause Reset    |                  |                                     |                 |        |  |

## REGISTER 25-6: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| DAW                   | Decimal A                        | djust W Regis                      | ster       | DECF                  | Decremen                 | t f                                 |                 |

|-----------------------|----------------------------------|------------------------------------|------------|-----------------------|--------------------------|-------------------------------------|-----------------|

| Syntax:               | DAW                              |                                    |            | Syntax:               | DECF f{,                 | d {,a}}                             |                 |

| Operands:             | None                             |                                    |            | Operands:             | $0 \leq f \leq 255$      |                                     |                 |

| Operation:            | If [W<3:0> > 9] or [DC = 1] then |                                    |            |                       | d ∈ [0,1]                |                                     |                 |

|                       | $(W<3:0>)+6\rightarrowW<3:0>;$   |                                    |            | On another            | a ∈ [0,1]                |                                     |                 |

|                       | else<br>(W<3:0>) –               | → W<3:0>                           |            | Operation:            | $(f) - 1 \rightarrow de$ |                                     |                 |

|                       | (11 10107)                       |                                    |            | Status Affected:      | C, DC, N, (              |                                     |                 |

|                       |                                  | > 9] or [C = 1]                    |            | Encoding:             | 0000                     |                                     | ff fff          |

|                       | (VV<7:4>) +<br>C = 1;            | $6 \rightarrow W < 7:4>;$          |            | Description:          |                          | register 'f'. If<br>red in W. If 'd |                 |

|                       | else                             |                                    |            |                       |                          | red back in re                      | ,               |

|                       | (W<7:4>) –                       | → W<7:4>                           |            |                       | (default).               |                                     | 0               |

| Status Affected:      | С                                |                                    |            |                       |                          | he Access Ba                        |                 |

| Encoding:             | 0000                             | 0000 000                           | 00 0111    |                       |                          | he BSR is use                       | ed to select th |

| Description:          | •                                | ts the eight-bit                   |            |                       | GPR bank                 |                                     | lad in atruatio |

|                       | •                                | om the earlier a<br>each in packed |            |                       |                          | nd the extend<br>led, this instru   |                 |

|                       |                                  | es a correct pa                    |            |                       | in Indexed               | Literal Offset                      | Addressing      |

|                       | result.                          |                                    |            |                       |                          | hever $f \le 95$ (5                 | ,               |

| Words:                | 1                                |                                    |            |                       |                          | .2.3 "Byte-Or<br>d Instruction      |                 |

| Cycles:               | 1                                |                                    |            |                       | Literal Off              | set Mode" for                       | details.        |

| Q Cycle Activity:     |                                  |                                    |            | Words:                | 1                        |                                     |                 |

| Q1                    | Q2                               | Q3                                 | Q4         | Cycles:               | 1                        |                                     |                 |

| Decode                | Read<br>register W               | Process<br>Data                    | Write<br>W | Q Cycle Activity:     |                          |                                     |                 |

|                       | legister w                       | Dala                               | ~~~        | Q1                    | Q2                       | Q3                                  | Q4              |

| Example 1:            | DAW                              |                                    |            | Decode                | Read                     | Process                             | Write to        |

| Before Instruc        | tion                             |                                    |            |                       | register 'f'             | Data                                | destination     |

| W<br>C                | = A5h<br>= 0                     |                                    |            | Example:              | DECF                     | CNT, 1, 0                           | h               |

| DC                    | = 0                              |                                    |            | Before Instru         |                          | CN1, 1, C                           | )               |

| After Instruction     |                                  |                                    |            | CNT                   | = 01h                    |                                     |                 |

| W<br>C                | = 05h<br>= 1                     |                                    |            | Z                     | = 0                      |                                     |                 |

| DC                    | = 0                              |                                    |            | After Instruct<br>CNT | = 00h                    |                                     |                 |

| Example 2:            |                                  |                                    |            | Z                     | = 1                      |                                     |                 |

| Before Instruc        |                                  |                                    |            |                       |                          |                                     |                 |

| W<br>C                | = CEh<br>= 0                     |                                    |            |                       |                          |                                     |                 |

| DC                    | = 0                              |                                    |            |                       |                          |                                     |                 |

| After Instructio<br>W | on<br>= 34h                      |                                    |            |                       |                          |                                     |                 |

| ••                    | = 1                              |                                    |            |                       |                          |                                     |                 |

| C<br>DC               | = 0                              |                                    |            |                       |                          |                                     |                 |

| RLNCF             | Rotate Left f (no carry)                                                                                                                                                                  | RRCF              | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:           | RLNCF f {,d {,a}}                                                                                                                                                                         | Syntax:           | RRCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                        | Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Operation:        | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                             | Operation:        | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow C,$<br>$(C) \rightarrow dest < 7 >$                                                                                                                                                                                                                                                                                                   |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                      | Status Affected:  |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Encoding:         | 0100 01da ffff ffff                                                                                                                                                                       |                   | C, N, Z                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Description:      | The contents of register 'f' are rotated                                                                                                                                                  | Encoding:         | 0011 00da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                   | one bit to the left. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.   | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in W.<br>If 'd' is '1', the result is placed back in                                                                                                                                                                                                                    |  |  |

|                   | If 'a' is '1', the BSR is used to select the                                                                                                                                              |                   | register 'f' (default).                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                   | GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates                                                                            |                   | If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select th<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |  |  |

|                   | in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                   |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Words:            | 1                                                                                                                                                                                         |                   | C→ register f                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Cycles:           | 1                                                                                                                                                                                         |                   |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Q Cycle Activity: |                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Q Cycle Activity. | Q2 Q3 Q4                                                                                                                                                                                  | Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Decode            | Read Process Write to                                                                                                                                                                     | Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Dooddo            | register 'f' Data destination                                                                                                                                                             | Q1                | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                   |                                                                                                                                                                                           | Decode            | Read Process Write to                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Example:          | RLNCF REG, 1, 0                                                                                                                                                                           |                   | register 'f' Data destination                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Before Instru     | ction                                                                                                                                                                                     |                   |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| REG               | = 1010 1011                                                                                                                                                                               | Example:          | RRCF REG, 0, 0                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| After Instruct    | ion                                                                                                                                                                                       | Before Instruc    | ction                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| REG               | = 0101 0111                                                                                                                                                                               | REG<br>C          | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                   |                                                                                                                                                                                           | After Instruction | on                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                   |                                                                                                                                                                                           | REG<br>W<br>C     | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TSTR        | SZ                                                   | Test f, Skip                                                                                                                                                                                                                                                                         | if O                                                                                                                                                                  |                 |  |  |  |

|-------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|