Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8722-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 64/80-Pin, 1-Mbit, Enhanced Flash Microcontrollers with 10-Bit A/D and nanoWatt Technology

#### **Power Management Features:**

- Run: CPU On, Peripherals On

- Idle: CPU Off, Peripherals On

- Sleep: CPU Off, Peripherals Off

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 25  $\mu\text{A}$  Typical

- Idle mode Currents Down to 6.8 µA Typical

- Sleep mode Current Down to 120 nA Typical

- Timer1 Oscillator: 900 nA, 32 kHz, 2V

- Watchdog Timer: 1.6 μA, 2V Typical

- Two-Speed Oscillator Start-up

#### Flexible Oscillator Structure:

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) Available for Crystal and Internal Oscillators

- Internal Oscillator Block:

- Fast wake from Sleep and Idle, 1  $\mu s$  typical

- Provides a complete range of clock speeds

- from 31 kHz to 32 MHz when used with PLL

- User-tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three Programmable External Interrupts

- Four Input Change Interrupts

- Enhanced Capture/Compare/PWM (ECCP) module (40/44-pin devices only):

- One, two or four PWM outputs

- Programmable dead time

- Auto-shutdown and auto-restart

### **Peripheral Highlights (Continued):**

- Up to 2 Capture/Compare/PWM (CCP) modules, one with Auto-Shutdown (28-pin devices)

- Master Synchronous Serial Port (MSSP) module Supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- RS-232 operation using internal oscillator block (no external crystal required)

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

- Programmable 16-Level High/Low-Voltage Detection (HLVD) module

#### **Special Microcontroller Features:**

- C Compiler Optimized Architecture

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

- Flash/Data EEPROM Retention: 100 Years Typical

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

- Programmable Brown-out Reset (BOR) with Software Enable Option

|            | Prog             | ram Memory                    | Data            | Memory            |     | 10-Bit      | CCP/          |   | MSSP |                             | E     | tors        | it s               | Bus      |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|-------------|---------------|---|------|-----------------------------|-------|-------------|--------------------|----------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D<br>(ch) | ECCP<br>(PWM) |   | SPI  | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External |

| PIC18F6527 | 48K              | 24576                         | 3936            | 1024              | 54  | 12          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6622 | 64K              | 32768                         | 3936            | 1024              | 54  | 12          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6627 | 96K              | 49152                         | 3936            | 1024              | 54  | 12          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6722 | 128K             | 65536                         | 3936            | 1024              | 54  | 12          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F8527 | 48K              | 24576                         | 3936            | 1024              | 70  | 16          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8622 | 64K              | 32768                         | 3936            | 1024              | 70  | 16          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8627 | 96K              | 49152                         | 3936            | 1024              | 70  | 16          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8722 | 128K             | 65536                         | 3936            | 1024              | 70  | 16          | 2/3           | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| Pin Name                             | Pin Number                          | Pin              | Buffer           | Description                                                                                                      |

|--------------------------------------|-------------------------------------|------------------|------------------|------------------------------------------------------------------------------------------------------------------|

| Pin Name                             | TQFP                                | Туре             | Туре             | Description                                                                                                      |

|                                      |                                     |                  |                  | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |

| RB0/INT0/FLT0<br>RB0<br>INT0<br>FLT0 | 48                                  | I/O<br>I<br>I    | TTL<br>ST<br>ST  | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for ECCPx.                                              |

| RB1/INT1<br>RB1<br>INT1              | 47                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 1.                                                                            |

| RB2/INT2<br>RB2<br>INT2              | 46                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 2.                                                                            |

| RB3/INT3<br>RB3<br>INT3              | 45                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 3.                                                                            |

| RB4/KBI0<br>RB4<br>KBI0              | 44                                  | I/O<br>I         | TTL<br>TTL       | Digital I/O.<br>Interrupt-on-change pin.                                                                         |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM   | 43                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                            |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC   | 42                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD   | 37                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |

|                                      | ompatible input<br>tt Trigger input | CMOS<br>with CMO |                  | <ul> <li>CMOS compatible input or output</li> <li>Analog = Analog input</li> </ul>                               |

| I = Input                            |                                     |                  |                  | = Output                                                                                                         |

| TABLE 1-3: | PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED) | • |

|------------|---------------------------------------------------------------|---|

| IADLL I-J. | FIGIOLOJZI/0022/0021/0122 FINOUT I/O DESCRIFTIONS (CONTINUED) | , |

P = Power  $I^2 C^{TM} = I^2 C/SMBus input buffer$

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Register            | Register Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |           |

|---------------------|-----------------------------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|-----------|

| FSR1H               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000                            | 0000      | uuuu      |

| FSR1L               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| BSR                 | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000                            | 0000      | uuuu      |

| INDF2               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | N/A                             | N/A       | N/A       |

| POSTINC2            | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | N/A                             | N/A       | N/A       |

| POSTDEC2            | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | N/A                             | N/A       | N/A       |

| PREINC2             | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | N/A                             | N/A       | N/A       |

| PLUSW2              | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | N/A                             | N/A       | N/A       |

| FSR2H               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000                            | 0000      | uuuu      |

| FSR2L               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| STATUS              | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | x xxxx                          | u uuuu    | u uuuu    |

| TMR0H               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| TMR0L               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| TOCON               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 1111 1111                       | 1111 1111 | uuuu uuuu |

| OSCCON              | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0100 q000                       | 0100 q000 | uuuu uuqu |

| HLVDCON             | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0-00 0101                       | 0-00 0101 | u-uu uuuu |

| WDTCON              | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0                               | 0         | u         |

| RCON <sup>(4)</sup> | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0q-1 11q0                       | 0q-q qquu | uq-u qquu |

| TMR1H               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| TMR1L               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| T1CON               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | u0uu uuuu | uuuu uuuu |

| TMR2                | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| PR2                 | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 1111 1111                       | uuuu uuuu | uuuu uuuu |

| T2CON               | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | -000 0000                       | -000 0000 | -uuu uuuu |

| SSP1BUF             | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| SSP1ADD             | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SSP1STAT            | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SSP1CON1            | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SSP1CON2            | 6X27                        | 6X22 | 8X27                               | 8X22                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend:u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

#### 5.1.5.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

#### 5.2 PIC18 Instruction Cycle

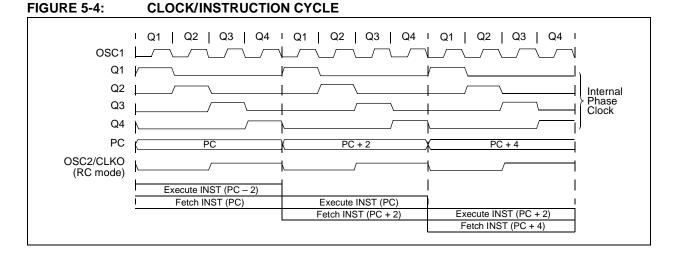

#### 5.2.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-4.

#### 5.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

| _                        | Тсү0       | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|--------------------------|------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h             | Fetch 1    | Execute 1 |           |           |             |               |

| 2. MOVWF PORTB           |            | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA SUB_1             |            |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (Fo   | orced NOP) |           |           | Fetch 4   | Flush (NOP) |               |

| 5. Instruction @ address | s SUB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### REGISTER 6-1: EECON1: EEPROM CONTROL REGISTER 1

| R/W-x      | R/W-x                                 | U-0                                | R/W-0                     | R/W-x                                                               | R/W-0           | R/S-0                            | R/S-0         |

|------------|---------------------------------------|------------------------------------|---------------------------|---------------------------------------------------------------------|-----------------|----------------------------------|---------------|

| EEPGD      | CFGS                                  | —                                  | FREE                      | WRERR <sup>(1)</sup>                                                | WREN            | WR                               | RD            |

| bit 7      |                                       |                                    |                           | ·                                                                   |                 |                                  | bit (         |

| Legend:    |                                       |                                    |                           |                                                                     |                 |                                  |               |

| R = Reada  | ble bit                               | W = Writable                       | bit                       | U = Unimplem                                                        | ented bit, rea  | d as '0'                         |               |

| -n = Value | at POR                                | '1' = Bit is se                    | t                         | '0' = Bit is clea                                                   |                 | x = Bit is unkr                  | nown          |

| bit 7      | FFPGD: Flas                           | h Program or                       | Data EEPRO                | M Memory Selec                                                      | t bit           |                                  |               |

|            | 1 = Access F                          | Flash program<br>data EEPROM       | memory                    |                                                                     |                 |                                  |               |

| bit 6      | CFGS: Flash                           | Program/Data                       | EEPROM or                 | Configuration S                                                     | elect bit       |                                  |               |

|            |                                       | Configuration re                   | •                         |                                                                     |                 |                                  |               |

| bit 5      |                                       | ited: Read as                      |                           | Colvi memory                                                        |                 |                                  |               |

| bit 4      | -                                     | Row Erase Er                       |                           |                                                                     |                 |                                  |               |

|            | 1 = Erase the (cleared                | e program mer<br>by completion     | mory row add              | ressed by TBLP <sup>-</sup><br>ration)                              | TR on the nex   | t WR command                     | I             |

| L:4 0      | 0 = Perform                           | •                                  |                           |                                                                     |                 |                                  |               |

| bit 3      |                                       |                                    |                           | Error Flag bit <sup>(1)</sup><br>hinated (any Res                   | et during self. | timed program                    | nina in norma |

|            |                                       | n, or an improp                    | •                         | · •                                                                 | ot during son   | unica program                    |               |

|            | 0 = The write                         | e operation cor                    | npleted                   |                                                                     |                 |                                  |               |

| bit 2      |                                       | •                                  |                           | Vrite Enable bit                                                    |                 |                                  |               |

|            |                                       | •                                  |                           | /data EEPROM<br>n/data EEPROM                                       |                 |                                  |               |

| bit 1      | WR: Write Co                          | -                                  | lash progran              |                                                                     |                 |                                  |               |

|            | 1 = Initiates a<br>(The ope<br>The WR | a data EEPRO<br>eration is self-ti | med and the set (not clea | cycle or a progra<br>bit is cleared by<br>red) in software.<br>lete | hardware onc    |                                  |               |

| bit 0      | RD: Read Co                           | ontrol bit                         |                           |                                                                     |                 |                                  |               |

|            |                                       |                                    |                           | es one cycle. RD                                                    |                 | nardware. The F<br>= 1 or CFGS = |               |

This allows tracing of the error condition.

| R/W-x         | R/W-x                                                                                                                                                                                                              | U-0                                                                                                                                                                        | R/W-0         | R/W-x                         | R/W-0           | R/S-0             | R/S-0          |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|-----------------|-------------------|----------------|--|--|--|

| EEPGD         | CFGS                                                                                                                                                                                                               |                                                                                                                                                                            | FREE          | WRERR <sup>(1)</sup>          | WREN            | WR                | RD             |  |  |  |

| bit 7         | •                                                                                                                                                                                                                  |                                                                                                                                                                            |               | · ·                           |                 |                   | bit            |  |  |  |

| Legend:       |                                                                                                                                                                                                                    |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                              | W = Writable                                                                                                                                                               | bit           | U = Unimplen                  | nented bit, rea | d as '0'          |                |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                | '1' = Bit is se                                                                                                                                                            | t             | '0' = Bit is clea             | ared            | x = Bit is unkr   | nown           |  |  |  |

| hit 7         |                                                                                                                                                                                                                    | ach Dragram ar                                                                                                                                                             |               | A Mamany Sala                 | at bit          |                   |                |  |  |  |

| bit 7         |                                                                                                                                                                                                                    | ash Program or<br>Flash program r                                                                                                                                          |               | vi Memory Sele                | CEDIE           |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | data EEPROM                                                                                                                                                                | •             |                               |                 |                   |                |  |  |  |

| bit 6         |                                                                                                                                                                                                                    | h Program/Data                                                                                                                                                             | -             | Configuration S               | Select bit      |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | Configuration re                                                                                                                                                           |               | C                             |                 |                   |                |  |  |  |

|               | 0 = Access                                                                                                                                                                                                         | Flash program of                                                                                                                                                           | or data EEPR  | OM memory                     |                 |                   |                |  |  |  |

| bit 5         | Unimpleme                                                                                                                                                                                                          | ented: Read as                                                                                                                                                             | 0'            |                               |                 |                   |                |  |  |  |

| bit 4         | FREE: Flash Row Erase Enable bit                                                                                                                                                                                   |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared b<br/>completion of erase operation)</li> </ul>                                                                      |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               | 0 = Perforn                                                                                                                                                                                                        |                                                                                                                                                                            | eration)      |                               |                 |                   |                |  |  |  |

| bit 3         |                                                                                                                                                                                                                    | •                                                                                                                                                                          | ata EEPROM    | Error Flag bit <sup>(1)</sup> |                 |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | <b>WRERR:</b> Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup><br>1 = A write operation is prematurely terminated (any Reset during self-timed programming in norma |               |                               |                 |                   |                |  |  |  |

|               | operation, or an improper write attempt)                                                                                                                                                                           |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               | 0 = The wr                                                                                                                                                                                                         | ite operation cor                                                                                                                                                          | npleted       |                               |                 |                   |                |  |  |  |

| bit 2         |                                                                                                                                                                                                                    | sh Program/Data                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | write cycles to F<br>write cycles to I                                                                                                                                     |               |                               |                 |                   |                |  |  |  |

| bit 1         | WR: Write (                                                                                                                                                                                                        | -                                                                                                                                                                          | lash piografi |                               | I               |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    |                                                                                                                                                                            | M erase/write | cycle or a progr              | am memory er    | ase cycle or writ | e cvcle        |  |  |  |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle.</li> <li>(The operation is self-timed and the bit is cleared by hardware once write is complete.</li> </ul> |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               | The WR bit can only be set (not cleared) in software.)                                                                                                                                                             |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | ycle to the EEPF                                                                                                                                                           | ROM is compl  | ete                           |                 |                   |                |  |  |  |

| bit 0         | RD: Read C                                                                                                                                                                                                         |                                                                                                                                                                            |               |                               |                 |                   |                |  |  |  |

|               |                                                                                                                                                                                                                    | s an EEPROM re<br>takes one cycle.                                                                                                                                         |               | d in hardware                 | The RD hit ca   | in only be set (i | not cleared) i |  |  |  |

|               |                                                                                                                                                                                                                    | e. RD bit cannot                                                                                                                                                           |               |                               |                 |                   |                |  |  |  |

|               | 0 = Does n                                                                                                                                                                                                         |                                                                                                                                                                            |               |                               | ,               |                   |                |  |  |  |

#### REGISTER 8-1: EECON1: DATA EEPROM CONTROL REGISTER 1

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

### **10.0 INTERRUPTS**

The PIC18F8722 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a highpriority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

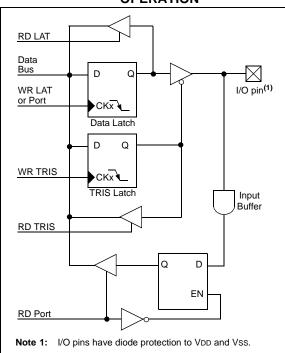

### 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to nine ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- Port register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

# 11.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 25.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with the analog VREF+ and VREF- inputs. The operation of pins RA5:RA0 as A/D converter inputs is selected by clearing or setting the PCFG<3:0> control bits in the ADCON1 register.

| Note: | On a Power-on Reset, RA5 and RA<3:0>          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMPLE 11-1: | INITIALIZING PORTA |

|---------------|--------------------|

|               |                    |

| CLRF  | PORTA  | ; Initialize PORTA by   |

|-------|--------|-------------------------|

|       |        | ; clearing output       |

|       |        | ; data latches          |

| CLRF  | LATA   | ; Alternate method      |

|       |        | ; to clear output       |

|       |        | ; data latches          |

| MOVLW | 0Fh    | ; Configure A/D         |

| MOVWF | ADCON1 | ; for digital inputs    |

| MOVLW | 0CFh   | ; Value used to         |

|       |        | ; initialize data       |

|       |        | ; direction             |

| MOVWF | TRISA  | ; Set RA<3:0> as inputs |

|       |        | ; RA<5:4> as outputs    |

|       |        | -                       |

| Pin Name       | Function | TRIS<br>Setting | I/O | I/О<br>Туре | Description                                                                              |

|----------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------|

| RA0/AN0        | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                       |

|                |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                 |

|                | AN0      | 1               | Ι   | ANA         | A/D input channel 0. Default input configuration on POR; does not affect digital output. |

| RA1/AN1        | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                 |

|                | AN1      | 1               | I   | ANA         | A/D input channel 1. Default input configuration on POR; does not affect digital output. |

| RA2/AN2/VREF-  | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled.                             |

|                | AN2      | 1               | Ι   | ANA         | A/D input channel 2. Default input configuration on POR.                                 |

|                | VREF-    | 1               | Ι   | ANA         | Comparator voltage reference low input and A/D voltage reference low input               |

| RA3/AN3/VREF+  | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                 |

|                | AN3      | 1               | Ι   | ANA         | A/D input channel 3. Default input configuration on POR.                                 |

|                | Vref+    | 1               | I   | ANA         | Comparator voltage reference high input and A/D voltage reference high input.            |

| RA4/T0CKI      | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                     |

|                |          | 1               | Ι   | ST          | PORTA<4> data input; default configuration on POR.                                       |

|                | T0CKI    | х               | Ι   | ST          | Timer0 clock input.                                                                      |

| RA5/AN4/HLVDIN | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                       |

|                |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                 |

|                | AN4      | 1               | Ι   | ANA         | A/D input channel 4. Default configuration on POR.                                       |

|                | HLVDIN   | 1               | I   | ANA         | High/Low-Voltage Detect external trip point input.                                       |

| OSC2/CLKO/RA6  | OSC2     | х               | 0   | ANA         | Main oscillator feedback output connection (XT, HS, HSPLL and LP modes)                  |

|                | CLKO     | x               | 0   | DIG         | System cycle clock output (Fosc/4) in all oscillator modes except RC, INTIO7 and EC.     |

|                | RA6      | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                        |

|                |          | 1               | Ι   | TTL         | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                        |

| OSC1/CLKI/RA7  | OSC1     | х               | I   | ANA         | Main oscillator input connection.                                                        |

|                | CLKI     | x               | Ι   | ANA         | Main clock input connection.                                                             |

|                | RA7      | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                              |

|                |          | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                              |

### TABLE 11-1:PORTA FUNCTIONS

Legend:PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST= Schmitt Buffer Input,<br/>TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 11-2: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name   | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 61                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 60                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 60                         |

| ADCON1 | _                     | —                     | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 59                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

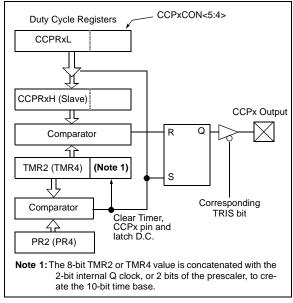

#### 17.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP4 and CCP5 pins are multiplexed with a PORTG data latch, the appropriate TRISG bit must be cleared to make the CCP4 or CCP5 pin an output.

| Note: | Clearing the CCP4CON or CCP5CON register will force the RG3 or RG4 output latch (depending on device configuration) |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       | to the default low level. This is not the PORTG I/O data latch.                                                     |

Figure 17-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up a CCP module for PWM operation, see **Section 17.4.3** "Setup for PWM Operation".

#### FIGURE 17-4: SIMPLIFIED PWM BLOCK DIAGRAM

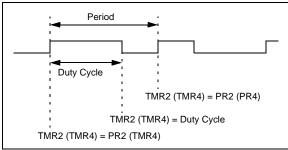

A PWM output (Figure 17-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 17-5: PWM OUTPUT

#### 17.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 (PR4) register. The PWM period can be calculated using the following formula:

#### EQUATION 17-1:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 (TMR4) is equal to PR2 (PR4), the following three events occur on the next increment cycle:

- TMR2 (TMR4) is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

- Note: The Timer2 and Timer 4 postscalers (see Section 14.0 "Timer2 Module" and Section 16.0 "Timer4 Module") are not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 17.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> contains the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 17-2:**

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPRxH until after a match between PR2 (PR4) and TMR2 (TMR4) occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

#### 18.4.6 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 18-4 for illustration. The lower seven bits of the ECCP1DEL register (Register 18-2) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### 18.4.7 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the two comparator modules or the FLT0 pin (or any combination of these three sources). The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a digital signal on the FLT0 pin can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCP1AS<2:0> bits (ECCP1AS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSS1AC<1:0> and PSS1BD<1:0> bits (ECCP1AS<3:0>). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCP1ASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCP1ASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCP1ASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCP1ASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCP1ASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCP1ASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCP1ASE bit is disabled while a shutdown condition is active.

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| PxRSEN | PxDC6 | PxDC5 | PxDC4 | PxDC3 | PxDC2 | PxDC1 | PxDC0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

### REGISTER 18-2: ECCPxDEL: ENHANCED PWM DEAD-BAND DELAY REGISTER

|                        |                        |                  | Legend:           |

|------------------------|------------------------|------------------|-------------------|

| read as '0'            | U = Unimplemented bit, | W = Writable bit | R = Readable bit  |

| x = Bit is unknown     | '0' = Bit is cleared   | '1' = Bit is set | -n = Value at POR |

| <br>x = Bit is unknown | '0' = Bit is cleared   | '1' = Bit is set | -n = Value at POR |

| bit 7   | PxRSEN: PWM Restart Enable bit                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Upon auto-shutdown, the ECCPxASE bit clears automatically once the shutdown event goes<br>away; the PWM restarts automatically |

|         | 0 = Upon auto-shutdown, the ECCPxASE bit must be cleared in software to restart the PWM                                            |

| bit 6-0 | PxDC<6:0>: PWM Delay Count bits                                                                                                    |

|         | Delay time, in number of Fosc/4 (4 * Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active. |

| R/W-0        | R/W-0                                                                                   | R/W-0                                                                                                                | R/W-0                | R/W-0                    | R/W-0                   | R/W-0               | R/W-0              |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|-------------------------|---------------------|--------------------|--|--|--|--|

| GCEN         | ACKSTAT                                                                                 | ACKDT <sup>(1)</sup>                                                                                                 | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>      | PEN <sup>(2)</sup>      | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |  |  |  |  |

| bit 7        |                                                                                         |                                                                                                                      |                      |                          |                         |                     | bit                |  |  |  |  |

| Legend:      |                                                                                         |                                                                                                                      |                      |                          |                         |                     |                    |  |  |  |  |

| R = Readab   | le bit                                                                                  | W = Writable                                                                                                         | bit                  | U = Unimplen             | nented bit, rea         | d as '0'            |                    |  |  |  |  |

| -n = Value a |                                                                                         | '1' = Bit is set                                                                                                     |                      | '0' = Bit is cle         |                         | x = Bit is unkn     | own                |  |  |  |  |

|              |                                                                                         |                                                                                                                      |                      |                          |                         |                     |                    |  |  |  |  |

| bit 7        | GCEN: Gene                                                                              | ral Call Enable                                                                                                      | bit (Slave mo        | de only)                 |                         |                     |                    |  |  |  |  |

|              |                                                                                         | terrupt when a<br>all address dis                                                                                    |                      | ddress (0000h)           | ) is received in        | the SSPxSR          |                    |  |  |  |  |

| bit 6        | ACKSTAT: A                                                                              | cknowledge Sta                                                                                                       | atus bit (Maste      | er Transmit mo           | de only)                |                     |                    |  |  |  |  |

|              |                                                                                         | dge was not re                                                                                                       |                      |                          |                         |                     |                    |  |  |  |  |

|              |                                                                                         | dge was receiv                                                                                                       |                      |                          | L \(1)                  |                     |                    |  |  |  |  |

| bit 5        | 1 = Not Ackn                                                                            | nowledge Data                                                                                                        | bit (Master Re       | eceive mode or           | niy)'''                 |                     |                    |  |  |  |  |

|              | 1 = Not Acknowle<br>0 = Acknowle                                                        | 0                                                                                                                    |                      |                          |                         |                     |                    |  |  |  |  |

| bit 4        | <b>ACKEN:</b> Acknowledge Sequence Enable bit (Master Receive mode only) <sup>(2)</sup> |                                                                                                                      |                      |                          |                         |                     |                    |  |  |  |  |

|              | Automati                                                                                | cally cleared by                                                                                                     | y hardware.          | SDAx and S               | CLx pins and            | d transmit ACK      | DT data b          |  |  |  |  |

| bit 3        |                                                                                         | <ul> <li>0 = Acknowledge sequence Idle</li> <li>RCEN: Receive Enable bit (Master mode only)<sup>(2)</sup></li> </ul> |                      |                          |                         |                     |                    |  |  |  |  |

|              |                                                                                         | Receive mode                                                                                                         | •                    | ,                        |                         |                     |                    |  |  |  |  |

| bit 2        | PEN: Stop Co                                                                            | ondition Enable                                                                                                      | bit (Master m        | ode only) <sup>(2)</sup> |                         |                     |                    |  |  |  |  |

|              |                                                                                         | op condition or                                                                                                      |                      |                          | matically clear         | ed by hardware.     |                    |  |  |  |  |

| bit 1        | RSEN: Repea                                                                             | ated Start Cond                                                                                                      | dition Enable b      | it (Master mod           | le only) <sup>(2)</sup> |                     |                    |  |  |  |  |

|              |                                                                                         | epeated Start of Start of Start of Start conditio                                                                    |                      | DAx and SCLx             | pins. Automa            | tically cleared by  | hardware.          |  |  |  |  |

| bit 0        | SEN: Start Co                                                                           | ondition Enable                                                                                                      | /Stretch Enab        | le bit <sup>(2)</sup>    |                         |                     |                    |  |  |  |  |

|              | <u>In Master mo</u><br>1 = Initiate St<br>0 = Start cond                                | art condition or                                                                                                     | n SDAx and S         | CLx pins. Auto           | matically clear         | ed by hardware.     |                    |  |  |  |  |

|              |                                                                                         |                                                                                                                      |                      | ave transmit ar          | nd slave receiv         | e (stretch enable   | ed)                |  |  |  |  |

|              | alue that will be t                                                                     |                                                                                                                      |                      | -                        |                         |                     |                    |  |  |  |  |

### REGISTER 19-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

For bits ACKEN, RCEN, PEN, RSEN, SEN: If the l<sup>2</sup>C<sup>™</sup> module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

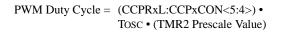

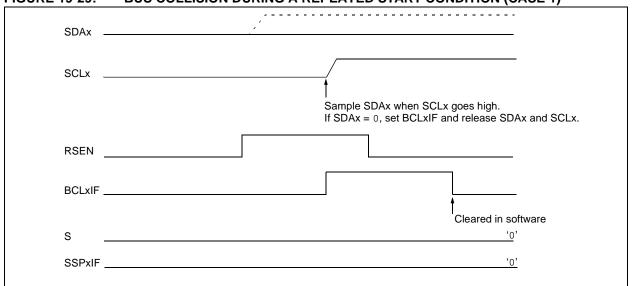

## 19.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from low level to high level.

- b) SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to '0'. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.