Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8722-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F6527 PIC18LF6527

- PIC18F6622 PIC18LF6622

- PIC18F6627 PIC18LF6627

- PIC18F6722 PIC18LF6722

- PIC18F8527 PIC18LF8527

- PIC18F8622 PIC18LF8622

- PIC18F8627 PIC18LF8627

- PIC18F8722 PIC18LF8722

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of highendurance, Enhanced Flash program memory. On top of these features, the PIC18F8722 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

## 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F8722 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be significantly reduced.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further.

- On-the-fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 28.0 "Electrical Characteristics" for values.

## 1.1.2 EXPANDED MEMORY

The PIC18F8722 family provides ample room for application code and includes members with 48, 64, 96 or 128 Kbytes of code space.

- Data RAM and Data EEPROM: The PIC18F8722 family also provides plenty of room for application data. The devices have 3936 bytes of data RAM, as well as 1024 bytes of data EEPROM, for long term retention of nonvolatile data.

- **Memory Endurance:** The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles, up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

#### 1.1.3 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F8722 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which provides an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of 6 user selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the high-speed crystal and internal oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

## 1.1.4 EXTERNAL MEMORY INTERFACE

In the unlikely event that 128 Kbytes of program memory is inadequate for an application, the PIC18F8527/8622/8627/8722 members of the family also implement an external memory interface. This allows the controller's internal program counter to address a memory space of up to 2 Mbytes, permitting a level of data access that few 8-bit devices can claim.

With the addition of new operating modes, the external memory interface offers many new options, including:

- Operating the microcontroller entirely from external memory

- Using combinations of on-chip and external memory, up to the 2-Mbyte limit

- Using external Flash memory for reprogrammable application code or large data tables

- Using external RAM devices for storing large amounts of variable data

#### 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

## 1.2 Other Special Features

- Communications: The PIC18F8722 family incorporates a range of serial communication peripherals, including 2 independent Enhanced USARTs and 2 Master SSP modules capable of both SPI and I<sup>2</sup>C (Master and Slave) modes of operation. Also, one of the general purpose I/O ports can be reconfigured as an 8-bit Parallel Slave Port for direct processor-to-processor communications.

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules and three Enhanced CCP (ECCP) modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once. Each of the three ECCP modules offer up to four PWM outputs, allowing for a total of 12 PWMs. The ECCPs also offer many beneficial features, including polarity selection, Programmable Dead-Time, Auto-Shutdown and Restart and Half-Bridge and Full-Bridge Output modes.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected boot block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F8722 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- **10-bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 28.0 "Electrical Characteristics" for time-out periods.

| Pin Name                             | Pin Number                          | Pin              | Buffer           | Description                                                                                                      |  |  |  |

|--------------------------------------|-------------------------------------|------------------|------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                             | TQFP                                | Туре             | Туре             | Description                                                                                                      |  |  |  |

|                                      |                                     |                  |                  | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |  |  |  |

| RB0/INT0/FLT0<br>RB0<br>INT0<br>FLT0 | 48                                  | I/O<br>I<br>I    | TTL<br>ST<br>ST  | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for ECCPx.                                              |  |  |  |

| RB1/INT1<br>RB1<br>INT1              | 47                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 1.                                                                            |  |  |  |

| RB2/INT2<br>RB2<br>INT2              | 46                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 2.                                                                            |  |  |  |

| RB3/INT3<br>RB3<br>INT3              | 45                                  | I/O<br>I         | TTL<br>ST        | Digital I/O.<br>External interrupt 3.                                                                            |  |  |  |

| RB4/KBI0<br>RB4<br>KBI0              | 44                                  | I/O<br>I         | TTL<br>TTL       | Digital I/O.<br>Interrupt-on-change pin.                                                                         |  |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM   | 43                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                            |  |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC   | 42                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD   | 37                                  | I/O<br>I<br>I/O  | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |  |  |  |

|                                      | ompatible input<br>tt Trigger input | CMOS<br>with CMO |                  | <ul> <li>CMOS compatible input or output</li> <li>Analog = Analog input</li> </ul>                               |  |  |  |

| I = Input                            |                                     |                  |                  | = Output                                                                                                         |  |  |  |

| TABLE 1-3: | PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED) | • |

|------------|---------------------------------------------------------------|---|

| IADLL I-J. | FIGIOLOJZI/0022/0021/0122 FINOUT I/O DESCRIFTIONS (CONTINUED) | , |

P = Power  $I^2 C^{TM} = I^2 C/SMBus input buffer$

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Din Norra                  | Pin Number       | Pin     | Buffer     | Description                                                 |  |  |  |

|----------------------------|------------------|---------|------------|-------------------------------------------------------------|--|--|--|

| Pin Name TQFP <sup>1</sup> |                  |         | Туре       | Description                                                 |  |  |  |

|                            |                  |         |            | PORTG is a bidirectional I/O port.                          |  |  |  |

| RG0/ECCP3/P3A              | 5                |         |            |                                                             |  |  |  |

| RG0                        |                  | I/O     | ST         | Digital I/O.                                                |  |  |  |

| ECCP3                      |                  | I/O     | ST         | Enhanced Capture 3 input/Compare 3 output/                  |  |  |  |

|                            |                  |         |            | PWM 3 output.                                               |  |  |  |

| P3A                        |                  | 0       | —          | ECCP3 PWM output A.                                         |  |  |  |

| RG1/TX2/CK2                | 6                |         |            |                                                             |  |  |  |

| RG1                        |                  | I/O     | ST         | Digital I/O.                                                |  |  |  |

| TX2                        |                  | 0       | _          | EUSART2 asynchronous transmit.                              |  |  |  |

| CK2                        |                  | I/O     | ST         | EUSART2 synchronous clock (see related RX2/DT2).            |  |  |  |

| RG2/RX2/DT2                | 7                |         |            |                                                             |  |  |  |

| RG2                        |                  | I/O     | ST         | Digital I/O.                                                |  |  |  |

| RX2                        |                  | 1       | ST         | EUSART2 asynchronous receive.                               |  |  |  |

| DT2                        |                  | I/O     | ST         | EUSART2 synchronous data (see related TX2/CK2).             |  |  |  |

| RG3/CCP4/P3D               | 8                |         |            |                                                             |  |  |  |

| RG3                        |                  | I/O     | ST         | Digital I/O.                                                |  |  |  |

| CCP4                       |                  | I/O     | ST         | Capture 4 input/Compare 4 output/PWM 4 output.              |  |  |  |

| P3D                        |                  | 0       | —          | ECCP3 PWM output D.                                         |  |  |  |

| RG4/CCP5/P1D               | 10               |         |            |                                                             |  |  |  |

| RG4                        |                  | I/O     | ST         | Digital I/O.                                                |  |  |  |

| CCP5                       |                  | I/O     | ST         | Capture 5 input/Compare 5 output/PWM 5 output.              |  |  |  |

| P1D                        |                  | 0       | —          | ECCP1 PWM output D.                                         |  |  |  |

| RG5                        |                  |         |            | See RG5/MCLR/VPP pin.                                       |  |  |  |

|                            | compatible input |         |            | = CMOS compatible input or output                           |  |  |  |

|                            |                  | with CN | 10S levels | Analog= Analog input                                        |  |  |  |

| I = Inpu                   |                  | 0       |            | = Output                                                    |  |  |  |

| P = Pow                    |                  |         | /SMB       | = I <sup>2</sup> C/SMBus input buffer                       |  |  |  |

|                            |                  | CP2 whe | en Configu | uration bit, CCP2MX, is cleared (all operating modes except |  |  |  |

| Microcontro                |                  |         |            |                                                             |  |  |  |

#### TABLE 1-4: PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

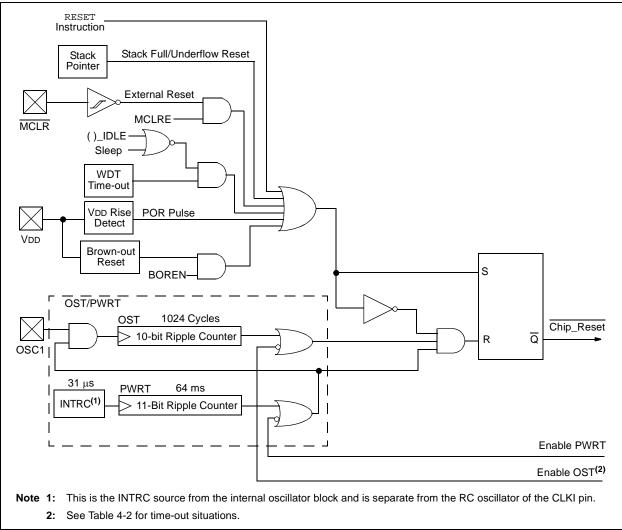

## 4.0 RESET

The PIC18F8722 family of devices differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 5.1.3.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 25.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

## 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.6** "**Reset State of Registers**".

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 10.0 "Interrupts". BOR is covered in Section 4.4 "Brown-out Reset (BOR)".

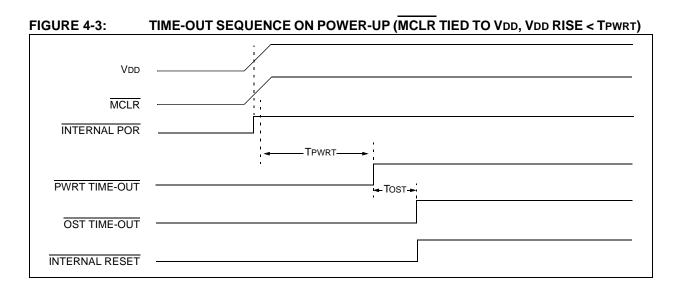

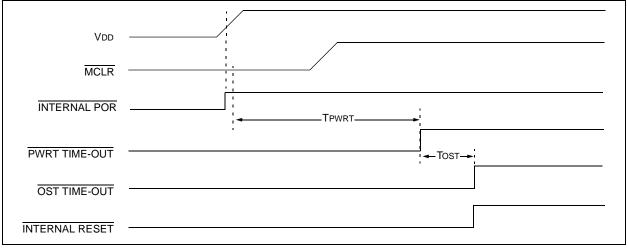

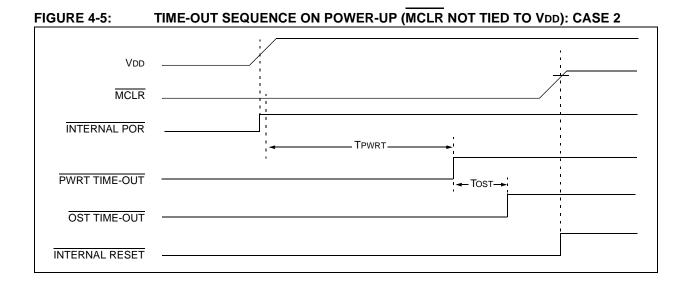

## FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

## 5.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.1.5.1 "Computed GOTO**").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

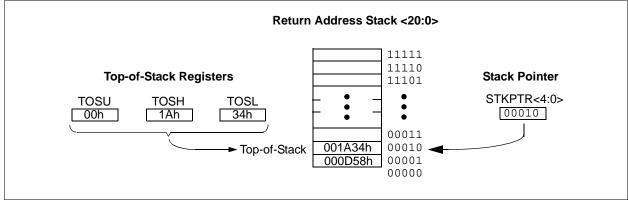

## 5.1.3 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions. The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special File Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a POP from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 5.1.3.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

## FIGURE 5-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

| TABLE 5-3       File Name | Bit 7                  | Bit 6              | Bit 5                     | Bit 4       | Bit 3        | Bit 2         | Bit 1                      | Bit 0   | Value on<br>POR, BOR | Details<br>on page: |

|---------------------------|------------------------|--------------------|---------------------------|-------------|--------------|---------------|----------------------------|---------|----------------------|---------------------|

| PORTJ <sup>(2)</sup>      | RJ7                    | RJ6                | RJ5                       | RJ4         | RJ3          | RJ2           | RJ1                        | RJ0     | xxxx xxxx            | 60, 156             |

| PORTH <sup>(2)</sup>      | RH7                    | RH6                | RH5                       | RH4         | RH3          | RH2           | RH1                        | RH0     | 0000 xxxx            | 60, 154             |

| PORTG                     | —                      | _                  | RG5 <sup>(5)</sup>        | RG4         | RG3          | RG2           | RG1                        | RG0     | xx xxxx              | 60, 151             |

| PORTF                     | RF7                    | RF6                | RF5                       | RF4         | RF3          | RF2           | RF1                        | RF0     | x000 0000            | 60, 149             |

| PORTE                     | RE7                    | RE6                | RE5                       | RE4         | RE3          | RE2           | RE1                        | RE0     | xxxx xxxx            | 60, 146             |

| PORTD                     | RD7                    | RD6                | RD5                       | RD4         | RD3          | RD2           | RD1                        | RD0     | xxxx xxxx            | 60, 143             |

| PORTC                     | RC7                    | RC6                | RC5                       | RC4         | RC3          | RC2           | RC1                        | RC0     | xxxx xxxx            | 60, 140             |

| PORTB                     | RB7                    | RB6                | RB5                       | RB4         | RB3          | RB2           | RB1                        | RB0     | xxxx xxxx            | 60, 137             |

| PORTA                     | RA7 <sup>(4)</sup>     | RA6 <sup>(4)</sup> | RA5                       | RA4         | RA3          | RA2           | RA1                        | RA0     | xx0x 0000            | 61, 135             |

| SPBRGH1                   | EUSART1 Ba             | aud Rate Gene      | rator Register            | High Byte   |              |               |                            |         | 0000 0000            | 61, 252             |

| BAUDCON1                  | ABDOVF                 | RCIDL              |                           | SCKP        | BRG16        |               | WUE                        | ABDEN   | 01-0 0-00            | 61, 250             |

| SPBRGH2                   | EUSART2 Ba             | aud Rate Gene      | rator Register            | High Byte   |              |               |                            |         | 0000 0000            | 61, 252             |

| BAUDCON2                  | ABDOVF                 | RCIDL              |                           | SCKP        | BRG16        |               | WUE                        | ABDEN   | 01-0 0-00            | 61, 250             |

| ECCP1DEL                  | P1RSEN                 | P1DC6              | P1DC5                     | P1DC4       | P1DC3        | P1DC2         | P1DC1                      | P1DC0   | 0000 0000            | 61, 200             |

| TMR4                      | Timer4 Regis           | 0000 0000          | 61, 178                   |             |              |               |                            |         |                      |                     |

| PR4                       | Timer4 Period Register |                    |                           |             |              |               |                            |         |                      | 61, 178             |

| T4CON                     | —                      | T4OUTPS3           | T4OUTPS2                  | T4OUTPS1    | T4OUTPS0     | TMR4ON        | T4CKPS1                    | T4CKPS0 | -000 0000            | 61, 178             |

| CCPR4H                    | Capture/Com            | xxxx xxxx          | 61, 180                   |             |              |               |                            |         |                      |                     |

| CCPR4L                    | Capture/Com            | pare/PWM Re        | gister 4 Low B            | yte         |              |               |                            |         | xxxx xxxx            | 61, 180             |

| CCP4CON                   | —                      | —                  | DC4B1                     | DC4B0       | CCP4M3       | CCP4M2        | CCP4M1                     | CCP4M0  | 00 0000              | 61, 179             |

| CCPR5H                    | Capture/Com            | pare/PWM Re        | gister 5 High E           | Byte        |              |               |                            |         | xxxx xxxx            | 61, 180             |

| CCPR5L                    | Capture/Com            | pare/PWM Re        | gister 5 Low B            | yte         | -            |               |                            | -       | xxxx xxxx            | 61, 180             |

| CCP5CON                   | —                      | —                  | DC5B1                     | DC5B0       | CCP5M3       | CCP5M2        | CCP5M1                     | CCP5M0  | 00 0000              | 61, 179             |

| SPBRG2                    | EUSART2 Ba             | aud Rate Gene      | rator Register            | Low Byte    |              |               |                            |         | 0000 0000            | 61, 252             |

| RCREG2                    | EUSART2 Re             | eceive Registe     | r                         |             |              |               |                            |         | 0000 0000            | 61, 260             |

| TXREG2                    | EUSART2 Tra            | ansmit Registe     | er                        |             | -            |               |                            | -       | 0000 0000            | 61, 257             |

| TXSTA2                    | CSRC                   | TX9                | TXEN                      | SYNC        | SENDB        | BRGH          | TRMT                       | TX9D    | 0000 0010            | 61, 248             |

| RCSTA2                    | SPEN                   | RX9                | SREN                      | CREN        | ADDEN        | FERR          | OERR                       | RX9D    | 0000 000x            | 61, 249             |

| ECCP3AS                   | ECCP3ASE               | ECCP3AS2           | ECCP3AS1                  | ECCP3AS0    | PSS3AC1      | PSS3AC0       | PSS3BD1                    | PSS3BD0 | 0000 0000            | 61, 201             |

| ECCP3DEL                  | P3RSEN                 | P3DC6              | P3DC5                     | P3DC4       | P3DC3        | P3DC2         | P3DC1                      | P3DC0   | 0000 0000            | 61, 200             |

| ECCP2AS                   | ECCP2ASE               | ECCP2AS2           | ECCP2AS1                  | ECCP2AS0    | PSS2AC1      | PSS2AC0       | PSS2BD1                    | PSS2BD0 | 0000 0000            | 61, 201             |

| ECCP2DEL                  | P2RSEN                 | P2DC6              | P2DC5                     | P2DC4       | P2DC3        | P2DC2         | P2DC1                      | P2DC0   | 0000 0000            | 61, 200             |

| SSP2BUF                   | MSSP2 Rece             | ive Buffer/Trar    | nsmit Register            |             |              |               |                            |         | xxxx xxxx            | 61, 170             |

| SSP2ADD                   | MSSP2 Addre            | ess Register ir    | I <sup>2</sup> C™ Slave r | node. MSSP2 | Baud Rate Re | load Register | in I <sup>2</sup> C Master | mode.   | 0000 0000            | 61, 170             |

| SSP2STAT                  | SMP                    | CKE                | D/A                       | Р           | S            | R/W           | UA                         | BF      | 0000 0000            | 61, 216             |

| SSP2CON1                  | WCOL                   | SSPOV              | SSPEN                     | CKP         | SSPM3        | SSPM2         | SSPM1                      | SSPM0   | 0000 0000            | 61, 217             |

| SSP2CON2                  | GCEN                   | ACKSTAT            | ACKDT                     | ACKEN       | RCEN         | PEN           | RSEN                       | SEN     | 0000 0000            | 61, 218             |

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, this bit reads as '0'.

2: These registers and/or bits are not implemented on 64-pin devices and are read as '0'. Reset values are shown for 80-pin devices; individual unimplemented bits should be interpreted as '-'.

3: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

4: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

5: RG5 and LATG5 are only available when Master Clear is disabled (MCLRE Configuration bit = 0); otherwise, RG5 and LATG5 read as '0'.

6: Bit 7 and Bit 6 are cleared by user software or by a POR.

7: Bit 21 of TBLPTRU allows access to the device Configuration bits.

## 7.2 Address and Data Width

PIC18F8527/8622/8627/8722 devices can be independently configured for different address and data widths on the same memory bus. Both address and data width are set by Configuration bits in the CONFIG3L register. As Configuration bits, this means that these options can only be configured by programming the device and are not controllable in software.

The BW bit selects an 8-bit or 16-bit data bus width. Setting this bit (default) selects a data width of 16 bits.

The ADW<1:0> bits determine the address bus width. The available options are 20-bit (default), 16-bit, 12-bit and 8-bit. Selecting any of the options other than 20-bit width makes a corresponding number of high-order lines available for I/O functions; these pins are no longer affected by the setting of the EBDIS bit. For example, selecting a 16-bit Address mode (ADW<1:0> = 10) disables A<19:16> and allows PORTH<3:0> to function without interruptions from the bus. Using smaller address widths allows users to tailor the memory bus to the size of the external memory space for a particular design while freeing up pins for dedicated I/O operation.

Because the ADW bits have the effect of disabling pins for memory bus operations, it is important to always select an address width at least equal to the data width. If 8-bit or 12-bit address widths are used with a 16-bit data width, the upper bits of data will not be available on the bus.

All combinations of address and data widths require multiplexing of address and data information on the same lines. The address and data multiplexing, as well as I/O ports made available by the use of smaller address widths, are summarized in Table 7-2.

## 7.2.1 21-BIT ADDRESSING

As an extension of 20-bit address width operation, the External Memory Bus can also fully address a 2 Mbyte memory space. This is done by using the Bus Address bit 0 (BA0) control line as the Least Significant bit of the address. The UB and LB control signals may also be used with certain memory devices to select the upper and lower bytes within a 16-bit wide data word.

This addressing mode is available in both 8-bit and certain 16-bit Data Width modes. Additional details are provided in Section 7.5.3 "16-bit Byte Select Mode" and Section 7.6 "8-Bit Data Width Modes".

## 7.3 Wait States

While it may be assumed that external memory devices will operate at the microcontroller clock rate, this is often not the case. In fact, many devices require longer times to write or retrieve data than the time allowed by the execution of table read or table write operations.

To compensate for this, the External Memory Bus can be configured to add a fixed delay to each table operation using the bus. Wait states are enabled by setting the WAITx bit. When enabled, the amount of delay is set by the WAIT<1:0> bits (MEMCON<5:4>). The delay is based on multiples of microcontroller instruction cycle time and are added following the instruction cycle when the table operation is executed. The range is from no delay to 3 Tcy (default value).

| Data Width | Address Width | Multiplexed Data and<br>Address Lines (and<br>Corresponding Ports) | Address-Only<br>Lines (and<br>Corresponding Ports) | Ports Available<br>for I/O  |

|------------|---------------|--------------------------------------------------------------------|----------------------------------------------------|-----------------------------|

|            | 8-bit         |                                                                    | _                                                  | All of PORTE and<br>PORTH   |

|            | 12-bit        | AD<7:0>                                                            | AD<11:8><br>(PORTE<3:0>)                           | PORTE<7:4>,<br>All of PORTH |

| 8-bit      | 16-bit        | (PORTD<7:0>)                                                       | AD<15:8><br>(PORTE<7:0>)                           | All of PORTH                |

|            | 20-bit        |                                                                    | A<19:16>, AD<15:8><br>(PORTH<3:0>,<br>PORTE<7:0>)  | _                           |

|            | 16-bit        | AD<15:0>                                                           | —                                                  | All of PORTH                |

| 16-bit     | 20-bit        | (PORTD<7:0>,<br>PORTE<7:0>)                                        | A<19:16><br>(PORTH<3:0>)                           | _                           |

#### TABLE 7-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS

| R/W     | -1 R/W-1                                    | R/W-1                             | R/W-1            | R/W-1            | R/W-1            | R/W-1           | R/W-1            |

|---------|---------------------------------------------|-----------------------------------|------------------|------------------|------------------|-----------------|------------------|

| RBP     | U INTEDG0                                   | INTEDG1                           | INTEDG2          | INTEDG3          | TMR0IP           | INT3IP          | RBIP             |

| bit 7   |                                             |                                   |                  |                  |                  |                 | bit 0            |

|         |                                             |                                   |                  |                  |                  |                 |                  |

| Legend: |                                             |                                   | L.14             |                  | newted bit week  |                 |                  |

|         | dable bit<br>Je at POR                      | W = Writable<br>'1' = Bit is set  |                  | 0 = 0 minimpler  | nented bit, read | x = Bit is unkr | 0.000            |

|         |                                             |                                   |                  |                  | aleu             | X = DILIS ULIKI | IOWIT            |

| bit 7   | RBPU: PORT                                  | B Pull-up Ena                     | ble bit          |                  |                  |                 |                  |

|         | 1 = All PORT                                | B pull-ups are                    | disabled         |                  |                  |                 |                  |

|         |                                             |                                   |                  | idual port latch | values           |                 |                  |

| bit 6   |                                             | ternal Interrup                   | •                | ct bit           |                  |                 |                  |

|         |                                             | on rising edge<br>on falling edge |                  |                  |                  |                 |                  |

| bit 5   | •                                           | ternal Interrup                   |                  | ct bit           |                  |                 |                  |

|         |                                             | on rising edge                    | •                |                  |                  |                 |                  |

|         | 0 = Interrupt                               | on falling edge                   | )                |                  |                  |                 |                  |

| bit 4   |                                             | ternal Interrup                   | •                | ct bit           |                  |                 |                  |

|         |                                             | on rising edge<br>on falling edge |                  |                  |                  |                 |                  |

| bit 3   | •                                           | ternal Interrup                   |                  | rt hit           |                  |                 |                  |

| bit 5   |                                             | on rising edge                    | •                |                  |                  |                 |                  |

|         |                                             | on falling edge                   |                  |                  |                  |                 |                  |

| bit 2   | TMR0IP: TM                                  | R0 Overflow In                    | terrupt Priority | ' bit            |                  |                 |                  |

|         | 1 = High prio                               | •                                 |                  |                  |                  |                 |                  |

| bit 1   | 0 = Low prior                               | -                                 | unt Driarity hit |                  |                  |                 |                  |

| DILI    | 1 = High prio                               | External Inter                    | upt Phonty bit   |                  |                  |                 |                  |

|         | 0 = Low prior                               |                                   |                  |                  |                  |                 |                  |

| bit 0   | RBIP: RB Po                                 | rt Change Inte                    | rrupt Priority b | it               |                  |                 |                  |

|         | 1 = High prio                               | •                                 |                  |                  |                  |                 |                  |

|         | 0 = Low prior                               | rity                              |                  |                  |                  |                 |                  |

| Note:   | Interrupt flag bits a                       |                                   |                  |                  |                  |                 |                  |

|         | enable bit or the g<br>are clear prior to e |                                   |                  |                  |                  |                 | errupt flag bits |

|         | are clear prior to e                        | nability an Inte                  | mupt. This lea   |                  | soliware polili  | y.              |                  |

## REGISTER 10-2: INTCON2: INTERRUPT CONTROL REGISTER 2

| TABLE 11-11:   | PORIFI   |                 | <b>G</b>                         |             |                                                                                                                    |

|----------------|----------|-----------------|----------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------|

| Pin Name       | Function | TRIS<br>Setting | I/O                              | l/O<br>Type | Description                                                                                                        |

| RF0/AN5        | RF0      | 0               | 0 O DIG LATF<0> data output; not |             | LATF<0> data output; not affected by analog input.                                                                 |

|                |          | 1               | Ι                                | ST          | PORTF<0> data input; disabled when analog input enabled.                                                           |

|                | AN5      | 1               | Ι                                | ANA         | A/D input channel 5. Default configuration on POR.                                                                 |

| RF1/AN6/C2OUT  | RF1      | 0               | 0                                | DIG         | LATF<1> data output; not affected by analog input.                                                                 |

|                |          | 1               | Ι                                | ST          | PORTF<1> data input; disabled when analog input enabled.                                                           |

|                | AN6      | 1               | Ι                                | ANA         | A/D input channel 6. Default configuration on POR.                                                                 |

|                | C2OUT    | 0               | 0                                | DIG         | Comparator 2 output; takes priority over port data.                                                                |

| RF2/AN7/C1OUT  | RF2      | 0               | 0                                | DIG         | LATF<2> data output; not affected by analog input.                                                                 |

|                |          | 1               | Ι                                | ST          | PORTF<2> data input; disabled when analog input enabled.                                                           |

|                | AN7      | 1               | Ι                                | ANA         | A/D input channel 7. Default configuration on POR.                                                                 |

|                | C1OUT    | 0               | 0                                | TTL         | Comparator 1 output; takes priority over port data.                                                                |

| RF3/AN8        | RF3      | 0               | 0                                | DIG         | LATF<3> data output; not affected by analog input.                                                                 |

|                |          | 1               | I                                | ST          | PORTF<3> data input; disabled when analog input enabled.                                                           |

|                | AN8      | 1               | I                                | ANA         | A/D input channel 8 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.   |

| RF4/AN9        | RF4      | 0               | 0                                | DIG         | LATF<4> data output; not affected by analog input.                                                                 |

|                |          | 1               | Ι                                | ST          | PORTF<4> data input; disabled when analog input enabled.                                                           |

|                | AN9      | 1               | I                                | ANA         | A/D input channel 9 and Comparator C2- input. Default input configuration on POR; does not affect digital output.  |

| RF5/AN10/CVREF | RF5      | 0               | 0                                | DIG         | LATF<5> data output; not affected by analog input. Disabled when CVREF output enabled.                             |

|                |          | 1               | I                                | ST          | PORTF<5> data input; disabled when analog input enabled. Disabled when CVREF output enabled.                       |

|                | AN10     | 1               | I                                | ANA         | A/D input channel 10 and Comparator C1+ input. Default input configuration on POR; not affected by analog output.  |

|                | CVREF    | x               | 0                                | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                   |

| RF6/AN11       | RF6      | 0               | 0                                | DIG         | LATF<6> data output; not affected by analog input.                                                                 |

|                |          | 1               | I                                | ST          | PORTF<6> data input; disabled when analog input enabled.                                                           |

|                | AN11     | 1               | Ι                                | ANA         | A/D input channel 11 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |

| RF7/SS1        | RF7      | 0               | 0                                | DIG         | LATF<7> data output.                                                                                               |

|                |          | 1               | Ι                                | ST          | PORTF<7> data input.                                                                                               |

|                | SS1      | 1               | I                                | TTL         | Slave select input for SSP (MSSP1 module).                                                                         |

## TABLE 11-11: PORTF FUNCTIONS

**Legend:** PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 11-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORT | TABLE 11-12: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTF |

|--------------------------------------------------------|--------------|--------------------------------------------|

|--------------------------------------------------------|--------------|--------------------------------------------|

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 60                         |

| PORTF  | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | 60                         |

| LATF   | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | 60                         |

| ADCON1 | _      | —      | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 59                         |

| CMCON  | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 59                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTF.

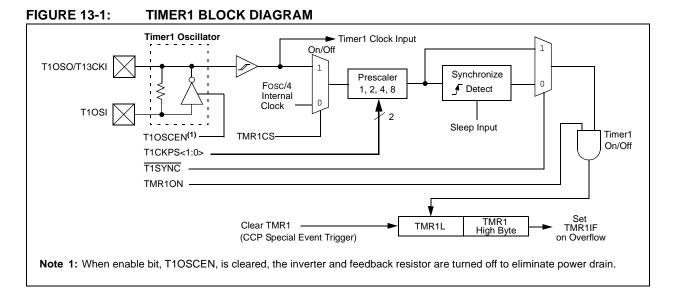

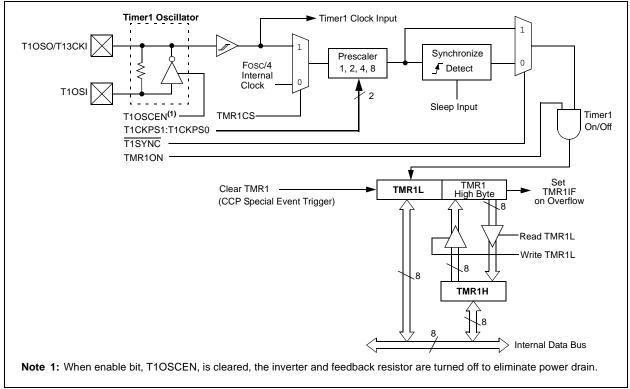

## 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:         |                                                                         |                                                                    |                                  |                        |  |  |  |

|-----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------|------------------------|--|--|--|

| R = Readable    | oit                                                                     | W = Writable bit                                                   | U = Unimplemented bit            | , read as '0'          |  |  |  |

| -n = Value at P | OR                                                                      | '1' = Bit is set                                                   | '0' = Bit is cleared             | x = Bit is unknown     |  |  |  |

|                 |                                                                         |                                                                    |                                  |                        |  |  |  |

| bit 7           |                                                                         | 6-Bit Read/Write Mode Enab                                         |                                  |                        |  |  |  |

|                 |                                                                         | bles register read/write of Tir<br>bles register read/write of Tir |                                  |                        |  |  |  |

| bit 6           | T1RUN:                                                                  | Timer1 System Clock Status                                         | bit                              |                        |  |  |  |

|                 |                                                                         | ice clock is derived from Tim                                      |                                  |                        |  |  |  |

|                 | 0 = Dev                                                                 | rice clock is derived from ano                                     | ther source                      |                        |  |  |  |

| bit 5-4         | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                    |                                                                    |                                  |                        |  |  |  |

|                 | 11 = 1:8 Prescale value                                                 |                                                                    |                                  |                        |  |  |  |

|                 |                                                                         | Prescale value                                                     |                                  |                        |  |  |  |

|                 | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                      |                                                                    |                                  |                        |  |  |  |

| bit 3           | <b>T10SCEN:</b> Timer1 Oscillator Enable bit                            |                                                                    |                                  |                        |  |  |  |

|                 | 1 = Timer1 oscillator is enabled                                        |                                                                    |                                  |                        |  |  |  |

|                 | 0 = Timer1 oscillator is shut off                                       |                                                                    |                                  |                        |  |  |  |

|                 |                                                                         | -                                                                  | ack resistor are turned off to e | eliminate power drain. |  |  |  |

| bit 2           | T1SYNC                                                                  | : Timer1 External Clock Inpu                                       | t Synchronization Select bit     |                        |  |  |  |

|                 | When TMR1CS = 1:                                                        |                                                                    |                                  |                        |  |  |  |

|                 |                                                                         | ot synchronize external clock                                      | < input                          |                        |  |  |  |

|                 | 0 = Synchronize external clock input<br>When TMR1CS = 0:                |                                                                    |                                  |                        |  |  |  |

|                 | This bit is ignored. Timer1 uses the internal clock when TMR1CS = $0$ . |                                                                    |                                  |                        |  |  |  |

| bit 1           |                                                                         | 6: Timer1 Clock Source Sele                                        |                                  |                        |  |  |  |

| bit i           | 1 = External clock from pin RC0/T10S0/T13CKI (on the rising edge)       |                                                                    |                                  |                        |  |  |  |

|                 | 0 = Internal clock (Fosc/4)                                             |                                                                    |                                  |                        |  |  |  |

| bit 0           | TMR10                                                                   | N: Timer1 On bit                                                   |                                  |                        |  |  |  |

|                 | 1 = Ena                                                                 | bles Timer1                                                        |                                  |                        |  |  |  |

|                 | 0 = Stop                                                                | os Timer1                                                          |                                  |                        |  |  |  |

## 13.1 Timer1 Operation

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction

cycle (Fosc/4). When the bit is set, Timer1 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When Timer1 is enabled, the RC1/T1OSI and RC0/T10SO/T13CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

## FIGURE 13-2: TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

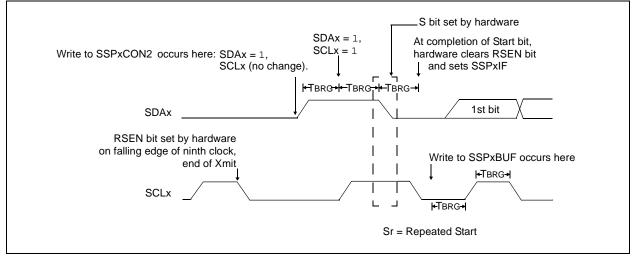

### 19.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 19.4.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 19-20: REPEATED START CONDITION WAVEFORM

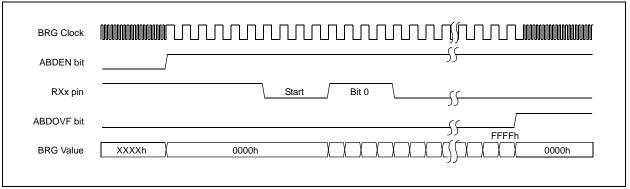

#### 20.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 20-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character) in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRGx begins counting up, using the preselected clock source on the first rising edge of RXx. After eight bits on the RXx pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGHx:SPBRGx register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCONx<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 20-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRGx and SPBRGHx will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGHx register. Refer to Table 20-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCxIF interrupt is set once the fifth rising edge on RXx is detected. The value in the RCREGx needs to be read to clear the RCxIF interrupt. The contents of RCREGx should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

## TABLE 20-4:BRG COUNTER<br/>CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |

|-------|------|-------------------|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |

|       |      |                   |  |  |  |

**Note:** During the ABD sequence, SPBRGx and SPBRGHx are both used as a 16-bit counter, independent of BRG16 setting.

#### 20.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREGx cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

| BRG Value                | XXXXh                    | 0000h                                            | XXXXXXXXXXXXXXX001Ch                                                                                               |

|--------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| RXx pin                  |                          | Edge #1 Edge #2<br>Start Bit 0 Bit 1 Bit 2 Bit 3 | Edge #3         Edge #4         Edge #5           Bit 4         Bit 5         Bit 6         Bit 7         Stop Bit |

| BRG Clock                | ົມທານທານສາມທານສາມທານກໍ່າ | www.iwwwwwwww                                    |                                                                                                                    |

| ABDEN bit                | Set by User —            |                                                  | Auto-Cleared                                                                                                       |

| RCxIF bit<br>(Interrupt) |                          |                                                  |                                                                                                                    |

| Read<br>RCREGx           |                          |                                                  |                                                                                                                    |

| SPBRGx                   |                          | XXXXh                                            | X 1Ch                                                                                                              |

| SPBRGHx                  |                          | XXXXh                                            | ∑ 00h                                                                                                              |

#### FIGURE 20-2: BRG OVERFLOW SEQUENCE

#### 20.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep, or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSRx register will transfer the data to the RCREGx register; if the RCxIE enable bit is set, the interrupt generated will wake the chip from the lowpower mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RCxIE.

- 3. If 9-bit reception is desired, set bit, RX9.

- 4. To enable reception, set enable bit, CREN.

- 5. Flag bit, RCxIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREGx register.

- 8. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7                                          | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|------------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR1     | PSPIF                                          | ADIF      | RC1IF  | TX1IF  | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 60                         |

| PIE1     | PSPIE                                          | ADIE      | RC1IE  | TX1IE  | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 60                         |

| IPR1     | PSPIP                                          | ADIP      | RC1IP  | TX1IP  | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 60                         |

| TRISC    | TRISC7                                         | TRISC6    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 60                         |

| TRISG    | —                                              | —         | _      | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 60                         |

| RCSTAx   | SPEN                                           | RX9       | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 59                         |

| RCREGx   | EUSARTx Receive Register                       |           |        |        |        |        | 59     |        |                            |

| TXSTAx   | CSRC                                           | TX9       | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 59                         |

| BAUDCONx | ABDOVF                                         | RCIDL     | _      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 61                         |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |           |        |        |        |        | 61     |        |                            |

| SPBRGx   | EUSARTx Baud Rate Generator Register Low Byte  |           |        |        |        |        |        | 59     |                            |

#### TABLE 20-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

| SUBWFB           |                                  | Subtract W from f with Borrow                                                                                                                                                                                                                                                            |                                               |                    |                |  |  |  |

|------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|----------------|--|--|--|

| Synta            | ax:                              | SUBWFB f {,d {,a}}                                                                                                                                                                                                                                                                       |                                               |                    |                |  |  |  |

| Operands:        |                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                                                                                           |                                               |                    |                |  |  |  |

| Operation:       |                                  |                                                                                                                                                                                                                                                                                          | $(f) - (W) - (\overline{C}) \rightarrow dest$ |                    |                |  |  |  |

| Status Affected: |                                  | N, OV, C,                                                                                                                                                                                                                                                                                | DC, Z                                         |                    | ·              |  |  |  |

| Enco             | -                                | 0101                                                                                                                                                                                                                                                                                     | 10da                                          | ffff               | ffff           |  |  |  |

| Description:     |                                  | Subtract W and the Carry flag (borrow)<br>from register 'f' (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default).                                                                              |                                               |                    |                |  |  |  |