Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8722t-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

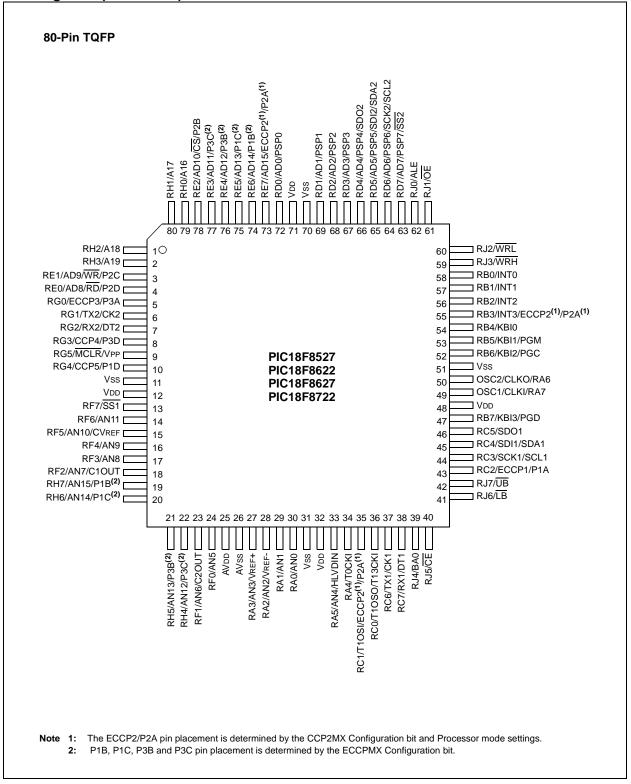

#### **Pin Diagrams (Continued)**

| Din Nama                                                                          | Pin Number              | Pin                    | Buffer           | Description                                                                                                                                                                         |  |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                          | TQFP                    | Туре                   | Туре             | Description                                                                                                                                                                         |  |  |  |  |

|                                                                                   |                         |                        |                  | PORTC is a bidirectional I/O port.                                                                                                                                                  |  |  |  |  |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI                                        | 30                      | I/O<br>O<br>I          | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                                                                    |  |  |  |  |

| RC1/T1OSI/ECCP2/P2A<br>RC1<br>T1OSI<br>ECCP2 <sup>(1)</sup><br>P2A <sup>(1)</sup> | 29                      | I/O<br>I<br>I/O<br>O   | ST<br>CMOS<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.<br>ECCP2 PWM output A.                                                      |  |  |  |  |

| RC2/ECCP1/P1A<br>RC2<br>ECCP1                                                     | 33                      | I/O<br>I/O             | ST<br>ST         | Digital I/O.<br>Enhanced Capture 1 input/Compare 1 output/<br>PWM 1 output.                                                                                                         |  |  |  |  |

| P1A                                                                               |                         | 0                      | —                | ECCP1 PWM output A.                                                                                                                                                                 |  |  |  |  |

| RC3/SCK1/SCL1<br>RC3<br>SCK1<br>SCL1                                              | C3  /O ST<br>CK1  /O ST |                        | ST<br>ST<br>ST   | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mod                                              |  |  |  |  |

| RC4/SDI1/SDA1<br>RC4<br>SDI1<br>SDA1                                              | 35                      | I/O<br>I<br>I/O        | ST<br>ST<br>ST   | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                                                                          |  |  |  |  |

| RC5/SDO1<br>RC5<br>SDO1                                                           | 36                      | I/O<br>O               | ST<br>—          | Digital I/O.<br>SPI data out.                                                                                                                                                       |  |  |  |  |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                                                  | 31                      | I/O<br>O<br>I/O        | ST<br>—<br>ST    | Digital I/O.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related RX1/DT1).                                                                                  |  |  |  |  |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                                                  | 32                      | I/O<br>I<br>I/O        | ST<br>ST<br>ST   | Digital I/O.<br>EUSART1 asynchronous receive.<br>EUSART1 synchronous data (see related TX1/CK1).                                                                                    |  |  |  |  |

| I = Input<br>P = Power                                                            | tt Trigger input        | O<br>I <sup>2</sup> C™ | OS levels        | <ul> <li>CMOS compatible input or output</li> <li>Analog = Analog input</li> <li>= Output</li> <li>= I<sup>2</sup>C/SMBus input buffer</li> <li>ion bit, CCP2MX, is set.</li> </ul> |  |  |  |  |

#### TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

**2:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Description                                                                                    |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

| ΓG is a bidirectional I/O port.                                                                |

| gital I/O.<br>hanced Capture 3 input/Compare 3 output/<br>VM 3 output.                         |

| CCP3 PWM output A.                                                                             |

| gital I/O.<br>JSART2 asynchronous transmit.<br>JSART2 synchronous clock (see related RX2/DT2). |

| gital I/O.<br>JSART2 asynchronous receive.<br>JSART2 synchronous data (see related TX2/CK2).   |

| gital I/O.<br>apture 4 input/Compare 4 output/PWM 4 output.<br>CCP3 PWM output D.              |

| gital I/O.<br>apture 5 input/Compare 5 output/PWM 5 output.<br>CCP1 PWM output D.              |

| RG5/MCLR/VPP pin.                                                                              |

| nd reference for logic and I/O pins.                                                           |

| ve supply for logic and I/O pins.                                                              |

| nd reference for analog modules.                                                               |

| ve supply for analog modules.                                                                  |

| ti<br>JI                                                                                       |

#### **TABLE 1-3:** PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

=  $I^2C/SMBus$  input buffer = Power Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

**2:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

I<sup>2</sup>C™

Р

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

### TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                | LP, XT, HS                    |                                       |                                    |

| Primary Device Clock           | HSPLL                         | Tcsd <sup>(1)</sup>                   | OSTS                               |

| (PRI_IDLE mode)                | EC, RC                        | 10.30 ( )                             |                                    |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| T1OSC or INTRC                 | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

| INTOSC <sup>(2)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

| (Sleep mode)                   | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

Note 1: TCSD (parameter 38, Table 28-12) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies. On Reset, INTOSC defaults to 1 MHz.

**3:** TOST is the Oscillator Start-up Timer (parameter 32, Table 28-12). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12, Table 28-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 28-12), the INTOSC stabilization period.

NOTES:

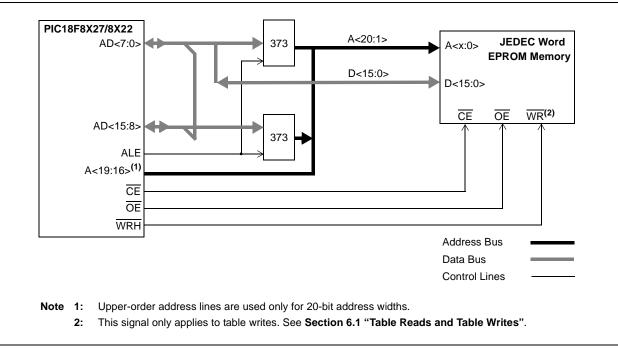

#### 7.5.2 16-BIT WORD WRITE MODE

Figure 7-2 shows an example of 16-bit Word Write mode for PIC18F8527/8622/8627/8722 devices. This mode is used for word-wide memories which includes some of the EPROM and Flash-type memories. This mode allows opcode fetches and table reads from all forms of 16-bit memory and table writes to any type of word-wide external memories. This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address (TBLPTR<0> = 0), the TABLAT data is transferred to a holding latch and the external address data bus is tri-stated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address (TBLPTR<0> = 1), the TABLAT data is presented on the upper byte of the AD15:AD0 bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus.

The WRH signal is strobed for each write cycle; the WRL pin is unused. The signal on the BA0 pin indicates the Least Significant bit of TBLPTR but it is left unconnected. Instead, the UB and LB signals are active to select both bytes. The obvious limitation to this method is that the table write must be done in pairs on a specific word boundary to correctly write a word location.

#### FIGURE 7-2: 16-BIT WORD WRITE MODE EXAMPLE

#### 11.9 PORTJ, TRISJ and LATJ Registers

| Note: | PORTJ   | is     | available    | only       | on |

|-------|---------|--------|--------------|------------|----|

|       | PIC18F8 | 527/86 | 22/8627/8722 | 2 devices. |    |

PORTJ is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISJ. Setting a TRISJ bit (= 1) will make the corresponding PORTJ pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISJ bit (= 0) will make the corresponding PORTJ pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATJ) is also memory mapped. Read-modify-write operations on the LATJ register, read and write the latched output value for PORTJ.

All pins on PORTJ are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power-on Reset, these pins ar | е |

|-------|------------------------------------|---|

|       | configured as digital inputs.      |   |

When the external memory interface is enabled, all of the PORTJ pins function as control outputs for the interface. This occurs automatically when the interface is enabled by clearing the EBDIS control bit (MEMCON<7>). The TRISJ bits are also overridden.

| EXAMPLE 11-9:   | INITIALIZING PORTJ |

|-----------------|--------------------|

| EAAIVIFLE II-9. |                    |

| CLRF  | PORTJ | ; | Initialize PORTJ by   |

|-------|-------|---|-----------------------|

|       |       | ; | clearing output       |

|       |       | ; | data latches          |

| CLRF  | LATJ  | ; | Alternate method      |

|       |       | ; | to clear output       |

|       |       | ; | data latches          |

| MOVLW | 0xCF  | ; | Value used to         |

|       |       | ; | initialize data       |

|       |       | ; | direction             |

| MOVWF | TRISJ | ; | Set RJ3:RJ0 as inputs |

|       |       | ; | RJ5:RJ4 as output     |

|       |       | ; | RJ7:RJ6 as inputs     |

|       |       |   |                       |

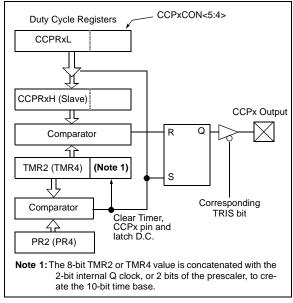

#### 17.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP4 and CCP5 pins are multiplexed with a PORTG data latch, the appropriate TRISG bit must be cleared to make the CCP4 or CCP5 pin an output.

| Note: | Clearing the CCP4CON or CCP5CON register will force the RG3 or RG4 output latch (depending on device configuration) |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       | to the default low level. This is not the PORTG I/O data latch.                                                     |

Figure 17-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up a CCP module for PWM operation, see **Section 17.4.3** "Setup for PWM Operation".

#### FIGURE 17-4: SIMPLIFIED PWM BLOCK DIAGRAM

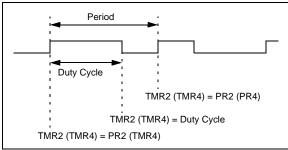

A PWM output (Figure 17-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 17-5: PWM OUTPUT

#### 17.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 (PR4) register. The PWM period can be calculated using the following formula:

#### EQUATION 17-1:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 (TMR4) is equal to PR2 (PR4), the following three events occur on the next increment cycle:

- TMR2 (TMR4) is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

- Note: The Timer2 and Timer 4 postscalers (see Section 14.0 "Timer2 Module" and Section 16.0 "Timer4 Module") are not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 17.4.2 PWM DUTY CYCLE

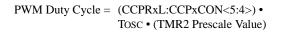

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> contains the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 17-2:**

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPRxH until after a match between PR2 (PR4) and TMR2 (TMR4) occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

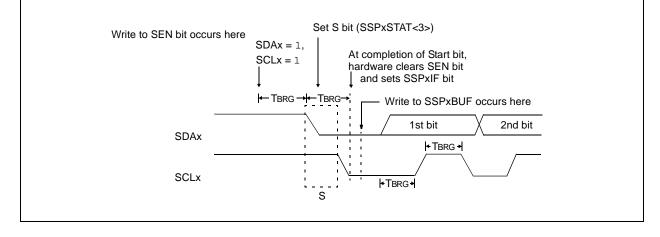

#### 19.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPxCON2<0>). If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit (SSPxSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPxCON2<0>) will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

Note: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 19.4.8.1 WCOL Status Flag

If the user writes the SSPxBUF when a Start sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of SSPxCON2 is disabled until the Start condition is complete.

#### FIGURE 19-19: FIRST START BIT TIMING

#### 19.4.14 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 19.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 19.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

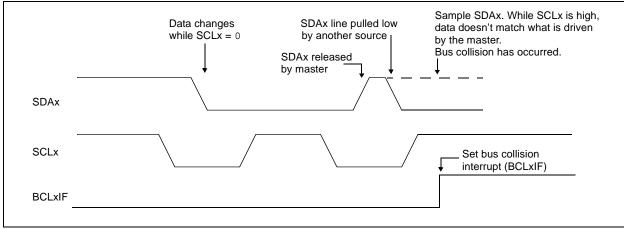

#### 19.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the  $I^2C$  port to its Idle state (Figure 19-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 19-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

#### 20.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 20-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character) in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRGx begins counting up, using the preselected clock source on the first rising edge of RXx. After eight bits on the RXx pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGHx:SPBRGx register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCONx<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 20-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRGx and SPBRGHx will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGHx register. Refer to Table 20-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCxIF interrupt is set once the fifth rising edge on RXx is detected. The value in the RCREGx needs to be read to clear the RCxIF interrupt. The contents of RCREGx should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

### TABLE 20-4:BRG COUNTER<br/>CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |  |  |

|-------|------|-------------------|--|--|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |  |  |

|       |      |                   |  |  |  |  |  |

**Note:** During the ABD sequence, SPBRGx and SPBRGHx are both used as a 16-bit counter, independent of BRG16 setting.

#### 20.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREGx cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

NOTES:

| File Name |                         | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2   | Bit 1                 | Bit 0  | Default/<br>Unprogrammed<br>Value |

|-----------|-------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------|-----------------------|--------|-----------------------------------|

| 300001h   | CONFIG1H                | IESO                 | FCMEN                |                      | _                    | FOSC3                | FOSC2   | FOSC1                 | FOSC0  | 00 0111                           |

| 300002h   | CONFIG2L                | _                    | _                    | _                    | BORV1                | BORV0                | BOREN1  | BOREN0                | PWRTEN | 1 1111                            |

| 300003h   | CONFIG2H                | _                    | —                    | _                    | WDTPS3               | WDTPS2               | WDTPS1  | WDTPS0                | WDTEN  | 1 1111                            |

| 300004h   | CONFIG3L <sup>(5)</sup> | WAIT                 | BW                   | ABW1                 | ABW0                 | _                    | —       | PM1                   | PM0    | 111111                            |

| 300005h   | CONFIG3H                | MCLRE                | —                    | —                    | _                    | —                    | LPT1OSC | ECCPMX <sup>(5)</sup> | CCP2MX | 1011                              |

| 300006h   | CONFIG4L                | DEBUG                | XINST                | BBSIZ1               | BBSIZ0               | _                    | LVP     | _                     | STVREN | 1000 -1-1                         |

| 300008h   | CONFIG5L                | CP7 <sup>(1)</sup>   | CP6 <sup>(1)</sup>   | CP5 <sup>(2)</sup>   | CP4 <sup>(2)</sup>   | CP3 <sup>(3)</sup>   | CP2     | CP1                   | CP0    | 1111 1111                         |

| 300009h   | CONFIG5H                | CPD                  | CPB                  | _                    | —                    | _                    | _       | _                     | _      | 11                                |

| 30000Ah   | CONFIG6L                | WRT7 <sup>(1)</sup>  | WRT6 <sup>(1)</sup>  | WRT5 <sup>(2)</sup>  | WRT4 <sup>(2)</sup>  | WRT3 <sup>(3)</sup>  | WRT2    | WRT1                  | WRT0   | 1111 1111                         |

| 30000Bh   | CONFIG6H                | WRTD                 | WRTB                 | WRTC                 | _                    | —                    | _       | _                     | _      | 111                               |

| 30000Ch   | CONFIG7L                | EBRT7 <sup>(1)</sup> | EBRT6 <sup>(1)</sup> | EBTR5 <sup>(2)</sup> | EBTR4 <sup>(2)</sup> | EBTR3 <sup>(3)</sup> | EBTR2   | EBTR1                 | EBTR0  | 1111 1111                         |

| 30000Dh   | CONFIG7H                | _                    | EBTRB                | _                    | —                    | _                    | —       | _                     | _      | -1                                |

| 3FFFFEh   | DEVID1 <sup>(4)</sup>   | DEV2                 | DEV1                 | DEV0                 | REV4                 | REV3                 | REV2    | REV1                  | REV0   | xxxx xxxx                         |

| 3FFFFFh   | DEVID2 <sup>(4)</sup>   | DEV10                | DEV9                 | DEV8                 | DEV7                 | DEV6                 | DEV5    | DEV4                  | DEV3   | xxxx xxxx                         |

#### TABLE 25-1: CONFIGURATION BITS AND DEVICE IDs

$\label{eq:logend: Legend: Legend: u = unchanged, - = unimplemented, q = value depends on condition.$

Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented in PIC18F6527/6622/6627/8527/8622/8627 devices.

2: Unimplemented in PIC18F6527/6622/8527/8622 devices.

3: Unimplemented in PIC18F6527/8527 devices.

4: See Register 25-13 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

5: Unimplemented in PIC18F6527/6622/6627/6722 devices.

| R/P-1           | R/P-0                                                                                                                                                                                                                  | R/P-0                                                                                                                                                                                                                               | R/P-0  | U-0              | R/P-1            | U-0             | R/P-1  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|------------------|-----------------|--------|--|--|--|--|

| DEBUG           | XINST                                                                                                                                                                                                                  | BBSIZ1                                                                                                                                                                                                                              | BBSIZ0 | —                | LVP              | —               | STVREN |  |  |  |  |

| bit 7           |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                     | ·      |                  | •                |                 | bit 0  |  |  |  |  |

| Legend:         |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                     |        |                  |                  |                 |        |  |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                        | bit    | U = Unimpler     | mented bit, read | as '0'          |        |  |  |  |  |

| -n = Value at I | POR                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                    |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |

| bit 7           | <b>DEBUG:</b> Background Debugger Enable bit<br>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins<br>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug |                                                                                                                                                                                                                                     |        |                  |                  |                 |        |  |  |  |  |

| bit 6           | 1 = Instruction                                                                                                                                                                                                        | <ul> <li>XINST: Extended Instruction Set Enable bit</li> <li>1 = Instruction set extension and Indexed Addressing mode enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> </ul> |        |                  |                  |                 |        |  |  |  |  |

| bit 5-4         | 11 = 4K word<br>10 = 4K word<br>01 = 2K word                                                                                                                                                                           | BBSIZ<1:0>: Boot Block Size Select bits<br>11 = 4K words (8 Kbytes) boot block size<br>10 = 4K words (8 Kbytes) boot block size<br>01 = 2K words (4 Kbytes) boot block size<br>00 = 1K word (2 Kbytes) boot block size              |        |                  |                  |                 |        |  |  |  |  |

| bit 3           | Unimplemen                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                                      | 0'     |                  |                  |                 |        |  |  |  |  |

| bit 2           | LVP: Single-Supply ICSP™ Enable bit<br>1 = Single-Supply ICSP enabled<br>0 = Single-Supply ICSP disabled                                                                                                               |                                                                                                                                                                                                                                     |        |                  |                  |                 |        |  |  |  |  |

| bit 1           | Unimplemen                                                                                                                                                                                                             | Unimplemented: Read as '0'                                                                                                                                                                                                          |        |                  |                  |                 |        |  |  |  |  |

| bit 0           | STVREN: Stack Full/Underflow Reset Enable bit<br>1 = Stack full/underflow will cause Reset<br>0 = Stack full/underflow will not cause Reset                                                                            |                                                                                                                                                                                                                                     |        |                  |                  |                 |        |  |  |  |  |

#### REGISTER 25-6: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| DEC                            | FSZ                                                                                                                                                                                                                                                                                  | Decrement                                           | Decrement f, Skip if 0                                                                                                                                               |                         |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| Synta                          | ax:                                                                                                                                                                                                                                                                                  | DECFSZ f                                            | DECFSZ f {,d {,a}}                                                                                                                                                   |                         |  |  |  |  |

| Oper                           | ands:                                                                                                                                                                                                                                                                                | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | f ≤ 255<br>[0,1]                                                                                                                                                     |                         |  |  |  |  |

| Oper                           | ation:                                                                                                                                                                                                                                                                               | ()                                                  | $(f) - 1 \rightarrow dest,$<br>skip if result = 0                                                                                                                    |                         |  |  |  |  |

| Statu                          | is Affected:                                                                                                                                                                                                                                                                         | None                                                |                                                                                                                                                                      |                         |  |  |  |  |

| Enco                           | oding:                                                                                                                                                                                                                                                                               | 0010                                                | 11da fff                                                                                                                                                             | f ffff                  |  |  |  |  |

| Desc                           | ription:                                                                                                                                                                                                                                                                             | decremente<br>placed in W                           | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default). |                         |  |  |  |  |

|                                |                                                                                                                                                                                                                                                                                      | which is alre                                       | If the result is '0', the next instruction which is already fetched is discarded and a $NOP$ is executed instead, making it a two-cycle instruction.                 |                         |  |  |  |  |

|                                |                                                                                                                                                                                                                                                                                      | lf 'a' is '1', th                                   | is '0', the Access Bank is selected.<br>is '1', the BSR is used to select the<br>bank (default).                                                                     |                         |  |  |  |  |

|                                | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                     |                                                                                                                                                                      |                         |  |  |  |  |

| Word                           | ls:                                                                                                                                                                                                                                                                                  | 1                                                   |                                                                                                                                                                      |                         |  |  |  |  |

| Cycle                          | es:                                                                                                                                                                                                                                                                                  |                                                     | rcles if skip an<br>2-word instru                                                                                                                                    |                         |  |  |  |  |

| QC                             | ycle Activity:                                                                                                                                                                                                                                                                       |                                                     |                                                                                                                                                                      |                         |  |  |  |  |

|                                | Q1                                                                                                                                                                                                                                                                                   | Q2                                                  | Q3                                                                                                                                                                   | Q4                      |  |  |  |  |

|                                | Decode Read<br>register 'f'                                                                                                                                                                                                                                                          |                                                     | Process<br>Data                                                                                                                                                      | Write to<br>destination |  |  |  |  |

| lf sk                          | in:                                                                                                                                                                                                                                                                                  | register i                                          | Dala                                                                                                                                                                 | uestination             |  |  |  |  |

|                                | Q1                                                                                                                                                                                                                                                                                   | Q2                                                  | Q3                                                                                                                                                                   | Q4                      |  |  |  |  |

|                                | No                                                                                                                                                                                                                                                                                   | No                                                  | No                                                                                                                                                                   | No                      |  |  |  |  |

|                                | operation                                                                                                                                                                                                                                                                            | operation                                           | operation                                                                                                                                                            | operation               |  |  |  |  |

| lf sk                          |                                                                                                                                                                                                                                                                                      | d by 2-word in:                                     |                                                                                                                                                                      | 04                      |  |  |  |  |

|                                | Q1<br>No                                                                                                                                                                                                                                                                             | Q2<br>No                                            | Q3<br>No                                                                                                                                                             | Q4<br>No                |  |  |  |  |

|                                | operation                                                                                                                                                                                                                                                                            | operation                                           | operation                                                                                                                                                            | operation               |  |  |  |  |

|                                | No                                                                                                                                                                                                                                                                                   | No                                                  | No                                                                                                                                                                   | No                      |  |  |  |  |

|                                | operation                                                                                                                                                                                                                                                                            | operation                                           | operation                                                                                                                                                            | operation               |  |  |  |  |

| Example:                       |                                                                                                                                                                                                                                                                                      | HERE                                                | DECFSZ<br>GOTO                                                                                                                                                       | CNT, 1, 1<br>LOOP       |  |  |  |  |

| CONTINUE<br>Before Instruction |                                                                                                                                                                                                                                                                                      |                                                     |                                                                                                                                                                      |                         |  |  |  |  |

|                                | PC<br>After Instruction                                                                                                                                                                                                                                                              | = Address                                           | = Address (HERE)                                                                                                                                                     |                         |  |  |  |  |

|                                | CNT<br>If CNT                                                                                                                                                                                                                                                                        | = CNT - 1<br>= 0;                                   |                                                                                                                                                                      |                         |  |  |  |  |

|                                | PC<br>If CNT                                                                                                                                                                                                                                                                         | = Address<br>$\neq$ 0;                              |                                                                                                                                                                      |                         |  |  |  |  |

| PC = Address (HERE + 2)        |                                                                                                                                                                                                                                                                                      |                                                     |                                                                                                                                                                      |                         |  |  |  |  |

| DCFSNZ                                                                                                                          | Decrement                                                                                                                      | Decrement f, Skip if not 0                                                                                                                                                                                                                                                           |                                                |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                         | DCFSNZ                                                                                                                         | DCFSNZ f {,d {,a}}                                                                                                                                                                                                                                                                   |                                                |  |  |  |  |  |

| Operands:                                                                                                                       | $0 \leq f \leq 255$                                                                                                            |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

|                                                                                                                                 | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| Operation:                                                                                                                      | (f) – 1 $\rightarrow$ de skip if resul                                                                                         |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| Status Affected:                                                                                                                | None                                                                                                                           | ·                                                                                                                                                                                                                                                                                    |                                                |  |  |  |  |  |

| Encoding:                                                                                                                       | 0100                                                                                                                           |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| Description:                                                                                                                    |                                                                                                                                |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| Description.                                                                                                                    | decremente<br>placed in W                                                                                                      | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default).                                                                                                                          |                                                |  |  |  |  |  |

|                                                                                                                                 | instruction<br>discarded a                                                                                                     | If the result is not '0', the next<br>instruction which is already fetched is<br>discarded and a NOP is executed<br>instead, making it a two-cycle<br>instruction                                                                                                                    |                                                |  |  |  |  |  |

|                                                                                                                                 | ,                                                                                                                              | he Access Bar<br>he BSR is used<br>(default).                                                                                                                                                                                                                                        |                                                |  |  |  |  |  |

|                                                                                                                                 | set is enabl<br>in Indexed<br>mode wher<br>Section 26<br>Bit-Oriente                                                           | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                |  |  |  |  |  |

| Words:                                                                                                                          | 1                                                                                                                              |                                                                                                                                                                                                                                                                                      | uelans.                                        |  |  |  |  |  |

| Cycles:                                                                                                                         |                                                                                                                                | 1(2)                                                                                                                                                                                                                                                                                 |                                                |  |  |  |  |  |

| Cycles.                                                                                                                         | Note: 3 c                                                                                                                      | ycles if skip ar<br>a 2-word instru                                                                                                                                                                                                                                                  |                                                |  |  |  |  |  |

| Q Cycle Activity:                                                                                                               |                                                                                                                                |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| Q1                                                                                                                              | Q2                                                                                                                             | Q3                                                                                                                                                                                                                                                                                   | Q4                                             |  |  |  |  |  |

| Decode                                                                                                                          | Read                                                                                                                           | Process                                                                                                                                                                                                                                                                              | Write to<br>destination                        |  |  |  |  |  |

| lf skip:                                                                                                                        | register 'f'                                                                                                                   | Data                                                                                                                                                                                                                                                                                 | destination                                    |  |  |  |  |  |

| Q1                                                                                                                              | Q2                                                                                                                             | Q3                                                                                                                                                                                                                                                                                   | Q4                                             |  |  |  |  |  |

| No                                                                                                                              | No                                                                                                                             | No                                                                                                                                                                                                                                                                                   | No                                             |  |  |  |  |  |

|                                                                                                                                 |                                                                                                                                |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| operation                                                                                                                       | operation                                                                                                                      | operation                                                                                                                                                                                                                                                                            | operation                                      |  |  |  |  |  |

| operation<br>If skip and followe                                                                                                |                                                                                                                                |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

|                                                                                                                                 |                                                                                                                                |                                                                                                                                                                                                                                                                                      |                                                |  |  |  |  |  |

| If skip and followe<br>Q1<br>No                                                                                                 | ed by 2-word in<br>Q2<br>No                                                                                                    | struction:<br>Q3<br>No                                                                                                                                                                                                                                                               | operation<br>Q4<br>No                          |  |  |  |  |  |

| If skip and followe<br>Q1<br>No<br>operation                                                                                    | ed by 2-word in<br>Q2<br>No<br>operation                                                                                       | struction:<br>Q3<br>No<br>operation                                                                                                                                                                                                                                                  | operation<br>Q4<br>No<br>operation             |  |  |  |  |  |

| If skip and followe<br>Q1<br>No<br>operation<br>No                                                                              | A provided by 2-word in Q2<br>No<br>operation<br>No                                                                            | struction:<br>Q3<br>No<br>operation<br>No                                                                                                                                                                                                                                            | operation<br>Q4<br>No<br>operation<br>No       |  |  |  |  |  |

| If skip and followe<br>Q1<br>No<br>operation                                                                                    | ed by 2-word in<br>Q2<br>No<br>operation<br>No<br>operation<br>HERE<br>ZERO                                                    | struction:<br>Q3<br>No<br>operation<br>No<br>operation                                                                                                                                                                                                                               | operation<br>Q4<br>No<br>operation             |  |  |  |  |  |

| If skip and followe<br>Q1<br>No<br>operation<br>No<br>operation                                                                 | ed by 2-word in<br>Q2<br>No<br>operation<br>No<br>operation<br>HERE<br>ZERO<br>NZERO                                           | struction:<br>Q3<br>No<br>operation<br>No<br>operation<br>DCFSNZ TEM                                                                                                                                                                                                                 | Q4<br>Q4<br>No<br>operation<br>No<br>operation |  |  |  |  |  |

| If skip and followe<br>Q1<br>No<br>operation<br>No<br>operation<br>Example:<br>Before Instru<br>TEMP<br>After Instructi         | ed by 2-word in<br>Q2<br>No<br>operation<br>No<br>operation<br>HERE<br>ZERO<br>NZERO<br>Ction                                  | struction:<br>Q3<br>No<br>operation<br>No<br>operation<br>DCFSNZ TEM<br>:<br>:                                                                                                                                                                                                       | Q4<br>Q4<br>No<br>operation<br>No<br>operation |  |  |  |  |  |