Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3936 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6527-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name              | Pin Number     | Pin      | Buffer  | Description                                             |

|-----------------------|----------------|----------|---------|---------------------------------------------------------|

| Pin Name              | TQFP           | Туре     | Туре    | Description                                             |

|                       |                |          |         | PORTJ is a bidirectional I/O port.                      |

| RJ0/ALE<br>RJ0<br>ALE | 62             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory address latch enable.   |

| RJ1/OE<br>RJ1<br>OE   | 61             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory output enable.          |

| RJ2/WRL<br>RJ2<br>WRL | 60             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory write low control.      |

| RJ3/WRH<br>RJ3<br>WRH | 59             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory write high control.     |

| RJ4/BA0<br>RJ4<br>BA0 | 39             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory byte address 0 control. |

| RJ5/CE<br>RJ4<br>CE   | 40             | I/O<br>O | ST<br>— | Digital I/O<br>External memory chip enable control.     |

| RJ6/LB<br>RJ6<br>LB   | 41             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory low byte control.       |

| RJ7/UB<br>RJ7<br>UB   | 42             | I/O<br>O | ST<br>— | Digital I/O.<br>External memory high byte control.      |

| Vss                   | 11, 31, 51, 70 | Р        | _       | Ground reference for logic and I/O pins.                |

| Vdd                   | 12, 32, 48, 71 | Р        | —       | Positive supply for logic and I/O pins.                 |

| AVss                  | 26             | Р        | —       | Ground reference for analog modules.                    |

| AVdd                  | 25             | P<br>CMC | —       | Positive supply for analog modules.                     |

#### **TABLE 1-4**: PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels Analog= Analog input = Output

= Input Т Ο = Power Ρ

I<sup>2</sup>C<sup>™</sup>/SMB = I<sup>2</sup>C/SMBus input buffer

Note 1: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

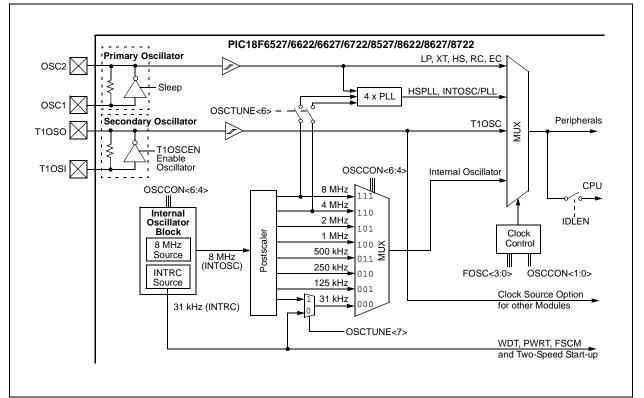

#### 2.7 Clock Sources and Oscillator Switching

The PIC18F8722 family of devices includes a feature that allows the device clock source to be switched from the main oscillator to an alternate clock source. These devices also offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary oscillators

- Secondary oscillators

- Internal oscillator block

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<3:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

The PIC18F8722 family of devices offers the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a real-time clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F8722 family of devices are shown in Figure 2-11. See **Section 25.0** "**Special Features of the CPU**" for Configuration register details.

FIGURE 2-11: PIC18F8722 FAMILY CLOCK DIAGRAM

| R/W-0                        | R/W-1 <sup>(1)</sup>                  | U-0                              | R/W-1                    | R-1               | R-1             | R/W-0 <sup>(2)</sup> | R/W-0       |

|------------------------------|---------------------------------------|----------------------------------|--------------------------|-------------------|-----------------|----------------------|-------------|

| IPEN                         | SBOREN                                | —                                | RI                       | TO                | PD              | POR                  | BOR         |

| bit 7                        |                                       |                                  |                          |                   |                 |                      | bit         |

|                              |                                       |                                  |                          |                   |                 |                      |             |

| <b>Legend:</b><br>R = Readat | hle hit                               | W = Writable                     | hit                      | II – I Inimpler   | nented bit, rea | ad as 'O'            |             |

| -n = Value a                 |                                       | '1' = Bit is se                  |                          | 0' = Bit is cle   |                 | x = Bit is unkn      | own         |

|                              |                                       |                                  |                          |                   |                 |                      | 0111        |

| bit 7                        | IPEN: Interru                         | pt Priority Ena                  | ble bit                  |                   |                 |                      |             |

|                              |                                       | iority levels or                 |                          |                   |                 |                      |             |

|                              |                                       |                                  |                          | IC16CXXX Co       | mpatibility mod | de)                  |             |

| bit 6                        |                                       | OR Software E                    | nable bit <sup>(1)</sup> |                   |                 |                      |             |

|                              | <u>If BOREN&lt;1:</u><br>1 = BOR is e |                                  |                          |                   |                 |                      |             |

|                              | 1 = BOR is ei0 = BOR is di            |                                  |                          |                   |                 |                      |             |

|                              | If BOREN<1:                           | 0> = <u>00, 10 or</u>            | <u>11:</u>               |                   |                 |                      |             |

|                              | Bit is disabled                       | d and read as '                  | 0'                       |                   |                 |                      |             |

| bit 5                        | Unimplemen                            | ted: Read as                     | '0'                      |                   |                 |                      |             |

| bit 4                        |                                       | struction Flag                   |                          |                   |                 |                      |             |

|                              |                                       |                                  |                          | ted (set by firm  | • /             |                      |             |

|                              |                                       | ET Instruction<br>ut Reset occur |                          | a causing a de    | vice Reset (n   | nust be set in so    | tware atter |

| bit 3                        |                                       | g Time-out Fla                   |                          |                   |                 |                      |             |

|                              |                                       | -                                | -                        | or SLEEP instr    | uction          |                      |             |

|                              |                                       | ime-out occurr                   |                          |                   |                 |                      |             |

| bit 2                        |                                       | own Detection                    | •                        |                   |                 |                      |             |

|                              |                                       | ower-up or by                    |                          |                   |                 |                      |             |

| <b>L</b> :L 4                |                                       | ecution of the                   |                          | ction             |                 |                      |             |

| bit 1                        |                                       |                                  |                          | (set by firmwar   |                 |                      |             |

|                              |                                       |                                  |                          |                   |                 | er-on Reset occur    | s)          |

| bit 0                        |                                       | out Reset Stat                   |                          |                   |                 |                      | ,           |

|                              | 1 = A Brown                           | -out Reset has                   | not occurred             | (set by firmwai   | e only)         |                      |             |

|                              | 0 = A Brown                           | -out Reset occ                   | urred (must b            | e set in softwar  | e after a Brow  | n-out Reset occu     | ırs)        |

| Note 1:                      | If SBOREN is ena                      | bled, its Reset                  | state is '1': ot         | herwise, it is '0 |                 |                      |             |

|                              | The actual Reset                      |                                  |                          |                   |                 | See the notes foll   | owing this  |

| r                            | register and Secti                    | on 4.6 "Reset                    | State of Reg             | isters" for add   | itional informa | ition.               | -           |

#### REGISTER 4-1: RCON: RESET CONTROL REGISTER

**Note 1:** It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after POR).

#### 5.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 6.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 8.0 "Data EEPROM Memory"**.

#### 5.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F6527 and PIC18F8527 each have 48 Kbytes of Flash memory and can store up to 24,576 single-word instructions.

The PIC18F6622 and PIC18F8622 each have 64 Kbytes of Flash memory and can store up to 32,768 single-word instructions.

The PIC18F6627 and PIC18F8627 each have 96 Kbytes of Flash memory and can store up to 49,152 single-word instructions.

The PIC18F6722 and PIC18F8722 each have 128 Kbytes of Flash memory and can store up to 65,536 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for the PIC18F8722 family of devices is shown in Figure 5-1.

#### 5.1.1 PIC18F8527/8622/8627/8722 PROGRAM MEMORY MODES

PIC18F8527/8622/8627/8722 devices differ significantly from their PIC18 predecessors in their utilization of program memory. In addition to available on-chip Flash program memory, these controllers can also address up to 2 Mbytes of external program memory through the external memory interface. There are four distinct operating modes available to the controllers:

- Microprocessor (MP)

- Microprocessor with Boot Block (MPBB)

- Extended Microcontroller (EMC)

- Microcontroller (MC)

The program memory mode is determined by setting the two Least Significant bits of the Configuration Register 3L (CONFIG3L) as shown in Register 25-4 (see **Section 25.1 "Configuration Bits**" for additional details on the device Configuration bits).

The program memory modes operate as follows:

- The Microprocessor Mode permits access only to external program memory; the contents of the on-chip Flash memory are ignored. The 21-bit program counter permits access to a 2-Mbyte linear program memory space.

- The Microprocessor with Boot Block Mode accesses on-chip Flash memory from the boot block. Above this, external program memory is accessed all the way up to the 2-Mbyte limit. Program execution automatically switches between the two memories as required. The boot block is configurable to 1, 2 or 4 Kbytes.

- The Microcontroller Mode accesses only on-chip Flash memory. Attempts to read above the physical limit of the on-chip Flash (0BFFFh for the PIC18F8527, 0FFFFh for the PIC18F8622, 17FFFh for the PIC18F8627, 1FFFFh for the PIC18F8722) causes a read of all '0's (a NOP instruction).

The Microcontroller mode is also the only operating mode available to PIC18F6527/6622/6627/6722 devices.

The Extended Microcontroller Mode allows access to both internal and external program memories as a single block. The device can access its entire on-chip Flash memory; above this, the device accesses external program memory up to the 2-Mbyte program space limit. As with Boot Block mode, execution automatically switches between the two memories as required.

In all modes, the microcontroller has complete access to data RAM and EEPROM.

Figure 5-2 compares the memory maps of the different program memory modes. The differences between on-chip and external memory access limitations are more fully explained in Table 5-1.

#### 5.4 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.5 "Data Memory and the Extended Instruction Set" for more information.

The data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.5.1 "Indexed Addressing with Literal Offset"**.

### 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.3 "General Purpose Register File") or a location in the Access Bank (Section 5.3.2 "Access Bank") as the data source for the instruction. The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 5.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

#### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

|         |       |            |   |                |

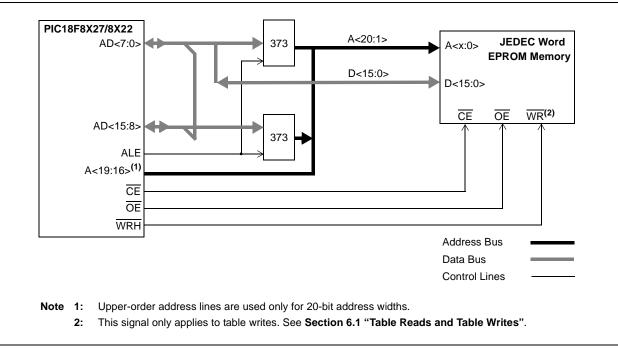

#### 7.5.2 16-BIT WORD WRITE MODE

Figure 7-2 shows an example of 16-bit Word Write mode for PIC18F8527/8622/8627/8722 devices. This mode is used for word-wide memories which includes some of the EPROM and Flash-type memories. This mode allows opcode fetches and table reads from all forms of 16-bit memory and table writes to any type of word-wide external memories. This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address (TBLPTR<0> = 0), the TABLAT data is transferred to a holding latch and the external address data bus is tri-stated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address (TBLPTR<0> = 1), the TABLAT data is presented on the upper byte of the AD15:AD0 bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus.

The WRH signal is strobed for each write cycle; the WRL pin is unused. The signal on the BA0 pin indicates the Least Significant bit of TBLPTR but it is left unconnected. Instead, the UB and LB signals are active to select both bytes. The obvious limitation to this method is that the table write must be done in pairs on a specific word boundary to correctly write a word location.

#### FIGURE 7-2: 16-BIT WORD WRITE MODE EXAMPLE

### 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:          |                                       |                                                                    |                                  |                      |  |  |  |  |

|------------------|---------------------------------------|--------------------------------------------------------------------|----------------------------------|----------------------|--|--|--|--|

| R = Readable b   | oit                                   | W = Writable bit                                                   | U = Unimplemented bit,           | , read as '0'        |  |  |  |  |

| -n = Value at P0 | OR                                    | '1' = Bit is set                                                   | '0' = Bit is cleared             | x = Bit is unknown   |  |  |  |  |

|                  |                                       |                                                                    |                                  |                      |  |  |  |  |

| bit 7            |                                       | 6-Bit Read/Write Mode Enab                                         |                                  |                      |  |  |  |  |

|                  |                                       | oles register read/write of Tir<br>oles register read/write of Tir |                                  |                      |  |  |  |  |

| bit 6            | T1RUN:                                | Timer1 System Clock Status                                         | bit                              |                      |  |  |  |  |

|                  |                                       | ce clock is derived from Tim<br>ce clock is derived from ano       |                                  |                      |  |  |  |  |

| bit 5-4          |                                       | <1:0>: Timer1 Input Clock P                                        |                                  |                      |  |  |  |  |

|                  |                                       | Prescale value                                                     |                                  |                      |  |  |  |  |

|                  | 10 = 1:4 Prescale value               |                                                                    |                                  |                      |  |  |  |  |

|                  | 01 = 1:2 Prescale value               |                                                                    |                                  |                      |  |  |  |  |

|                  | ••••••                                | Prescale value                                                     |                                  |                      |  |  |  |  |

| bit 3            | T1OSCEN: Timer1 Oscillator Enable bit |                                                                    |                                  |                      |  |  |  |  |

|                  |                                       | r1 oscillator is enabled                                           |                                  |                      |  |  |  |  |

|                  |                                       | er1 oscillator is shut off<br>oscillator inverter and feedba       | ack resistor are turned off to e | liminate power drain |  |  |  |  |

| bit 2            |                                       | : Timer1 External Clock Inpu                                       |                                  |                      |  |  |  |  |

|                  |                                       | /R1CS = 1:                                                         |                                  |                      |  |  |  |  |

|                  | 1 = Do no                             | ot synchronize external clock                                      | c input                          |                      |  |  |  |  |

|                  | 0 = Sync                              | hronize external clock input                                       |                                  |                      |  |  |  |  |

|                  |                                       | <u>/IR1CS = 0:</u>                                                 |                                  |                      |  |  |  |  |

|                  |                                       | •                                                                  | ternal clock when TMR1CS =       | = 0.                 |  |  |  |  |

| bit 1            |                                       | : Timer1 Clock Source Sele                                         |                                  |                      |  |  |  |  |

|                  |                                       | rnal clock from pin RC0/T1C<br>nal clock (Fosc/4)                  | SO/T13CKI (on the rising edg     | ge)                  |  |  |  |  |

| bit 0            | TMR10N                                | I: Timer1 On bit                                                   |                                  |                      |  |  |  |  |

|                  | 1 = Enal                              | oles Timer1                                                        |                                  |                      |  |  |  |  |

|                  | 0 = Stop                              | s Timer1                                                           |                                  |                      |  |  |  |  |

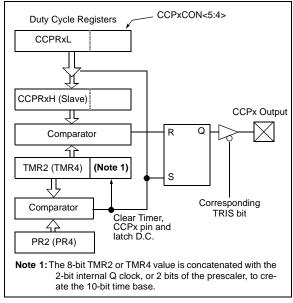

#### 17.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP4 and CCP5 pins are multiplexed with a PORTG data latch, the appropriate TRISG bit must be cleared to make the CCP4 or CCP5 pin an output.

| Note: | Clearing the CCP4CON or CCP5CON register will force the RG3 or RG4 output latch (depending on device configuration) |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       | to the default low level. This is not the PORTG I/O data latch.                                                     |

Figure 17-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up a CCP module for PWM operation, see **Section 17.4.3** "Setup for PWM Operation".

#### FIGURE 17-4: SIMPLIFIED PWM BLOCK DIAGRAM

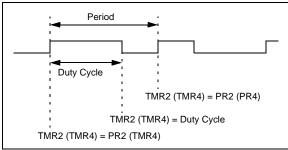

A PWM output (Figure 17-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 17-5: PWM OUTPUT

#### 17.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 (PR4) register. The PWM period can be calculated using the following formula:

#### EQUATION 17-1:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 (TMR4) is equal to PR2 (PR4), the following three events occur on the next increment cycle:

- TMR2 (TMR4) is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

- Note: The Timer2 and Timer 4 postscalers (see Section 14.0 "Timer2 Module" and Section 16.0 "Timer4 Module") are not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 17.4.2 PWM DUTY CYCLE

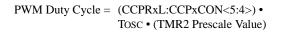

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> contains the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 17-2:**

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPRxH until after a match between PR2 (PR4) and TMR2 (TMR4) occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

#### **18.1 ECCP Outputs and Configuration**

Each of the Enhanced CCP modules may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are multiplexed with various I/O pins. Some ECCPx pin assignments are constant, while others change based on device configuration. For those pins that do change, the controlling bits are:

- CCP2MX Configuration bit (CONFIG3H<0>)

- ECCPMX Configuration bit (CONFIG3H<1>)

- Program Memory mode (set by Configuration bits, CONFIG3L<1:0>)

The pin assignments for the Enhanced CCP modules are summarized in Table 18-1, Table 18-2 and Table 18-3. To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxMx and CCPxMx bits (CCPxCON<7:6> and <3:0>, respectively). The appropriate TRIS direction bits for the corresponding port pins must also be set as outputs.

#### 18.1.1 USE OF CCP4 AND CCP5 WITH ECCP1 AND ECCP3

Only the ECCP2 module has four dedicated output pins available for use. Assuming that the I/O ports or other multiplexed functions on those pins are not needed, they may be used whenever needed without interfering with any other CCP module.

ECCP1 and ECCP3, on the other hand, only have three dedicated output pins: ECCPx/P3A, PxB and PxC. Whenever these modules are configured for Quad PWM mode, the pin used for CCP4 or CCP5 takes priority over the D output pins for ECCP3 and ECCP1, respectively.

#### 18.1.2 ECCP MODULE OUTPUTS, PROGRAM MEMORY MODES AND EMB ADDRESS BUS WIDTH

For PIC18F8527/8622/8627/8722 devices, the program memory mode of the device (Section 7.2 "Address and Data Width" and Section 7.4 "Program Memory Modes and the External Memory Bus") impacts both pin multiplexing and the operation of the module.

The ECCP2 input/output (ECCP2/P2A) can be multiplexed to one of three pins. By default, this is RC1 for all devices; in this case, the default is in effect when CCP2MX is set and the device is operating in Microcontroller mode. With PIC18F8527/8622/8627/8722 devices, three other options exist. When CCP2MX is not set (= 0) and the device is in Microcontroller mode, ECCP2/P2A is multiplexed to RE7; in all other program memory modes, it is multiplexed to RB3.

Another option is for ECCPMX to be set while the device is operating in one of the three other program memory modes. In this case, ECCP1 and ECCP3 operate as compatible (i.e., single output) CCP modules. The pins used by their other outputs (PxB through PxD) are available for other multiplexed functions. ECCP2 continues to operate as an Enhanced CCP module regardless of the program memory mode.

The final option is that the ABW<1:0> Configuration bits can be used to select 8, 12, 16 or 20-bit EMB addressing. Pins not assigned to EMB address pins are available for peripheral or port functions.

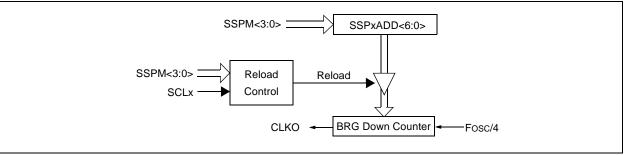

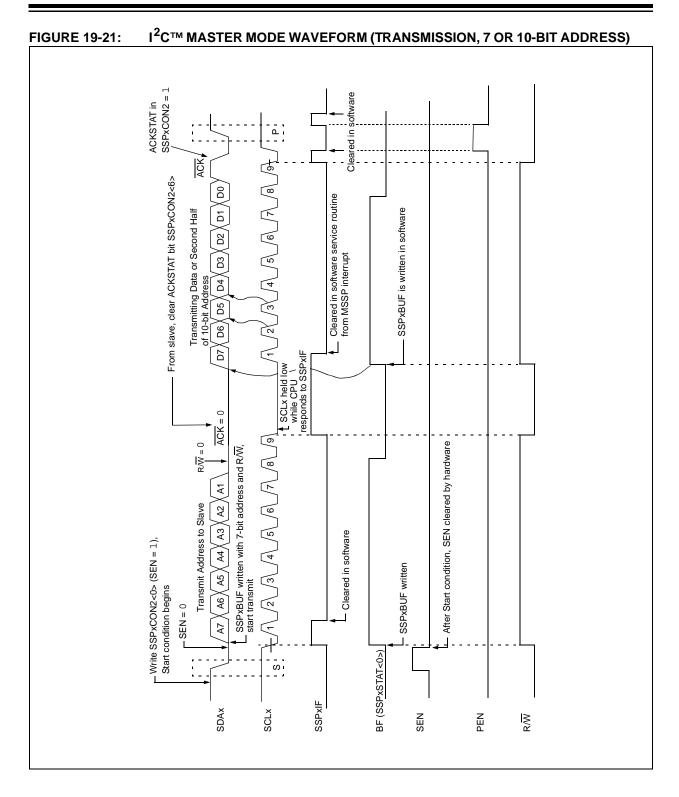

#### 19.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 19-17). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to '0' and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 19-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

#### 19.4.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

#### TABLE 19-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy*2  | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|--------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz | 18h       | 400 kHz <sup>(1)</sup>       |

| 40 MHz | 10 MHz | 20 MHz | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz  | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz | 4 MHz  | 8 MHz  | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz  | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz  | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz  | 1 MHz  | 2 MHz  | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz  | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

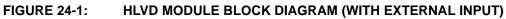

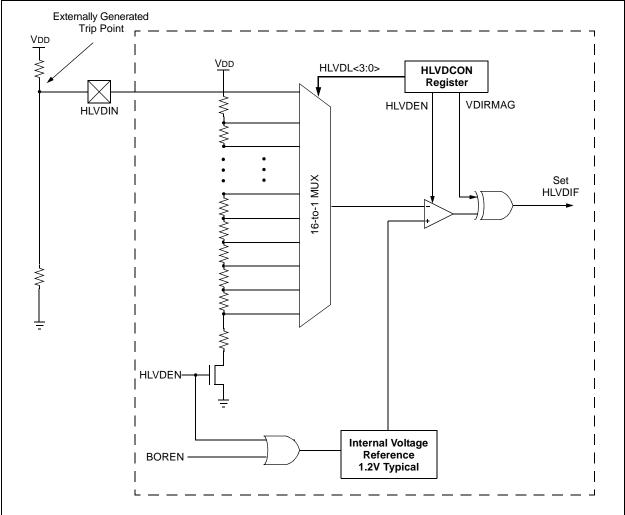

The module is enabled by setting the HLVDEN bit. Each time that the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit and is used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

#### 24.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits HLVDL<3:0> are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

#### 25.0 SPECIAL FEATURES OF THE CPU

The PIC18F8722 family of devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, the PIC18F8722 family of devices has a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

#### 25.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device Configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

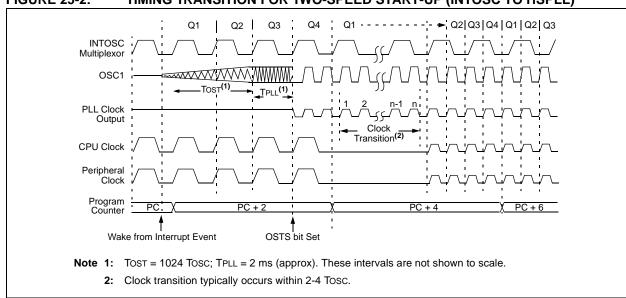

#### 25.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits IRCF<2:0> immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:0> bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 25.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 3.1.4 "Multiple Sleep Commands**"). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### FIGURE 25-2: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

| COMF                 | Complemen                                                    | nt f                                                                                                               |                                | CPFS        | EQ                                     | Compare f                    | with W, Skip                                                                        | if f = W       |

|----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|----------------------------------------|------------------------------|-------------------------------------------------------------------------------------|----------------|

| Syntax:              | COMF f {,                                                    | d {,a}}                                                                                                            |                                | Synta       | x:                                     | CPFSEQ                       | f {,a}                                                                              |                |

| Operands:            | $0 \le f \le 255$                                            |                                                                                                                    |                                | Opera       | inds:                                  | $0 \leq f \leq 255$          |                                                                                     |                |

|                      | d ∈ [0,1]                                                    |                                                                                                                    |                                | -           |                                        | a ∈ [0,1]                    |                                                                                     |                |

|                      | a ∈ [0,1]                                                    |                                                                                                                    |                                | Opera       | ition:                                 | (f) – (W),<br>skip if (f) =  | (\\\/)                                                                              |                |

| Operation:           | (f) $\rightarrow$ dest                                       | t                                                                                                                  |                                |             |                                        | • • • • •                    | comparison)                                                                         |                |

| Status Affected:     | N, Z                                                         |                                                                                                                    |                                | Status      | Affected:                              | None                         | . ,                                                                                 |                |

| Encoding:            | 0001                                                         | 11da ffi                                                                                                           | ff ffff                        | Encod       | ling:                                  | 0110                         | 001a ff:                                                                            | ff ffff        |

| Description:         | The contents<br>complemente<br>stored in W.<br>stored back i | ed. If 'd' is '0'<br>If 'd' is '1', th                                                                             | , the result is<br>e result is | Descr       | iption:                                | location 'f' t<br>performing | o the contents<br>an unsigned s                                                     | ubtraction.    |

|                      | If 'a' is '1', the                                           | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default). |                                |             |                                        | discarded a                  | en the fetchec<br>and a NOP is ex<br>aking this a two                               | kecuted        |

|                      |                                                              | d, this instruction                                                                                                | 0                              |             |                                        | ,                            | he Access Bai<br>he BSR is use<br>(default).                                        |                |

|                      | Section 26.2<br>Bit-Oriented                                 | 2.3 "Byte-Ori                                                                                                      | iented and<br>s in Indexed     |             |                                        | set is enabl<br>in Indexed   | nd the extende<br>led, this instruct<br>Literal Offset $A$<br>never f $\leq$ 95 (5) | ction operates |

| Words:               | 1                                                            |                                                                                                                    |                                |             |                                        |                              | .2.3 "Byte-Or                                                                       | ,              |

| Cycles:              | 1                                                            |                                                                                                                    |                                |             |                                        |                              | d Instruction                                                                       |                |

| Q Cycle Activity:    |                                                              |                                                                                                                    |                                | 10/         |                                        |                              | set Mode" for                                                                       | details.       |

| Q1                   | Q2                                                           | Q3                                                                                                                 | Q4                             | Words       |                                        | 1                            |                                                                                     |                |

| Decode               | Read<br>register 'f'                                         | Process<br>Data                                                                                                    | Write to destination           | Cycle       | 5.                                     | •                            | cles if skip and<br>2-word instrue                                                  |                |

| E                    |                                                              |                                                                                                                    |                                | Q Cy        | cle Activity:                          |                              |                                                                                     |                |

| Example:             |                                                              | REG, 0, 0                                                                                                          |                                | -           | Q1                                     | Q2                           | Q3                                                                                  | Q4             |

| Before Instru<br>REG | uction<br>= 13h                                              |                                                                                                                    |                                |             | Decode                                 | Read                         | Process                                                                             | No             |

| After Instruc        |                                                              |                                                                                                                    |                                | lf ski      | <b>.</b> .                             | register 'f'                 | Data                                                                                | operation      |

| REG<br>W             | = 13h<br>= ECh                                               |                                                                                                                    |                                |             | Q1                                     | Q2                           | Q3                                                                                  | Q4             |

| •••                  | - 2011                                                       |                                                                                                                    |                                |             | No                                     | No                           | No                                                                                  | No             |

|                      |                                                              |                                                                                                                    |                                | 16 - 1 -    | operation                              | operation                    | operation                                                                           | operation      |

|                      |                                                              |                                                                                                                    |                                | IT SKI      |                                        | d by 2-word in<br>Q2         | Q3                                                                                  | Q4             |

|                      |                                                              |                                                                                                                    |                                | Г           | No                                     | No                           | No                                                                                  | No             |

|                      |                                                              |                                                                                                                    |                                |             | operation                              | operation                    | operation                                                                           | operation      |

|                      |                                                              |                                                                                                                    |                                |             | No                                     | No                           | No                                                                                  | No             |

|                      |                                                              |                                                                                                                    |                                | <u>Exam</u> | operation<br>ple:                      | OPERATION<br>HERE<br>NEQUAL  | OPFSEQ REG                                                                          | operation      |

|                      |                                                              |                                                                                                                    |                                |             |                                        | EQUAL                        | :                                                                                   |                |

|                      |                                                              |                                                                                                                    |                                |             | Before Instruct<br>PC Addr<br>W<br>REG | ESS = HE<br>= ?<br>= ?       | RE                                                                                  |                |

After Instruction If REG PC If REG PC

= ≠ W; Address (EQUAL) W; Address (NEQUAL)

| DAW                   | Decimal A                                                                                                                                                                                                                                                                  | djust W Regis              | ster       | DECF                  | Decremen                 | t f                                 |                 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|-----------------------|--------------------------|-------------------------------------|-----------------|

| Syntax:               | DAW                                                                                                                                                                                                                                                                        |                            |            | Syntax:               | DECF f{,                 | d {,a}}                             |                 |

| Operands:             | None                                                                                                                                                                                                                                                                       |                            |            | Operands:             | $0 \leq f \leq 255$      |                                     |                 |

| Operation:            | ds: None   on: If $[W<3:0>> 9]$ or $[DC = 1]$ then $(W<3:0>) + 6 \rightarrow W<3:0>;$ else $(W<3:0>) \rightarrow W<3:0>$ If $[W<7:4>> 9]$ or $[C = 1]$ then $(W<7:4>) + 6 \rightarrow W<7:4>;$ C = 1; else $(W<7:4>) \rightarrow W<7:4>$ offected: C   org: 0000 0000 0111 |                            | ] then     |                       | d ∈ [0,1]                |                                     |                 |

|                       | . ,                                                                                                                                                                                                                                                                        | $6 \rightarrow W < 3:0>;$  |            | On another            | a ∈ [0,1]                |                                     |                 |

|                       |                                                                                                                                                                                                                                                                            | → W<3:0>                   |            | Operation:            | $(f) - 1 \rightarrow de$ |                                     |                 |

|                       | (11 10107)                                                                                                                                                                                                                                                                 |                            |            | Status Affected:      | C, DC, N, (              |                                     |                 |

|                       |                                                                                                                                                                                                                                                                            |                            |            | Encoding:             | 0000                     |                                     | ff fff          |

|                       |                                                                                                                                                                                                                                                                            | $b \rightarrow VV < 7:4>;$ |            | Description:          |                          | register 'f'. If<br>red in W. If 'd |                 |

|                       |                                                                                                                                                                                                                                                                            |                            |            |                       |                          | red back in re                      | ,               |

|                       | (W<7:4>) –                                                                                                                                                                                                                                                                 | → W<7:4>                   |            |                       | (default).               |                                     | 0               |

| Status Affected:      | С                                                                                                                                                                                                                                                                          |                            |            |                       |                          | he Access Ba                        |                 |

| Encoding:             | 0000                                                                                                                                                                                                                                                                       | 0000 000                   | 00 0111    |                       |                          | he BSR is use                       | ed to select th |

| Description:          | •                                                                                                                                                                                                                                                                          | -                          |            |                       | GPR bank                 |                                     | lad in atruatio |

|                       | •                                                                                                                                                                                                                                                                          |                            |            |                       |                          | nd the extend<br>led, this instru   |                 |

|                       |                                                                                                                                                                                                                                                                            | es a correct pa            |            |                       | in Indexed               | Literal Offset                      | Addressing      |

|                       | result.                                                                                                                                                                                                                                                                    |                            |            |                       |                          | hever $f \le 95$ (5                 | ,               |

| Words:                | 1                                                                                                                                                                                                                                                                          |                            |            |                       |                          | .2.3 "Byte-Or<br>d Instruction      |                 |

| Cycles:               | 1                                                                                                                                                                                                                                                                          |                            |            |                       | Literal Off              | set Mode" for                       | details.        |

| Q Cycle Activity:     |                                                                                                                                                                                                                                                                            |                            |            | Words:                | 1                        |                                     |                 |

| Q1                    | Q2                                                                                                                                                                                                                                                                         | Q3                         | Q4         | Cycles:               | 1                        |                                     |                 |

| Decode                | Read<br>register W                                                                                                                                                                                                                                                         | Process<br>Data            | Write<br>W | Q Cycle Activity:     |                          |                                     |                 |

|                       | legister w                                                                                                                                                                                                                                                                 | Dala                       | ~~~        | Q1                    | Q2                       | Q3                                  | Q4              |

| Example 1:            | DAW                                                                                                                                                                                                                                                                        |                            |            | Decode                | Read                     | Process                             | Write to        |

| Before Instruc        | tion                                                                                                                                                                                                                                                                       |                            |            |                       | register 'f'             | Data                                | destination     |

| W<br>C                | = A5h<br>= 0                                                                                                                                                                                                                                                               |                            |            | Example:              | DECF                     | CNT, 1, 0                           | h               |

| DC                    | = 0                                                                                                                                                                                                                                                                        |                            |            | Before Instru         |                          | CN1, 1, C                           | )               |

| After Instruction     |                                                                                                                                                                                                                                                                            |                            |            | CNT                   | = 01h                    |                                     |                 |

| W<br>C                | = 05h<br>= 1                                                                                                                                                                                                                                                               |                            |            | Z                     | = 0                      |                                     |                 |

| DC                    | = 0                                                                                                                                                                                                                                                                        |                            |            | After Instruct<br>CNT | = 00h                    |                                     |                 |

| Example 2:            |                                                                                                                                                                                                                                                                            |                            |            | Z                     | = 1                      |                                     |                 |

| Before Instruc        |                                                                                                                                                                                                                                                                            |                            |            |                       |                          |                                     |                 |

| W<br>C                | = CEh<br>= 0                                                                                                                                                                                                                                                               |                            |            |                       |                          |                                     |                 |

| DC                    | = 0                                                                                                                                                                                                                                                                        |                            |            |                       |                          |                                     |                 |

| After Instructio<br>W | on<br>= 34h                                                                                                                                                                                                                                                                |                            |            |                       |                          |                                     |                 |

| ••                    | = 1                                                                                                                                                                                                                                                                        |                            |            |                       |                          |                                     |                 |

| C<br>DC               | = 0                                                                                                                                                                                                                                                                        |                            |            |                       |                          |                                     |                 |