Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

|                            |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 48KB (24K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3936 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6527t-i-pt |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                               | Pin Number | Pin           | Buffer                 | Description                                                              |

|----------------------------------------|------------|---------------|------------------------|--------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре                   | Description                                                              |

|                                        |            |               |                        | PORTF is a bidirectional I/O port.                                       |

| RF0/AN5<br>RF0<br>AN5                  | 18         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 5.                                          |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 17         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 6.<br>Comparator 2 output.                  |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 16         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 7.<br>Comparator 1 output.                  |

| RF3/AN8<br>RF3<br>AN8                  | 15         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 8.                                          |

| RF4/AN9<br>RF4<br>AN9                  | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 9.                                          |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 13         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog input 10.<br>Comparator reference voltage output. |

| RF6/AN11<br>RF6<br>AN11                | 12         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 11.                                         |

| RF7/SS1<br>RF7<br>SS1                  | 11         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                  |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog= Analog input I = Input O = Output

P = Power  $I^2C^{TM}$  =  $I^2C/SMBus$  input buffer

Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

### REGISTER 10-2: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-1 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  | R/W-1 |

|-------|---------|---------|---------|---------|--------|--------|-------|

| RBPU  | INTEDG0 | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP  |

| bit 7 | •       |         |         |         |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RBPU: PORTB Pull-up Enable bit

1 = All PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG0: External Interrupt 0 Edge Select bit

1 = Interrupt on rising edge0 = Interrupt on falling edge

bit 5 INTEDG1: External Interrupt 1 Edge Select bit

1 = Interrupt on rising edge0 = Interrupt on falling edge

bit 4 INTEDG2: External Interrupt 2 Edge Select bit

1 = Interrupt on rising edge0 = Interrupt on falling edge

bit 3 INTEDG3: External Interrupt 3 Edge Select bit

1 = Interrupt on rising edge0 = Interrupt on falling edge

bit 2 TMR0IP: TMR0 Overflow Interrupt Priority bit

1 = High priority0 = Low priority

bit 1 INT3IP: INT3 External Interrupt Priority bit

1 = High priority0 = Low priority

bit 0 RBIP: RB Port Change Interrupt Priority bit

1 = High priority0 = Low priority

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits

are clear prior to enabling an interrupt. This feature allows for software polling.

### REGISTER 10-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| R/W-1  | R/W-1 | U-0 | R/W-1 | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-------|-----|-------|--------|--------|--------|--------|

| OSCFIP | CMIP  | _   | EEIP  | BCL1IP | HLVDIP | TMR3IP | CCP2IP |

| bit 7  |       |     |       |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIP: Oscillator Fail Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 CMIP: Comparator Interrupt Priority bit

1 = High priority0 = Low priority

bit 5 **Unimplemented:** Read as '0'

bit 4 **EEIP:** Interrupt Priority bit

1 = High priority0 = Low priority

bit 3 BCL1IP: MSSP1 Bus Collision Interrupt Priority bit

1 = High priority0 = Low priority

bit 2 **HLVDIP:** High/Low-Voltage Detect Interrupt Priority bit

1 = High priority0 = Low priority

bit 1 TMR3IP: TMR3 Overflow Interrupt Priority bit

1 = High priority0 = Low priority

bit 0 CCP2IP: ECCP2 Interrupt Priority bit

1 = High priority0 = Low priority

TABLE 11-1: PORTA FUNCTIONS

| Pin Name       | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                              |  |  |  |

|----------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0        | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                       |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                 |  |  |  |

|                | AN0      | 1               | I   | ANA         | A/D input channel 0. Default input configuration on POR; does not affect digital output. |  |  |  |

| RA1/AN1        | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                       |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                 |  |  |  |

|                | AN1      | 1               | I   | ANA         | A/D input channel 1. Default input configuration on POR; does not affect digital output. |  |  |  |

| RA2/AN2/VREF-  | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input.                                       |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<2> data input. Disabled when analog functions enabled.                             |  |  |  |

|                | AN2      | 1               | I   | ANA         | A/D input channel 2. Default input configuration on POR.                                 |  |  |  |

|                | VREF-    | 1               | I   | ANA         | Comparator voltage reference low input and A/D voltage reference low input.              |  |  |  |

| RA3/AN3/VREF+  | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                       |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                 |  |  |  |

|                | AN3      | 1               | I   | ANA         | A A/D input channel 3. Default input configuration on POR.                               |  |  |  |

|                | VREF+    | 1               | I   | ANA         | Comparator voltage reference high input and A/D voltage reference high input.            |  |  |  |

| RA4/T0CKI      | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                     |  |  |  |

|                |          | 1               | I   | ST          | PORTA<4> data input; default configuration on POR.                                       |  |  |  |

|                | T0CKI    | х               | I   | ST          | Timer0 clock input.                                                                      |  |  |  |

| RA5/AN4/HLVDIN | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                       |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                 |  |  |  |

|                | AN4      | 1               | I   | ANA         | A/D input channel 4. Default configuration on POR.                                       |  |  |  |

|                | HLVDIN   | 1               | I   | ANA         | High/Low-Voltage Detect external trip point input.                                       |  |  |  |

| OSC2/CLKO/RA6  | OSC2     | х               | 0   | ANA         | Main oscillator feedback output connection (XT, HS, HSPLL and LP modes).                 |  |  |  |

|                | CLKO     | х               | 0   | DIG         | System cycle clock output (Fosc/4) in all oscillator modes except RC, INTIO7 and EC.     |  |  |  |

|                | RA6      | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                        |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                        |  |  |  |

| OSC1/CLKI/RA7  | OSC1     | х               | I   | ANA         | Main oscillator input connection.                                                        |  |  |  |

|                | CLKI     | х               | I   | ANA         | Main clock input connection.                                                             |  |  |  |

|                | RA7      | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                              |  |  |  |

|                |          | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                              |  |  |  |

**Legend:** PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST= Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 61                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 60                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 60                         |

| ADCON1 | _                     | _                     | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 59                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

TABLE 11-3: PORTB FUNCTIONS

| Pin Name      | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                               |

|---------------|----------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT0/FLT0 | RB0                  | 0               | 0   | DIG         | LATB<0> data output.                                                                                                                      |

|               |                      | 1               | ı   | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | INT0                 | 1               | ı   | ST          | External interrupt 0 input.                                                                                                               |

|               | FLT0                 | 1               | ı   | ST          | ECCPx PWM Fault input, enabled in software.                                                                                               |

| RB1/INT1      | RB1                  | 0               | 0   | DIG         | LATB<1> data output.                                                                                                                      |

|               |                      | 1               | I   | TTL         | PORTB<1> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | INT1                 | 1               | I   | ST          | External interrupt 1 input.                                                                                                               |

| RB2/INT2      | RB2                  | 0               | 0   | DIG         | LATB<2> data output.                                                                                                                      |

|               |                      | 1               | I   | TTL         | PORTB<2> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | INT2                 | 1               | I   | ST          | External interrupt 2 input.                                                                                                               |

| RB3/INT3/     | RB3                  | 0               | 0   | DIG         | LATB<3> data output.                                                                                                                      |

| ECCP2/P2A     |                      | 1               | I   | TTL         | PORTB<3> data input; weak pull-up when RBPU bit is cleared and capture input is disabled.                                                 |

|               | INT3                 | 1               | I   | ST          | External interrupt 3 input.                                                                                                               |

|               | ECCP2 <sup>(1)</sup> | 0               | 0   | DIG         | ECCP2 compare output and ECCP2 PWM output. Takes priority over port data.                                                                 |

|               |                      | 1               | I   | ST          | ECCP2 capture input.                                                                                                                      |

|               | P2A <sup>(1)</sup>   | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RB4/KBI0      | RB4                  | 0               | 0   | DIG         | LATB<4> data output.                                                                                                                      |

|               |                      | 1               | I   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | KBI0                 | 1               | ı   | TTL         | Interrupt-on-pin change.                                                                                                                  |

| RB5/KBI1/PGM  | RB5                  | 0               | 0   | DIG         | LATB<5> data output                                                                                                                       |

|               |                      | 1               | I   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | KBI1                 | 1               | ı   | TTL         | Interrupt-on-pin change.                                                                                                                  |

|               | PGM                  | х               | I   | ST          | Single-Supply Programming mode entry (ICSP). Enabled by LVP Configuration bit; all other pin functions disabled.                          |

| RB6/KBI2/PGC  | RB6                  | 0               | 0   | DIG         | LATB<6> data output.                                                                                                                      |

|               |                      | 1               | I   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | KBI2                 | 1               | ı   | TTL         | Interrupt-on-pin change.                                                                                                                  |

|               | PGC                  | х               | I   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operation (2).                                                                      |

| RB7/KBI3/PGD  | RB7                  | 0               | 0   | DIG         | LATB<7> data output.                                                                                                                      |

|               |                      | 1               | I   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                               |

|               | KBI3                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                  |

|               | PGD                  | х               | 0   | DIG         | Serial execution data output for ICSP and ICD operation <sup>(2)</sup> .                                                                  |

|               |                      | х               | I   | ST          | Serial execution data input for ICSP and ICD operation <sup>(2)</sup> .                                                                   |

**Legend:** PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

2: All other pin functions are disabled when ICSP or ICD operations are enabled.

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared (Microprocessor, Extended Microcontroller and Microcontroller with Boot Block modes, 80-pin devices only). Default assignment is RC1.

### 12.0 TIMERO MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable prescaler

- · Selectable clock source (internal or external)

- · Edge select for external clock

- · Interrupt-on-overflow

The TOCON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | T0CS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | TMR0ON: Timer0 On/Off Contro | l bit |

|-------|------------------------------|-------|

|       |                              |       |

1 = Enables Timer00 = Stops Timer0

bit 6 T08BIT: Timer0 8-bit/16-bit Control bit

1 = Timer0 is configured as an 8-bit timer/counter 0 = Timer0 is configured as a 16-bit timer/counter

bit 5 Tocs: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

bit 3 PSA: Timer0 Prescaler Assignment bit

1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.

bit 2-0 T0PS<2:0>: Timer0 Prescaler Select bits

111 = 1:256 Prescale value

110 = 1:128 Prescale value

101 = 1:64 Prescale value

100 = 1:32 Prescale value

011 = 1:16 Prescale value

010 = 1:8 Prescale value

001 = 1:4 Prescale value

000 = 1:2 Prescale value

NOTES:

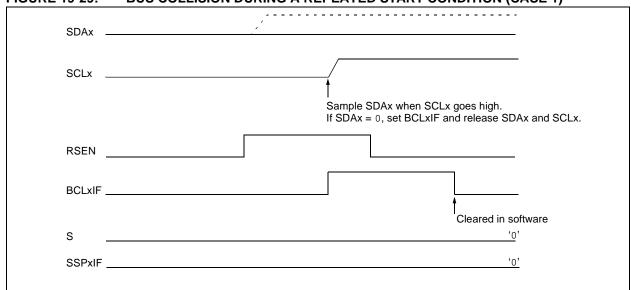

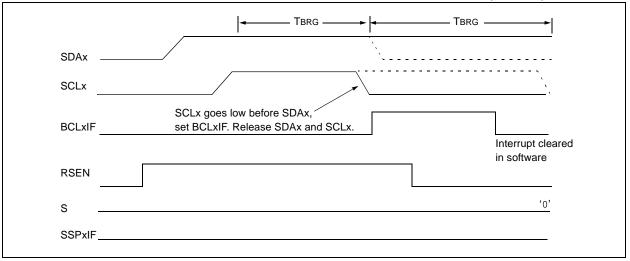

## 19.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- A low level is sampled on SDAx when SCLx goes from low level to high level.

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to '0'. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 19-29). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 19-30).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

FIGURE 19-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 19-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

### REGISTER 20-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|-------|-------|-------|-------|-------|------|------|-------|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| bit 7 |       |       |       |       |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RXx/DTx and TXx/CKx pins as serial port pins)

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-bit Receive Enable bit

1 = Selects 9-bit reception0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care.

Synchronous mode - Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode – Slave:

Don't care.

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enables interrupt and loads the receive buffer when RSRx<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 9-bit (RX9 = 0):

Don't care.

bit 2 **FERR:** Framing Error bit

1 = Framing error (can be updated by reading RCREGx register and receiving next valid byte)

0 = No framing error

bit 1 OERR: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** 9th bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

### 21.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 21-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor Chold. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

Note:

When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 21-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 21-3 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions:

CHOLD = 25 pF Rs =  $2.5 \text{ k}\Omega$ Conversion Error  $\leq$  1/2 LSb

VDD =  $5V \rightarrow Rss = 2 \text{ k}\Omega$ Temperature =  $85^{\circ}\text{C}$  (system max.)

### **EQUATION 21-1: ACQUISITION TIME**

```

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

```

### **EQUATION 21-2: A/D MINIMUM CHARGING TIME**

```

\begin{array}{lll} V_{HOLD} & = & (V_{REF} - (V_{REF}/2048)) \bullet (1 - e^{(-T_{C}/C_{HOLD}(R_{IC} + R_{SS} + R_{S}))}) \\ \text{or} \\ T_{C} & = & -(C_{HOLD})(R_{IC} + R_{SS} + R_{S}) \ln(1/2048) \end{array}

```

### **EQUATION 21-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME**

```

TACQ = TAMP + TC + TCOFF  TAMP = 0.2 μs  TCOFF = (Temp - 25^{\circ}C)(0.02 \text{ μs/°C})  (85°C - 25°C)(0.02 μs/°C) 1.2 μs  Temperature coefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 ms.  TC  = -(CHOLD)(RIC + Rss + Rs) \ln(1/2047) \text{ μs}  -(25 pF) (1 kΩ + 2 kΩ + 2.5 kΩ) \ln(0.0004883) \text{ μs}  1.05 μs  TACQ = 0.2 \text{ μs} + 1 \text{ μs} + 1.2 \text{ μs}  2.4 μs

```

### 24.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18F8722 family of devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

Legend:

R = Readable bit

High/Low-Voltage Detect Control register The (Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 24-1.

### REGISTER 24-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

W = Writable bit

| R/W-0   | U-0 | R-0   | R/W-0  | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

|---------|-----|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | _   | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |     |       |        |                       |                       |                       | bit 0                 |

U = Unimplemented bit, read as '0'

| -n = Value at | POR                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                              | '0' = Bit is cleared            | x = Bit is unknown |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|--------------------|--|--|--|--|

| bit 7         | VDIRMAG                                                                                                                                                                                                                                                                                               | 3: Voltage Direction Magn                     | itude Select bit                |                    |  |  |  |  |

|               | 1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>) 0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>)                                                                                                                                                   |                                               |                                 |                    |  |  |  |  |

| bit 6         | Unimplen                                                                                                                                                                                                                                                                                              | nented: Read as '0'                           |                                 |                    |  |  |  |  |

| bit 5         | IRVST: Int                                                                                                                                                                                                                                                                                            | ternal Reference Voltage                      | Stable Flag bit                 |                    |  |  |  |  |

|               | <ul> <li>1 = Indicates that the voltage detect logic will generate the interrupt flag at the specified voltage range</li> <li>0 = Indicates that the voltage detect logic will not generate the interrupt flag at the specified voltage range and the HLVD interrupt should not be enabled</li> </ul> |                                               |                                 |                    |  |  |  |  |

| bit 4         | HLVDEN:<br>1 = HLVD<br>0 = HLVD                                                                                                                                                                                                                                                                       |                                               | Power Enable bit                |                    |  |  |  |  |

| bit 3-0       | HLVDL<3                                                                                                                                                                                                                                                                                               | :0>: Voltage Detection Lir                    | mit bits <sup>(1)</sup>         |                    |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                       | kternal analog input is use<br>aximum setting | ed (input comes from the HLVDIN | l pin)             |  |  |  |  |

|               | ·<br>·                                                                                                                                                                                                                                                                                                |                                               |                                 |                    |  |  |  |  |

Note 1: See Table 28-4 for specifications.

0000 = Minimum setting

MOVLW Move Literal to W Syntax: MOVLW k Operands:  $0 \le k \le 255$ Operation:  $\mathsf{k}\to\mathsf{W}$ Status Affected: None Encoding: 0000 1110 kkkk kkkk Description: The eight-bit literal 'k' is loaded into W. Words: Cycles:

Q Cycle Activity:

| Q1     | Q2          | Q3      | Q4       |

|--------|-------------|---------|----------|

| Decode | Read        | Process | Write to |

|        | literal 'k' | Data    | W        |

Example: MOVLW 5Ah

After Instruction

W = 5Ah

| MOVWF            | Move W to f                                                                          |        |      |      |  |  |

|------------------|--------------------------------------------------------------------------------------|--------|------|------|--|--|

| Syntax:          | MOVWF                                                                                | f {,a} |      |      |  |  |

| Operands:        | $0 \le f \le 255$<br>a $\in [0,1]$                                                   |        |      |      |  |  |

| Operation:       | $(W) \to f$                                                                          |        |      |      |  |  |

| Status Affected: | None                                                                                 |        |      |      |  |  |

| Encoding:        | 0110                                                                                 | 111a   | ffff | ffff |  |  |

| Description:     | Move data from W to register 'f'. Location 'f' can be anywhere in the 256-byte bank. |        |      |      |  |  |

If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See

If 'a' is '0', the Access Bank is selected.

Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: MOVWF REG, 0

Before Instruction

W = 4Fh REG = FFh

After Instruction

W = 4FhREG = 4Fh 28.2 DC Characteristics: Power-Down and Supply Current

PIC18F6X27/6X22/8X27/8X22 (Industrial, Extended) PIC18LF6X27/6X22/8X27/8X22 (Industrial) (Continued)

| (Industrial) |                                     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial                                                                         |     |       |        |            |                                       |  |

|--------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|------------|---------------------------------------|--|

|              |                                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |       |        |            |                                       |  |

| Param<br>No. | Device                              | Тур                                                                                                                                                                                                                                 | Max | Units |        | Conditi    | ons                                   |  |

|              | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                                                                     |     |       |        |            |                                       |  |

|              | PIC18LF6X27/6X22/8X27/8X22          | 1.0                                                                                                                                                                                                                                 | 1.3 | mA    | -40°C  |            |                                       |  |

|              |                                     | 1.0                                                                                                                                                                                                                                 | 1.3 | mA    | +25°C  | VDD = 2.0V |                                       |  |

|              |                                     | 1.0                                                                                                                                                                                                                                 | 1.3 | mA    | +85°C  |            |                                       |  |

|              | PIC18LF6X27/6X22/8X27/8X22          | 1.6                                                                                                                                                                                                                                 | 1.9 | mA    | -40°C  |            |                                       |  |

|              |                                     | 1.6                                                                                                                                                                                                                                 | 1.9 | mA    | +25°C  | VDD = 3.0V | FOSC = 4 MHz<br>( <b>RC_RUN</b> mode, |  |

|              |                                     | 1.6                                                                                                                                                                                                                                 | 1.9 | mA    | +85°C  |            | Internal oscillator source)           |  |

|              | All devices                         | 3.0                                                                                                                                                                                                                                 | 3.5 | mA    | -40°C  |            | ,                                     |  |

|              |                                     | 3.0                                                                                                                                                                                                                                 | 3.4 | mA    | +25°C  | VDD = 5.0V |                                       |  |

|              |                                     | 3.0                                                                                                                                                                                                                                 | 3.4 | mA    | +85°C  | VDD = 3.0V |                                       |  |

|              | Extended devices only               | 3.0                                                                                                                                                                                                                                 | 3.4 | mA    | +125°C |            |                                       |  |

|              | PIC18LF6X27/6X22/8X27/8X22          | 3.5                                                                                                                                                                                                                                 | 5   | μΑ    | -40°C  |            |                                       |  |

|              |                                     | 3.7                                                                                                                                                                                                                                 | 5   | μΑ    | +25°C  | VDD = 2.0V |                                       |  |

|              |                                     | 4.3                                                                                                                                                                                                                                 | 9.5 | μΑ    | +85°C  |            |                                       |  |

|              | PIC18LF6X27/6X22/8X27/8X22          | 5.4                                                                                                                                                                                                                                 | 7   | μΑ    | -40°C  |            |                                       |  |

|              |                                     | 5.7                                                                                                                                                                                                                                 | 8   | μΑ    | +25°C  | VDD = 3.0V | FOSC = 31 kHz (RC IDLE mode,          |  |

|              |                                     | 7.0                                                                                                                                                                                                                                 | 15  | μΑ    | +85°C  |            | Internal oscillator source)           |  |

|              | All devices                         | 11                                                                                                                                                                                                                                  | 15  | μΑ    | -40°C  |            |                                       |  |

|              |                                     | 11.8                                                                                                                                                                                                                                | 15  | μΑ    | +25°C  | VDD = 5.0V | \/DD - F 0\/                          |  |

|              |                                     | 13.5                                                                                                                                                                                                                                | 35  | μΑ    | +85°C  | VDD = 5.0V |                                       |  |

|              | Extended devices only               | 25                                                                                                                                                                                                                                  | 200 | μΑ    | +125°C |            |                                       |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\frac{\text{OSC1}}{\text{MCLR}}$  = external square wave, from rail-to-rail, all I/O pins tri-stated, pulled to VDD OR VSS;  $\frac{\text{MCLR}}{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

- 3: When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0. When operation will always be above -10°C, then the low-power Timer1 oscillator may be selected.

- **4:** BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

TABLE 28-1: MEMORY PROGRAMMING REQUIREMENTS

|              |       |                                                                  | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for industrial |      |     |       |                                                            |

|--------------|-------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|-----|-------|------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                                                   | Min                                                                                                             | Тур† | Max | Units | Conditions                                                 |

|              |       | Data EEPROM Memory                                               |                                                                                                                 |      |     |       |                                                            |

| D120         | ED    | Byte Endurance                                                   | 100K                                                                                                            | 1M   | _   | E/W   | -40°C to +85°C                                             |

| D121         | VDRW  | VDD for Read/Write                                               | VMIN                                                                                                            | _    | 5.5 | V     | Using EECON to read/write VMIN = Minimum operating voltage |

| D122         | TDEW  | Erase/Write Cycle Time                                           | _                                                                                                               | 4    | _   | ms    |                                                            |

| D123         | TRETD | Characteristic Retention                                         | 40                                                                                                              | _    | _   | Year  | Provided no other specifications are violated              |

| D124         | TREF  | Number of Total Erase/Write Cycles before Refresh <sup>(1)</sup> | 1M                                                                                                              | 10M  | _   | E/W   | -40°C to +85°C                                             |

| D125         | IDDP  | Supply Current during<br>Programming                             | _                                                                                                               | 10   | _   | mA    |                                                            |

|              |       | Program Flash Memory                                             |                                                                                                                 |      |     |       |                                                            |

| D130         | EР    | Cell Endurance                                                   | 10K                                                                                                             | 100K | _   | E/W   | -40°C to +85°C                                             |

| D131         | VPR   | VDD for Read                                                     | VMIN                                                                                                            | _    | 5.5 | V     | VMIN = Minimum operating voltage                           |

| D132B        | VPEW  | VDD for Self-Timed Write and Row Erase                           | VMIN                                                                                                            | _    | 5.5 | V     | VMIN = Minimum operating voltage                           |

| D133A        | Tıw   | Self-Timed Write Cycle Time                                      | _                                                                                                               | 2    | _   | ms    |                                                            |

| D134         | TRETD | Characteristic Retention                                         | 40                                                                                                              | 100  | _   | Year  | Provided no other specifications are violated              |

| D135         | IDDP  | Supply Current during<br>Programming                             | _                                                                                                               | 10   | _   | mA    |                                                            |

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Refer to Section 8.8 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

### **TABLE 28-2: COMPARATOR SPECIFICATIONS**

| Operating Conditions: 3.0V < VDD < 5.5V, -40°C < TA < +85°C (unless otherwise stated) |        |                                           |     |      |           |       |                                     |

|---------------------------------------------------------------------------------------|--------|-------------------------------------------|-----|------|-----------|-------|-------------------------------------|

| Param<br>No.                                                                          | Sym    | Characteristics                           | Min | Тур  | Max       | Units | Comments                            |

| D300                                                                                  | VIOFF  | Input Offset Voltage                      | _   | ±5.0 | ±10       | mV    |                                     |

| D301                                                                                  | VICM   | Input Common Mode Voltage                 | 0   | _    | VDD - 1.5 | V     |                                     |

| D302                                                                                  | CMRR   | Common Mode Rejection Ratio               | 55  | _    | _         | dB    |                                     |

| 300                                                                                   | TRESP  | Response Time <sup>(1)</sup>              | _   | 150  | 400       | ns    | PIC18FXXXX                          |

| 300A                                                                                  |        |                                           | _   | 150  | 600       | ns    | PIC18 <b>LF</b> XXXX,<br>VDD = 2.0V |

| 301                                                                                   | TMC2OV | Comparator Mode Change to<br>Output Valid | _   | _    | 10        | μS    |                                     |

Note 1: Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 28-3: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Operating    | Operating Conditions: 3.0V < VDD < 5.5V, -40°C < TA < +85°C (unless otherwise stated) |                              |        |     |        |       |          |

|--------------|---------------------------------------------------------------------------------------|------------------------------|--------|-----|--------|-------|----------|

| Param<br>No. | Sym                                                                                   | Characteristics              | Min    | Тур | Max    | Units | Comments |

| D310         | VRES                                                                                  | Resolution                   | VDD/24 | _   | VDD/32 | LSb   |          |

| D311         | VRAA                                                                                  | Absolute Accuracy            | _      | _   | 1/2    | LSb   |          |

| D312         | VRur                                                                                  | Unit Resistor Value (R)      | _      | 2k  | _      | Ω     |          |

| 310          | TSET                                                                                  | Settling Time <sup>(1)</sup> | _      | _   | 10     | μS    |          |

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'.

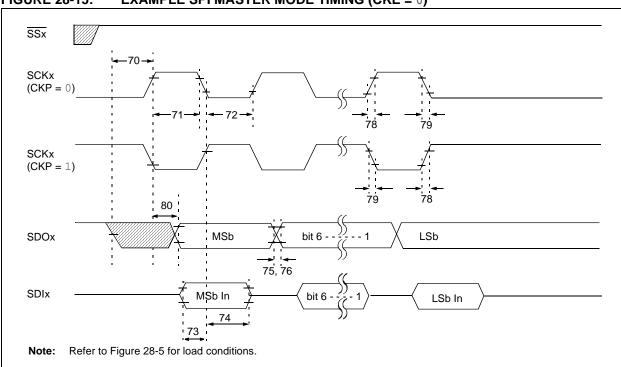

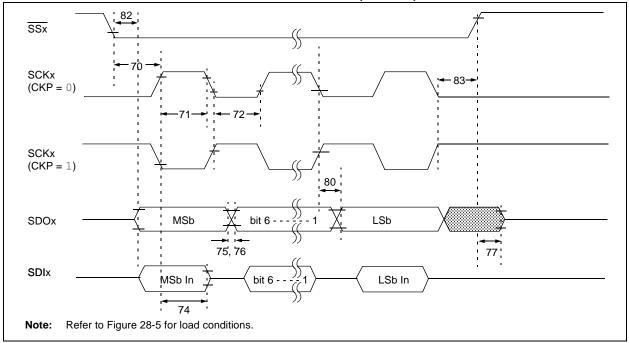

FIGURE 28-15: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

TABLE 28-16: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristi                                             | c                                   | Min           | Max | Units | Conditions |

|--------------|-----------------------|-----------------------------------------------------------|-------------------------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or SCKx ↑ In                              | put                                 | Tcy           | _   | ns    |            |

| 71           | TscH                  | SCKx Input High Time                                      | Continuous                          | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       | (Slave mode)                                              | Single Byte                         | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCKx Input Low Time                                       | Continuous                          | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                                              | Single Byte                         | 40            | _   | ns    | (Note 1)   |

| 73           | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input                             | 20                                  | _             | ns  |       |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2 |                                     | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input t                            | o SCKx Edge                         | 40            | _   | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                                | PIC18FXXXX                          | _             | 25  | ns    |            |

|              |                       |                                                           | PIC18 <b>LF</b> XXXX                | _             | 45  | ns    | VDD = 2.0V |

| 76           | TDOF                  | SDOx Data Output Fall Time                                |                                     | _             | 25  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time                                     | PIC18FXXXX                          | _             | 25  | ns    |            |

|              |                       | (Master mode)                                             | Master mode) PIC18LFXXXX            |               | 45  | ns    | VDD = 2.0V |

| 79           | TscF                  | SCKx Output Fall Time (Maste                              | SCKx Output Fall Time (Master mode) |               | 25  | ns    |            |

| 80           | TscH2DoV,             | SDOx Data Output Valid after                              | PIC18FXXXX                          | _             | 50  | ns    |            |

|              | TscL2doV              | SCKx Edge                                                 | PIC18 <b>LF</b> XXXX                |               | 100 | ns    | VDD = 2.0V |

Note 1: Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

FIGURE 28-18: EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

TABLE 28-19: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param<br>No. | Symbol                | Characteristic                            |                      | Min           | Max | Units | Conditions |

|--------------|-----------------------|-------------------------------------------|----------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or SCKx ↑ Input           |                      | 3 Tcy         | _   | ns    |            |

| 71           | TscH                  | SCKx Input High Time                      | Continuous           | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       | (Slave mode)                              | Single Byte          | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCKx Input Low Time                       | Continuous           | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                              | Single Byte          | 40            | _   | ns    | (Note 1)   |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First Cl | ock Edge of Byte 2   | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx      | 40                   | _             | ns  |       |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                | PIC18FXXXX           | _             | 25  | ns    |            |

|              |                       |                                           | PIC18 <b>LF</b> XXXX | _             | 45  | ns    | VDD = 2.0V |

| 76           | TDOF                  | SDOx Data Output Fall Time                |                      | 1             | 25  | ns    |            |

| 77           | TssH2DoZ              | SSx ↑ to SDOx Output High-Impedan         | ce                   | 10            | 50  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time                     | PIC18FXXXX           | _             | 25  | ns    |            |

|              |                       | (Master mode)                             | PIC18 <b>LF</b> XXXX | _             | 45  | ns    | VDD = 2.0V |

| 79           | TscF                  | SCKx Output Fall Time (Master mode)       | )                    | _             | 25  | ns    |            |

| 80           |                       | SDOx Data Output Valid after SCKx         | PIC18FXXXX           | _             | 50  | ns    |            |

|              | TscL2doV              | Edge                                      | PIC18 <b>LF</b> XXXX | _             | 100 | ns    | VDD = 2.0V |

| 82           | TssL2DoV              | SDOx Data Output Valid after SSx ↓        | PIC18FXXXX           | _             | 50  | ns    |            |

|              |                       | Edge                                      | PIC18 <b>LF</b> XXXX | _             | 100 | ns    | VDD = 2.0V |

| 83           | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx Edge                     |                      | 1.5 Tcy + 40  | _   | ns    |            |

Note 1: Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

NOTES:

### PIC18F8722 FAMILY PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART N<br>Device     | — T — T                                                                                                                                                                                                                                                                                                                                                                 | Examples:  a) PIC18LF6622-I/PT 301 = Industrial temp., TQFP package, Extended VDD limits, QTP pattern #301. |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| Device               | PIC18F6527/6622/6627/6722 <sup>(1)</sup> , PIC18F8527/8622/8627/8722 <sup>(1)</sup> , PIC18F6527/6622/6627/6722T <sup>(2)</sup> , PIC18F8527/8622/8627/8722T <sup>(2)</sup> ; VDD range 4.2V to 5.5V  PIC18LF6627/6722 <sup>(1)</sup> , PIC18LF8627/8722T <sup>(2)</sup> , PIC18LF6627/6722T <sup>(2)</sup> , PIC18LF8627/8722T <sup>(2)</sup> ; VDD range 2.0V to 5.5V | b) PIC18LF6722-E/PT = Extended temp., TQFP package, standard VDD limits.                                    |  |  |  |

| Temperature<br>Range | I = -40°C to +85°C (Industrial)<br>E = -40°C to +125°C (Extended)                                                                                                                                                                                                                                                                                                       |                                                                                                             |  |  |  |

| Package<br>Pattern   | PT = TQFP (Thin Quad Flatpack)  QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                                                                                                                                                                               | Note 1: F = Standard Voltage Range LF = Wide Voltage Range 2: T = in tape and reel TQFP packages only.      |  |  |  |