Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3936 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6622t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                                                                                                                                 | Pin Number | Pin           | Buffer    | Description                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-----------|-------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                                                                                                                                                 | TQFP       | Туре          | Туре      | Description                                                                         |  |  |  |

|                                                                                                                                                                                                          |            |               |           | PORTE is a bidirectional I/O port.                                                  |  |  |  |

| RE0/RD/P2D<br>RE0<br>RD<br>P2D                                                                                                                                                                           | 2          | I/O<br>I<br>O | ST<br>TTL | Digital I/O.<br>Read control for Parallel Slave Port.<br>ECCP2 PWM output D.        |  |  |  |

| RE1/WR/P2C<br>RE1<br>WR<br>P2C                                                                                                                                                                           | 1          | I/O<br>I<br>O | ST<br>TTL | Digital I/O.<br>Write control for Parallel Slave Port.<br>ECCP2 PWM output C.       |  |  |  |

| RE2/CS/P2B<br>RE2<br>CS<br>P2B                                                                                                                                                                           | 64         | I/O<br>I<br>O | ST<br>TTL | Digital I/O.<br>Chip select control for Parallel Slave Port.<br>ECCP2 PWM output B. |  |  |  |

| RE3/P3C<br>RE3<br>P3C                                                                                                                                                                                    | 63         | I/O<br>O      | ST<br>—   | Digital I/O.<br>ECCP3 PWM output C.                                                 |  |  |  |

| RE4/P3B<br>RE4<br>P3B                                                                                                                                                                                    | 62         | I/O<br>O      | ST<br>—   | Digital I/O.<br>ECCP3 PWM output B.                                                 |  |  |  |

| RE5/P1C<br>RE5<br>P1C                                                                                                                                                                                    | 61         | I/O<br>O      | ST<br>—   | Digital I/O.<br>ECCP1 PWM output C.                                                 |  |  |  |

| RE6/P1B<br>RE6<br>P1B                                                                                                                                                                                    | 60         | I/O<br>O      | ST<br>—   | Digital I/O.<br>ECCP1 PWM output B.                                                 |  |  |  |

| RE7/ECCP2/P2A<br>RE7<br>ECCP2 <sup>(2)</sup>                                                                                                                                                             | 59         | I/O<br>I/O    | ST<br>ST  | Digital I/O.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.         |  |  |  |

| P2A <sup>(2)</sup>                                                                                                                                                                                       |            | 0             |           | ECCP2 PWM output A.                                                                 |  |  |  |

| Legend:TTL = TTL compatible inputCMOS= CMOS compatible input or outputST = Schmitt Trigger input with CMOS levels Analog=Analog inputI = InputO= OutputP = Power $l^2C^{TM}$ = $l^2C/SMBus$ input buffer |            |               |           |                                                                                     |  |  |  |

## TABLE 1-3: PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

# 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the device clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after either of the SCS<1:0> bits are changed, following a brief clock transition interval. The SCS bits are reset on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source (31 kHz), the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source derived from the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source and disables the INTOSC to reduce current consumption.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Additionally, the INTOSC source will already be stable should a switch to a higher frequency be needed quickly. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer and PLL Start-up Timer (if enabled) have timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable.

The IDLEN bit controls whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 3.0** "Power-Managed Modes".

| Note 1: | The Timer1 oscillator must be enabled to<br>select the secondary clock source. The<br>Timer1 oscillator is enabled by setting the<br>T1OSCEN bit in the Timer1 Control regis- |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | ter (T1CON<3>). If the Timer1 oscillator<br>is not enabled, then any attempt to select<br>a secondary clock source will be ignored.                                           |

| 2:      | It is recommended that the Timer1 oscillator be operating and stable before                                                                                                   |

2: It is recommended that the filmer oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

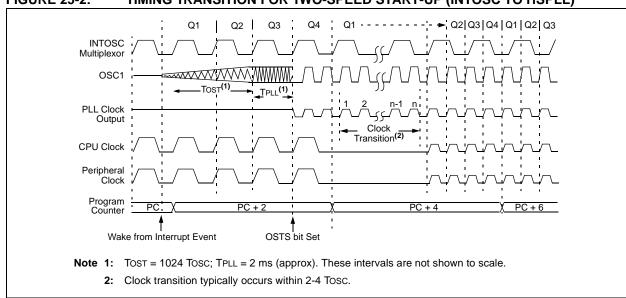

# 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F8722 family of devices contains circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes**".

## 4.5 Device Reset Timers

The PIC18F8722 family of devices incorporates three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F8722 family of devices is an 11-bit counter which uses the INTRC source as the clock input. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 in Table 28-12 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33, Table 28-12). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

# 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, all time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18F8722 family device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> a                              | Exit from                       |                                 |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|

| Configuration  | <b>PWRTEN</b> = 0                                      | <b>PWRTEN</b> = 1               | Power-Managed Mode              |

| HSPLL          | TPWRT <sup>(1)</sup> + 1024 TOSC + TPLL <sup>(2)</sup> | 1024 Tosc + Tpll <sup>(2)</sup> | 1024 Tosc + Tpll <sup>(2)</sup> |

| HS, XT, LP     | Tpwrt <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |

| EC, ECIO       | TPWRT <sup>(1)</sup>                                   | _                               | —                               |

| RC, RCIO       | TPWRT <sup>(1)</sup>                                   | _                               | —                               |

| INTIO1, INTIO2 | Tpwrt <sup>(1)</sup>                                   | _                               | —                               |

TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

Note 1: See parameter 33, Table 28-12.

2: 2 ms is the nominal time required for the PLL to lock.

| Register            | A    | opplicabl | e Device | s    | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|---------------------|------|-----------|----------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| FSR1H               | 6X27 | 6X22      | 8X27     | 8X22 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR1L               | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| BSR                 | 6X27 | 6X22      | 8X27     | 8X22 | 0000                               | 0000                                                             | uuuu                            |  |

| INDF2               | 6X27 | 6X22      | 8X27     | 8X22 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC2            | 6X27 | 6X22      | 8X27     | 8X22 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC2            | 6X27 | 6X22      | 8X27     | 8X22 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC2             | 6X27 | 6X22      | 8X27     | 8X22 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW2              | 6X27 | 6X22      | 8X27     | 8X22 | N/A                                | N/A                                                              | N/A                             |  |

| FSR2H               | 6X27 | 6X22      | 8X27     | 8X22 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR2L               | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| STATUS              | 6X27 | 6X22      | 8X27     | 8X22 | x xxxx                             | u uuuu                                                           | u uuuu                          |  |

| TMR0H               | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TMR0L               | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| TOCON               | 6X27 | 6X22      | 8X27     | 8X22 | 1111 1111                          | 1111 1111                                                        | uuuu uuuu                       |  |

| OSCCON              | 6X27 | 6X22      | 8X27     | 8X22 | 0100 q000                          | 0100 q000                                                        | uuuu uuqu                       |  |

| HLVDCON             | 6X27 | 6X22      | 8X27     | 8X22 | 0-00 0101                          | 0-00 0101                                                        | u-uu uuuu                       |  |

| WDTCON              | 6X27 | 6X22      | 8X27     | 8X22 | 0                                  | 0                                                                | u                               |  |

| RCON <sup>(4)</sup> | 6X27 | 6X22      | 8X27     | 8X22 | 0q-1 11q0                          | 0q-q qquu                                                        | uq-u qquu                       |  |

| TMR1H               | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| TMR1L               | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| T1CON               | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | u0uu uuuu                                                        | uuuu uuuu                       |  |

| TMR2                | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| PR2                 | 6X27 | 6X22      | 8X27     | 8X22 | 1111 1111                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| T2CON               | 6X27 | 6X22      | 8X27     | 8X22 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |

| SSP1BUF             | 6X27 | 6X22      | 8X27     | 8X22 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| SSP1ADD             | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSP1STAT            | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSP1CON1            | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSP1CON2            | 6X27 | 6X22      | 8X27     | 8X22 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

# TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend:u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

# 6.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

## 6.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- The CPU will stall for duration of the erase for TIW (see parameter D133A).

- 8. Re-enable interrupts.

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ERASE_ROW | 110 V WI                                           |                                                                                     |                                                              |

|           | BSF                                                | EECON1, EEPGD                                                                       | ; point to Flash program memory                              |

|           | BCF                                                | EECON1, CFGS                                                                        | ; access Flash program memory                                |

|           | BSF                                                | EECON1, WREN                                                                        | ; enable write to memory                                     |

|           | BSF                                                | EECON1, FREE                                                                        | ; enable Row Erase operation                                 |

|           | BCF                                                | INTCON, GIE                                                                         | ; disable interrupts                                         |

| Required  | MOVLW                                              | 55h                                                                                 |                                                              |

| Sequence  | MOVWF                                              | EECON2                                                                              | ; write 55h                                                  |

|           | MOVLW                                              | 0AAh                                                                                |                                                              |

|           | MOVWF                                              | EECON2                                                                              | ; write OAAh                                                 |

|           | BSF                                                | EECON1, WR                                                                          | ; start erase (CPU stall)                                    |

|           | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |

## EXAMPLE 6-2: ERASING A FLASH PROGRAM MEMORY ROW

# **10.0 INTERRUPTS**

The PIC18F8722 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a highpriority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| R/W     | -1 R/W-1                                    | R/W-1                                       | R/W-1            | R/W-1            | R/W-1            | R/W-1           | R/W-1            |  |  |  |  |

|---------|---------------------------------------------|---------------------------------------------|------------------|------------------|------------------|-----------------|------------------|--|--|--|--|

| RBP     | U INTEDG0                                   | INTEDG1                                     | INTEDG2          | INTEDG3          | TMR0IP           | INT3IP          | RBIP             |  |  |  |  |

| bit 7   |                                             |                                             |                  |                  |                  |                 | bit 0            |  |  |  |  |

|         |                                             |                                             |                  |                  |                  |                 |                  |  |  |  |  |

| Legend: |                                             |                                             | L.14             |                  | newted bit week  |                 |                  |  |  |  |  |

|         | dable bit<br>Je at POR                      | W = Writable<br>'1' = Bit is set            |                  | 0 = 0 minimpler  | nented bit, read | x = Bit is unkr | 0.000            |  |  |  |  |

|         |                                             |                                             |                  |                  | aleu             | X = DILIS ULIKI | IOWIT            |  |  |  |  |

| bit 7   | RBPU: PORT                                  | B Pull-up Ena                               | ble bit          |                  |                  |                 |                  |  |  |  |  |

|         | 1 = All PORT                                | B pull-ups are                              | disabled         |                  |                  |                 |                  |  |  |  |  |

|         |                                             |                                             |                  | idual port latch | values           |                 |                  |  |  |  |  |

| bit 6   |                                             | ternal Interrup                             | •                | ct bit           |                  |                 |                  |  |  |  |  |

|         |                                             | on rising edge<br>on falling edge           |                  |                  |                  |                 |                  |  |  |  |  |

| bit 5   | •                                           | ternal Interrup                             |                  | ct bit           |                  |                 |                  |  |  |  |  |

|         |                                             | on rising edge                              | •                |                  |                  |                 |                  |  |  |  |  |

|         | 0 = Interrupt                               | on falling edge                             | )                |                  |                  |                 |                  |  |  |  |  |

| bit 4   |                                             | ternal Interrup                             | •                | ct bit           |                  |                 |                  |  |  |  |  |

|         |                                             | on rising edge<br>on falling edge           |                  |                  |                  |                 |                  |  |  |  |  |

| bit 3   | •                                           | ternal Interrup                             |                  | rt hit           |                  |                 |                  |  |  |  |  |

| bit 5   |                                             | on rising edge                              | •                |                  |                  |                 |                  |  |  |  |  |

|         |                                             | on falling edge                             |                  |                  |                  |                 |                  |  |  |  |  |

| bit 2   | TMR0IP: TM                                  | R0 Overflow In                              | terrupt Priority | ' bit            |                  |                 |                  |  |  |  |  |

|         | 1 = High prio                               | •                                           |                  |                  |                  |                 |                  |  |  |  |  |

| bit 1   | 0 = Low prior                               | -                                           | unt Driarity hit |                  |                  |                 |                  |  |  |  |  |

| DILI    | 1 = High prio                               | External Inter                              | upt Phonty bit   |                  |                  |                 |                  |  |  |  |  |

|         | 0 = Low prior                               |                                             |                  |                  |                  |                 |                  |  |  |  |  |

| bit 0   | RBIP: RB Po                                 | RBIP: RB Port Change Interrupt Priority bit |                  |                  |                  |                 |                  |  |  |  |  |

|         | 1 = High prio                               | •                                           |                  |                  |                  |                 |                  |  |  |  |  |

|         | 0 = Low prior                               | rity                                        |                  |                  |                  |                 |                  |  |  |  |  |

| Note:   | Interrupt flag bits a                       |                                             |                  |                  |                  |                 |                  |  |  |  |  |

|         | enable bit or the g<br>are clear prior to e |                                             |                  |                  |                  |                 | errupt flag bits |  |  |  |  |

|         | are clear prior to e                        | nability an Inte                            | mupt. This lea   |                  | soliware polili  | y.              |                  |  |  |  |  |

# REGISTER 10-2: INTCON2: INTERRUPT CONTROL REGISTER 2

## REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1      | R/W-1                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0            |

|------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|------------------|

| INT2I      | P INT1IP                      | INT3IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INT2IE          | INT1IE           | INT3IF           | INT2IF          | INT1IF           |

| bit 7      | ·                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  | •                |                 | bit 0            |

|            |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |                  |

| Legend:    | abla bit                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L.14            |                  |                  |                 |                  |

| R = Read   |                               | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | •                | mented bit, read |                 |                  |

| -n = Value | atPOR                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | '0' = Bit is cle | ared             | x = Bit is unkr | IOWN             |

| bit 7      | INT2IP: INT2                  | 2 External Interi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | upt Priority bi | t                |                  |                 |                  |

|            | 1 = High prid<br>0 = Low prid |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |                  |

| bit 6      | INT1IP: INT1                  | External Intern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | upt Priority bi | t                |                  |                 |                  |

|            | 1 = High price                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                  |                  |                 |                  |

| bit 5      | 0 = Low price                 | rity<br>3 External Interi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | unt Enchlo hi   | +                |                  |                 |                  |

| DILD       |                               | the INT3 exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •               | L                |                  |                 |                  |

|            |                               | the INT3 exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •               |                  |                  |                 |                  |

| bit 4      | INT2IE: INT2                  | 2 External Interi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | upt Enable bi   | t                |                  |                 |                  |

|            |                               | the INT2 exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                  |                  |                 |                  |

| bit 3      |                               | the INT2 exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •               |                  |                  |                 |                  |

| DIL 3      |                               | External Internation Internation International Internation | •               | L                |                  |                 |                  |