Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3936 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8622-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 64/80-Pin, 1-Mbit, Enhanced Flash Microcontrollers with 10-Bit A/D and nanoWatt Technology

#### **Power Management Features:**

- Run: CPU On, Peripherals On

- Idle: CPU Off, Peripherals On

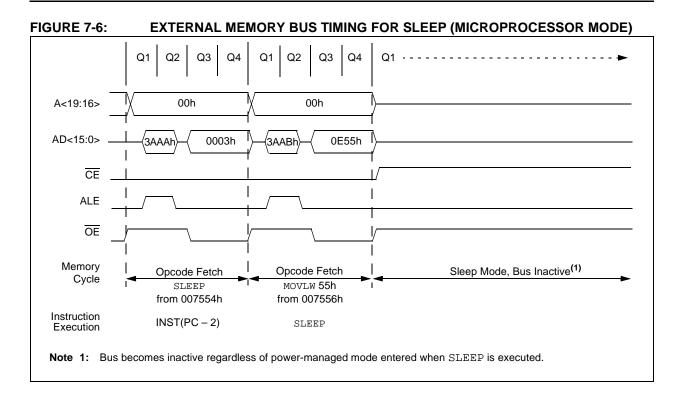

- Sleep: CPU Off, Peripherals Off

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 25  $\mu\text{A}$  Typical

- Idle mode Currents Down to 6.8 µA Typical

- Sleep mode Current Down to 120 nA Typical

- Timer1 Oscillator: 900 nA, 32 kHz, 2V

- Watchdog Timer: 1.6 μA, 2V Typical

- Two-Speed Oscillator Start-up

#### Flexible Oscillator Structure:

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) Available for Crystal and Internal Oscillators

- Internal Oscillator Block:

- Fast wake from Sleep and Idle, 1  $\mu s$  typical

- Provides a complete range of clock speeds

- from 31 kHz to 32 MHz when used with PLL

- User-tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three Programmable External Interrupts

- Four Input Change Interrupts

- Enhanced Capture/Compare/PWM (ECCP) module (40/44-pin devices only):

- One, two or four PWM outputs

- Programmable dead time

- Auto-shutdown and auto-restart

#### **Peripheral Highlights (Continued):**

- Up to 2 Capture/Compare/PWM (CCP) modules, one with Auto-Shutdown (28-pin devices)

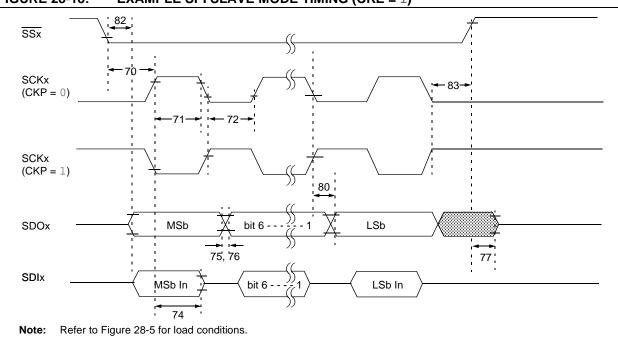

- Master Synchronous Serial Port (MSSP) module Supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

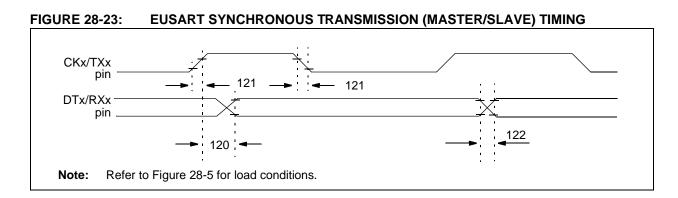

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- RS-232 operation using internal oscillator block (no external crystal required)

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

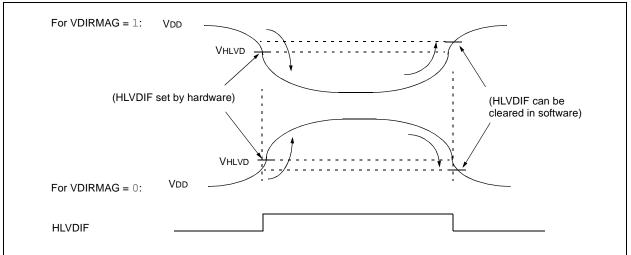

- Programmable 16-Level High/Low-Voltage Detection (HLVD) module

#### **Special Microcontroller Features:**

- C Compiler Optimized Architecture

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

- Flash/Data EEPROM Retention: 100 Years Typical

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

- Programmable Brown-out Reset (BOR) with Software Enable Option

|            | Prog             | Program Memory                |                 | Data Memory       |     | 10-Bit CCP  |        |   | MSSP |                             |       | tors        | it s               | Bus      |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|-------------|--------|---|------|-----------------------------|-------|-------------|--------------------|----------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D<br>(ch) | D ECCP |   | SPI  | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External |

| PIC18F6527 | 48K              | 24576                         | 3936            | 1024              | 54  | 12          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6622 | 64K              | 32768                         | 3936            | 1024              | 54  | 12          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6627 | 96K              | 49152                         | 3936            | 1024              | 54  | 12          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F6722 | 128K             | 65536                         | 3936            | 1024              | 54  | 12          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Ν        |

| PIC18F8527 | 48K              | 24576                         | 3936            | 1024              | 70  | 16          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8622 | 64K              | 32768                         | 3936            | 1024              | 70  | 16          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8627 | 96K              | 49152                         | 3936            | 1024              | 70  | 16          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| PIC18F8722 | 128K             | 65536                         | 3936            | 1024              | 70  | 16          | 2/3    | 2 | Y    | Y                           | 2     | 2           | 2/3                | Y        |

| Din Nama                                                                        | Pin Number       | Pin                               | Buffer                | Deserintion                                                                                                                                                                                                |  |  |  |  |

|---------------------------------------------------------------------------------|------------------|-----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                        | TQFP             | Туре                              | Туре                  | Description                                                                                                                                                                                                |  |  |  |  |

|                                                                                 |                  |                                   |                       | PORTE is a bidirectional I/O port.                                                                                                                                                                         |  |  |  |  |

| RE0/AD8/RD/P2D<br>RE0<br>AD8<br>RD<br>P2D                                       | 4                | I/O<br>I/O<br>I<br>O              | ST<br>TTL<br>TTL<br>— | Digital I/O.<br>External memory address/data 8.<br>Read control for Parallel Slave Port.<br>ECCP2 PWM output D.                                                                                            |  |  |  |  |

| RE1/AD9/WR/P2C<br>RE1<br>AD9<br>WR<br>P2C                                       | 3                | I/O<br>I/O<br>I<br>O              | ST<br>TTL<br>TTL      | Digital I/O.<br>External memory address/data 9.<br>Write control for Parallel Slave Port.<br>ECCP2 PWM output C.                                                                                           |  |  |  |  |

| RE2/AD10/CS/P2B<br>RE2<br>AD10<br>CS<br>P2B                                     | 78               | I/O<br>I/O<br>I<br>O              | ST<br>TTL<br>TTL<br>— | Digital I/O.<br>External memory address/data 10.<br>Chip select control for Parallel Slave Port.<br>ECCP2 PWM output B.                                                                                    |  |  |  |  |

| RE3/AD11/P3C<br>RE3<br>AD11<br>P3C <sup>(4)</sup>                               | 77               | I/O<br>I/O<br>O                   | ST<br>TTL             | Digital I/O.<br>External memory address/data 11.<br>ECCP3 PWM output C.                                                                                                                                    |  |  |  |  |

| RE4/AD12/P3B<br>RE4<br>AD12<br>P3B <sup>(4)</sup>                               | 76               | I/O<br>I/O<br>O                   | ST<br>TTL             | Digital I/O.<br>External memory address/data 12.<br>ECCP3 PWM output B.                                                                                                                                    |  |  |  |  |

| RE5/AD13/P1C<br>RE5<br>AD13<br>P1C <sup>(4)</sup>                               | 75               | I/O<br>I/O<br>O                   | ST<br>TTL             | Digital I/O.<br>External memory address/data 13.<br>ECCP1 PWM output C.                                                                                                                                    |  |  |  |  |

| RE6/AD14/P1B<br>RE6<br>AD14<br>P1B <sup>(4)</sup>                               | 74               | I/O<br>I/O<br>O                   | ST<br>TTL             | Digital I/O.<br>External memory address/data 14.<br>ECCP1 PWM output B.                                                                                                                                    |  |  |  |  |

| RE7/AD15/ECCP2/P2A<br>RE7<br>AD15<br>ECCP2 <sup>(3)</sup><br>P2A <sup>(3)</sup> | 73               | I/O<br>I/O<br>I/O                 | ST<br>TTL<br>ST       | Digital I/O.<br>External memory address/data 15.<br>Enhanced Capture 2 input/Compare 2 output/<br>PWM 2 output.<br>ECCP2 PWM output A.                                                                     |  |  |  |  |

| I = Input<br>P = Power                                                          | tt Trigger input | with CM<br>O<br>I <sup>2</sup> C™ | IOS levels<br>VSMB    | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>I<sup>2</sup>C/SMBus input buffer</li> <li>aration bit, CCP2MX, is cleared (all operating modes except)</li> </ul> |  |  |  |  |

#### TABLE 1-4: PIC18F8527/8622/8627/8722 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

5: Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX is clear).

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

### TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |  |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|--|

|                                | LP, XT, HS                    |                                       |                                    |  |

| Primary Device Clock           | HSPLL                         | <sub>тсер</sub> (1)                   | OSTS                               |  |

| (PRI_IDLE mode)                | EC, RC                        | 10.30 ( )                             |                                    |  |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| T1OSC or INTRC                 | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

|                                | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |  |

| INTOSC <sup>(2)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

| (Sleep mode)                   | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

Note 1: TCSD (parameter 38, Table 28-12) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies. On Reset, INTOSC defaults to 1 MHz.

**3:** TOST is the Oscillator Start-up Timer (parameter 32, Table 28-12). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12, Table 28-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 28-12), the INTOSC stabilization period.

#### 5.1.3.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 25.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st PUSH will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st PUSH and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st PUSH and STKPTR will remain at 31. When the stack has been popped enough times to unload the stack, the next POP will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                |

#### 5.1.3.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

#### REGISTER 5-1: STKPTR: STACK POINTER REGISTER

| R/C-0                 | R/C-0                                         | U-0                                                               | R/W-0                                                  | R/W-0            | R/W-0            | R/W-0           | R/W-0              |  |  |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|------------------|------------------|-----------------|--------------------|--|--|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup>                         | _                                                                 | SP4                                                    | SP3              | SP2              | SP1             | SP0                |  |  |

| bit 7                 |                                               |                                                                   |                                                        |                  |                  |                 | bit (              |  |  |

|                       |                                               |                                                                   |                                                        |                  |                  |                 |                    |  |  |

| Legend:               |                                               |                                                                   |                                                        |                  |                  |                 |                    |  |  |

| R = Readable          | bit                                           | W = Writable                                                      | bit                                                    | U = Unimpler     | nented bit, read | d as '0'        |                    |  |  |

| -n = Value at I       | POR                                           | '1' = Bit is set                                                  | t                                                      | '0' = Bit is cle | ared             | x = Bit is unkr | x = Bit is unknown |  |  |

| bit 7<br>bit 6        | 1 = Stack bec<br>0 = Stack has<br>STKUNF: Sta | ck Full Flag bit<br>ame full or ove<br>not become funck Underflow | erflowed<br>ull or overflow<br>Flag bit <sup>(1)</sup> | ed               |                  |                 |                    |  |  |

|                       |                                               | lerflow occurre<br>lerflow did not                                |                                                        |                  |                  |                 |                    |  |  |

| bit 5                 | Unimplemen                                    | ted: Read as '                                                    | ʻ0'                                                    |                  |                  |                 |                    |  |  |

| bit 4-0               | <b>SP&lt;4:0&gt;:</b> Sta                     | ck Pointer Loc                                                    | ation bits                                             |                  |                  |                 |                    |  |  |

|                       |                                               |                                                                   |                                                        |                  |                  |                 |                    |  |  |

#### 5.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 5.5 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

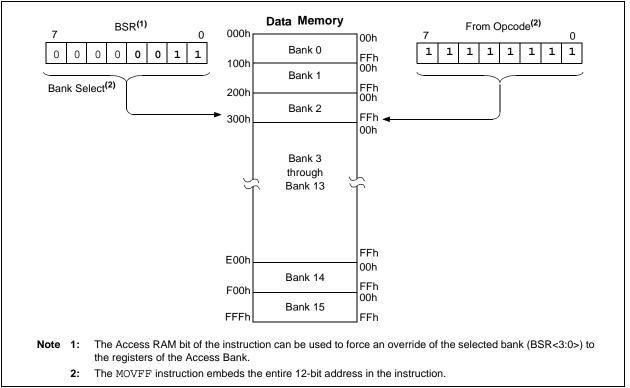

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each; the PIC18F8722 family of devices implements all 16 banks. Figure 5-6 shows the data memory organization for the PIC18F8722 family of devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 5.3.2** "Access Bank" provides a detailed description of the Access RAM.

#### 5.3.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location's address; the instruction itself includes the 8 Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory; the 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 5-7.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 5-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

#### 5.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 5-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 5.5.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 5.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

|                |       |         |       | · /                             |

|----------------|-------|---------|-------|---------------------------------|

| PROGRAM_MEMORY |       |         |       |                                 |

|                | BSF   | EECON1, | EEPGD | ; point to Flash program memory |

|                | BCF   | EECON1, | CFGS  | ; access Flash program memory   |

|                | BSF   | EECON1, | WREN  | ; enable write to memory        |

|                | BCF   | INTCON, | GIE   | ; disable interrupts            |

|                | MOVLW | 55h     |       |                                 |

| Required       | MOVWF | EECON2  |       | ; write 55h                     |

| Sequence       | MOVLW | 0AAh    |       |                                 |

|                | MOVWF | EECON2  |       | ; write OAAh                    |

|                | BSF   | EECON1, | WR    | ; start program (CPU stall)     |

|                | BSF   | INTCON, | GIE   | ; re-enable interrupts          |

|                | BCF   | EECON1, | WREN  | ; disable write to memory       |

|                |       |         |       |                                 |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 25.0 "Special Features of the CPU" for more detail.

#### 6.6 Flash Program Operation During Code Protection

See Section 25.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7      | Bit 6         | Bit 5                 | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|------------|---------------|-----------------------|---------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU |            | —             | bit 21 <sup>(1)</sup> | Program Me    | emory Table I | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 57                         |

| TBPLTRH | Program Me | emory Table   | Pointer H             | ligh Byte (TE | BLPTR<15:8    | S>)          |               |            | 57                         |

| TBLPTRL | Program Me | emory Table   | Pointer L             | ow Byte (TB   | LPTR<7:0>     | )            |               |            | 57                         |

| TABLAT  | Program Me | emory Table   | Latch                 |               |               |              |               |            | 57                         |

| INTCON  | GIE/GIEH   | PEIE/GIEL     | TMR0IE                | INT0IE        | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 57                         |

| EECON2  | EEPROM C   | Control Regis | ster 2 (not           | a physical r  | egister)      |              |               |            | 59                         |

| EECON1  | EEPGD      | CFGS          | -                     | FREE          | WRERR         | WREN         | WR            | RD         | 59                         |

| IPR2    | OSCFIP     | CMIP          | —                     | EEIP          | BCL1IP        | HLVDIP       | TMR3IP        | CCP2IP     | 60                         |

| PIR2    | OSCFIF     | CMIF          | —                     | EEIF          | BCL1IF        | HLVDIF       | TMR3IF        | CCP2IF     | 60                         |

| PIE2    | OSCFIE     | CMIE          | _                     | EEIE          | BCL1IE        | HLVDIE       | TMR3IE        | CCP2IE     | 60                         |

TABLE 6-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

**Note 1:** Bit 21 of TBLPTRU allows access to the device Configuration bits.

| Pin Name    | Function | TRIS<br>Setting                                                                                | I/O | I/O Type | Description                                                                                                   |  |  |

|-------------|----------|------------------------------------------------------------------------------------------------|-----|----------|---------------------------------------------------------------------------------------------------------------|--|--|

| RC6/TX1/CK1 | RC6      | 0                                                                                              | 0   | DIG      | LATC<6> data output.                                                                                          |  |  |

|             |          | 1                                                                                              | Ι   | ST       | PORTC<6> data input.                                                                                          |  |  |

|             | TX1      | 0 O DIG Asynchronous serial transmit data output (EUSART1 module).<br>priority over port data. |     |          |                                                                                                               |  |  |

|             | CK1      | 0                                                                                              | 0   | DIG      | Synchronous serial clock output (EUSART1 module). Takes priority over port data.                              |  |  |

|             |          | 1                                                                                              | Ι   | ST       | Synchronous serial clock input (EUSART1 module).                                                              |  |  |

| RC7/RX1/DT1 | RC7      | 0                                                                                              | 0   | DIG      | LATC<7> data output.                                                                                          |  |  |

|             |          | 1                                                                                              | Ι   | ST       | PORTC<7> data input.                                                                                          |  |  |

|             | RX1      | 1                                                                                              | Ι   | ST       | Asynchronous serial receive data input (EUSART1 module)                                                       |  |  |

|             | DT1      | 1                                                                                              | 0   | DIG      | Synchronous serial data output (EUSART1 module). Takes priority over port data. User must configure as input. |  |  |

|             |          | 1                                                                                              | I   | ST       | Synchronous serial data input (EUSART1 module). User must configure as an input.                              |  |  |

#### TABLE 11-5: PORTC FUNCTIONS (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when CCP2MX Configuration bit is set.

| TABLE 11-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 60                         |

| LATC  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 60                         |

| TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 60                         |

#### 17.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The PIC18F8722 family of devices all have a total of five CCP (Capture/Compare/PWM) modules. Two of these (CCP4 and CCP5) implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes and are discussed in this section. The other three modules (ECCP1, ECCP2, ECCP3) implement standard Capture and Compare modes, as well as Enhanced PWM modes. These are discussed in Section 18.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Each CCP/ECCP module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operations in the following sections are described with respect to CCP4, but are equally applicable to CCP5. Capture and Compare operations described in this chapter apply to all standard and Enhanced CCP modules. The operations of PWM mode described in **Section 17.4** "**PWM Mode**" apply to CCP4 and CCP5 only.

Note: Throughout this section and Section 18.0 "Enhanced Capture/Compare/PWM (ECCP) Module", references to register and bit names that may be associated with a specific CCP module are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP4 or CCP5, or ECCP1, ECCP2 or ECCP3. "CCPxCON" is used throughout these sections to refer to the module control register, regardless of whether the CCP module is a standard or enhanced implementation.

#### **REGISTER 17-1: CCPxCON: CCPx CONTROL REGISTER (CCP4 AND CCP5 MODULES)**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     |     | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | <b>DCxB&lt;1:0&gt;</b> : PWM Duty Cycle bit 1 and bit 0 for CCP Module x                                                                                                        |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | Capture mode:                                                                                                                                                                   |  |  |  |  |  |

|         | Unused.                                                                                                                                                                         |  |  |  |  |  |

|         | Compare mode:                                                                                                                                                                   |  |  |  |  |  |

|         | Unused.                                                                                                                                                                         |  |  |  |  |  |

|         | PWM mode:                                                                                                                                                                       |  |  |  |  |  |

|         | These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCx<9:2>) of the duty cycle are found in CCPRxL. |  |  |  |  |  |

| bit 3-0 | CCPxM<3:0>: CCP Module x Mode Select bits                                                                                                                                       |  |  |  |  |  |

|         | 0000 = Capture/Compare/PWM disabled; resets CCPx module                                                                                                                         |  |  |  |  |  |

|         | 0001 = Reserved                                                                                                                                                                 |  |  |  |  |  |

|         | 0010 = Compare mode, toggle output on match; CCPxIF bit is set                                                                                                                  |  |  |  |  |  |

|         | 0011 = Reserved                                                                                                                                                                 |  |  |  |  |  |

|         | 0100 = Capture mode, every falling edge                                                                                                                                         |  |  |  |  |  |

|         | 0101 = Capture mode, every rising edge                                                                                                                                          |  |  |  |  |  |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                                      |  |  |  |  |  |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                                     |  |  |  |  |  |

|         | 1000 = Compare mode, initialize CCPx pin low; on compare match, force CCPx pin high; CCPxIF bit is set                                                                          |  |  |  |  |  |

|         | 1001 = Compare mode, initialize CCPx pin high; on compare match, force CCPx pin low; CCPxIF bit is set                                                                          |  |  |  |  |  |

|         | 1010 = Compare mode, generate software interrupt on compare match; CCPxIF bit is set; CCPx pin reflects I/O state                                                               |  |  |  |  |  |

|         | 1011 = Compare mode, trigger special event; CCPxIF bit is set, CCPx pin is unaffected (For the effects of the trigger, see Section 17.3.4 "Special Event Trigger".)             |  |  |  |  |  |

|         | 11xx = PWM mode                                                                                                                                                                 |  |  |  |  |  |

#### 21.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in the Sleep mode requires the A/D FRC clock to be selected. If bits ACQT<2:0> are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

#### 21.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as analog inputs. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

| R/P-1        | R/P-1                    | R/P-1                                   | R/P-1          | U-0              | U-0             | R/P-1           | R/P-1 |  |  |

|--------------|--------------------------|-----------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|

| WAIT         | BW                       | ABW1                                    | ABW0           | —                | —               | PM1             | PM0   |  |  |

| bit 7        |                          |                                         |                |                  |                 |                 | bit C |  |  |

| Legend:      |                          |                                         |                |                  |                 |                 |       |  |  |

| R = Readab   | le bit                   | W = Writable                            | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |

| -n = Value a | t POR                    | '1' = Bit is set                        | :              | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |  |  |

|              |                          |                                         |                |                  |                 |                 |       |  |  |

| bit 7        | WAIT: Extern             | al Bus Data Wa                          | ait Enable bit |                  |                 |                 |       |  |  |

|              |                          |                                         |                | ble reads and t  |                 |                 |       |  |  |

|              | 0 = Wait sele            | ections for table                       | e reads and ta | ble writes are o | determined by   | the WAIT<1:0>   | bits  |  |  |

| bit 6        | BW: Data Bu              | BW: Data Bus Width Select bit           |                |                  |                 |                 |       |  |  |

|              |                          | ternal Bus mod                          |                |                  |                 |                 |       |  |  |

|              | 0 = 8-bit Exte           | ernal Bus mode                          | e              |                  |                 |                 |       |  |  |

| bit 5-4      | ABW<1:0>:/               | ABW<1:0>: Address Bus Width Select bits |                |                  |                 |                 |       |  |  |

|              | 11 = 20-bit a            | address bus                             |                |                  |                 |                 |       |  |  |

|              | 10 = 16-bit a            |                                         |                |                  |                 |                 |       |  |  |

|              | 01 = 12-bit a            |                                         |                |                  |                 |                 |       |  |  |

|              | 00 = 8-bit a             |                                         |                |                  |                 |                 |       |  |  |

| bit 3-2      | Unimplemen               | ted: Read as '                          | 0'             |                  |                 |                 |       |  |  |

| bit 1-0      | <b>PM&lt;1:0&gt;:</b> Pr | ocessor Data N                          | lemory Mode    | Select bits      |                 |                 |       |  |  |

|              | 11 = Microco             | ontroller mode                          |                |                  |                 |                 |       |  |  |

|              |                          |                                         |                |                  |                 |                 |       |  |  |

|              | 10 = Micropr             | ocessor mode<br>ocessor with B          |                |                  |                 |                 |       |  |  |

#### REGISTER 25-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)<sup>(1)</sup>

Note 1: This register is unimplemented in PIC18F6527/6622/6627/6722 devices.

#### REGISTER 25-15: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| —     | —   | —   | _   | —   | —   | —   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-1 <b>Unimplemented</b> : Read as '0' |

|--------------------------------------------|

|--------------------------------------------|

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = Watchdog Timer is on

- 0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

#### TABLE 25-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|----------------------------|

| RCON   | IPEN  | SBOREN | _     | RI    | TO    | PD    | POR   | BOR    | 56                         |

| WDTCON | —     | —      |       |       |       |       |       | SWDTEN | 58                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

#### TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit:                                                                                                                                        |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                            |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                           |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                    |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                             |

| C, DC, Z, OV, N | ALU status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                         |

| d               | Destination select bit:                                                                                                                                |

|                 | d = 0: store result in WREG<br>d = 1: store result in file register f                                                                                  |

| dogt            | Destination: either the WREG register or the specified register file location.                                                                         |

| dest<br>f       | 8-bit Register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                                          |

|                 | 12-bit Register file address (000h to FFFh). This is the source address.                                                                               |

| f <sub>s</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                          |

| f <sub>d</sub>  | Global Interrupt Enable bit.                                                                                                                           |

| GIE             | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                              |

| k               | Label name.                                                                                                                                            |

| label           | The mode of the TBLPTR register for the table read and table write instructions.                                                                       |

| mm              | Only used with table read and table write instructions:                                                                                                |

| *               | No Change to register (such as TBLPTR with table reads and writes)                                                                                     |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                   |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                   |

|                 |                                                                                                                                                        |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                    |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for Call/Branch and Return instructions.           |

| PC              | Program Counter.                                                                                                                                       |

| PCL             | Program Counter Low Byte.                                                                                                                              |

| PCH             | Program Counter High Byte.                                                                                                                             |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                       |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                      |

| PD              | Power-Down bit.                                                                                                                                        |

| PRODH           | Product of Multiply High Byte.                                                                                                                         |

| PRODL           | Product of Multiply Low Byte.                                                                                                                          |

| S               | Fast Call/Return mode select bit:                                                                                                                      |

|                 | s = 0: do not update into/from shadow registers                                                                                                        |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                 |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).<br>8-bit Table Latch.                                                                      |

| TABLAT          |                                                                                                                                                        |

| TO              | Time-out bit.<br>Top-of-Stack.                                                                                                                         |

| TOS             |                                                                                                                                                        |

| u<br>NDT        | Unused or Unchanged.<br>Watchdog Timer.                                                                                                                |

| WDT             |                                                                                                                                                        |

| WREG<br>x       | Working register (accumulator).         Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for |

|                 | compatibility with all Microchip software tools.                                                                                                       |

| Z <sub>S</sub>  | 7-bit offset value for Indirect Addressing of register files (source).                                                                                 |

| z <sub>d</sub>  | 7-bit offset value for Indirect Addressing of register files (destination).                                                                            |

| { }             | Optional argument.                                                                                                                                     |

| [text]          | Indicates an indexed address.                                                                                                                          |

| (text)          | The contents of text.                                                                                                                                  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                         |

| $\rightarrow$   | Assigned to.                                                                                                                                           |

| < >             | Register bit field.                                                                                                                                    |

| E               | In the set of.                                                                                                                                         |

| italics         | User-defined term (font is Courier).                                                                                                                   |

| INCF         | SZ                                | Increment                                                            | Increment f, Skip if 0                                                                                                                                                                                                                                                               |                        |                       |  |  |  |

|--------------|-----------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--|--|--|

| Synta        | ax:                               | INCFSZ f                                                             | INCFSZ f {,d {,a}}                                                                                                                                                                                                                                                                   |                        |                       |  |  |  |

| Opera        | ands:                             | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                  | d ∈ [0,1]                                                                                                                                                                                                                                                                            |                        |                       |  |  |  |

| Operation:   |                                   | (f) + 1 $\rightarrow$ de skip if resul                               | -                                                                                                                                                                                                                                                                                    |                        |                       |  |  |  |

| Statu        | s Affected:                       | None                                                                 | None                                                                                                                                                                                                                                                                                 |                        |                       |  |  |  |

| Enco         | ding:                             | 0011                                                                 | 11da                                                                                                                                                                                                                                                                                 | ffff                   | ffff                  |  |  |  |

| Description: |                                   | incremente<br>placed in W                                            | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. (default)                                                                                                                 |                        |                       |  |  |  |

|              |                                   | If the result<br>which is alr<br>and a NOP<br>it a two-cyc           | eady fetch                                                                                                                                                                                                                                                                           | ed is dis<br>d instead | carded                |  |  |  |

|              |                                   | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank                     | he BSR is                                                                                                                                                                                                                                                                            |                        |                       |  |  |  |

|              |                                   | set is enabl<br>in Indexed<br>mode wher<br>Section 26<br>Bit-Oriente | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                        |                       |  |  |  |

| Word         | s:                                | 1                                                                    |                                                                                                                                                                                                                                                                                      |                        |                       |  |  |  |

| Cycle        | es:                               |                                                                      | cycles if ski<br>a 2-word i                                                                                                                                                                                                                                                          | •                      |                       |  |  |  |

| QC           | cle Activity:                     |                                                                      |                                                                                                                                                                                                                                                                                      |                        |                       |  |  |  |

|              | Q1                                | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                   |                        | Q4                    |  |  |  |

|              | Decode                            | Read<br>register 'f'                                                 | Process<br>Data                                                                                                                                                                                                                                                                      |                        | Vrite to<br>stination |  |  |  |

| lf sk        | in:                               | register i                                                           | Dala                                                                                                                                                                                                                                                                                 | ue                     | SIIIalion             |  |  |  |

| II OIN       | Q1                                | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                   |                        | Q4                    |  |  |  |

|              | No                                | No                                                                   | No                                                                                                                                                                                                                                                                                   |                        | No                    |  |  |  |

|              | operation                         | operation                                                            | operation                                                                                                                                                                                                                                                                            | n op                   | eration               |  |  |  |

| lf sk        | ip and followe                    | 2                                                                    | _                                                                                                                                                                                                                                                                                    |                        | 04                    |  |  |  |

|              | Q1<br>No                          | Q2<br>No                                                             | Q3<br>No                                                                                                                                                                                                                                                                             |                        | Q4<br>No              |  |  |  |

|              | operation                         | operation                                                            | operation                                                                                                                                                                                                                                                                            | n or                   | peration              |  |  |  |

|              | No                                | No                                                                   | No                                                                                                                                                                                                                                                                                   |                        | No                    |  |  |  |

|              | operation                         | operation                                                            | operatio                                                                                                                                                                                                                                                                             | n op                   | peration              |  |  |  |

| <u>Exarr</u> | n <u>ple:</u>                     | NZERO                                                                | INCFSZ<br>:                                                                                                                                                                                                                                                                          | CNT,                   | 1, 0                  |  |  |  |

|              | Before Instruc<br>PC              | = Address                                                            | S (HERE)                                                                                                                                                                                                                                                                             |                        |                       |  |  |  |

|              | After Instructic<br>CNT<br>If CNT | on<br>= CNT + 1<br>= 0;                                              | 1                                                                                                                                                                                                                                                                                    |                        |                       |  |  |  |

|              | PC<br>If CNT<br>PC                |                                                                      | s (ZERO)<br>s (NZERO                                                                                                                                                                                                                                                                 | )                      |                       |  |  |  |