Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

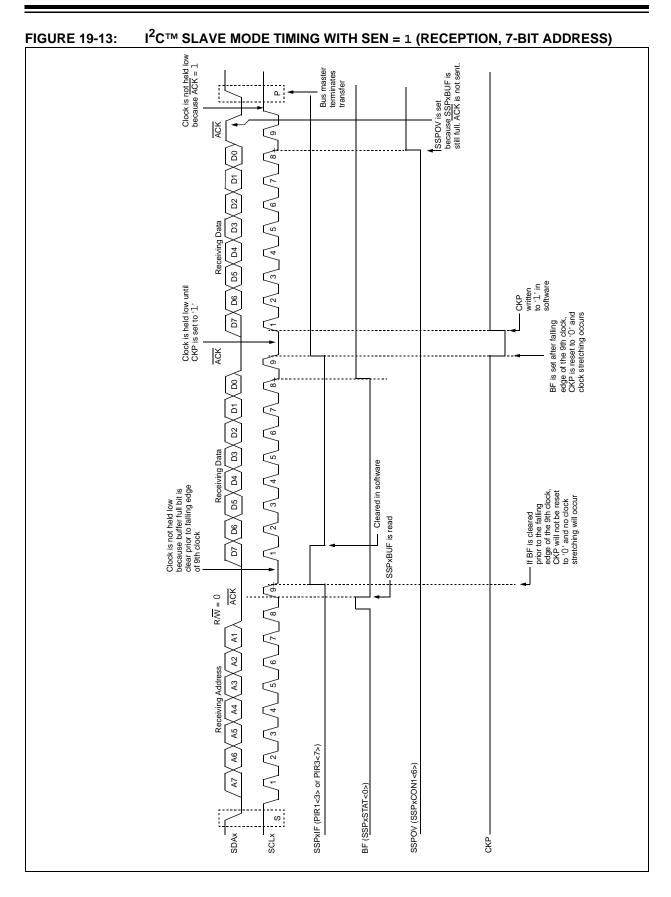

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8627-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Description                                                                                    |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

| Description                                                                                    |  |  |  |

| ΓG is a bidirectional I/O port.                                                                |  |  |  |

| gital I/O.<br>hanced Capture 3 input/Compare 3 output/<br>VM 3 output.                         |  |  |  |

| CCP3 PWM output A.                                                                             |  |  |  |

| gital I/O.<br>JSART2 asynchronous transmit.<br>JSART2 synchronous clock (see related RX2/DT2). |  |  |  |

| gital I/O.<br>JSART2 asynchronous receive.<br>JSART2 synchronous data (see related TX2/CK2).   |  |  |  |

| gital I/O.<br>apture 4 input/Compare 4 output/PWM 4 output.<br>CCP3 PWM output D.              |  |  |  |

| gital I/O.<br>apture 5 input/Compare 5 output/PWM 5 output.<br>CCP1 PWM output D.              |  |  |  |

| RG5/MCLR/VPP pin.                                                                              |  |  |  |

| nd reference for logic and I/O pins.                                                           |  |  |  |

| ve supply for logic and I/O pins.                                                              |  |  |  |

| nd reference for analog modules.                                                               |  |  |  |

| ve supply for analog modules.                                                                  |  |  |  |

| ti<br>JI                                                                                       |  |  |  |

#### **TABLE 1-3:** PIC18F6527/6622/6627/6722 PINOUT I/O DESCRIPTIONS (CONTINUED)

=  $I^2C/SMBus$  input buffer = Power Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

**2:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

I<sup>2</sup>C™

Р

#### FIGURE 5-2: MEMORY MAPS FOR PIC18F8722 FAMILY PROGRAM MEMORY MODES

| _                       | Microprocessor<br>Mode               |                                                 | Microprocessor<br>with Boot Block<br>Mode      |                                                                                                                                                       | Microcontroller<br>Mode <sup>(5)</sup> |                              | Extended<br>Microcontroller<br>Mode                                                                                                                                                                                  |                                               |                        |                               |                              |

|-------------------------|--------------------------------------|-------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|-------------------------------|------------------------------|

| Program Space Execution | 000000h                              | External<br>Program<br>Memory                   | On-Chip<br>Program<br>Memory<br>(No<br>access) | 000000h<br>0007FFh <sup>(6)</sup> or<br>000FFFh <sup>(6)</sup> or<br>001FFFh <sup>(6)</sup> or<br>001000h <sup>(6)</sup> or<br>002000h <sup>(6)</sup> | External<br>Program<br>Memory          | On-Chip<br>Program<br>Memory | 000000h<br>0BFFFh <sup>(1)</sup><br>0FFFFh <sup>(2)</sup><br>017FFFh <sup>(3)</sup><br>01FFFFh <sup>(4)</sup><br>0C000h <sup>(1)</sup><br>010000h <sup>(2)</sup><br>018000h <sup>(3)</sup><br>020000h <sup>(4)</sup> | On-Chip<br>Program<br>Memory<br>Reads<br>'0's | 020000h <sup>(4)</sup> | External<br>Program<br>Memory | On-Chip<br>Program<br>Memory |

|                         | 1FFFFFh                              | External<br>Memory                              | On-Chip<br>Flash                               | 1FFFFfh                                                                                                                                               | External<br>Memory                     | On-Chip<br>Flash             | 1FFFFFh                                                                                                                                                                                                              | On-Chip<br>Flash                              |                        | External<br>Memory            | On-Chip<br>Flash             |

| No                      | ote 1:<br>2:<br>3:<br>4:<br>5:<br>6: | PIC18F66<br>PIC18F66<br>PIC18F67<br>This is the |                                                | 8F8622.<br>8F8627.                                                                                                                                    |                                        |                              |                                                                                                                                                                                                                      |                                               |                        |                               |                              |

### 6.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

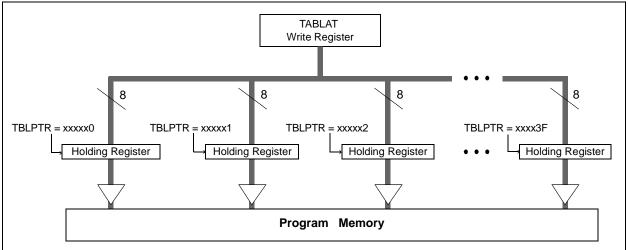

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 holding registers before executing a write operation.

#### FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

## 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the row erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

An example of the required code is shown in Example 6-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

|           |   | $(ARG1L \bullet ARG2L)$                  |

#### EXAMPLE 9-3:

#### 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | i                 |

|   |        |             |                   |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| R | RES3:RES0=ARG1H:ARG1L • ARG2H:ARG2L                             |

|---|-----------------------------------------------------------------|

|   | $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

|   | $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

|   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

|   | $(ARG1L \bullet ARG2L) +$                                       |

|   | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

|   | $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$  |

|   |                                                                 |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| -   |         | WOLI        | IFLI KOUTINE       |

|-----|---------|-------------|--------------------|

|     | MOVF    | ARG1L, W    |                    |

|     | MULWF   | ARG2L       | ; ARG1L * ARG2L -> |

|     |         |             | ; PRODH:PRODL      |

|     | MOVFF   | PRODH, RES1 | ;                  |

|     | MOVFF   | PRODL, RESO | ;                  |

| ;   |         |             |                    |

|     | MOVF    | ARG1H, W    |                    |

|     | MULWF   | ARG2H       | ; ARG1H * ARG2H -> |

|     |         |             | ; PRODH:PRODL      |

|     | MOVFF   | PRODH, RES3 | ;                  |

|     | MOVFF   | PRODL, RES2 | ;                  |

| ;   |         |             |                    |

|     | MOVF    | ARG1L, W    |                    |

|     | MULWF   | ARG2H       | ; ARG1L * ARG2H -> |

|     |         |             | ; PRODH:PRODL      |

|     | MOVF    | PRODL, W    | ;                  |

|     | ADDWF   | RES1, F     | ; Add cross        |

|     | MOVF    |             | ; products         |

|     | ADDWFC  | RES2, F     | ;                  |

|     |         | WREG        | ;                  |

|     |         | RES3, F     | ;                  |

| ;   |         |             |                    |

|     | MOVF    | ARG1H, W    | ;                  |

|     |         | ARG2L       | ; ARG1H * ARG2L -> |

|     |         |             | ; PRODH:PRODL      |

|     | MOVF    | PRODL, W    | ;                  |

|     |         | RES1, F     | ; Add cross        |

|     | MOVF    |             | ; products         |

|     |         | RES2, F     | ;                  |

|     |         | WREG        | ;                  |

|     |         | RES3, F     | ;                  |

| ;   |         |             |                    |

|     | BTESS   | ARG2H, 7    | ; ARG2H:ARG2L neg? |

|     | BRA     | SIGN_ARG1   | ; no, check ARG1   |

|     |         | ARG1L, W    | ;                  |

|     | SUBWF   | RES2        | ;                  |

|     | MOVF    | ARG1H, W    | ;                  |

|     | SUBWFB  |             |                    |

| ;   | 502112  | 11200       |                    |

|     | N_ARG1  |             |                    |

|     |         | ARG1H, 7    | ; ARG1H:ARG1L neg? |

|     | BRA     | CONT_CODE   | ; no, done         |

|     |         | ARG2L, W    | ;                  |

|     | SUBWF   | RES2        | ;                  |

|     |         | ARG2H, W    | ;                  |

|     | SUBWFB  |             |                    |

| ;   | SODMI D | 1000        |                    |

|     | T_CODE  |             |                    |

| CON | :       |             |                    |

|     |         |             |                    |

#### 15.2 Timer3 16-bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer3 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in **Section 13.0** "Timer1 Module".

#### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If any of the CCP modules are configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. ECCP2 can also start an A/D conversion if the A/D module is enabled (see **Section 17.3.4 "Special Event Trigger"** for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

**Note:** The Special Event Triggers from the CCPx module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR2   | OSCFIF                    | CMIF      | _       | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 60                         |

| PIE2   | OSCFIE                    | CMIE      | _       | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 60                         |

| IPR2   | OSCFIP                    | CMIP      | _       | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 60                         |

| TMR3L  | Timer3 Register Low Byte  |           |         |         |         |        |        | 59     |                            |

| TMR3H  | Timer3 Register High Byte |           |         |         |         |        | 59     |        |                            |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 58                         |

| T3CON  | RD16                      | T3CCP2    | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 59                         |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

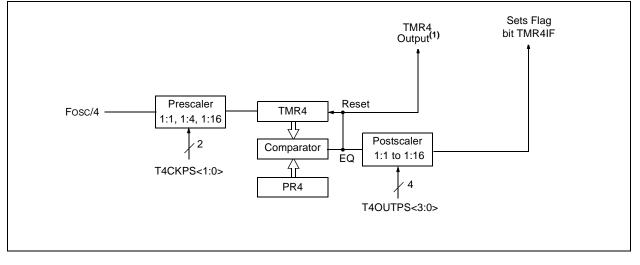

#### 16.2 Timer4 Interrupt

The Timer4 module has an 8-bit Period register, PR4, which is both readable and writable. Timer4 increments from 00h until it matches PR4 and then resets to 00h on the next increment cycle. The PR4 register is initialized to FFh upon Reset.

#### FIGURE 16-1: TIMER4 BLOCK DIAGRAM

#### 16.3 Output of TMR4

The output of TMR4 (before the postscaler) is used only as a PWM time base for the CCP modules. It is not used as a baud rate clock for the MSSP, as is the Timer2 output.

#### TABLE 16-1: REGISTERS ASSOCIATED WITH TIMER4 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6     | Bit 5    | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|------------------------|-----------|----------|---------------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL | TMR0IE   | <b>INTOIE</b> | RBIE     | TMR0IF | INT0IF  | RBIF    | 57                         |

| IPR3   | SSP2IP                 | BCL2IP    | RC2IP    | TX2IP         | TMR4IP   | CCP5IP | CCP4IP  | CCP3IP  | 60                         |

| PIR3   | SSP2IF                 | BCL2IF    | RC2IF    | TX2IF         | TMR4IF   | CCP5IF | CCP4IF  | CCP3IF  | 60                         |

| PIE3   | SSP2IE                 | BCL2IE    | RC2IE    | TX2IE         | TMR4IE   | CCP5IE | CCP4IE  | CCP3IE  | 60                         |

| TMR4   | Timer4 Register        |           |          |               |          |        |         |         | 61                         |

| T4CON  | —                      | T4OUTPS3  | T4OUTPS2 | T4OUTPS1      | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 61                         |

| PR4    | Timer4 Period Register |           |          |               |          |        |         |         | 61                         |

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used by the Timer4 module.

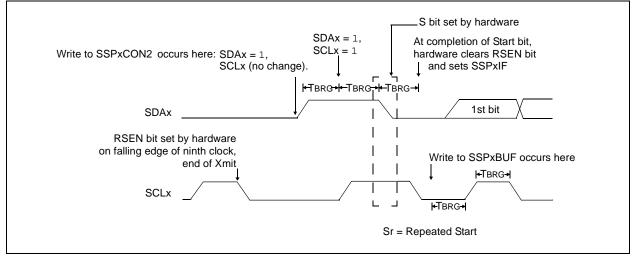

#### 19.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 19.4.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 19-20: REPEATED START CONDITION WAVEFORM

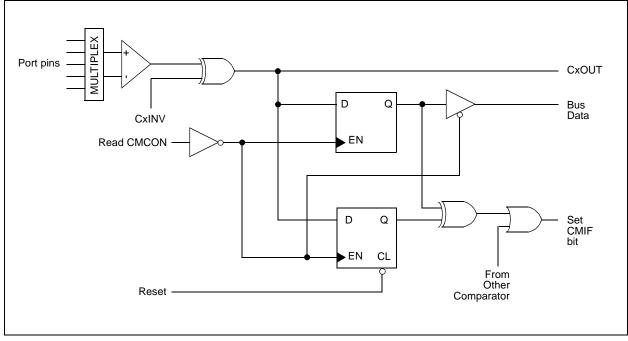

### 22.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR2         |

|       | register) interrupt flag may not get set.  |

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit, CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

## 22.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 22.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM<2:0> = 111). However, the input pins (RF3 through RF6) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is also determined by the setting of the PCFG<3:0> bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

#### REGISTER 25-13: DEVID1: DEVICE ID REGISTER 1 FOR THE PIC18F8722 FAMILY

| R                | R           | R                | R    | R                                       | R                | R        | R     |  |

|------------------|-------------|------------------|------|-----------------------------------------|------------------|----------|-------|--|

| DEV2             | DEV1        | DEV0             | REV4 | REV3                                    | REV2             | REV1     | REV0  |  |

| bit 7            |             |                  |      |                                         |                  |          | bit ( |  |

| Legend:          |             |                  |      |                                         |                  |          |       |  |

| R = Reada        | ole bit     | W = Writable     | bit  | U = Unimpler                            | nented bit, read | d as '0' |       |  |

| -n = Value a     | at POR      | '1' = Bit is set |      | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

|                  |             |                  |      |                                         |                  |          |       |  |

| bit 7-5          | DEV<2:0>: [ | Device ID bits   |      |                                         |                  |          |       |  |

|                  | 001 = PIC18 | F8722            |      |                                         |                  |          |       |  |

|                  | 111 = PIC18 | F8627            |      |                                         |                  |          |       |  |

|                  | 101 = PIC18 | F8622            |      |                                         |                  |          |       |  |

| 011 = PIC18F8527 |             |                  |      |                                         |                  |          |       |  |

|                  | 000 = PIC18 | F6722            |      |                                         |                  |          |       |  |

|                  | 110 = PIC18 | F6627            |      |                                         |                  |          |       |  |

|                  | 100 = PIC18 | F6622            |      |                                         |                  |          |       |  |

|                  | 010 = PIC18 | F6527            |      |                                         |                  |          |       |  |

|         | 010 = PIC 10 F 0027                                  |

|---------|------------------------------------------------------|

| bit 4-0 | REV<4:0>: Revision ID bits                           |

|         | These bits are used to indicate the device revision. |

#### REGISTER 25-14: DEVID2: DEVICE ID REGISTER 2 FOR THE PIC18F8722 FAMILY

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

| Legend:           |                                                                |                      |                    |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | adable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0 **DEV<10:3>:** Device ID bits<sup>(1)</sup>

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

0001 0100 = PIC18F6722/8722 devices

0001 0011 = PIC18F6527/6622/6627/8527/8622/8627 devices

**Note 1:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

#### 25.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

#### 25.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

### 25.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

### 25.7 In-Circuit Serial Programming

The PIC18F8722 family of devices can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 25.8 In-Circuit Debugger

When the  $\overline{\text{DEBUG}}$  Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 25-4 shows which resources are required by the background debugger.

|  | TABLE 25-4: | DEBUGGER RESOURCES |

|--|-------------|--------------------|

|--|-------------|--------------------|

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to RG5/MCLR/VPP, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

### 25.9 Single-Supply ICSP Programming

The LVP Configuration bit enables Single-Supply ICSP Programming (formerly known as Low-Voltage ICSP Programming or LVP). When Single-Supply Programming is enabled, the microcontroller can be programmed witho<u>ut requiring high voltage being applied to the</u> RG5/MCLR/VPP pin, but the RB5/KBI1/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

While programming, using single-<u>supply</u> programming mode, VDD is applied to the RG5/MCLR/VPP pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: By default, Single-Supply ICSP is enabled in unprogrammed devices (as supplied from Microchip) and erased devices.

- **3:** When Single-Supply Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- 4: When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared. RB5/KBI1/PGM then becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the RG5/ MCLR/VPP pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

| POP                                                                                                                                                                                                                                                                                                     |                               | Рор Тор о             | f Retur   | n Stack          | 1  |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----------|------------------|----|---------------|

| Synta                                                                                                                                                                                                                                                                                                   | ax:                           | POP                   |           |                  |    |               |

| Oper                                                                                                                                                                                                                                                                                                    | ands:                         | None                  |           |                  |    |               |

| Oper                                                                                                                                                                                                                                                                                                    | ation:                        | $(TOS) \rightarrow b$ | it bucke  | et               |    |               |

| Statu                                                                                                                                                                                                                                                                                                   | s Affected:                   | None                  |           |                  |    |               |

| Enco                                                                                                                                                                                                                                                                                                    | ding:                         | 0000                  | 0000      | 000              | 0  | 0110          |

| Description: The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                               |                       |           |                  |    |               |

| Word                                                                                                                                                                                                                                                                                                    | ls:                           | 1                     |           |                  |    |               |

| Cycle                                                                                                                                                                                                                                                                                                   | es:                           | 1                     |           |                  |    |               |

| QC                                                                                                                                                                                                                                                                                                      | ycle Activity:                |                       |           |                  |    |               |

|                                                                                                                                                                                                                                                                                                         | Q1                            | Q2                    | C         | 23               |    | Q4            |

|                                                                                                                                                                                                                                                                                                         | Decode                        | No<br>operation       | POP<br>va | TOS<br>lue       | ор | No<br>eration |

| <u>Exan</u>                                                                                                                                                                                                                                                                                             | nple:                         | POP<br>GOTO           | NEW       |                  |    |               |

| Before Instruction<br>TOS<br>Stack (1 level d                                                                                                                                                                                                                                                           |                               |                       | =<br>=    | 0031A2<br>014332 |    |               |

|                                                                                                                                                                                                                                                                                                         | After Instructic<br>TOS<br>PC | n                     | =<br>=    | 014332<br>NEW    | 2h |               |

| PUS                                                    | н                           | Push Top o                                                                                | of Ret                              | urn Stac                                     | k                              |                                      |  |  |

|--------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|--------------------------------|--------------------------------------|--|--|

| Synta                                                  | ax:                         | PUSH                                                                                      |                                     |                                              |                                |                                      |  |  |

| Oper                                                   | ands:                       | None                                                                                      |                                     |                                              |                                |                                      |  |  |

| Oper                                                   | ation:                      | $(PC + 2) \rightarrow$                                                                    | тоѕ                                 |                                              |                                |                                      |  |  |

| Statu                                                  | is Affected:                | None                                                                                      |                                     |                                              |                                |                                      |  |  |

| Enco                                                   | oding:                      | 0000                                                                                      | 0000                                | 000                                          | 0                              | 0101                                 |  |  |

| Desc                                                   | ription:                    | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack.<br>shed c<br>tion a<br>ack by | The prev<br>lown on<br>llows imp<br>modifyir | ious<br>the s<br>blem<br>ng Tr | TOS<br>stack.<br>lenting a<br>OS and |  |  |

| Word                                                   | ds:                         | 1                                                                                         | 1                                   |                                              |                                |                                      |  |  |

| Cycle                                                  | es:                         | 1                                                                                         | 1                                   |                                              |                                |                                      |  |  |

| QC                                                     | ycle Activity:              |                                                                                           |                                     |                                              |                                |                                      |  |  |

|                                                        | Q1                          | Q2                                                                                        |                                     | Q3                                           |                                | Q4                                   |  |  |

|                                                        | Decode                      | PUSH<br>PC + 2 onto<br>return stack                                                       |                                     | No<br>ration                                 | ор                             | No<br>peration                       |  |  |

| Exan                                                   | nple:                       | PUSH                                                                                      |                                     |                                              |                                |                                      |  |  |

|                                                        | Before Instruc<br>TOS<br>PC | tion                                                                                      | =<br>=                              | 345Ah<br>0124h                               |                                |                                      |  |  |

| After Instruction<br>PC<br>TOS<br>Stack (1 level down) |                             |                                                                                           | =<br>=<br>=                         | 0126h<br>0126h<br>345Ah                      |                                |                                      |  |  |

| SUB                                                  | WFB                              | Subtract                                                                                                                                                                                                    | W from f                                                                            | with Bor                                                               | ·ow                                              |  |  |  |  |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| Synta                                                | ax:                              | SUBWFB                                                                                                                                                                                                      | f {,d {,a}                                                                          | }                                                                      |                                                  |  |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                  |                                                                                                                                                                                                             |                                                                                     |                                                                        |                                                  |  |  |  |  |

| •                                                    | ation:                           |                                                                                                                                                                                                             | $-(\overline{C}) \rightarrow de$                                                    | st                                                                     |                                                  |  |  |  |  |

|                                                      | s Affected:                      | N, OV, C,                                                                                                                                                                                                   | DC, Z                                                                               |                                                                        | ·                                                |  |  |  |  |

| Enco                                                 | -                                | 0101                                                                                                                                                                                                        | 10da                                                                                | ffff                                                                   | ffff                                             |  |  |  |  |

| Desc                                                 | ription:                         | Subtract W and the Carry flag (borrow)<br>from register 'f' (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default). |                                                                                     |                                                                        |                                                  |  |  |  |  |

|                                                      |                                  | If 'a' is '1',                                                                                                                                                                                              |                                                                                     | s used to                                                              | s selected.<br>select the                        |  |  |  |  |

|                                                      |                                  | set is ena<br>in Indexed<br>mode whe<br>Section 2<br>Bit-Orien                                                                                                                                              | and the ex<br>bled, this i<br>d Literal O<br>enever f ≤<br>26.2.3 "By<br>ted Instru | nstructior<br>ffset Addr<br>95 (5Fh).<br><b>te-Orient</b><br>ctions in | n operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |  |

| Word                                                 | ls:                              | 1                                                                                                                                                                                                           |                                                                                     |                                                                        |                                                  |  |  |  |  |

| Cycle                                                |                                  | 1                                                                                                                                                                                                           |                                                                                     |                                                                        |                                                  |  |  |  |  |

| QC                                                   | ycle Activity:                   | 0.0                                                                                                                                                                                                         |                                                                                     | _                                                                      | <b>.</b>                                         |  |  |  |  |

|                                                      | Q1<br>Decode                     | Q2<br>Read                                                                                                                                                                                                  | Q:<br>Proce                                                                         |                                                                        | Q4<br>Write to                                   |  |  |  |  |

|                                                      | Decoue                           | register 'f'                                                                                                                                                                                                | Dat                                                                                 |                                                                        | estination                                       |  |  |  |  |

| <u>Exan</u>                                          | nple 1:                          | SUBWFB                                                                                                                                                                                                      | REG,                                                                                | 1, 0                                                                   |                                                  |  |  |  |  |

|                                                      | Before Instruct                  | ion                                                                                                                                                                                                         |                                                                                     |                                                                        |                                                  |  |  |  |  |

|                                                      | REG<br>W<br>C                    | = 19h<br>= 0Dh<br>= 1                                                                                                                                                                                       | (000<br>(000                                                                        | 1 1001)<br>0 1101)                                                     |                                                  |  |  |  |  |

|                                                      | After Instructio                 |                                                                                                                                                                                                             |                                                                                     |                                                                        |                                                  |  |  |  |  |

|                                                      | REG<br>W<br>C<br>Z               | = 0Ch<br>= 0Dh<br>= 1<br>= 0                                                                                                                                                                                | (000<br>(000                                                                        | 0 1011)<br>0 1101)                                                     |                                                  |  |  |  |  |

|                                                      | N                                | = 0<br>= 0                                                                                                                                                                                                  | ; resu                                                                              | lt is posit                                                            | ve                                               |  |  |  |  |

| Exan                                                 | nple 2:                          | SUBWFB                                                                                                                                                                                                      | REG, 0                                                                              | , 0                                                                    |                                                  |  |  |  |  |

|                                                      | Before Instruct                  |                                                                                                                                                                                                             |                                                                                     |                                                                        |                                                  |  |  |  |  |

|                                                      | REG<br>W<br>C                    | = 1Bh<br>= 1Ah<br>= 0                                                                                                                                                                                       |                                                                                     | 1 1011)<br>1 1010)                                                     |                                                  |  |  |  |  |

|                                                      | After Instructio<br>REG<br>W     | = 1Bh<br>= 00h                                                                                                                                                                                              | (000                                                                                | 1 1011)                                                                |                                                  |  |  |  |  |

|                                                      | C<br>Z<br>N                      | = 1<br>= 1<br>= 0                                                                                                                                                                                           | ; resu                                                                              | lt is zero                                                             |                                                  |  |  |  |  |

|                                                      | nple 3:                          | SUBWFB                                                                                                                                                                                                      | REG,                                                                                | 1, 0                                                                   |                                                  |  |  |  |  |

|                                                      | Before Instruct<br>REG<br>W<br>C | ion<br>= 03h<br>= 0Eh<br>= 1                                                                                                                                                                                |                                                                                     | 0 0011)<br>0 1101)                                                     |                                                  |  |  |  |  |

|                                                      | After Instructio<br>REG          | = F5h                                                                                                                                                                                                       |                                                                                     | 1 0100)<br>comp]                                                       |                                                  |  |  |  |  |

|                                                      | W<br>C<br>Z<br>N                 | = 0Eh<br>= 0<br>= 0                                                                                                                                                                                         | (000                                                                                | 0 1101)                                                                |                                                  |  |  |  |  |

|                                                      | N                                | = 1                                                                                                                                                                                                         | ; resu                                                                              | lt is nega                                                             | tive                                             |  |  |  |  |

| SWAPF                                       | Swap f                                                                                                 |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|--|--|--|--|

| Syntax:                                     | SWAPF f                                                                                                | {,d {,a}}                                                                                                                                                                    |                                                                   |                                                |  |  |  |  |

| Operands:                                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                    | d ∈ [0,1]                                                                                                                                                                    |                                                                   |                                                |  |  |  |  |

| Operation:                                  | (f<3:0>) →<br>(f<7:4>) →                                                                               |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| Status Affected:                            | None                                                                                                   |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| Encoding:                                   | 0011                                                                                                   | 10da                                                                                                                                                                         | ffff                                                              | ffff                                           |  |  |  |  |

| Description:                                | 'f' are exch<br>is placed ir                                                                           | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed in register 'f' (default). |                                                                   |                                                |  |  |  |  |

|                                             | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank                                                       | he BSR                                                                                                                                                                       | is used to                                                        |                                                |  |  |  |  |

|                                             | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 26<br>Bit-Oriento<br>Literal Offi | led, this i<br>Literal O<br>never f ≤<br>5.2.3 "By<br>ed Instru                                                                                                              | nstruction<br>ffset Addro<br>95 (5Fh).<br>te-Oriento<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |  |

| Words:                                      | 1                                                                                                      |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| Cycles:                                     | 1                                                                                                      |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| Q Cycle Activity:                           |                                                                                                        |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| Q1                                          | Q2                                                                                                     | Q3                                                                                                                                                                           | 3                                                                 | Q4                                             |  |  |  |  |

| Decode                                      | Read<br>register 'f'                                                                                   | Proce<br>Data                                                                                                                                                                |                                                                   | Vrite to<br>stination                          |  |  |  |  |

| Example:                                    | SWAPF I                                                                                                | REG, 1,                                                                                                                                                                      | 0                                                                 |                                                |  |  |  |  |

| Before Instruction                          |                                                                                                        |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

| REG = 53h<br>After Instruction<br>REG = 35h |                                                                                                        |                                                                                                                                                                              |                                                                   |                                                |  |  |  |  |

## 27.11 PICSTART<sup>®</sup> Plus Development Programmer

The PICSTART<sup>®</sup> Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 27.12 PICkit<sup>™</sup> 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 27.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 28.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               | 300 mA               |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iικ (Vι < 0 or Vι > VDD)                | ±20 mA               |