Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8722-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>QUARTZ CRYSTALS

| Osc Type | Crystal<br>Freq                     | Typical Capacitor Values<br>Tested:       |                                           |  |

|----------|-------------------------------------|-------------------------------------------|-------------------------------------------|--|

|          | Fieq                                | C1                                        | C2                                        |  |

| LP       | 32 kHz                              | 22 pF                                     | 22 pF                                     |  |

| XT       | 1 MHz<br>4 MHz                      | 22 pF<br>22 pF                            | 22 pF<br>22 pF                            |  |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF |  |

### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588 PIC<sup>®</sup> Microcontroller Oscillator Design Guide

- AN826 Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices

- AN849 Basic PIC® Oscillator Design

- AN943 Practical PIC<sup>®</sup> Oscillator Analysis and Design

- AN949 Making Your Oscillator Work

See the notes following this table for additional information.

**Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

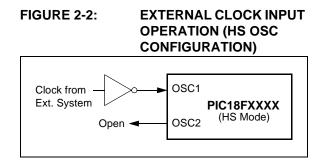

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2. When operated in this mode, parameters D033 and D043 apply.

# 2.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

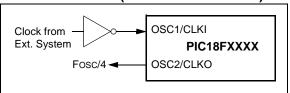

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

### FIGURE 2-3:

#### EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

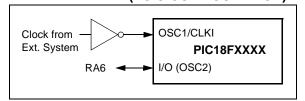

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode. When operated in this mode, parameters D033A and D043A apply.

### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

# 2.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the configured oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin in crystal oscillator modes) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the powermanaged mode (see Section 25.2 "Watchdog Timer (WDT)" and Section 25.4 "Fail-Safe Clock Monitor" for more information). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output. The INTOSC output is also enabled for Two-Speed Start-up at 1 MHz after Resets and when configured for wake from Sleep mode.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a realtime clock. Other features may be operating that do not require a device clock source (i.e., SSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 28.2 "DC Characteristics".

# 2.9 Power-up Delays

Power-up delays are controlled by two or three timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT) which provides a fixed delay on power-up (parameter 33, Table 28-12). It is enabled by clearing (= 0) the PWRTEN Configuration bit (CONFIG2L<0>).

## 2.9.1 DELAYS FOR POWER-UP AND RETURN TO PRIMARY CLOCK

The second timer is the Oscillator Start-up Timer (OST), intended to delay execution until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, a third timer delays execution for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency. At the end of these delays, the OSTS bit (OSCCON<3>) is set.

There is a delay of interval TCSD (parameter 38, Table 28-12), once execution is allowed to start, when the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |  |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------|--|--|

| RC, INTIO1    | Floating, external resistor pulls high                | At logic low (clock/4 output)                         |  |  |

| RCIO          | Floating, external resistor pulls high                | Configured as PORTA, bit 6                            |  |  |

| INTIO2        | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |  |  |

| ECIO          | Floating, driven by external clock                    | Configured as PORTA, bit 6                            |  |  |

| EC            | Floating, driven by external clock                    | At logic low (clock/4 output)                         |  |  |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |  |

TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 4-2 in **Section 4.0** "**Reset**" for time-outs due to Sleep and MCLR Reset.

# 5.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.1.5.1 "Computed GOTO**").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

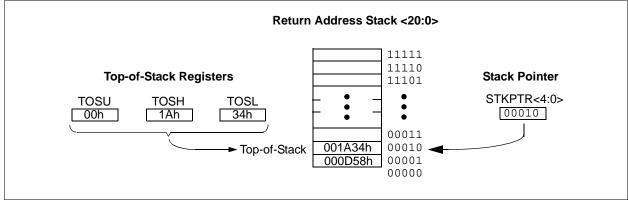

# 5.1.3 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions. The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special File Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a POP from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

# 5.1.3.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

# FIGURE 5-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### 5.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.4 FAST REGISTER STACK

A fast register stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, | FAST | ;STATUS, WREG, BSR      |

|------------|------|-------------------------|

|            |      | ;SAVED IN FAST REGISTER |

|            |      | ; STACK                 |

| •          |      |                         |

| •          |      |                         |

|            |      |                         |

| SUB1 •     |      |                         |

| •          |      |                         |

| RETURN,    | FAST | ;RESTORE VALUES SAVED   |

|            |      | ;IN FAST REGISTER STACK |

#### 5.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of  ${\tt RETLW}\ {\tt nn}$  instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

PCL" instruction does not The "ADDWF Note: update the PCLATH and PCLATU registers. A read operation on PCL must be performed to update PCLATH and PCLATU.

| EXAM      | PLE 5-2:                                         | COMPU                           | ITED GC | TO USING AN OFFSET VALUE                                                                                                                            |

|-----------|--------------------------------------------------|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| MAIN:     | ORG<br>MOVLW<br>CALL                             | 0x0000<br>0x00<br>TABLE         |         |                                                                                                                                                     |

| <br>TABLE | ORG<br>MOVF<br>RLNCF<br>ADDWF                    | 0x8000<br>PCL, F<br>W, W<br>PCL | ;       | A simple read of PCL will update PCLATH, PCLATU<br>Multiply by 2 to get correct offset in table<br>Add the modified offset to force jump into table |

|           | RETLW<br>RETLW<br>RETLW<br>RETLW<br>RETLW<br>END | `A'<br>`B'<br>`C'<br>`D'<br>`E' |         |                                                                                                                                                     |

#

### 8.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADRH:EEADR register pair, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available on the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 8-1.

# 8.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADRH:EEADR register pair and the data written to the EEDATA register. The sequence in Example 8-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, EECON1, EEADRH:EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

# 8.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

EXAMPLE 8-1: DATA EEPROM READ

| MOVLW<br>MOVWF | DATA_EE_ADDRH<br>EEADRH | ;<br>; Upper bits of Data Memory Address to read |

|----------------|-------------------------|--------------------------------------------------|

| MOVLW          | DATA_EE_ADDR            | ;                                                |

| MOVWF          | EEADR                   | ; Lower bits of Data Memory Address to read      |

| BCF            | EECON1, EEPGD           | ; Point to DATA memory                           |

| BCF            | EECON1, CFGS            | ; Access EEPROM                                  |

| BSF            | EECON1, RD              | ; EEPROM Read                                    |

| MOVF           | EEDATA, W               | ; W = EEDATA                                     |

|                |                         |                                                  |

| EXAMPLE 8-2: | DATA EEPROM WRITE |

|--------------|-------------------|

|              |                   |

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | ;                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EPGD  | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | i                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | 0AAh          | ;                                             |

|          | MOVWF | EECON2        | ; Write OAAh                                  |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

|          |       |               |                                               |

# 11.4 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power-on Reset, these pins are | Э |

|-------|-------------------------------------|---|

|       | configured as digital inputs.       |   |

In 80-pin devices, PORTD is multiplexed with the system bus as part of the external memory interface. I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled, PORTD is the low-order byte of the multiplexed address/data bus (AD<7:0>). The TRISD bits are also overridden.

PORTD can also be configured to function as an 8-bit wide parallel microprocessor port by setting the PSPMODE control bit (PSPCON<4>). In this mode, parallel port data takes priority over other digital I/O (but not the external memory interface). When the parallel port is active, the input buffers are TTL. For more information, refer to **Section 11.10** "**Parallel Slave Port**".

#### EXAMPLE 11-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATD  | ; Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                    |

|       |       | ; RD<5:4> as outputs                       |

|       |       | ; RD<7:6> as inputs                        |

|       |       |                                            |

# 11.5 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

All pins on PORTE are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power    | -on Reset,    | these | pins | are |

|-------|---------------|---------------|-------|------|-----|

|       | configured as | digital input | s.    |      |     |

When the device is operating in Microcontroller mode, pin RE7 can be configured as the alternate peripheral pin for the ECCP2 module. This is done by clearing the CCP2MX Configuration bit.

In 80-pin devices, PORTE is multiplexed with the system bus as part of the external memory interface. I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled (80-pin devices only), PORTE is the high-order byte of the multiplexed address/data bus (AD<15:8>). The TRISE bits are also overridden.

When the Parallel Slave Port is active on PORTD, three of the PORTE pins (RE0/AD8/RD/P2D, RE1/AD9/WR/P2C and RE2/AD10/CS/P2B) are configured as digital control inputs for the port. The control functions are summarized in Table 11-9. The reconfiguration occurs automatically when the PSPMODE control bit (PSPCON<4>) is set. Users must still make certain the corresponding TRISE bits are set to configure these pins as digital inputs.

| EXAMP | 'LE 11-5 | : INITIALIZING PORTE    |

|-------|----------|-------------------------|

| CLRF  | PORTE    | ; Initialize PORTE by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATE     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 03h      | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISE    | ; Set RE<1:0> as inputs |

|       |          | ; RE<7:2> as outputs    |

|       |          |                         |

### EXAMPLE 11-5: INITIALIZING PORTE

### 19.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and the SDAx line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPxSTAT<0>) is set, or bit SSPOV (SSPxCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. The interrupt flag bit, SSPxIF, must be cleared in software. The SSPxSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPxCON2<0> = 1), SCLx will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPxCON1<4>). See **Section 19.4.4** "Clock **Stretching**" for more detail.

# 19.4.3.3 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register. The ACK pulse will be sent on the ninth bit and pin SCLx is held low regardless of SEN (see **Section 19.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then pin SCLx should be enabled by setting bit, CKP (SSPxCON1<4>). The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time (Figure 19-9).

The ACK pulse from the master-receiver is latched on the rising edge of the <u>ninth</u> SCLx input pulse. If the SDAx line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPxSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, pin SCLx must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared in software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

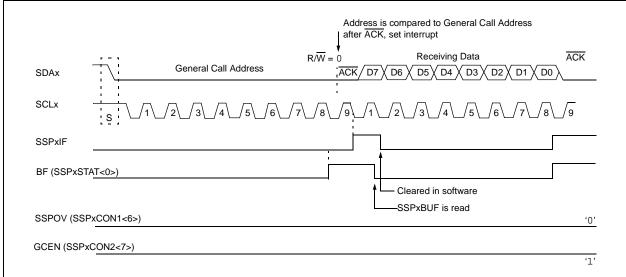

#### 19.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPxCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPxSR and the address is compared against the SSPxADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPxSR is transferred to the SSPxBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPxIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPxBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPxADD is required to be updated for the second half of the address to match and the UA bit is set (SSPxSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 19-15).

|       |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|-------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc                  | = 40.000                      | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2   | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4   | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6   | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2  | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6  | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2 | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | —          | —                           |

# TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|              | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                       |            |                             |                       |                  |                             |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 4.000 MHz              |            |                             | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                         | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16            | 207                         |  |

| 1.2          | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16            | 51                          |  |

| 2.4          | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16            | 25                          |  |

| 9.6          | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _                | —                           |  |

| 19.2         | 19.231                        | 0.16       | 12                          | —                     | _          | _                           | —                     | _                | —                           |  |

| 57.6         | 62.500                        | 8.51       | 3                           | —                     | _          | _                           | —                     | _                | _                           |  |

| 115.2        | 125.000                       | 8.51       | 1                           | _                     | —          | —                           | _                     | —                |                             |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                                                      |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00                                                 | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00                                                 | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02                                                 | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06                                                 | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03                                                | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35                                                 | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22                                                | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 11.7647               | -2.12      | 16                          |

|       |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |                  |                             |                       |                  |                             |  |

|-------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD  | Fosc = 4.000 MHz      |                                                      |                             | Fos                   | Fosc = 2.000 MHz |                             |                       | Fosc = 1.000 MHz |                             |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3   | 0.300                 | 0.01                                                 | 3332                        | 0.300                 | -0.04            | 1665                        | 0.300                 | -0.04            | 832                         |  |

| 1.2   | 1.200                 | 0.04                                                 | 832                         | 1.201                 | -0.16            | 415                         | 1.201                 | -0.16            | 207                         |  |

| 2.4   | 2.404                 | 0.16                                                 | 415                         | 2.403                 | -0.16            | 207                         | 2.403                 | -0.16            | 103                         |  |

| 9.6   | 9.615                 | 0.16                                                 | 103                         | 9.615                 | -0.16            | 51                          | 9.615                 | -0.16            | 25                          |  |

| 19.2  | 19.231                | 0.16                                                 | 51                          | 19.230                | -0.16            | 25                          | 19.230                | -0.16            | 12                          |  |

| 57.6  | 58.824                | 2.12                                                 | 16                          | 55.555                | 3.55             | 8                           | —                     | —                | —                           |  |

| 115.2 | 111.111               | -3.55                                                | 8                           | —                     | _                | _                           |                       | —                | —                           |  |

NOTES:

# REGISTER 25-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| R/C-1             |                      | R/C-1                         | R/C-1              | R/C-1                            | R/C-1          | R/C-1           | R/C-1 |

|-------------------|----------------------|-------------------------------|--------------------|----------------------------------|----------------|-----------------|-------|

| CP7 <sup>(1</sup> | ) CP6 <sup>(1)</sup> | CP5 <sup>(2)</sup>            | CP5 <sup>(2)</sup> | CP3 <sup>(3)</sup>               | CP2            | CP1             | CP0   |

| bit 7             |                      |                               |                    |                                  |                |                 | bit ( |

| Legend:           |                      |                               |                    |                                  |                |                 |       |

| R = Read          | able bit             | W = Writable                  | bit                | U = Unimplen                     | nented bit, re | ad as '0'       |       |

| -n = Value        | at POR               | '1' = Bit is set              |                    | '0' = Bit is clea                | ared           | x = Bit is unkr | nown  |

| bit 7             | CP7: Code P          | Protection bit <sup>(1)</sup> |                    |                                  |                |                 |       |

|                   | 1 = Block 7 (        | 01C000-01FFF<br>01C000-01FFF  |                    |                                  |                |                 |       |

| bit 6             | CP6: Code P          | Protection bit <sup>(1)</sup> |                    |                                  |                |                 |       |

|                   | •                    | 01BFFF-01800<br>01BFFF-01800  |                    |                                  |                |                 |       |

| bit 5             | CP5: Code P          | Protection bit <sup>(2)</sup> |                    |                                  |                |                 |       |

|                   |                      | 014000-017FF<br>014000-017FF  |                    |                                  |                |                 |       |

| bit 4             | CP4: Code P          | Protection bit <sup>(2)</sup> |                    |                                  |                |                 |       |

|                   |                      | 010000-013FF<br>010000-013FF  |                    |                                  |                |                 |       |

| bit 3             | CP3: Code P          | Protection bit <sup>(3)</sup> |                    |                                  |                |                 |       |

|                   | •                    | 00C000-00FFF<br>00C000-00FFF  | ,                  | •                                |                |                 |       |

| bit 2             | CP2: Code P          | rotection bit                 |                    |                                  |                |                 |       |

|                   |                      | 008000-00BFF<br>008000-00BFF  |                    |                                  |                |                 |       |

| bit 1             | CP1: Code P          | rotection bit                 |                    |                                  |                |                 |       |

|                   |                      | 004000-007FF<br>004000-007FF  |                    |                                  |                |                 |       |

| bit 0             | CP0: Code P          |                               |                    |                                  |                |                 |       |

|                   |                      |                               |                    | )-003FFFh) not<br>)-003FFFh) coc |                | ed              |       |

| Note 1:           | Unimplemented in     |                               |                    |                                  |                |                 |       |

| 2:                | Unimplemented in     |                               |                    |                                  |                | set.            |       |

| 3:                | Unimplemented in     | PIC18F6527/8                  | 3527 devices;      | maintain this bi                 | it set.        |                 |       |

4: Boot block size is determined by the BBSIZ<1:0> bits in CONFIG4L.

# REGISTER 25-9: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| R/C-1               | R/C-1               | R/C-1                        | R/C-1               | R/C-1                           | R/C-1           | R/C-1           | R/C-1 |

|---------------------|---------------------|------------------------------|---------------------|---------------------------------|-----------------|-----------------|-------|

| WRT7 <sup>(1)</sup> | WRT6 <sup>(1)</sup> | WRT5 <sup>(2)</sup>          | WRT4 <sup>(2)</sup> | WRT3 <sup>(3)</sup>             | WRT2            | WRT1            | WRT0  |

| bit 7               | •                   |                              | •                   |                                 |                 | •               | bit ( |

| Legend:             |                     |                              |                     |                                 |                 |                 |       |

| R = Readal          | ble bit             | W = Writable                 | bit                 | U = Unimplem                    | nented bit, rea | ad as '0'       |       |

| -n = Value a        | at POR              | '1' = Bit is set             |                     | '0' = Bit is clea               | ared            | x = Bit is unkr | nown  |

| bit 7               | WRT7: Write         | Protection bit <sup>(1</sup> | )                   |                                 |                 |                 |       |

|                     |                     | 01C000-01FFF<br>01C000-01FFF |                     |                                 |                 |                 |       |

| bit 6               | WRT6: Write         | Protection bit(              | )                   |                                 |                 |                 |       |

|                     | •                   | 01BFFF-01800<br>01BFFF-01800 | · ·                 |                                 |                 |                 |       |

| bit 5               | WRT5: Write         | Protection bit <sup>(2</sup> | 2)                  |                                 |                 |                 |       |

|                     |                     | 014000-017FF<br>014000-017FF |                     |                                 |                 |                 |       |

| bit 4               | WRT4: Write         | Protection bit <sup>(2</sup> | 2)                  |                                 |                 |                 |       |

|                     |                     | 010000-013FF<br>010000-013FF |                     |                                 |                 |                 |       |

| bit 3               |                     | Protection bit(              |                     |                                 |                 |                 |       |

|                     |                     | 00C000-00FFF<br>00C000-00FFF |                     |                                 |                 |                 |       |

| bit 2               | WRT2: Write         | Protection bit               |                     |                                 |                 |                 |       |

|                     | ·                   | 008000-00BFF<br>008000-00BFF | , ,                 |                                 |                 |                 |       |

| bit 1               | WRT1: Write         | Protection bit               |                     |                                 |                 |                 |       |

|                     |                     | 004000-007FF<br>004000-007FF |                     |                                 |                 |                 |       |

| bit 0               |                     | Protection bit               |                     |                                 |                 |                 |       |

|                     |                     |                              |                     | -003FFFh) not<br>-003FFFh) writ |                 | ed              |       |

|                     | Unimplemented in    |                              |                     |                                 |                 |                 |       |

|                     | Unimplemented in    |                              |                     |                                 |                 | set.            |       |

| 3:                  | Unimplemented in    | PIC18F6527/8                 | 3527 devices;       | maintain this bi                | t set.          |                 |       |

4: Boot block size is determined by the BBSIZ<1:0> bits in CONFIG4L.

### 25.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

### 25.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

# 25.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

# 25.7 In-Circuit Serial Programming

The PIC18F8722 family of devices can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 25.8 In-Circuit Debugger

When the  $\overline{\text{DEBUG}}$  Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 25-4 shows which resources are required by the background debugger.

|  | TABLE 25-4: | DEBUGGER RESOURCES |

|--|-------------|--------------------|

|--|-------------|--------------------|

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to RG5/MCLR/VPP, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

# 25.9 Single-Supply ICSP Programming

The LVP Configuration bit enables Single-Supply ICSP Programming (formerly known as Low-Voltage ICSP Programming or LVP). When Single-Supply Programming is enabled, the microcontroller can be programmed witho<u>ut requiring high voltage being applied to the</u> RG5/MCLR/VPP pin, but the RB5/KBI1/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

While programming, using single-<u>supply</u> programming mode, VDD is applied to the RG5/MCLR/VPP pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: By default, Single-Supply ICSP is enabled in unprogrammed devices (as supplied from Microchip) and erased devices.

- **3:** When Single-Supply Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- 4: When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared. RB5/KBI1/PGM then becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the RG5/ MCLR/VPP pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

| DAW                           | Decimal A             | djust W Regis                      | ster       | DECF                                                        | Decremen                 | t f                                 |                 |  |

|-------------------------------|-----------------------|------------------------------------|------------|-------------------------------------------------------------|--------------------------|-------------------------------------|-----------------|--|

| Syntax:                       | DAW                   |                                    |            | Syntax:                                                     | DECF f{,                 | d {,a}}                             |                 |  |

| Operands:                     | None                  |                                    |            | Operands:                                                   | $0 \leq f \leq 255$      |                                     |                 |  |

| Operation:                    | lf [W<3:0> :          | > 9] or [DC = 1                    | ] then     |                                                             | d ∈ [0,1]                |                                     |                 |  |

|                               | , ,                   | $6 \rightarrow W < 3:0>;$          |            | On another                                                  | a ∈ [0,1]                |                                     |                 |  |

|                               | else<br>(W<3:0>) –    | → W<3:0>                           |            | Operation:                                                  | $(f) - 1 \rightarrow de$ |                                     |                 |  |

|                               | (11 10107)            |                                    |            | Status Affected:                                            | C, DC, N, (              |                                     |                 |  |

|                               |                       | > 9] or [C = 1]                    |            | Encoding:                                                   | 0000                     |                                     | ff fff          |  |

|                               | (VV<7:4>) +<br>C = 1; | $6 \rightarrow W < 7:4>;$          |            | Description:                                                |                          | register 'f'. If<br>red in W. If 'd |                 |  |

|                               | else                  |                                    |            |                                                             |                          | red back in re                      | ,               |  |

|                               | (W<7:4>) –            | → W<7:4>                           |            |                                                             | (default).               |                                     | 0               |  |

| Status Affected:              | С                     |                                    |            |                                                             |                          | he Access Ba                        |                 |  |

| Encoding: 0000 0000 0000 0111 |                       | 00 0111                            |            | If 'a' is '1', the BSR is used to selec GPR bank (default). |                          |                                     |                 |  |

| Description:                  | •                     | ts the eight-bit                   |            |                                                             |                          |                                     | lad in atruatio |  |

|                               | •                     | om the earlier a<br>each in packed |            |                                                             |                          | nd the extend<br>led, this instru   |                 |  |

|                               |                       | es a correct pa                    |            |                                                             | in Indexed               | Literal Offset                      | Addressing      |  |

|                               | result.               |                                    |            |                                                             |                          | hever $f \le 95$ (5                 | ,               |  |

| Words:                        | 1                     |                                    |            |                                                             |                          | .2.3 "Byte-Or<br>d Instruction      |                 |  |

| Cycles:                       | 1                     |                                    |            |                                                             | Literal Off              | set Mode" for                       | details.        |  |

| Q Cycle Activity:             |                       |                                    |            | Words:                                                      | 1                        |                                     |                 |  |

| Q1                            | Q2                    | Q3                                 | Q4         | Cycles:                                                     | 1                        |                                     |                 |  |

| Decode                        | Read<br>register W    | Process<br>Data                    | Write<br>W | Q Cycle Activity:                                           |                          |                                     |                 |  |

|                               | legister w            | Dala                               | ~~~        | Q1                                                          | Q2                       | Q3                                  | Q4              |  |

| Example 1:                    | DAW                   |                                    |            | Decode                                                      | Read                     | Process                             | Write to        |  |

| Before Instruc                | tion                  |                                    |            |                                                             | register 'f'             | Data                                | destination     |  |

| W<br>C                        | = A5h<br>= 0          |                                    |            | Example:                                                    | DECF                     | CNT, 1, 0                           | h               |  |

| DC                            | = 0                   |                                    |            | Before Instru                                               |                          | CN1, 1, C                           | )               |  |

| After Instruction             |                       |                                    |            | CNT                                                         | = 01h                    |                                     |                 |  |

| W<br>C                        | = 05h<br>= 1          |                                    |            | Z                                                           | = 0                      |                                     |                 |  |

| DC                            | = 0                   |                                    |            | After Instruct<br>CNT                                       | = 00h                    |                                     |                 |  |

| Example 2:                    |                       |                                    |            | Z                                                           | = 1                      |                                     |                 |  |

| Before Instruc                |                       |                                    |            |                                                             |                          |                                     |                 |  |

| W<br>C                        | = CEh<br>= 0          |                                    |            |                                                             |                          |                                     |                 |  |

| DC                            | = 0                   |                                    |            |                                                             |                          |                                     |                 |  |

| After Instructio<br>W         | on<br>= 34h           |                                    |            |                                                             |                          |                                     |                 |  |

| ••                            | = 1                   |                                    |            |                                                             |                          |                                     |                 |  |

| C<br>DC                       | = 0                   |                                    |            |                                                             |                          |                                     |                 |  |

| LFSF  | ર                                                         | Load FSR                                                            | Load FSR                                                             |               |                                       |  |  |  |  |  |

|-------|-----------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|---------------|---------------------------------------|--|--|--|--|--|

| Synta | ax:                                                       | LFSR f, k                                                           | (                                                                    |               |                                       |  |  |  |  |  |

| Oper  | ands:                                                     | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 408 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 4095 \end{array}$ |               |                                       |  |  |  |  |  |

| Oper  | ation:                                                    | $k\toFSRf$                                                          | $k \rightarrow FSRf$                                                 |               |                                       |  |  |  |  |  |

| Statu | s Affected:                                               | None                                                                |                                                                      |               |                                       |  |  |  |  |  |

| Enco  | ding:                                                     | 1110<br>1111                                                        | 1110<br>0000                                                         | 00ff<br>k7kkk | k11kkk<br>kkkk                        |  |  |  |  |  |

| Desc  | ription:                                                  | The 12-bit<br>file select                                           |                                                                      |               |                                       |  |  |  |  |  |

| Word  | ls:                                                       | 2                                                                   |                                                                      |               |                                       |  |  |  |  |  |

| Cycle | es:                                                       | 2                                                                   |                                                                      |               |                                       |  |  |  |  |  |

| QC    | ycle Activity:                                            |                                                                     |                                                                      |               |                                       |  |  |  |  |  |

|       | Q1                                                        | Q2                                                                  | Q3                                                                   |               | Q4                                    |  |  |  |  |  |

|       | Decode                                                    | Read literal<br>'k' MSB                                             | Proce:<br>Data                                                       | i li          | Write<br>teral 'k'<br>MSB to<br>FSRfH |  |  |  |  |  |

|       | Decode                                                    | Read literal<br>'k' LSB                                             | Proce:<br>Data                                                       |               | rite literal<br>to FSRfL              |  |  |  |  |  |

|       | Example: LFSR 2, 3ABh<br>After Instruction<br>FSR2H = 03h |                                                                     |                                                                      |               |                                       |  |  |  |  |  |

|       | FSR2L                                                     | = A                                                                 | Bh                                                                   |               |                                       |  |  |  |  |  |

| MOVF                                                                                                             | Move f                                                                                                                          |                                                                                                                                                                                                                                                                              |      |      |  |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|

| Syntax:                                                                                                          | MOVF f                                                                                                                          | {,d {,a}}                                                                                                                                                                                                                                                                    |      |      |  |  |  |

| Operands:                                                                                                        | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                             |                                                                                                                                                                                                                                                                              |      |      |  |  |  |

| Operation:                                                                                                       | $f \to \text{dest}$                                                                                                             | $f \rightarrow dest$                                                                                                                                                                                                                                                         |      |      |  |  |  |