Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | XCore                                                          |

| Core Size                  | 32-Bit 24-Core                                                 |

| Speed                      | 4000MIPS                                                       |

| Connectivity               | USB                                                            |

| Peripherals                | -                                                              |

| Number of I/O              | 176                                                            |

| Program Memory Size        | -                                                              |

| Program Memory Type        | ROMIess                                                        |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1M x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | External                                                       |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 374-LFBGA                                                      |

| Supplier Device Package    | 374-FBGA (18x18)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu224-1024-fb374-c40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 xCORE Multicore Microcontrollers

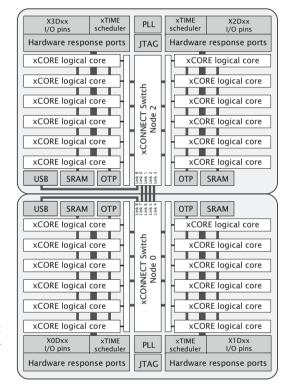

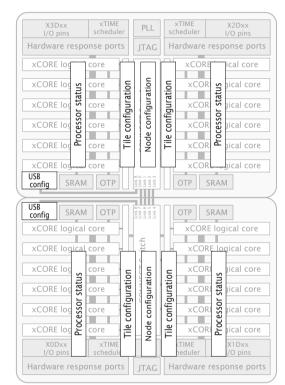

The xCORE-200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

Figure 1: XU224-1024-FB374 block diagram

Key features of the XU224-1024-FB374 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores

2

| Signal         | Function                                         |                       |                       |                   |                   | Туре | Properties |

|----------------|--------------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|------------|

| X1D17          | X <sub>0</sub> L3 <sup>0</sup> <sub>in</sub>     | 4D <sup>1</sup>       | 8B <sup>3</sup>       | 16A <sup>11</sup> |                   | 1/0  | IO, PD     |

| X1D18          | X <sub>0</sub> L3 <sup>0</sup> <sub>out</sub>    | 4D <sup>2</sup>       | 8B <sup>4</sup>       | 16A <sup>12</sup> |                   | I/O  | IO, PD     |

| X1D19          | X <sub>0</sub> L3 <sup>1</sup> <sub>out</sub>    | 4D <sup>3</sup>       | 8B <sup>5</sup>       | 16A <sup>13</sup> |                   | 1/0  | IO, PD     |

| X1D20          | NULSout                                          | 4C <sup>2</sup>       | 8B <sup>6</sup>       | 16A <sup>14</sup> | 32A <sup>30</sup> | 1/0  | IO, PD     |

| X1D20<br>X1D21 |                                                  | 4C <sup>3</sup>       | 8B <sup>7</sup>       | 16A <sup>15</sup> | 32A <sup>31</sup> | 1/0  | IO, PD     |

| X1D22          | X <sub>0</sub> L3 <sup>4</sup> 1C                | -                     | 00                    | IUA               | J2A               | 1/0  | IO, PD     |

| X1D23          | 1H                                               |                       |                       |                   |                   | 1/0  | IO, PD     |

| X1D23          | 11                                               |                       |                       |                   |                   | I/O  | IO, PD     |

| X1D24<br>X1D25 | 1J <sup>(</sup>                                  |                       |                       |                   |                   | 1/0  | IO, PD     |

| X1D25          | , ij                                             | 4E <sup>0</sup>       | 8C <sup>0</sup>       | 16B <sup>0</sup>  |                   | 1/0  | IOT, PD    |

| X1D20<br>X1D27 |                                                  | 4E <sup>1</sup>       | 8C <sup>1</sup>       | 16B <sup>1</sup>  |                   | 1/0  | IOT, PD    |

| X1D27<br>X1D28 |                                                  | 4E<br>4F <sup>0</sup> | 8C<br>8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O  | IOT, PD    |

| X1D28<br>X1D29 |                                                  | 4F <sup>3</sup>       | 8C <sup>-</sup>       | 16B <sup>-</sup>  |                   | 1/0  | IOT, PD    |

| X1D29<br>X1D30 |                                                  | 4F <sup>2</sup>       | 8C <sup>4</sup>       | 16B <sup>4</sup>  |                   |      |            |

| X1D30<br>X1D31 |                                                  | 4F <sup>2</sup>       | 8C <sup>5</sup>       | 168 <sup>5</sup>  |                   | I/O  | IOT, PD    |

| -              |                                                  |                       |                       | -                 |                   | I/O  | IOT, PD    |

| X1D32          |                                                  | 4E <sup>2</sup>       | 8C <sup>6</sup>       | 16B <sup>6</sup>  |                   | I/0  | IOT, PD    |

| X1D33          |                                                  | 4E <sup>3</sup>       | 8C <sup>7</sup>       | 16B <sup>7</sup>  |                   | I/0  | IOT, PD    |

| X1D34          | X <sub>0</sub> L0 <sup>2</sup> <sub>out</sub> 1K |                       |                       |                   |                   | I/O  | IO, PD     |

| X1D35          | X <sub>0</sub> L0 <sup>3</sup> <sub>out</sub> 1L |                       |                       |                   |                   | I/O  | IO, PD     |

| X1D36          | X <sub>0</sub> L0 <sup>4</sup> <sub>out</sub> 1M |                       | 8D <sup>0</sup>       | 16B <sup>8</sup>  |                   | I/O  | IO, PD     |

| X1D37          | X <sub>0</sub> L3 <sup>4</sup> 1N                |                       | 8D <sup>1</sup>       | 16B <sup>9</sup>  |                   | I/O  | IO, PD     |

| X1D38          | X <sub>0</sub> L3 <sup>3</sup> 1C                |                       | 8D <sup>2</sup>       | 16B <sup>10</sup> |                   | I/O  | IO, PD     |

| X1D39          | X <sub>0</sub> L3 <sup>2</sup> 1P                | 0                     | 8D <sup>3</sup>       | 16B <sup>11</sup> |                   | I/O  | IO, PD     |

| X1D40          |                                                  |                       | 8D <sup>4</sup>       | 16B <sup>12</sup> |                   | I/O  | IOT, PD    |

| X1D41          |                                                  |                       | 8D <sup>5</sup>       | 16B <sup>13</sup> |                   | I/0  | IOT, PD    |

| X1D42          |                                                  |                       | 8D <sup>6</sup>       | 16B <sup>14</sup> |                   | I/O  | IOT, PD    |

| X1D43          |                                                  |                       | 8D <sup>7</sup>       | 16B <sup>15</sup> |                   | I/O  | IOT, PD    |

| X1D49          | X <sub>0</sub> L1 <sup>4</sup> <sub>in</sub>     |                       |                       |                   | 32A <sup>0</sup>  | I/O  | IO, PD     |

| X1D50          | X <sub>0</sub> L1 <sup>3</sup><br>in             |                       |                       |                   | 32A <sup>1</sup>  | I/O  | IO, PD     |

| X1D51          | X <sub>0</sub> L1 <sup>2</sup> <sub>in</sub>     |                       |                       |                   | 32A <sup>2</sup>  | I/O  | IO, PD     |

| X1D52          | X <sub>0</sub> L1 <sup>1</sup>                   |                       |                       |                   | 32A <sup>3</sup>  | I/O  | IO, PD     |

| X1D53          | $X_0L1_{in}^0$                                   |                       |                       |                   | 32A <sup>4</sup>  | I/0  | IO, PD     |

| X1D54          | X <sub>0</sub> L1 <sup>0</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>5</sup>  | I/O  | IO, PD     |

| X1D55          | X <sub>0</sub> L1 <sup>1</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>6</sup>  | I/O  | IO, PD     |

| X1D56          | X <sub>0</sub> L1 <sup>2</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>7</sup>  | I/O  | IO, PD     |

| X1D57          | X <sub>0</sub> L1 <sup>3</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>8</sup>  | I/O  | IO, PD     |

| X1D58          | X <sub>0</sub> L1 <sup>4</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>9</sup>  | I/O  | IO, PD     |

| X1D61          | X <sub>0</sub> L2 <sup>4</sup>                   |                       |                       |                   | 32A <sup>10</sup> | I/0  | IO, PD     |

| X1D62          | X <sub>0</sub> L2 <sup>3</sup>                   |                       |                       |                   | 32A <sup>11</sup> | I/0  | IO, PD     |

| X1D63          | $X_0L2_{in}^2$                                   |                       |                       |                   | 32A <sup>12</sup> | I/O  | IO, PD     |

| X1D64          | X <sub>0</sub> L2 <sup>1</sup>                   |                       |                       |                   | 32A <sup>13</sup> | I/O  | IO, PD     |

| X1D65          | X <sub>0</sub> L2 <sup>0</sup>                   |                       |                       |                   | 32A <sup>14</sup> | I/O  | IO, PD     |

| X1D66          | X <sub>0</sub> L2 <sup>0</sup> <sub>out</sub>    |                       |                       |                   | 32A <sup>15</sup> | I/O  | IO, PD     |

|                |                                                  |                       |                       |                   |                   |      |            |

(continued)

XS2-U24A-1024-FB374

X009642,

| -XMOS <sup>®</sup> - |  |

|----------------------|--|

|----------------------|--|

(continued)

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Signal | Function                                                                      |                                     | Туре | Properties |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------|-------------------------------------|------|------------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D53  | X <sub>2</sub> L5 <sup>0</sup>                                                | 32A <sup>4</sup>                    | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D54  | X <sub>2</sub> L5 <sup>0</sup> <sub>out</sub>                                 | 32A <sup>5</sup>                    | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D55  | X <sub>2</sub> L5 <sup>1</sup>                                                | 32A <sup>6</sup>                    | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D56  | X <sub>2</sub> L5 <sup>2</sup> <sub>out</sub>                                 | 32A <sup>7</sup>                    | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D57  | X <sub>2</sub> L5 <sup>3</sup> <sub>out</sub>                                 | 32A <sup>8</sup>                    | I/O  | IO, PD     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X2D58  | X <sub>2</sub> L5 <sup>4</sup> <sub>out</sub>                                 | 32A <sup>9</sup>                    | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D61  | X <sub>2</sub> L6 <sup>4</sup> <sub>in</sub>                                  | 32A <sup>10</sup>                   | I/O  | IO, PD     |

| X2D64 $X_2L6_{in}^{in}$ $32A^{13}$ I/O         IO, PD           X2D65 $X_2L6_{0ut}^{in}$ $32A^{14}$ I/O         IO, PD           X2D66 $X_2L6_{0ut}^{in}$ $32A^{15}$ I/O         IO, PD           X2D67 $X_2L6_{0ut}^{in}$ $32A^{15}$ I/O         IO, PD           X2D68 $X_2L6_{0ut}^{in}$ $32A^{17}$ I/O         IO, PD           X2D69 $X_2L6_{0ut}^{in}$ $32A^{18}$ I/O         IO, PD           X2D69 $X_2L6_{0ut}^{in}$ $32A^{18}$ I/O         IO, PD           X3D00 $X_2L7_{in}^{in}$ 1A <sup>0</sup> I/O         IO, PD           X3D01 $X_2L7_{in}^{in}$ 1B <sup>0</sup> I/O         IO, PD           X3D02 $X_2L4_{0ut}^{in}$ 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>21</sup> I/O         IO, PD           X3D03 $X_2L4_{0ut}^{in}$ 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>22</sup> I/O         IO, PD           X3D04 $X_2L4_{0ut}^{in}$ 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>22</sup> I/O         IO, PD           X3D05 <td< td=""><td>X2D62</td><td>X<sub>2</sub>L6<sup>3</sup><sub>in</sub></td><td>32A<sup>11</sup></td><td>I/O</td><td>IO, PD</td></td<> | X2D62  | X <sub>2</sub> L6 <sup>3</sup> <sub>in</sub>                                  | 32A <sup>11</sup>                   | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D63  | X <sub>2</sub> L6 <sup>2</sup> <sub>in</sub>                                  | 32A <sup>12</sup>                   | I/O  | IO, PD     |

| X2D66 $X_2L6_{out}^0$ $32A^{15}$ I/OIO, PDX2D67 $X_2L6_{out}^1$ $32A^{16}$ I/OIO, PDX2D68 $X_2L6_{out}^2$ $32A^{17}$ I/OIO, PDX2D69 $X_2L6_{out}^2$ $32A^{18}$ I/OIO, PDX2D70 $X_2L6_{out}^4$ $32A^{19}$ I/OIO, PDX3D00 $X_2L7_{in}^2$ $1A^0$ $32A^{19}$ I/OIO, PDX3D01 $X_2L7_{in}^2$ $1A^0$ I/OIO, PDX3D02 $X_2L4_{out}^0$ $4A^0$ $8A^0$ $16A^0$ $32A^{20}$ I/OX3D03 $X_2L4_{out}^2$ $4A^1$ $8A^1$ $16A^1$ $32A^{21}$ I/OIO, PDX3D04 $X_2L4_{out}^1$ $4B^0$ $8A^2$ $16A^2$ $32A^{22}$ I/OIO, PDX3D05 $X_2L4_{out}^2$ $4B^1$ $8A^3$ $16A^3$ $32A^{22}$ I/OIO, PDX3D06 $X_2L4_{out}^3$ $4B^2$ $8A^4$ $16A^4$ $32A^{21}$ I/OIO, PDX3D07 $X_2L4_{out}^3$ $4B^2$ $8A^4$ $16A^4$ $32A^{22}$ I/OIO, PDX3D08 $X_2L7_{out}^3$ $4B^2$ $8A^4$ $16A^4$ $32A^{24}$ I/OIO, PDX3D09 $X_2L7_{in}^3$ $4A^3$ $8A^7$ $16A^7$ $32A^{27}$ I/OIO, PDX3D11 $1D^0$ $U^{0}$ IO, PDI/OIO, PDI/OIO, PDX3D12 $1E^0$ $I/O$ IO, PDI/OIO, PDX3D13 $1F^0$ $U^{1}$ $8B^7$                                                                                                                                                                                            | X2D64  | X <sub>2</sub> L6 <sup>1</sup> <sub>in</sub>                                  | 32A <sup>13</sup>                   | I/O  | IO, PD     |

| X2D67 $X_2L6_{out}^1$ $32A^{16}$ I/OIO, PDX2D68 $X_2L6_{out}^2$ $32A^{17}$ I/OIO, PDX2D69 $X_2L6_{out}^3$ $32A^{18}$ I/OIO, PDX2D70 $X_2L6_{out}^3$ $32A^{19}$ I/OIO, PDX3D00 $X_2L7_{in}^2$ $1A^0$ $32A^{19}$ I/OIO, PDX3D01 $X_2L7_{in}^1$ $1B^0$ I/OIO, PDX3D02 $X_2L4_{out}^0$ $4A^0$ $8A^0$ $16A^0$ $32A^{20}$ I/OIO, PDX3D03 $X_2L4_{out}^2$ $4A^1$ $8A^1$ $16A^1$ $32A^{21}$ I/OIO, PDX3D04 $X_2L4_{out}^1$ $4B^0$ $8A^2$ $16A^2$ $32A^{22}$ I/OIO, PDX3D05 $X_2L4_{out}^2$ $4B^1$ $8A^3$ $16A^3$ $32A^{22}$ I/OIO, PDX3D06 $X_2L4_{out}^3$ $4B^2$ $8A^4$ $16A^4$ $32A^{22}$ I/OIO, PDX3D07 $X_2L4_{out}^4$ $4B^3$ $8A^5$ $16A^5$ $32A^{22}$ I/OIO, PDX3D08 $X_2L7_{in}^4$ $4A^2$ $8A^6$ $16A^6$ $32A^{22}$ I/OIO, PDX3D10 $1C^0$ $1C^0$ $1/O$ IO, PDX3D19 $1/O$ IO, PDX3D11 $1D^0$ $1C^0$ $1/O$ IO, PDX3D12 $1F^0$ $1/O$ IO, PDX3D13 $1F^0$ $1C^0$ $8B^0$ $16A^8$ $32A^{28}$ $1/O$ IO, PDX3D14 $4C^0$ $8B^0$ $16A^8$ $32A^{29}$ $1/O$                                                                                                                                                                                         | X2D65  | X <sub>2</sub> L6 <sup>0</sup> <sub>in</sub>                                  | 32A <sup>14</sup>                   | I/O  | IO, PD     |

| X2D68 $X_2L6^3_{out}$ $32A^{17}$ I/OIO, PDX2D69 $X_2L6^4_{out}$ $32A^{18}$ I/OIO, PDX2D70 $X_2L6^4_{out}$ $32A^{19}$ I/OIO, PDX3D00 $X_2L7^2_{in}$ $1A^0$ $32A^{19}$ I/OIO, PDX3D01 $X_2L7^2_{in}$ $1A^0$ I/OIO, PDX3D02 $X_2L4^0_{iut}$ $4A^0$ $8A^0$ $16A^0$ $32A^{20}$ I/OIO, PDX3D03 $X_2L4^0_{out}$ $4A^1$ $8A^1$ $16A^1$ $32A^{21}$ I/OIO, PDX3D04 $X_2L4^0_{out}$ $4A^1$ $8A^1$ $16A^2$ $32A^{22}$ I/OIO, PDX3D05 $X_2L4^3_{out}$ $4B^1$ $8A^3$ $16A^3$ $32A^{22}$ I/OIO, PDX3D06 $X_2L4^3_{out}$ $4B^2$ $8A^4$ $16A^4$ $32A^{22}$ I/OIO, PDX3D07 $X_2L4^4_{out}$ $4B^2$ $8A^4$ $16A^4$ $32A^{22}$ I/OIO, PDX3D08 $X_2L7^3_{in}$ $4A^3$ $8A^7$ $16A^7$ $32A^{27}$ I/OIO, PDX3D10 $1C^0$ I/OIO, PDI/OIO, PDX3D11ID0I/OIO, PDX3D11 $1D^0$ I/OIO, PDX3D13 $1F^0$ I/OIO, PDX3D13 $1F^0$ I/OIO, PDX3D14 $4C^0$ $8B^0$ $16A^8$ $32A^{29}$ I/OIO, PDX3D14 $4C^2$ $8B^6$ $16A^{14}$ $32A^{31}$ I/OIO, PDX3D20X3D20                                                                                                                                                                                                                     | X2D66  | X <sub>2</sub> L6 <sup>0</sup> <sub>out</sub>                                 | 32A <sup>15</sup>                   | I/O  | IO, PD     |

| X2D68 $X_2L6^2_{out}$ $32A^{17}$ I/OIO, PDX2D69 $X_2L6^4_{out}$ $32A^{18}$ I/OIO, PDX2D70 $X_2L6^4_{out}$ $32A^{19}$ I/OIO, PDX3D00 $X_2L7^2_{in}$ $1A^0$ I/OIO, PDX3D01 $X_2L7^2_{in}$ $1A^0$ I/OIO, PDX3D02 $X_2L4^0_{in}$ $4A^0$ $8A^0$ $16A^0$ $32A^{20}$ I/OIO, PDX3D03 $X_2L4^0_{out}$ $4A^1$ $8A^1$ $16A^1$ $32A^{21}$ I/OIO, PDX3D04 $X_2L4^0_{out}$ $4A^1$ $8A^1$ $16A^2$ $32A^{22}$ I/OIO, PDX3D05 $X_2L4^0_{out}$ $4B^1$ $8A^3$ $16A^3$ $32A^{22}$ I/OIO, PDX3D06 $X_2L4^0_{out}$ $4B^2$ $8A^4$ $16A^4$ $32A^{22}$ I/OIO, PDX3D07 $X_2L4^4_{out}$ $4B^3$ $8A^5$ $16A^5$ $32A^{22}$ I/OIO, PDX3D08 $X_2L4^2_{out}$ $4B^3$ $8A^5$ $16A^5$ $32A^{22}$ I/OIO, PDX3D09 $X_2L4^4_{out}$ $4B^3$ $8A^5$ $16A^5$ $32A^{22}$ I/OIO, PDX3D10 $1C^0$ $V$ $V$ IO, PD $V$ $V$ $V$ $V$ X3D11 $1D^0$ $V$ $V$ $V$ $V$ $V$ $V$ $V$ X3D13 $1F^0$ $V$ $V$ $V$ $V$ $V$ $V$ $V$ X3D14 $4C^0$ $8B^0$ $16A^8$ $32A^{29}$ $I/O$                                                                                                                                                                                                                     | X2D67  |                                                                               | 32A <sup>16</sup>                   | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D68  | X <sub>2</sub> L6 <sup>2</sup> <sub>out</sub>                                 | 32A <sup>17</sup>                   | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D69  | X <sub>2</sub> L6 <sup>3</sup> <sub>out</sub>                                 | 32A <sup>18</sup>                   | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X2D70  | X <sub>2</sub> L6 <sup>4</sup> <sub>out</sub>                                 | 32A <sup>19</sup>                   | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D00  | X <sub>2</sub> L7 <sup>2</sup> <sub>in</sub> 1A <sup>0</sup>                  |                                     | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D01  | X <sub>2</sub> L7 <sup>1</sup> <sub>in</sub> 1B <sup>0</sup>                  |                                     | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D02  |                                                                               | 16A <sup>0</sup> 32A <sup>20</sup>  | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D03  |                                                                               | 16A <sup>1</sup> 32A <sup>21</sup>  | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D04  |                                                                               | 16A <sup>2</sup> 32A <sup>22</sup>  | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D05  | X <sub>2</sub> L4 <sup>2</sup> <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> | 16A <sup>3</sup> 32A <sup>23</sup>  | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D06  | X <sub>2</sub> L4 <sup>3</sup> <sub>out</sub> 4B <sup>2</sup> 8A <sup>4</sup> | 16A <sup>4</sup> 32A <sup>24</sup>  | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D07  | X <sub>2</sub> L4 <sup>4</sup> <sub>out</sub> 4B <sup>3</sup> 8A <sup>5</sup> | 16A <sup>5</sup> 32A <sup>25</sup>  | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D08  |                                                                               | 16A <sup>6</sup> 32A <sup>26</sup>  | I/O  | IO, PD     |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D09  |                                                                               | 16A <sup>7</sup> 32A <sup>27</sup>  | I/O  | IO, PD     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X3D10  | 1C <sup>0</sup>                                                               |                                     | I/O  | IOT, PD    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X3D11  | 1D <sup>0</sup>                                                               |                                     | I/O  | IOT, PD    |

| X3D14         4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup> I/O         IO, PD           X3D15         4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup> I/O         IO, PD           X3D20         4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> I/O         IO, PD           X3D21         4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> I/O         IO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X3D12  | 1 E <sup>0</sup>                                                              |                                     | I/O  | IO, PD     |

| X3D15         4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup> I/O         IO, PD           X3D20         4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> I/O         IO, PD           X3D21         4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> I/O         IO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X3D13  | 1F <sup>0</sup>                                                               |                                     | I/O  | IO, PD     |

| X3D20         4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> I/O         IO, PD           X3D21         4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> I/O         IO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X3D14  | 4C <sup>0</sup> 8B <sup>0</sup>                                               | 16A <sup>8</sup> 32A <sup>28</sup>  | I/O  | IO, PD     |

| X3D21 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> I/O IO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | X3D15  |                                                                               |                                     | I/O  | IO, PD     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X3D20  | 4C <sup>2</sup> 8B <sup>6</sup>                                               | 16A <sup>14</sup> 32A <sup>30</sup> | I/O  | IO, PD     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X3D21  | 4C <sup>3</sup> 8B <sup>7</sup>                                               | 16A <sup>15</sup> 32A <sup>31</sup> | I/O  | IO, PD     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X3D23  | 1H <sup>0</sup>                                                               |                                     | I/O  | IO, PD     |

| X3D24 11 <sup>0</sup> 1/O 10, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X3D24  | 110                                                                           |                                     | I/O  | IO, PD     |

| X3D25 1J <sup>0</sup> I/O IO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X3D25  | ۱J <sup>0</sup>                                                               |                                     | I/O  | IO, PD     |

| X3D26 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D26  | 4E <sup>0</sup> 8C <sup>0</sup>                                               | 16B <sup>0</sup>                    | I/O  |            |

| X3D27 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D27  | 4E <sup>1</sup> 8C <sup>1</sup>                                               | 16B <sup>1</sup>                    | I/O  | IOT, PD    |

| X3D28 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D28  | 4F <sup>0</sup> 8C <sup>2</sup>                                               | 16B <sup>2</sup>                    | I/O  | IOT, PD    |

| X3D29 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D29  | 4F <sup>1</sup> 8C <sup>3</sup>                                               | 16B <sup>3</sup>                    | I/O  | IOT, PD    |

| X3D30 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D30  | 4F <sup>2</sup> 8C <sup>4</sup>                                               | 16B <sup>4</sup>                    | I/O  | IOT, PD    |

| X3D31 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup> I/O IOT, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X3D31  | 4F <sup>3</sup> 8C <sup>5</sup>                                               |                                     | I/O  | IOT, PD    |

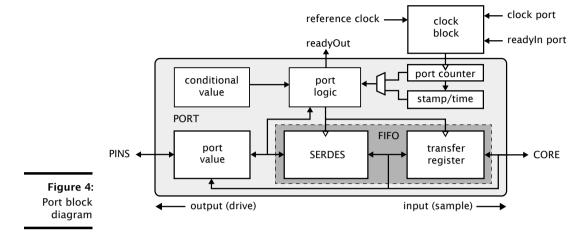

ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle. xCORE-200 IO pins can be used as *open collector* outputs, where signals are driven low if a zero is output, but left high impedance if a one is output. This option is set on a per-port basis.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

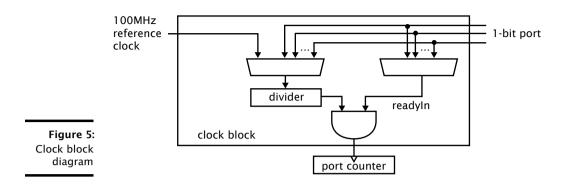

## 6.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces. xCORE-200 clock blocks optionally divide the clock input from a 1-bit port.

In many cases I/O signals are accompanied by strobing signals. The xCORE ports can input and interpret strobe (known as readyIn and readyOut) signals generated by external sources, and ports can generate strobe signals to accompany output data.

On reset, each port is connected to clock block 0, which runs from the xCORE Tile reference clock.

## 6.5 Channels and Channel Ends

Logical cores communicate using point-to-point connections, formed between two channel ends. A channel-end is a resource on an xCORE tile, that is allocated by the program. Each channel-end has a unique system-wide identifier that comprises a unique number and their tile identifier. Data is transmitted to a channel-end by an output-instruction; and the other side executes an input-instruction. Data can be passed synchronously or asynchronously between the channel ends.

## 6.6 xCONNECT Switch and Links

XMOS devices provide a scalable architecture, where multiple xCORE devices can be connected together to form one system. Each xCORE device has an xCONNECT interconnect that provides a communication infrastructure for all tasks that run on the various xCORE tiles on the system.

The interconnect relies on a collection of switches and XMOS links. Each xCORE device has an on-chip switch that can set up circuits or route data. The switches are connected by xConnect Links. An XMOS link provides a physical connection between two switches. The switch has a routing algorithm that supports many different topologies, including lines, meshes, trees, and hypercubes.

The links operate in either 2 wires per direction or 5 wires per direction mode, depending on the amount of bandwidth required. Circuit switched, streaming

The pins used for QSPI boot are hardcoded in the boot ROM and cannot be changed. If required, an QSPI boot program can be burned into OTP that uses different pins.

#### 8.2 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 11, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

Figure 11: SPI master pins

PinSignalDescriptionX0D00MISOMaster In Slave Out (Data)X0D01SSSlave SelectX0D10SCLKClockX0D11MOSIMaster Out Slave In (Data)

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant bit first may have to reverse the bits in each byte of the image stored in the SPI device.

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.3 Boot from SPI slave

If set to boot from SPI slave, the processor enables the three pins specified in Figure 12 and expects a boot image to be clocked in. The supported clock polarity and phase are 0/0 and 1/1.

Figure 12 SPI slave pins

|    | Pin   | Signal | Description                |

|----|-------|--------|----------------------------|

| -  | X0D00 | SS     | Slave Select               |

| 2: | X0D10 | SCLK   | Clock                      |

| ns | X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.4 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables its link(s) around 2 us after the boot process starts. Enabling the Link switches off the pull-down

resistors on the link, drives all the TX wires low (the initial state for the Link), and monitors the RX pins for boot-traffic; they must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 8.5 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 8), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 8.6 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 13 provide a strong level of protection and are sufficient for providing strong IP security.

## 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds

## 13.3 ESD Stress Voltage

Figure 23 ESD stress voltage

| 23: | Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|-----|--------|----------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model     | -2.00 |     | 2.00 | KV    |       |

| ige | CDM    | Charged Device Model | -500  |     | 500  | V     |       |

## 13.4 Reset Timing

| 5            | Symbol      | Parameters                                | MIN      | TYP  | MAX | UNITS | Notes |

|--------------|-------------|-------------------------------------------|----------|------|-----|-------|-------|

| Figure 24:   | T(RST)      | Reset pulse width                         | 5        |      |     | μs    |       |

| Reset timing | T(INIT)     | Initialization time                       |          |      | 150 | μs    | А     |

|              | A Shows the | time taken to start booting after PST N k | and anno | high |     |       |       |

A Shows the time taken to start booting after RST\_N has gone high.

#### 13.5 Power Consumption

| Symbol     | Parameter              | MIN | ТҮР  | MAX  | UNITS   | Notes      |

|------------|------------------------|-----|------|------|---------|------------|

| I(DDCQ)    | Quiescent VDD current  |     | 90   |      | mA      | A, B, C    |

| PD         | Tile power dissipation |     | 325  |      | µW/MIPS | A, D, E, F |

| IDD        | Active VDD current     |     | 1140 | 1400 | mA      | A, G       |

| I(ADDPLL)  | PLL_AVDD current       |     | 5    | 7    | mA      | Н          |

| I(VDD33)   | VDD33 current          |     | 53.4 |      | mA      | I          |

| I(USB_VDD) | USB_VDD current        |     | 16.6 |      | mA      | J          |

Figure 25: xCORE Tile currents

A Use for budgetary purposes only.

- B Assumes typical tile and I/O voltages with no switching activity.

- C Includes PLL current.

- D Assumes typical tile and I/O voltages with nominal switching activity.

- E Assumes 1 MHz = 1 MIPS.

- F PD(TYP) value is the usage power consumption under typical operating conditions.

- G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

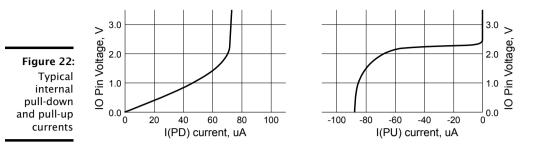

- H PLL\_AVDD = 1.0 V