Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | XCore                                                          |

| Core Size                  | 32-Bit 24-Core                                                 |

| Speed                      | 4000MIPS                                                       |

| Connectivity               | USB                                                            |

| Peripherals                | -                                                              |

| Number of I/O              | 176                                                            |

| Program Memory Size        | ·                                                              |

| Program Memory Type        | ROMIess                                                        |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1M x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | External                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 374-LFBGA                                                      |

| Supplier Device Package    | 374-FBGA (18x18)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu224-1024-fb374-i40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal  | Function                                      |                  |                 |                 |                   |                   | Туре | Properties |

|---------|-----------------------------------------------|------------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X1D67   | X <sub>0</sub> L2 <sup>1</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>16</sup> | I/O  | IO, PD     |

| X1D68   | $X_0L2_{out}^2$                               |                  |                 |                 |                   | 32A <sup>17</sup> | I/0  | IO, PD     |

| X1D69   | X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>18</sup> | I/0  | IO, PD     |

| X1D70   | X <sub>0</sub> L2 <sup>4</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>19</sup> | I/O  | IO, PD     |

| X2D00   |                                               | 1A <sup>0</sup>  |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D02   |                                               |                  | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/0  | IO, PD     |

| X2D03   |                                               |                  | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/0  | IO, PD     |

| X2D04   |                                               |                  | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/0  | IO, PD     |

| X2D05   |                                               |                  | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O  | IO, PD     |

| X2D06   |                                               |                  | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O  | IO, PD     |

| X2D07   |                                               |                  | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O  | IO, PD     |

| X2D08   |                                               |                  | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IO, PD     |

| X2D09   |                                               |                  | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O  | IO, PD     |

| X2D11   |                                               | 1D <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D12   |                                               | 1 E <sup>0</sup> |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D13   |                                               | 1F <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D14   |                                               |                  | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | 1/0  | IO, PD     |

| X2D15   |                                               |                  | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O  | IO, PD     |

| X2D16   | X <sub>2</sub> L4 <sup>4</sup> <sub>in</sub>  |                  | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> | -                 | 1/0  | IO, PD     |

| X2D17   | X <sub>2</sub> L4 <sup>3</sup> <sub>in</sub>  |                  | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | 1/0  | IO, PD     |

| X2D18   | X <sub>2</sub> L4 <sup>2</sup> <sub>in</sub>  |                  | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | 1/0  | IO, PD     |

| X2D19   | X <sub>2</sub> L4 <sup>1</sup> <sub>in</sub>  |                  | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | 1/0  | IO, PD     |

| X2D20   |                                               |                  | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | 1/0  | IO, PD     |

| X2D21   |                                               |                  | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | 1/0  | IO, PD     |

| X2D22   |                                               | 1G <sup>0</sup>  | -               | -               | -                 | -                 | 1/0  | IO, PD     |

| X2D23   |                                               | 1H <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D24   | X <sub>2</sub> L7 <sup>0</sup>                | 110              |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D25   | X <sub>2</sub> L7 <sup>0</sup> <sub>out</sub> | 1J <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D26   | X <sub>2</sub> L7 <sup>3</sup> <sub>out</sub> | .,               | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | 1/0  | IO, PD     |

| X2D27   | X <sub>2</sub> L7 <sup>4</sup> <sub>out</sub> |                  | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | 1/0  | IO, PD     |

| X2D28   | ···2 -·· out                                  |                  | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | 1/0  | IO, PD     |

| X2D29   |                                               |                  | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | 1/0  | IO, PD     |

| X2D30   |                                               |                  | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | 1/0  | IO, PD     |

| X2D31   |                                               |                  | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | 1/0  | IO, PD     |

| X2D32   |                                               |                  | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O  | IO, PD     |

| X2D33   |                                               |                  | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | 1/0  | IO, PD     |

| X2D34   | X <sub>2</sub> L7 <sup>1</sup>                | 1K <sup>0</sup>  |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D35   | X <sub>2</sub> L7 <sup>2</sup> <sub>out</sub> | 1L0              |                 |                 |                   |                   | 1/0  | IO, PD     |

| X2D36   | ··2 001                                       | 1M <sup>0</sup>  |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | 1/0  | IO, PD     |

| X2D49   | X <sub>2</sub> L5 <sup>4</sup>                |                  |                 |                 |                   | 32A <sup>0</sup>  | 1/0  | IO, PD     |

| X2D50   | X <sub>2</sub> L5 <sup>3</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>1</sup>  | 1/0  | IO, PD     |

| X2D51   | $X_2L5_{in}^2$<br>$X_2L5_{in}^2$              |                  |                 |                 |                   | 32A <sup>2</sup>  | 1/0  | IO, PD     |

| X2D52   | $X_2L5_{in}^1$<br>$X_2L5_{in}^1$              |                  |                 |                 |                   | 32A <sup>3</sup>  | 1/0  | IO, PD     |

| NED J E | 1/2 - Jin                                     |                  |                 |                 |                   | J2A               | 1/0  |            |

-XMOS<sup>®</sup>-

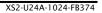

# 5 Example Application Diagram

- Figure 2: Simplified Reference Schematic

- see Section 10 for details on the USB PHY

- see Section 12 for details on the power supplies and PCB design

-XMOS

# 6 Product Overview

The XU224-1024-FB374 is a powerful device that consists of four xCORE Tiles, each comprising a flexible logical processing cores with tightly integrated I/O and on-chip memory.

### 6.1 Logical cores

Each tile has 6 active logical cores, which issue instructions down a shared fivestage pipeline. Instructions from the active cores are issued round-robin. If up to five logical cores are active, each core is allocated a fifth of the processing cycles. If more than five logical cores are active, each core is allocated at least 1/n cycles (for *n* cores). Figure 3 shows the guaranteed core performance depending on the number of cores used.

Figure 3: Logical core performance

| ure 3: | Speed | MIPS      | Frequency | Mi  | inimum | n MIPS | per cor | e (for <i>i</i> | 1 core | s) |  |

|--------|-------|-----------|-----------|-----|--------|--------|---------|-----------------|--------|----|--|

| l core | grade |           |           | 1   | 2      | 3      | 4       | 5               | 6      |    |  |

| nance  | 20    | 2000 MIPS | 500 MHz   | 100 | 100    | 100    | 100     | 100             | 83     |    |  |

There is no way that the performance of a logical core can be reduced below these predicted levels (unless *priority threads* are used: in this case the guaranteed minimum performance is computed based on the number of priority threads as defined in the architecture manual). Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than five logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

# 6.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

#### 6.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XU224-1024-FB374, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit

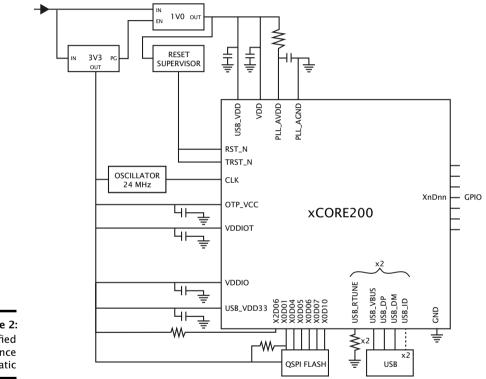

Figure 6: Switch, links and channel ends

and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between xCORE Tiles (up to 250 MBit/s), but each stream requires a single link to be reserved between switches on two tiles. All packet communications can be multiplexed onto a single link.

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-U Link Performance and Design Guide, X2999.

# 7 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock. The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 7:

Figure 7: PLL multiplier values and MODE pins

|      | Oscillator  | MC | DDE | Tile        | PLL Ratio | PLL settings |     | gs |  |

|------|-------------|----|-----|-------------|-----------|--------------|-----|----|--|

|      | Frequency   | 1  | 0   | Frequency   |           | OD           | F   | R  |  |

| e 7: | 3.25-10 MHz | 0  | 0   | 130-400 MHz | 40        | 1            | 159 | 0  |  |

| lier | 9-25 MHz    | 1  | 1   | 144-400 MHz | 16        | 1            | 63  | 0  |  |

| ind  | 25-50 MHz   | 1  | 0   | 167-400 MHz | 8         | 1            | 31  | 0  |  |

| ins  | 50-100 MHz  | 0  | 1   | 196-400 MHz | 4         | 1            | 15  | 0  |  |

-XMOS

#### 8.1 Boot from QSPI master

If set to boot from QSPI master, the processor enables the six pins specified in Figure 10, and drives the SPI clock at 50 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

|            | Pin        | Signal | Description  |

|------------|------------|--------|--------------|

|            | X0D01      | SS     | Slave Select |

| Figure 10: | X0D04X0D07 | SPIO   | Data         |

| QSPI pins  | X0D10      | SCLK   | Clock        |

-XMOS<sup>®</sup>

The xCORE Tile expects each byte to be transferred with the *least-significant nibble first*. Programmers who write bytes into an QSPI interface using the most significant nibble first may have to reverse the nibbles in each byte of the image stored in the QSPI device.

resistors on the link, drives all the TX wires low (the initial state for the Link), and monitors the RX pins for boot-traffic; they must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

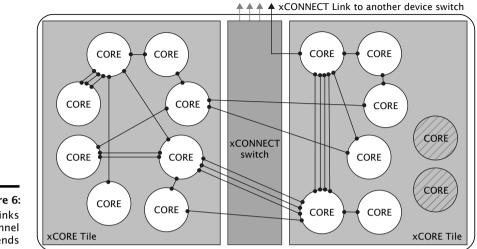

#### 8.5 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 8), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 8.6 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 13 provide a strong level of protection and are sufficient for providing strong IP security.

# 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds

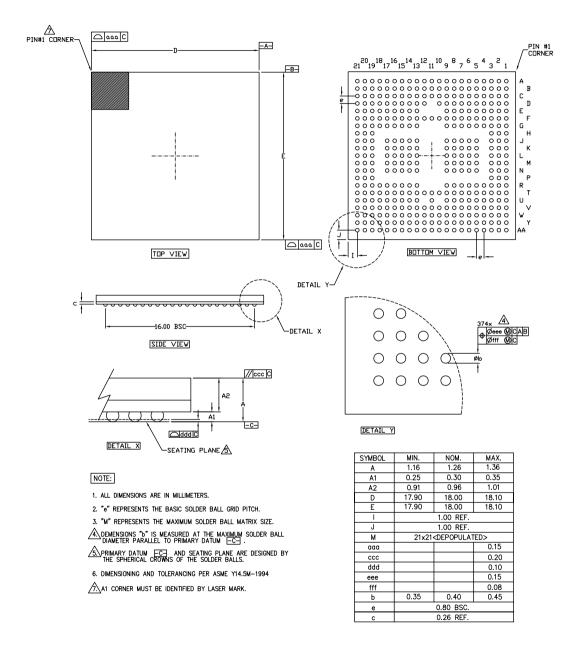

# 14 Package Information

-XMOS

XS2-U24A-1024-FB374

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RW   | RAM base address                      |

| 0x01      | RW   | Vector base address                   |

| 0x02      | RW   | xCORE Tile control                    |

| 0x03      | RO   | xCORE Tile boot status                |

| 0x05      | RW   | Security configuration                |

| 0x06      | RW   | Ring Oscillator Control               |

| 0x07      | RO   | Ring Oscillator Value                 |

| 0x08      | RO   | Ring Oscillator Value                 |

| 0x09      | RO   | Ring Oscillator Value                 |

| 0x0A      | RO   | Ring Oscillator Value                 |

| 0x0C      | RO   | RAM size                              |

| 0x10      | DRW  | Debug SSR                             |

| 0x11      | DRW  | Debug SPC                             |

| 0x12      | DRW  | Debug SSP                             |

| 0x13      | DRW  | DGETREG operand 1                     |

| 0x14      | DRW  | DGETREG operand 2                     |

| 0x15      | DRW  | Debug interrupt type                  |

| 0x16      | DRW  | Debug interrupt data                  |

| 0x18      | DRW  | Debug core control                    |

| 0x20 0x27 | DRW  | Debug scratch                         |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |

| 0x70 0x73 | DRW  | Data breakpoint control register      |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |

| 0x90 0x93 | DRW  | Resources breakpoint value            |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |

Figure 33:

Summary

X009642,

#### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00040000.

**0x00:** RAM base address

| )0: | Bits | Perm | Init | Description                                |

|-----|------|------|------|--------------------------------------------|

| se  | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| SS  | 1:0  | RO   | -    | Reserved                                   |

### B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

| - | Bits  | Perm | Init | Description                      |

|---|-------|------|------|----------------------------------|

| 2 | 31:18 | RW   |      | The event and interrupt vectors. |

| 5 | 17:0  | RO   | -    | Reserved                         |

### B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

| Bits  | Perm | Init | Description                                                                                                                                                                                                                           |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                            |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1 |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                   |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock divider is enabled. In dynamic mode the clock divider is only activated when all active threads are paused. In static mode the clock divider is always enabled.      |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                |

| 3     | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 2     | RW   |      | Select between UTMI (1) and ULPI (0) mode.                                                                                                                                                                                            |

| 1     | RW   |      | Enable the ULPI Hardware support module                                                                                                                                                                                               |

| 0     | RO   | -    | Reserved                                                                                                                                                                                                                              |

0x02: xCORE Tile control

# B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS"-

|         | Bits  | Perm | Init | Description                                               |

|---------|-------|------|------|-----------------------------------------------------------|

|         | 31:24 | RO   | -    | Reserved                                                  |

|         | 23:16 | RO   |      | Processor number.                                         |

|         | 15:9  | RO   | -    | Reserved                                                  |

|         | 8     | RO   |      | Overwrite BOOT_MODE.                                      |

|         | 7:6   | RO   | -    | Reserved                                                  |

|         | 5     | RO   |      | Indicates if core1 has been powered off                   |

|         | 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| -       | 3     | RO   |      | Boot ROM boots from RAM                                   |

| ).<br>2 | 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 5       | 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03: xCORE Tile boot status

| 0   | x0C: |

|-----|------|

| RAM | size |

|        | Bits | Perm | Init | Description                                |

|--------|------|------|------|--------------------------------------------|

| 0x0C:  | 31:2 | RO   |      | Most significant 16 bits of all addresses. |

| A size | 1:0  | RO   | -    | Reserved                                   |

#### B.12 Debug SSR: 0x10

This register contains the value of the SSR register when the debugger was called.

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:11 | RO   | -    | Reserved                                                                           |

| 10    | DRW  |      | Address space indentifier                                                          |

| 9     | DRW  |      | Determines the issue mode (DI bit) upon Kernel Entry after Exception or Interrupt. |

| 8     | RO   |      | Determines the issue mode (DI bit).                                                |

| 7     | DRW  |      | When 1 the thread is in fast mode and will continually issue.                      |

| 6     | DRW  |      | When 1 the thread is paused waiting for events, a lock or another resource.        |

| 5     | RO   | -    | Reserved                                                                           |

| 4     | DRW  |      | 1 when in kernel mode.                                                             |

| 3     | DRW  |      | 1 when in an interrupt handler.                                                    |

| 2     | DRW  |      | 1 when in an event enabling sequence.                                              |

| 1     | DRW  |      | When 1 interrupts are enabled for the thread.                                      |

| 0     | DRW  |      | When 1 events are enabled for the thread.                                          |

**0x10:** Debug SSR

# B.13 Debug SPC: 0x11

This register contains the value of the SPC register when the debugger was called.

| 0x11:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SPC | 31:0 | DRW  |      | Value.      |

-XMOS<sup>®</sup>-

#### B.14 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

#### B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

**0x16:** Debug interrupt data

| 1 <b>6:</b><br>ug | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| ata               | 31:0 | DRW  |      | Value.      |

# B.19 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

0x18: Debug core control

|            | Bits | Perm | Init | Description                                                                                                                                       |

|------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 31:8 | RO   | -    | Reserved                                                                                                                                          |

| :<br>:<br> | 7:0  | DRW  |      | 1-hot vector defining which threads are stopped when not in<br>debug mode. Every bit which is set prevents the respective<br>thread from running. |

#### B.20 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| x27:<br>bug | Bits | Perm | Init | Description |

|-------------|------|------|------|-------------|

| atch        | 31:0 | DRW  |      | Value.      |

# B.21 Instruction breakpoint address: 0x30 .. 0x33

-XM()S

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

|                         | Bits  | Perm | Init | Description                                                                                              |

|-------------------------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|                         | 31:24 | RO   | -    | Reserved                                                                                                 |

|                         | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 0x9C 0x9F:<br>Resources | 15:2  | RO   | -    | Reserved                                                                                                 |

| breakpoint<br>control   | 1     | DRW  | 0    | When 0 break when condition A is met. When 1 = break when condition B is met.                            |

| register                | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

|                | Bits  | Perm | Init | Description                                        |

|----------------|-------|------|------|----------------------------------------------------|

|                | 31:24 | CRO  |      | Processor ID of this XCore.                        |

| 0x00:          | 23:16 | CRO  |      | Number of the node in which this XCore is located. |

| Device         | 15:8  | CRO  |      | XCore revision.                                    |

| identification | 7:0   | CRO  |      | XCore version.                                     |

#### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

xCORE Tile description 1

0x01:

#### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

|     | Bits  | Perm | Init | Description             |

|-----|-------|------|------|-------------------------|

| 02: | 31:16 | RO   | -    | Reserved                |

| īle | 15:8  | CRO  |      | Number of clock blocks. |

| n 2 | 7:0   | CRO  |      | Number of timers.       |

#### C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

# C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                 |

|------|------|------|---------------------------------------------|

| 31:2 | RO   | -    | Reserved                                    |

| 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

| 0    | CRW  | 0    | Request a debug interrupt on the processor. |

### C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |

| 30:16 | RO   | -    | Reserved                                                      |

| 15:0  | CRW  | 0    | Clock divider.                                                |

# C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

Bits

31:0

### C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

### C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| 9x47:<br>gical | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ore 7          | 31:0 | CRO  |      | Value.      |

# C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

# C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 61:<br>ical | Bits | Perm | Init | Description |

|-------------|------|------|------|-------------|

| e 1         | 31:0 | CRO  |      | Value.      |

·XMC

# C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

# E.3 Node identifier: 0x05

**0x05:** Node identifier

0x51: System clock frequency

| Bits  | Perm | Init | Description                                                                                            |

|-------|------|------|--------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                               |

| 15:0  | RW   | 0    | 16-bit node identifier. This does not need to be set, and present for compatibility with XS1-switches. |

# E.4 System clock frequency: 0x51

| Bits | Perm | Init | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:7 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6:0  | RW   | 25   | Oscillator clock frequency in MHz rounded up to the nearest<br>integer value. Only values between 5 and 100 MHz are valid -<br>writes outside this range are ignored and will be NACKed.<br>This field must be set on start up of the device and any time that<br>the input oscillator clock frequency is changed. It must contain<br>the system clock frequency in MHz rounded up to the nearest<br>integer value. |

E.5 Link Control and Status: 0x80

| Bits  | Perm | Init | Description                                                                                              |

|-------|------|------|----------------------------------------------------------------------------------------------------------|

| 31:28 | RO   | -    | Reserved                                                                                                 |

| 27    | RO   |      | Rx buffer overflow or illegal token encoding received.                                                   |

| 26    | RO   | 0    | This end of the xlink has issued credit to allow the remote end to transmit                              |

| 25    | RO   | 0    | This end of the xlink has credit to allow it to transmit.                                                |

| 24    | WO   |      | Clear this end of the xlink's credit and issue a HELLO token.                                            |

| 23    | WO   |      | Reset the receiver. The next symbol that is detected will be the first symbol in a token.                |

| 22    | RO   | -    | Reserved                                                                                                 |

| 21:11 | RW   | 1    | Specify min. number of idle system clocks between two contin-<br>uous symbols witin a transmit token -1. |

| 10:0  | RW   | 1    | Specify min. number of idle system clocks between two contin-<br>uous transmit tokens -1.                |

-XMOS

0x80: Link Control and Status

XS2-U24A-1024-FB374

is

|                     | Bits  | Perm | Init | Description                                                                                                                                          |

|---------------------|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 31:19 | RO   | -    | Reserved                                                                                                                                             |

|                     | 18    | RW   | 0    | Set to 1 to disable pulldowns on ports 8A and 8B.                                                                                                    |

|                     | 17:14 | RO   | -    | Reserved                                                                                                                                             |

|                     | 13    | RW   | 0    | After an auto-resume, this bit is set to indicate that the resume signalling was for reset (se0). Set to 0 to clear.                                 |

|                     | 12    | RW   | 0    | After an auto-resume, this bit is set to indicate that the resume signalling was for resume (K). Set to 0 to clear.                                  |

|                     | 11:8  | RW   | 0    | Log-2 number of clocks before any linestate change is propa-<br>gated.                                                                               |

|                     | 7     | RW   | 0    | Set to 1 to use the suspend controller handle to resume from suspend. Otherwise, the program has to poll the linestate_filt field in phy_teststatus. |

| <b>)x40:</b><br>PHY | 6:4   | RW   | 0    | Control the the conf1,2,3 input pins of the PHY.                                                                                                     |

| ntrol               | 3:0   | RO   | -    | Reserved                                                                                                                                             |

# F.17 UIFM PHY control: 0x40

**0x40** UIFM PHY control

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XU224-1024-FB374. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 12).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 12).

- The VDD (core) supply is capable of supplying 1400 mA (Section 12 and Figure 21).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 12

#### H.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 12).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 12).

#### H.3 Power on reset

The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### H.4 Clock

- The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 7. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

#### H.5 Boot

- □ The device is connected to a QSPI flash for booting, connected to X0D01, X0D04..X0D07, and X0D10 (Section 8). If not, you must boot the device through OTP or JTAG, or set it to boot from SPI and connect a SPI flash.

- ☐ The Flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### H.6 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- $\Box$  If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.7 GPIO

- □ You have not mapped both inputs and outputs to the same multi-bit port.

- Pins X0D04, X0D05, X0D06, and X0D07 are output only and are, during and after reset, pulled high and low appropriately (Section 8)

- Pins X2D04, X2D05, X2D06 and X2D07 are output only and during and after reset, X2D06 is pulled high and X2D04, X2D05, and X2D07 are pulled low (Section 8)

#### H.8 Multi device designs

Skip this section if your design only includes a single XMOS device.

- $\Box$  One device is connected to a QSPI or SPI flash for booting.

- Devices that boot from link have, for example, X0D06 pulled high and have link XL0 connected to a device to boot from (Section 8).