Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 24                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                      |

| Data Converters            | A/D 23x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f920-g-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                             | 4.00 |

|-----------------------------------------------------------------------------|------|

| 18.7.Flash Error Reset                                                      |      |

| 18.8.SmaRTClock (Real Time Clock) Reset                                     |      |

| 18.9.Software Reset                                                         |      |

| 19. Clocking Sources                                                        |      |

| 19.1.Programmable Precision Internal Oscillator                             | 192  |

| 19.2.Low Power Internal Oscillator                                          | 192  |

| 19.3.External Oscillator Drive Circuit                                      | 192  |

| 19.3.1.External Crystal Mode                                                | 192  |

| 19.3.2.External RC Mode                                                     |      |

| 19.3.3.External Capacitor Mode                                              |      |

| 19.3.4.External CMOS Clock Mode                                             |      |

| 19.4.Special Function Registers for Selecting and Configuring the System Cl |      |

| 20. SmaRTClock (Real Time Clock)                                            |      |

| 20.1.SmaRTClock Interface                                                   |      |

| 20.1.1.SmaRTClock Lock and Key Functions                                    |      |

| 20.1.2.Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal F            |      |

| -                                                                           | -    |

| 20.1.3.RTC0ADR Short Strobe Feature                                         | -    |

|                                                                             |      |

| 20.1.4.SmaRTClock Interface Autoread Feature                                |      |

| 20.1.5.RTC0ADR Autoincrement Feature                                        |      |

| 20.2.SmaRTClock Clocking Sources                                            | 206  |

| 20.2.1.Using the SmaRTClock Oscillator with a Crystal or                    |      |

| External CMOS Clock                                                         |      |

| 20.2.2.Using the SmaRTClock Oscillator in Self-Oscillate Mode               |      |

| 20.2.3.Programmable Load Capacitance                                        | 207  |

| 20.2.4.Automatic Gain Control (Crystal Mode Only) and SmaRTClock            |      |

| Bias Doubling                                                               | 208  |

| 20.2.5.Missing SmaRTClock Detector                                          | 210  |

| 20.2.6.SmaRTClock Oscillator Crystal Valid Detector                         | 210  |

| 20.3.SmaRTClock Timer and Alarm Function                                    |      |

| 20.3.1.Setting and Reading the SmaRTClock Timer Value                       |      |

| 20.3.2.Setting a SmaRTClock Alarm                                           |      |

| 20.3.3.Software Considerations for using the SmaRTClock Timer and Ala       |      |

| 21. Port Input/Output                                                       |      |

| 21.1.Port I/O Modes of Operation                                            | 217  |

| 21.1.1.Port Pins Configured for Analog I/O                                  |      |

| 21.1.2.Port Pins Configured For Digital I/O                                 |      |

|                                                                             |      |

| 21.1.3.Interfacing Port I/O to 5 V and 3.3 V Logic                          |      |

| 21.1.4. Increasing Port I/O Drive Strength                                  |      |

| 21.2.Assigning Port I/O Pins to Analog and Digital Functions                |      |

| 21.2.1.Assigning Port I/O Pins to Analog Functions                          |      |

| 21.2.2.Assigning Port I/O Pins to Digital Functions                         |      |

| 21.2.3.Assigning Port I/O Pins to External Digital Event Capture Function   |      |

| 21.3.Priority Crossbar Decoder                                              |      |

| 21.4.Port Match                                                             | 227  |

## 3. Pinout and Package Definitions

| Pin Numbers<br>Name |          | <b>T</b> | Description |                                                                                                                                                                                                                                                                                                     |  |

|---------------------|----------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                | 'F920/30 | 'F921/31 | Туре        | Description                                                                                                                                                                                                                                                                                         |  |

| VBAT                | 5        | 5        | P In        | Battery Supply Voltage. Must be 0.9 to 1.8 V in single-cell battery mode and 1.8 to 3.6 V in dual-cell battery mode.                                                                                                                                                                                |  |

| V <sub>DD</sub> /   | 3        | 3        | P In        | Power Supply Voltage. Must be 1.8 to 3.6 V. This supply voltage is not required in low power sleep mode. This voltage must always be $\geq$ VBAT.                                                                                                                                                   |  |

| DC+                 |          |          | P Out       | Positive output of the dc-dc converter. In single-cell battery mode, a 1 $\mu$ F ceramic capacitor is required between DC+ and DC–. This pin can supply power to external devices when operating in single-cell battery mode.                                                                       |  |

| DC-/                | 1        | 1        | P In        | DC-DC converter return current path. In single-cell battery mode, this pin is typically not connected to ground.                                                                                                                                                                                    |  |

| GND                 |          |          | G           | In dual-cell battery mode, this pin must be connected directly to ground.                                                                                                                                                                                                                           |  |

| GND                 | 2        | 2        | G           | Required Ground.                                                                                                                                                                                                                                                                                    |  |

| DCEN                | 4        | 4        | P In        | P In DC-DC Enable Pin. In single-cell battery mode, this pin must be connected to VBAT through a 0.68 µH inductor                                                                                                                                                                                   |  |

|                     |          |          | G           | In dual-cell battery mode, this pin must be connected directly to ground.                                                                                                                                                                                                                           |  |

| RST/                | 6        | 6        | D I/O       | Device Reset. Open-drain output of internal POR or $V_{DD}$<br>monitor. An external source can initiate a system reset by<br>driving this pin low for at least 15 µs. A 1 k $\Omega$ to 5 k $\Omega$ pullup<br>to $V_{DD}$ is recommended. See Reset Sources Section for a<br>complete description. |  |

| C2CK                |          |          | D I/O       | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                            |  |

| P2.7/               | 7        | 7        | D I/O       | Port 2.7. This pin can only be used as GPIO. The Crossbar<br>cannot route signals to this pin and it cannot be configured<br>as an analog input. See Port I/O Section for a complete<br>description.                                                                                                |  |

| C2D                 |          |          | D I/O       | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                                                                                                              |  |

| XTAL3               | 10       | 9        | A In        | SmaRTClock Oscillator Crystal Input.<br>See Section 20 for a complete description.                                                                                                                                                                                                                  |  |

| XTAL4               | 9        | 8        | A Out       | SmaRTClock Oscillator Crystal Output.<br>See Section 20 for a complete description.                                                                                                                                                                                                                 |  |

Table 3.1. Pin Definitions for the C8051F92x-C8051F93x

### 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to userprogrammed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | AD0GT[15:8] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Page = 0x0; SFR Address = 0xC4

| Bit | Name        | Function                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------|

| 7:0 | AD0GT[15:8] | ADC0 Greater-Than High Byte.<br>Most Significant Byte of the 16-bit Greater-Than window compare register. |

|     |             | most Significant Byte of the To-bit Greater-man window compare register.                                  |

## SFR Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | AD0GT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Page = 0x0; SFR Address = 0xC3

| Bit   | Name                                                    | Function                                                                                                  |  |  |  |  |  |

|-------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | AD0GT[7:0]                                              | ADC0 Greater-Than Low Byte.<br>Least Significant Byte of the 16-bit Greater-Than window compare register. |  |  |  |  |  |

| Note: | te: In 8-bit mode, this register should be set to 0x00. |                                                                                                           |  |  |  |  |  |

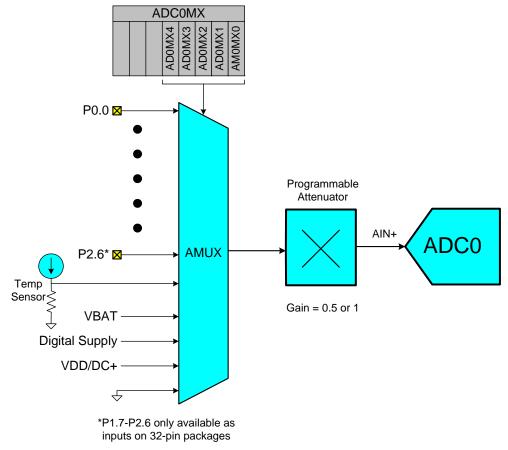

## 5.5. ADC0 Analog Multiplexer

ADC0 on C8051F93x-C8051F92x has an analog multiplexer, referred to as AMUX0.

AMUX0 selects the positive inputs to the single-ended ADC0. Any of the following may be selected as the positive input: Port I/O pins, the on-chip temperature sensor, the VBAT Power Supply, Regulated Digital Supply Voltage (Output of VREG0), VDD/DC+ Supply, or the positive input may be connected to GND. The ADC0 input channels are selected in the ADC0MX register described in SFR Definition 5.12.

Figure 5.7. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN and disable the digital driver (PnMDOUT = 0 and Port Latch = 1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "21. Port Input/Output" on page 216 for more Port I/O configuration details.

## 6. Programmable Current Reference (IREF0)

C8051F93x-C8051F92x devices include an on-chip programmable current reference (source or sink) with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in High Current Mode is 504  $\mu$ A (8  $\mu$ A steps).

The current source/sink is controlled though the IREF0CN special function register. It is enabled by setting the desired output current to a non-zero value. It is disabled by writing 0x00 to IREF0CN. The port I/O pin associated with ISRC0 should be configured as an analog input and skipped in the Crossbar. See Section "21. Port Input/Output" on page 216 for more details.

### SFR Definition 6.1. IREF0CN: Current Reference Control

| Bit   | 7    | 6    | 5   | 4 | 3    | 2    | 1 | 0 |

|-------|------|------|-----|---|------|------|---|---|

| Name  | SINK | MODE |     |   | IREF | 0DAT |   |   |

| Туре  | R/W  | R/W  | R/W |   |      |      |   |   |

| Reset | 0    | 0    | 0   | 0 | 0    | 0    | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xB9

| Bit | Name          | Function                                                                                                                                                                                           |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SINK          | IREF0 Current Sink Enable.                                                                                                                                                                         |

|     |               | Selects if IREF0 is a current source or a current sink.<br>0: IREF0 is a current source.<br>1: IREF0 is a current sink.                                                                            |

| 6   | MDSEL         | IREF0 Output Mode Select.                                                                                                                                                                          |

|     |               | Selects Low Power or High Current Mode.                                                                                                                                                            |

|     |               | 0: Low Power Mode is selected (step size = 1 $\mu$ A).                                                                                                                                             |

|     |               | 1: High Current Mode is selected (step size = $8 \mu A$ ).                                                                                                                                         |

| 5:0 | IREF0DAT[5:0] | IREF0 Data Word.                                                                                                                                                                                   |

|     |               | Specifies the number of steps required to achieve the desired output current.<br>Output current = direction x step size x IREF0DAT.<br>IREF0 is in a low power state when IREF0DAT is set to 0x00. |

#### 6.1. IREF0 Specifications

See Table 4.12 on page 63 for a detailed listing of IREF0 specifications.

### 8.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

#### SFR Definition 8.1. DPL: Data Pointer Low Byte

| Bit                                      | 7             | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|---------------|----------|---|---|---|---|---|---|

| Name                                     | •             | DPL[7:0] |   |   |   |   |   |   |

| Туре                                     |               | R/W      |   |   |   |   |   |   |

| Rese                                     | t 0           | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Page = All Pages; SFR Address = 0x82 |               |          |   |   |   |   |   |   |

| Bit                                      | Name Function |          |   |   |   |   |   |   |

| 7:0 | DPL[7:0] | Data Pointer Low.                                                                                                           |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------|

|     |          | The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

#### SFR Definition 8.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | DPH[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0x83

| Bit | Name     | Function                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                                                                                           |

|     |          | The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

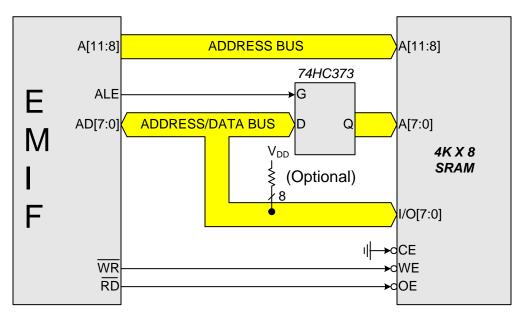

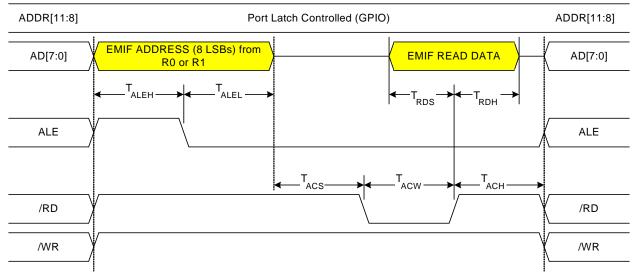

Figure 10.2. Multiplexed to Non-Multiplexed Configuration Example

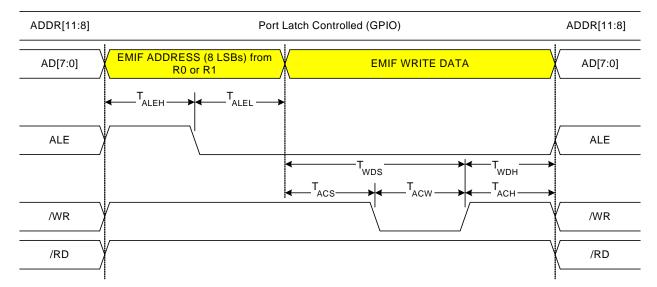

### 10.8.2. Multiplexed 8-bit MOVX without Bank Select: EMI0CF[3:2] = 01 or 11.

Muxed 8-bit WRITE Without Bank Select

#### Muxed 8-bit READ Without Bank Select

Note: See the Port Input/Output chapter to determine which port pins are mapped to the ADDR[11:8], AD[7:0], ALE, /RD, and /WR signals.

#### Figure 10.5. Multiplexed 8-bit MOVX without Bank Select Timing

## **12.3.** Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. If a high priority interrupt preempts a low priority interrupt, the low priority interrupt will finish execution after the high priority interrupt completes. Each interrupt has an associated interrupt priority bit in in the Interrupt Priority and Extended Interrupt Priority registers used to configure its priority level. Low priority is the default.

If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate. See Table 12.1 on page 138 to determine the fixed priority order used to arbitrate between simultaneously recognized interrupts.

#### 12.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 7 system clock cycles: 1 clock cycle to detect the interrupt, 1 clock cycle to execute a single instruction, and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 19 system clock cycles: 1 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

#### 13.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

An additional 1024-byte scratchpad is available for non-volatile data storage. It is accessible at addresses 0x0000 to 0x03FF when SFLE is set to 1. The scratchpad area cannot be used for code execution.

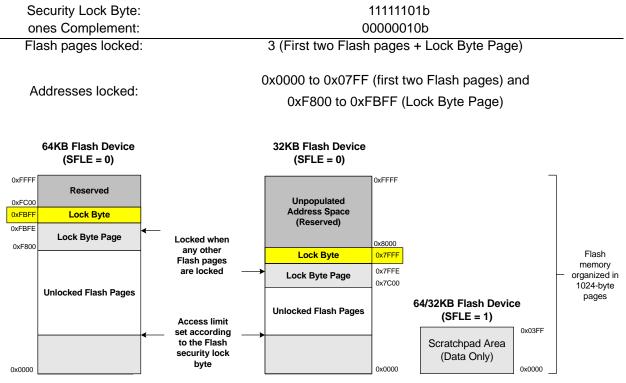

#### 13.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock *n* 1024-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x03FF), where *n* is the 1s complement number represented by the Security Lock Byte. **The page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0). See the C8051F930 example below.**

Figure 13.1. Flash Program Memory Map

GPIO pins configured as digital inputs can be used during sleep mode as wakeup sources using the port match feature. In two-cell mode, they will maintain the same input level specs in sleep mode as they have in normal mode. In one-cell mode, the VDD supply will drop to the level of VBAT, which will lower the switching threshold and increase the propagation delay.

**Note:** By default, the VDD/DC+ supply is connected to VBAT upon entry into Sleep Mode (one-cell mode). If the VDDSLP bit (DC0CF.1) is set to logic 1, the VDD/DC+ supply will float in Sleep Mode. This allows the decoupling capacitance on the VDD/DC+ supply to maintain the supply rail until the capacitors are discharged. For relatively short sleep intervals, this can result in substantial power savings because the decoupling capacitance is not continuously charged and discharged.

RAM and SFR register contents are preserved in Sleep mode as long as the voltage on VBAT does not fall below  $V_{POR}$ . The PC counter and all other volatile state information is preserved allowing the device to resume code execution upon waking up from Sleep mode. The following wake-up sources can be configured to wake the device from Sleep mode:

- SmaRTClock Oscillator Fail

- SmaRTClock Alarm

- Port Match Event

- Comparator0 Rising Edge.

The Comparator0 Rising Edge wakeup is only valid in two-cell mode. The comparator requires a supply voltage of at least 1.8 V to operate properly.

In addition, any falling edge on  $\overline{\text{RST}}$  (due to a pin reset or a noise glitch) will cause the device to exit sleep mode. In order for the MCU to respond to the pin reset event, software must not place the device back into sleep mode for a period of 15 µs. The PMU0CF register may be checked to determine if the wake-up was due to a falling edge on the RST pin. If the wake-up source is not due to a falling edge on RST, there is no time restriction on how soon software may place the device back into sleep mode. A 4.7 kΩ pullup resistor to VDD/DC+ is recommend for RST to prevent noise glitches from waking the device.

## 14.6. Configuring Wakeup Sources

Before placing the device in a low power mode, one or more wakeup sources should be enabled so that the device does not remain in the low power mode indefinitely. For idle mode, this includes enabling any interrupt. For stop mode, this includes enabling any reset source or relying on the RST pin to reset the device.

Wake-up sources for suspend and sleep modes are configured through the PMU0CF register. Wake-up sources are enabled by writing 1 to the corresponding wake-up source enable bit. Wake-up sources must be re-enabled each time the device is placed in Suspend or Sleep mode, in the same write that places the device in the low power mode.

The reset pin is always enabled as a wake-up source. On the falling edge of  $\overline{RST}$ , the device will be awaken from sleep mode. The device must remain awake for more than 15 µs in order for the reset to take place.

The 16-bit C8051F93x-C8051F92x CRC algorithm can be described by the following code:

unsigned short UpdateCRC (unsigned short CRC\_acc, unsigned char CRC\_input)

{

```

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

11

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;</pre>

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;</pre>

}

}

// Return the final remainder (CRC value)

return CRC_acc;

```

The following table lists several input values and the associated outputs using the 16-bit C8051F93x-C8051F92x CRC algorithm:

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0x8C                         | 0xB1F4 |

| 0x7D                         | 0x4ECA |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

}

### **19.1.** Programmable Precision Internal Oscillator

All C8051F93x-C8051F92x devices include a programmable precision internal oscillator that may be selected as the system clock. OSCICL is factory calibrated to obtain a 24.5 MHz frequency. See Section "4. Electrical Characteristics" on page 45 for complete oscillator specifications.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The deviation from the nominal oscillator frequency is +0%, -1.6%, and the step size is typically 0.26% of the nominal frequency. When using this mode, the typical average oscillator frequency is lowered from 24.5 MHz to 24.3 MHz.

#### 19.2. Low Power Internal Oscillator

All C8051F93x-C8051F92x devices include a low power internal oscillator that defaults as the system clock after a system reset. The low power internal oscillator frequency is  $20 \text{ MHz} \pm 10\%$  and is automatically enabled when selected as the system clock and disabled when not in use. See Section "4. Electrical Characteristics" on page 45 for complete oscillator specifications.

#### **19.3. External Oscillator Drive Circuit**

All C8051F93x-C8051F92x devices include an external oscillator circuit that may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. Figure 19.1 shows a block diagram of the four external oscillator options. The external oscillator is enabled and configured using the OSCXCN register.

The external oscillator output may be selected as the system clock or used to clock some of the digital peripherals (e.g., timers, PCA, etc.). See the data sheet chapters for each digital peripheral for details. See Section "4. Electrical Characteristics" on page 45 for complete oscillator specifications.

#### 19.3.1. External Crystal Mode

If a crystal or ceramic resonator is used as the external oscillator, the crystal/resonator and a 10 M $\Omega$  resistor must be wired across the XTAL1 and XTAL2 pins as shown in Figure 19.1, Option 1. Appropriate loading capacitors should be added to XTAL1 and XTAL2, and both pins should be configured for analog I/O with the digital output drivers disabled.

Figure 19.2 shows the external oscillator circuit for a 20 MHz quartz crystal with a manufacturer recommended load capacitance of 12.5 pF. Loading capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins. The total value of the each loading capacitor and the stray capacitance of each XTAL pin should equal 12.5pF x 2 = 25 pF. With a stray capacitance of 10 pF per pin, the 15 pF capacitors yield an equivalent series capacitance of 12.5 pF across the crystal.

**Note:** The recommended load capacitance depends upon the crystal and the manufacturer. Refer to the crystal data sheet when completing these calculations.

Table 20.3 shows a summary of the oscillator bias settings. The SmaRTClock Bias Doubling feature allows the self-oscillation frequency to be increased (almost doubled) and allows a higher crystal drive strength in crystal mode. High crystal drive strength is recommended when the crystal is exposed to poor environmental conditions such as excessive moisture. SmaRTClock Bias Doubling is enabled by setting BIASX2 (RTC0XCN.5) to 1.

| Mode           | Setting                  | Power<br>Consumption |

|----------------|--------------------------|----------------------|

| Crystal        | Bias Double Off, AGC On  | Lowest<br>600 nA     |

|                | Bias Double Off, AGC Off | Low<br>800 nA        |

|                | Bias Double On, AGC On   | High                 |

|                | Bias Double On, AGC Off  | Highest              |

| Self-Oscillate | Bias Double Off          | Low                  |

|                | Bias Double On           | High                 |

Table 20.3. SmaRTClock Bias Settings

## Internal Register Definition 20.8. CAPTUREn: SmaRTClock Timer Capture

| Bit                                                                                     | 7                | 6                                                                                                                                                                                        | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Name                                                                                    | e                | CAPTURE[31:0]                                                                                                                                                                            |     |     |     |     |     |     |

| Туре                                                                                    | R/W              | R/W                                                                                                                                                                                      | R/W | R/W | R/W | R/W | R/W | R/W |

| Rese                                                                                    | t 0              | 0                                                                                                                                                                                        | 0   | 0   | 0   | 0   | 0   | 0   |

| SmaRTClock Addresses: CAPTURE0 = 0x00; CAPTURE1 = 0x01; CAPTURE2 =0x02; CAPTURE3: 0x03. |                  |                                                                                                                                                                                          |     |     |     |     |     |     |

| Bit                                                                                     | Name Function    |                                                                                                                                                                                          |     |     |     |     |     |     |

| 7:0                                                                                     | CAPTURE[31       | PTURE[31:0] SmaRTClock Timer Capture.                                                                                                                                                    |     |     |     |     |     |     |

|                                                                                         |                  | These 4 registers (CAPTURE3–CAPTURE0) are used to read or set the 32-bit SmaRTClock timer. Data is transferred to or from the SmaRTClock timer when the RTC0SET or RTC0CAP bits are set. |     |     |     |     |     |     |

| Note:                                                                                   | The least signif |                                                                                                                                                                                          |     |     |     |     |     |     |

### Internal Register Definition 20.9. ALARMn: SmaRTClock Alarm Programmed Value

| Bit   | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | ALARM[31:0] |     |     |     |     |     |     |     |

| Туре  | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SmaRTClock Addresses: ALARM0 = 0x08; ALARM1 = 0x09; ALARM2 = 0x0A; ALARM3 = 0x0B

| Bit   | Name                                                                      | Function                                                                                                                                                                      |  |  |  |  |

|-------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | ALARM[31:0]                                                               | SmaRTClock Alarm Programmed Value.                                                                                                                                            |  |  |  |  |

|       |                                                                           | These 4 registers (ALARM3–ALARM0) are used to set an alarm event for the SmaRTClock timer. The SmaRTClock alarm should be disabled (RTC0AEN=0) when updating these registers. |  |  |  |  |

| Note: | : The least significant bit of the alarm programmed value is in ALARM0.0. |                                                                                                                                                                               |  |  |  |  |

### SFR Definition 21.6. P1MASK: Port1 Mask Register

| Bit   | 7   | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-------------|---|---|---|---|---|---|

| Name  |     | P1MASK[7:0] |   |   |   |   |   |   |

| Туре  | R/W |             |   |   |   |   |   |   |

| Reset | 0   | 0           | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page= 0x0; SFR Address = 0xBF

| Bit | Name                                  | Function                                                                                                                                                                                            |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0]                           | Port 1 Mask Value.                                                                                                                                                                                  |

|     |                                       | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

|     | On C8051F931/21<br>must be set to 0b. | devices, port match is not available on P1.6 or P1.7. The corresponding P1MASK bits                                                                                                                 |

## SFR Definition 21.7. P1MAT: Port1 Match Register

| Bit   | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------|---|---|---|---|---|---|

| Name  |     | P1MAT[7:0] |   |   |   |   |   |   |

| Туре  | R/W |            |   |   |   |   |   |   |

| Reset | 1   | 1          | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xCF

| Bit     | Name                                                                  | Function                                                                                                                                                                                    |  |  |  |  |

|---------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0     | P1MAT[7:0]                                                            | Port 1 Match Value.                                                                                                                                                                         |  |  |  |  |

|         |                                                                       | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |  |  |  |  |

| Note: ( | On C8051F931/21 devices, port match is not available on P1.6 or P1.7. |                                                                                                                                                                                             |  |  |  |  |

## SFR Definition 21.19. P2SKIP: Port2 Skip

| Bit   | 7             | 6                                                                              | 5      | 4    | 3 | 2 | 1     | 0 |  |

|-------|---------------|--------------------------------------------------------------------------------|--------|------|---|---|-------|---|--|

| Name  | 9             | P2SKIP[7:0]                                                                    |        |      |   |   |       |   |  |

| Туре  |               | R/W                                                                            |        |      |   |   |       |   |  |

| Rese  | <b>t</b> 0    | 0                                                                              | 0      | 0    | 0 | 0 | 0     | 0 |  |

| SFR P | age = 0x0; SF | R Address =                                                                    | = 0xD6 |      |   |   |       |   |  |

| Bit   | Name          | Description                                                                    |        | Read |   |   | Write |   |  |

| 7:0   | P2SKIP[7:0]   | P2SKIP[7:0] Port 1 Crossbar Skip Enable Bits.                                  |        |      |   |   |       |   |  |

|       |               | These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins |        |      |   |   |       |   |  |

used for analog, special functions or GPIO should be skipped by the Crossbar. 0: Corresponding P2.n pin is not skipped by the Crossbar.

1: Corresponding P2.n pin is skipped by the Crossbar.

Note: Pins P2.0-P2.6 are only available in 32-pin devices.

#### SFR Definition 21.20. P2MDIN: Port2 Input Mode

| Bit   | 7        | 6                   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---------------------|---|---|---|---|---|---|

| Name  | Reserved | eserved P2MDIN[6:0] |   |   |   |   |   |   |

| Туре  | R/W      |                     |   |   |   |   |   |   |

| Reset | 1        | 1                   | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xF3

| Bit     | Name                                                      | Function                                                                                                                                                                                                                                                                                          |  |  |  |  |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7       |                                                           | Reserved. Read = 1b; Must Write 1b.                                                                                                                                                                                                                                                               |  |  |  |  |

| 6:0     | P2MDIN[3:0]                                               | Analog Configuration Bits for P2.6–P2.0 (respectively).                                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                           | <ul><li>Port pins configured for analog mode have their weak pullup and digital receiver disabled. The digital driver is not explicitly disabled.</li><li>0: Corresponding P2.n pin is configured for analog mode.</li><li>1: Corresponding P2.n pin is not configured for analog mode.</li></ul> |  |  |  |  |

| Note: F | ote: Pins P2.0-P2.6 are only available in 32-pin devices. |                                                                                                                                                                                                                                                                                                   |  |  |  |  |

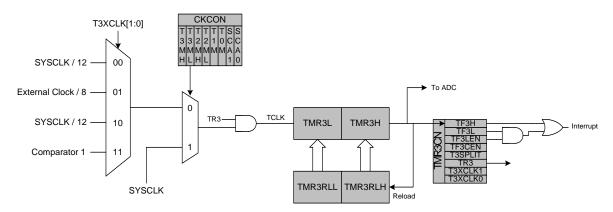

## 25.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR2CN.3) defines the Timer 3 operation mode. Timer 3 can also be used in Capture Mode to measure the external oscillator source or the Comparator 1 period with respect to another oscillator. The ability to measure the Comparator 1 period with respect to the system clock is makes using Touch Sense Switches very easy.

Timer 3 may be clocked by the system clock, the system clock divided by 12, external oscillator source divided by 8, or Comparator 1 output. The external oscillator source divided by 8 and Comparator 1 output is synchronized with the system clock.

#### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, external oscillator clock source divided by 8, or Comparator 1 output. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.7, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x000.

Figure 25.7. Timer 3 16-Bit Mode Block Diagram

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com