Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 24                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 23x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 32-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 32-QFN (5x5)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f930-g-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 21.5. Special Function Registers for Accessing and Configuring Port I/O | 229 |

|-----|-------------------------------------------------------------------------|-----|

| 22. | SMBus                                                                   | 238 |

|     | 22.1.Supporting Documents                                               | 239 |

|     | 22.2.SMBus Configuration                                                | 239 |

|     | 22.3.SMBus Operation                                                    |     |

|     | 22.3.1.Transmitter Vs. Receiver                                         |     |

|     | 22.3.2.Arbitration                                                      |     |

|     | 22.3.3.Clock Low Extension                                              |     |

|     | 22.3.4.SCL Low Timeout                                                  |     |

|     | 22.3.5.SCL High (SMBus Free) Timeout                                    |     |

|     | 22.4.Using the SMBus                                                    | 242 |

|     | 22.4.1.SMBus Configuration Register                                     |     |

|     | 22.4.2.SMB0CN Control Register                                          |     |

|     | 22.4.3.Hardware Slave Address Recognition                               |     |

|     | 22.4.4.Data Register                                                    |     |

|     | 22.5.SMBus Transfer Modes                                               |     |

|     | 22.5.1.Write Sequence (Master)                                          |     |

|     | 22.5.2.Read Sequence (Master)                                           |     |

|     | 22.5.3.Write Sequence (Slave)                                           |     |

|     | 22.5.4.Read Sequence (Slave)                                            |     |

|     | 22.6.SMBus Status Decoding                                              |     |

|     | UART0                                                                   |     |

|     | 23.1.Enhanced Baud Rate Generation                                      |     |

|     | 23.2.Operational Modes                                                  |     |

|     | 23.2.1.8-Bit UART                                                       |     |

|     | 23.2.2.9-Bit UART                                                       | 263 |

|     | 23.3.Multiprocessor Communications                                      |     |

|     | Enhanced Serial Peripheral Interface (SPI0 and SPI1)                    |     |

|     | 24.1.Signal Descriptions                                                |     |

|     | 24.1.1.Master Out, Slave In (MOSI)                                      |     |

|     | 24.1.2.Master In, Slave Out (MISO)                                      |     |

|     | 24.1.3.Serial Clock (SCK)                                               |     |

|     | 24.1.4.Slave Select (NSS)                                               | 269 |

|     | 24.2.SPI Master Mode Operation                                          |     |

|     | 24.3.SPI Slave Mode Operation                                           |     |

|     | 24.4.SPI Interrupt Sources                                              |     |

|     | 24.5.Serial Clock Phase and Polarity                                    | 273 |

|     | 24.6.SPI Special Function Registers                                     |     |

|     | Timers                                                                  |     |

|     | 25.1.Timer 0 and Timer 1                                                | 285 |

|     | 25.1.1.Mode 0: 13-bit Counter/Timer                                     |     |

|     | 25.1.2.Mode 1: 16-bit Counter/Timer                                     |     |

|     | 25.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload                     | 287 |

|     | 25.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)                  | 288 |

|     | 25.2.Timer 2                                                            | 293 |

# List of Figures

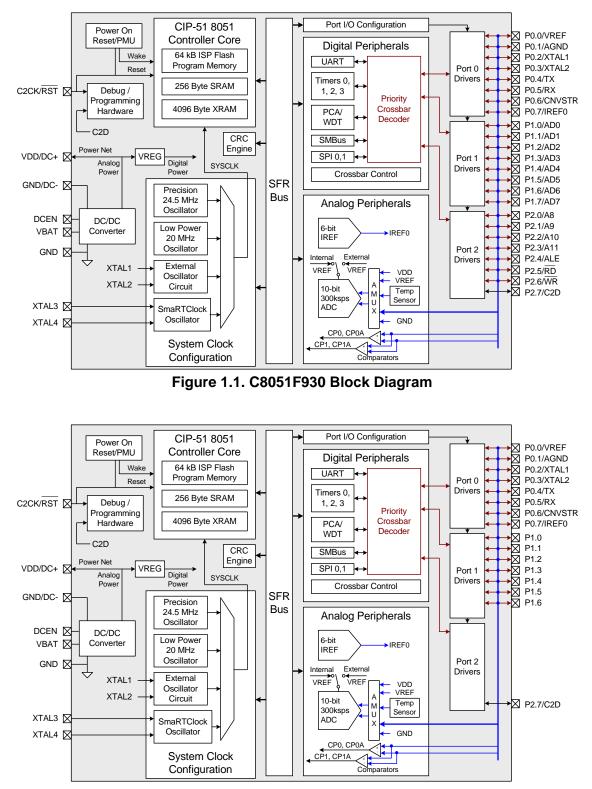

| Figure 1.1. C8051F930 Block Diagram                                                          | 18 |

|----------------------------------------------------------------------------------------------|----|

| Figure 1.2. C8051F931 Block Diagram                                                          |    |

| Figure 1.3. C8051F920 Block Diagram                                                          |    |

| Figure 1.4. C8051F921 Block Diagram                                                          |    |

| Figure 1.5. Port I/O Functional Block Diagram                                                |    |

| Figure 1.6. PCA Block Diagram                                                                |    |

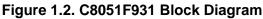

| Figure 1.7. ADC0 Functional Block Diagram                                                    |    |

| Figure 1.8. ADC0 Multiplexer Block Diagram                                                   |    |

| Figure 1.9. Comparator 0 Functional Block Diagram                                            |    |

| Figure 1.10. Comparator 1 Functional Block Diagram                                           |    |

| Figure 3.1. QFN-32 Pinout Diagram (Top View)                                                 |    |

| Figure 3.2. QFN-24 Pinout Diagram (Top View)                                                 |    |

| Figure 3.3. LQFP-32 Pinout Diagram (Top View)                                                |    |

| Figure 3.4. QFN-32 Package Marking Diagram                                                   |    |

| Figure 3.5. QFN-24 Package Marking Diagram                                                   |    |

| Figure 3.6. LQFP-32 Package Marking Diagram                                                  |    |

| Figure 3.7. QFN-32 Package Drawing                                                           |    |

| Figure 3.8. Typical QFN-32 Landing Diagram                                                   |    |

| Figure 3.9. QFN-24 Package Drawing                                                           |    |

| Figure 3.10. Typical QFN-24 Landing Diagram                                                  |    |

| Figure 3.11. LQFP-32 Package Diagram                                                         |    |

| Figure 3.12. Typical LQFP-32 Landing Diagram                                                 |    |

| Figure 4.1. Active Mode Current (External CMOS Clock)                                        |    |

| Figure 4.2. Idle Mode Current (External CMOS Clock)                                          |    |

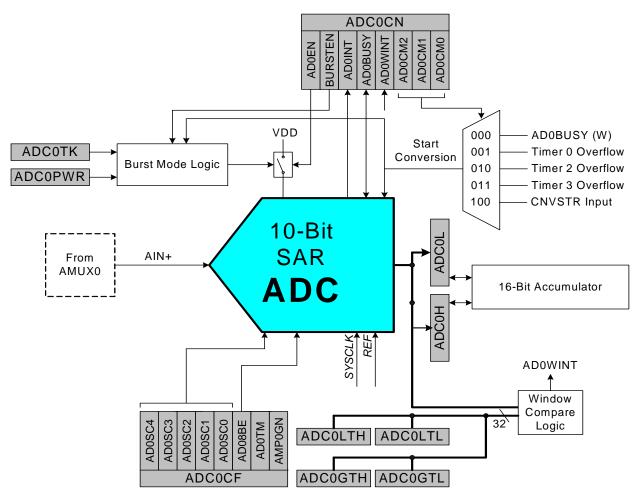

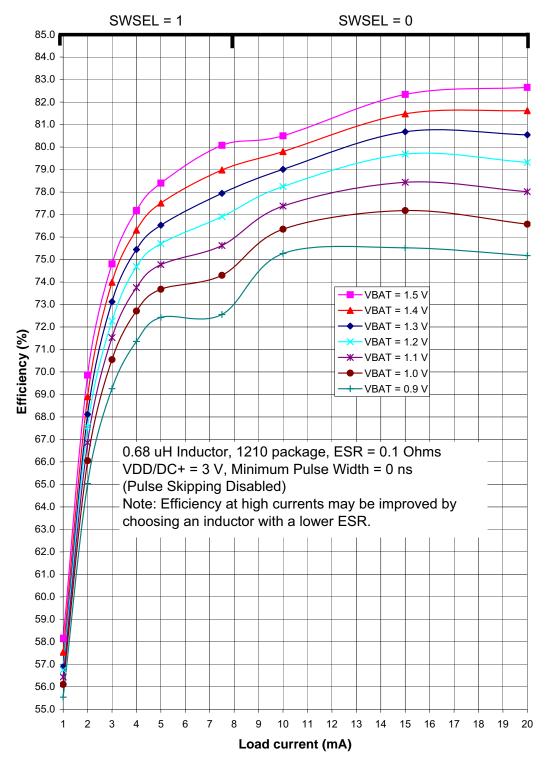

| Figure 4.3. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = $2 \text{ V}$ )      |    |

| Figure 4.4. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = $3$ V)               |    |

| Figure 4.5. Typical DC-DC Converter Efficiency (Low Current, VDD/DC+ = $2 V$ )               |    |

| Figure 4.6. Typical One-Cell Suspend Mode Current                                            |    |

| Figure 4.7. Typical VOH Curves, 1.8–3.6 V                                                    |    |

| Figure 4.8. Typical VOH Curves, 0.9–1.8 V                                                    |    |

| Figure 4.9. Typical VOL Curves, 1.8–3.6 V                                                    |    |

| Figure 4.10. Typical VOL Curves, 0.9–1.8 V                                                   |    |

| Figure 5.1. ADC0 Functional Block Diagram                                                    |    |

| Figure 5.2. 10-Bit ADC Track and Conversion Example Timing (BURSTEN = 0)                     |    |

| Figure 5.3. Burst Mode Tracking Example with Repeat Count Set to 4                           |    |

| Figure 5.4. ADC0 Equivalent Input Circuits                                                   |    |

| Figure 5.5. ADC Window Compare Example: Right-Justified Single-Ended Data                    | 83 |

| Figure 5.6. ADC Window Compare Example: Left-Justified Single-Ended Data                     |    |

| Figure 5.7. ADC0 Multiplexer Block Diagram                                                   |    |

| Figure 5.8. Temperature Sensor Transfer Function                                             |    |

| Figure 5.9. Temperature Sensor Error with 1-Point Calibration ( $V_{REF} = 1.68 \text{ V}$ ) |    |

| Figure 5.10. Voltage Reference Functional Block Diagram                                      |    |

| Figure 7.1. Comparator 0 Functional Block Diagram                                            |    |

| - Sale Comparator o ranouonal Blook Blagram minimum                                          | 50 |

| Table 22.2 Minimum CDA Cature and Hold Times                            | - 4 4 |

|-------------------------------------------------------------------------|-------|

|                                                                         | 244   |

| Table 22.3. Sources for Hardware Changes to SMB0CN 2                    | 248   |

| Table 22.4. Hardware Address Recognition Examples (EHACK = 1) 2         | 249   |

| Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled |       |

| (EHACK = 0)                                                             | 256   |

| Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled  |       |

| (EHACK = 1)                                                             | 258   |

| Table 23.1. Timer Settings for Standard Baud Rates                      |       |

| Using The Internal 24.5 MHz Oscillator 2                                | 267   |

| Table 23.2. Timer Settings for Standard Baud Rates                      |       |

| Using an External 22.1184 MHz Oscillator 2                              | 267   |

| Table 24.1. SPI Slave Timing Parameters                                 | 282   |

| Table 25.1. Timer 0 Running Modes 2                                     | 285   |

| Table 26.1. PCA Timebase Input Options                                  | 306   |

| Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare    |       |

| Modules                                                                 | 308   |

| Table 26.3. Watchdog Timer Timeout Intervals1                           | 317   |

## 1.1. CIP-51<sup>™</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F93x-C8051F92x family utilizes Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS.

#### 1.1.3. Additional Features

The C8051F93x-C8051F92x SoC family includes several key enhancements to the CIP-51 core and peripherals to improve performance and ease of use in end applications.

The extended interrupt handler provides multiple interrupt sources into the CIP-51 allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

Eight reset sources are available: power-on reset circuitry (POR), an on-chip  $V_{DD}$  monitor (forces reset when power supply voltage drops below safe levels), a Watchdog Timer, a Missing Clock Detector, SmaRTClock oscillator fail or alarm, a voltage level detection from Comparator0, a forced software reset, an external reset pin, and an illegal Flash access protection circuit. Each reset source except for the POR, Reset Input Pin, or Flash error may be disabled by the user in software. The WDT may be permanently disabled in software after a power-on reset during MCU initialization.

The internal oscillator factory calibrated to 24.5 MHz and is accurate to  $\pm 2\%$  over the full temperature and supply range. The internal oscillator period can also be adjusted by user firmware. An additional 20 MHz low power oscillator is also available which facilitates low-power operation. An external oscillator drive circuit is included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate the system clock. If desired, the system clock source may be switched on-the-fly between both internal and external oscillator circuits. An external oscillator can also be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) source, while periodically switching to the fast (up to 25 MHz) internal oscillator as needed.

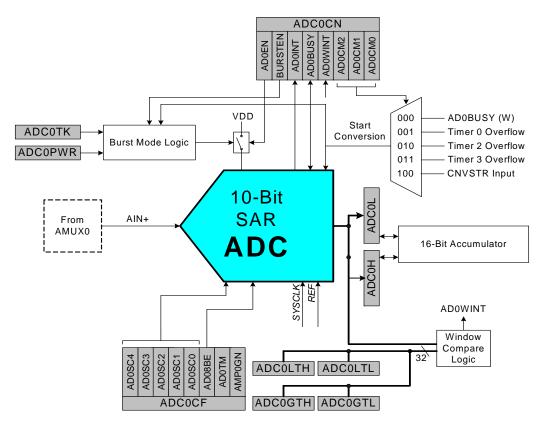

## 1.5. 10-Bit SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

C8051F93x-C8051F92x devices have a 300 ksps, 10-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically average the ADC results, providing an effective 11, 12, or 13 bit ADC result without any additional CPU intervention.

The ADC can sample the voltage at any of the GPIO pins (with the exception of P2.7) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD/DC+ supply voltage, the VBAT supply voltage, and the internal digital supply voltage.

Figure 1.7. ADC0 Functional Block Diagram

Figure 4.3. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 2 V)

Figure 4.4. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 3 V)

# 5. 10-Bit SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on the C8051F93x-C8051F92x is a 300 ksps, 10-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.5. ADC0 Analog Multiplexer" on page 84. The voltage reference for the ADC is selected as described in "5.7. Voltage and Ground Reference Options" on page 89.

Figure 5.1. ADC0 Functional Block Diagram

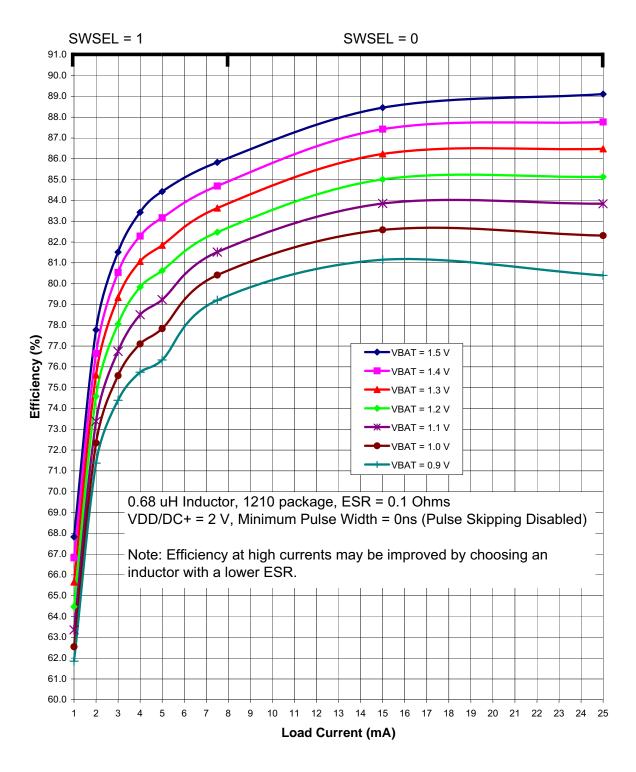

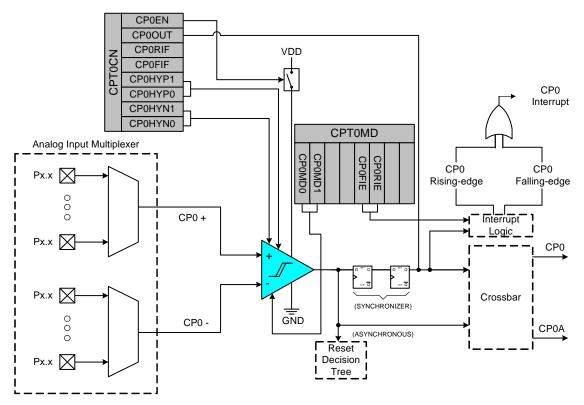

# 7. Comparators

C8051F93x-C8051F92x devices include two on-chip programmable voltage comparators: Comparator 0 (CPT0) is shown in Figure 7.1; Comparator 1 (CPT1) is shown in Figure 7.2. The two comparators operate identically, but may differ in their ability to be used as reset or wake-up sources. See the Reset Sources chapter and the Power Management chapter for details on reset sources and low power mode wake-up sources, respectively.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

## 7.1. Comparator Inputs

Each Comparator performs an analog comparison of the voltage levels at its positive (CP0+ or CP1+) and negative (CP0- or CP1-) input. Both comparators support multiple port pin inputs multiplexed to their positive and negative comparator inputs using analog input multiplexers. The analog input multiplexers are completely under software control and configured using SFR registers. See Section "7.6. Comparator0 and Comparator1 Analog Multiplexers" on page 100 for details on how to select and configure Comparator inputs.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs and skipped by the Crossbar. See the Port I/O chapter for more details on how to configure Port I/O pins as Analog Inputs. The Comparator may also be used to compare the logic level of digital signals, however, Port I/O pins configured as digital inputs must be driven to a valid logic state (HIGH or LOW) to avoid increased power consumption.

Figure 7.1. Comparator 0 Functional Block Diagram

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |  |

|--------------------|--------------------------------------------|-------|-----------------|--|

| CLR A              | Clear A                                    | 1     | 1               |  |

| CPL A              | Complement A                               | 1     | 1               |  |

| RL A               | Rotate A left                              | 1     | 1               |  |

| RLC A              | Rotate A left through Carry                | 1     | 1               |  |

| RR A               | Rotate A right                             | 1     | 1               |  |

| RRC A              | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |  |

|                    | Data Transfer                              |       |                 |  |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |  |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |  |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

|                    | Boolean Manipulation                       |       | <b></b>         |  |

| CLR C              | Clear Carry                                | 1     | 1               |  |

| CLR bit            | Clear direct bit                           | 2     | 2               |  |

| SETB C             | Set Carry                                  | 1     | 1               |  |

| SETB bit           | Set direct bit                             | 2     | 2               |  |

| CPL C              | Complement Carry                           | 1     | 1               |  |

| CPL bit            | Complement direct bit                      | 2     | 2               |  |

| ANL C, bit         | AND direct bit to Carry                    | 2     | 2               |  |

| ,                  |                                            | 2     | <u> </u>        |  |

# Table 8.1. CIP-51 Instruction Set Summary (Continued)

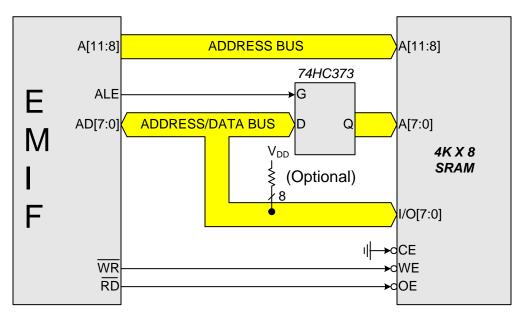

Figure 10.2. Multiplexed to Non-Multiplexed Configuration Example

# **11. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F93x-C8051F92x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F93x-C8051F92x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 11.1 and Table 11.2 list the SFRs implemented in the C8051F93x-C8051F92x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 11.3, for a detailed description of each register.

| F8 | SPI0CN     | PCA0L         | PCA0H    | PCA0CPL0 | PCA0CPH0 | PCA0CPL4 | PCA0CPH4 | VDM0CN  |

|----|------------|---------------|----------|----------|----------|----------|----------|---------|

| F0 | В          | POMDIN        | P1MDIN   | P2MDIN   | SMB0ADR  | SMB0ADM  | EIP1     | EIP2    |

| E8 | ADC0CN     | PCA0CPL1      | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | PCA0CPL3 | PCA0CPH3 | RSTSRC  |

| E0 | ACC        | XBR0          | XBR1     | XBR2     | IT01CF   |          | EIE1     | EIE2    |

| D8 | PCA0CN     | PCA0MD        | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | PCA0CPM3 | PCA0CPM4 | PCA0PWM |

| D0 | PSW        | <b>REF0CN</b> | PCA0CPL5 | PCA0CPH5 | P0SKIP   | P1SKIP   | P2SKIP   | POMAT   |

| C8 | TMR2CN     | REG0CN        | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H    | PCA0CPM5 | P1MAT   |

| C0 | SMB0CN     | SMB0CF        | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL  | ADC0LTH  | P0MASK  |

| B8 | IP         | IREF0CN       | ADC0AC   | ADC0MX   | ADC0CF   | ADC0L    | ADC0H    | P1MASK  |

| B0 | SPI1CN     | OSCXCN        | OSCICN   | OSCICL   |          | PMU0CF   | FLSCL    | FLKEY   |

| A8 | IE         | CLKSEL        | EMIOCN   | EMI0CF   | RTC0ADR  | RTC0DAT  | RTC0KEY  | EMI0TC  |

| A0 | P2         | SPI0CFG       | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT  | P2MDOUT  | SFRPAGE |

| 98 | SCON0      | SBUF0         | CPT1CN   | CPT0CN   | CPT1MD   | CPT0MD   | CPT1MX   | CPT0MX  |

| 90 | P1         | TMR3CN        | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H    | DC0CF    | DC0CN   |

| 88 | TCON       | TMOD          | TL0      | TL1      | TH0      | TH1      | CKCON    | PSCTL   |

| 80 | P0         | SP            | DPL      | DPH      | SPI1CFG  | SPI1CKR  | SPI1DAT  | PCON    |

|    | 0(8)       | 1(9)          | 2(A)     | 3(B)     | 4(C)     | 5(D)     | 6(E)     | 7(F)    |

| /h | it address | abla)         |          |          |          |          |          |         |

#### Table 11.1. Special Function Register (SFR) Memory Map (Page 0x0)

(bit addressable)

## Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page | Description                      | Page |

|----------|---------|----------|----------------------------------|------|

| P0SKIP   | 0xD4    | 0x0      | Port 0 Skip                      | 230  |

| P1       | 0x90    | All      | Port 1 Latch                     | 233  |

| P1DRV    | 0xA5    | 0xF      | Port 1 Drive Strength            | 235  |

| P1MASK   | 0xBF    | 0x0      | Port 1 Mask                      | 228  |

| P1MAT    | 0xCF    | 0x0      | Port 1 Match                     | 228  |

| P1MDIN   | 0xF2    | 0x0      | Port 1 Input Mode Configuration  | 234  |

| P1MDOUT  | 0xA5    | 0x0      | Port 1 Output Mode Configuration | 234  |

| P1SKIP   | 0xD5    | 0x0      | Port 1 Skip                      | 233  |

| P2       | 0xA0    | All      | Port 2 Latch                     | 235  |

| P2DRV    | 0xA6    | 0xF      | Port 2 Drive Strength            | 237  |

| P2MDIN   | 0xF3    | 0x0      | Port 2 Input Mode Configuration  | 236  |

| P2MDOUT  | 0xA6    | 0x0      | Port 2 Output Mode Configuration | 237  |

| P2SKIP   | 0xD6    | 0x0      | Port 2 Skip                      | 236  |

| PCA0CN   | 0xD8    | 0x0      | PCA0 Control                     | 318  |

| PCA0CPH0 | 0xFC    | 0x0      | PCA0 Capture 0 High              | 323  |

| PCA0CPH1 | 0xEA    | 0x0      | PCA0 Capture 1 High              | 323  |

| PCA0CPH2 | 0xEC    | 0x0      | PCA0 Capture 2 High              | 323  |

| PCA0CPH3 | 0xEE    | 0x0      | PCA0 Capture 3 High              | 323  |

| PCA0CPH4 | 0xFE    | 0x0      | PCA0 Capture 4 High              | 323  |

| PCA0CPH5 | 0xD3    | 0x0      | PCA0 Capture 5 High              | 323  |

| PCA0CPL0 | 0xFB    | 0x0      | PCA0 Capture 0 Low               | 323  |

| PCA0CPL1 | 0xE9    | 0x0      | PCA0 Capture 1 Low               | 323  |

| PCA0CPL2 | 0xEB    | 0x0      | PCA0 Capture 2 Low               | 323  |

| PCA0CPL3 | 0xED    | 0x0      | PCA0 Capture 3 Low               | 323  |

| PCA0CPL4 | 0xFD    | 0x0      | PCA0 Capture 4 Low               | 323  |

| PCA0CPL5 | 0xD2    | 0x0      | PCA0 Capture 5 Low               | 323  |

| PCA0CPM0 | 0xDA    | 0x0      | PCA0 Module 0 Mode Register      | 321  |

| PCA0CPM1 | 0xDB    | 0x0      | PCA0 Module 1 Mode Register      | 321  |

| PCA0CPM2 | 0xDC    | 0x0      | PCA0 Module 2 Mode Register      | 321  |

| PCA0CPM3 | 0xDD    | 0x0      | PCA0 Module 3 Mode Register      | 321  |

| PCA0CPM4 | 0xDE    | 0x0      | PCA0 Module 4 Mode Register      | 321  |

| PCA0CPM5 | 0xCE    | 0x0      | PCA0 Module 5 Mode Register      | 321  |

| PCA0H    | 0xFA    | 0x0      | PCA0 Counter High                | 322  |

| PCA0L    | 0xF9    | 0x0      | PCA0 Counter Low                 | 322  |

# SFR Definition 12.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1      | 0     |

|-------|-----|------|------|-------|-------|--------|--------|-------|

| Name  | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ERTC0A | ESMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W    | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0      | 0     |

|       |     |      |      |       |       | ·      |        |       |

SFR Page = All Pages; SFR Address = 0xE6

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET3    | Enable Timer 3 Interrupt.<br>This bit sets the masking of the Timer 3 interrupt.<br>0: Disable Timer 3 interrupts.<br>1: Enable interrupt requests generated by the TF3L or TF3H flags.                                                                                           |

| 6   | ECP1   | Enable Comparator1 (CP1) Interrupt.<br>This bit sets the masking of the CP1 interrupt.<br>0: Disable CP1 interrupts.<br>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.                                                                                     |

| 5   | ECP0   | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                     |

| 4   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 3   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 2   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | ERTC0A | Enable SmaRTClock Alarm Interrupts.<br>This bit sets the masking of the SmaRTClock Alarm interrupt.<br>0: Disable SmaRTClock Alarm interrupts.<br>1: Enable interrupt requests generated by a SmaRTClock Alarm.                                                                   |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

## 13.5. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F92x-C8051F93x devices for the Flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### **13.5.1. VDD Maintenance and the VDD Monitor**

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the maximum VBAT ramp time specification of 3 ms is met. This specification is outlined in Table 4.4 on page 59. On silicon revision F and later revisions, if the system cannot meet this rise time specification, then add an external VDD brownout circuit to the RST pin of the device that holds the device in reset until VDD reaches the minimum device operating voltage and re-asserts RST if VDD drops below the minimum device operating voltage.

- 3. Keep the on-chip VDD Monitor enabled and enable the VDD Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the 'C' compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the VDD Monitor and enabling the VDD Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

#### Notes:

On C8051F93x-C8051F92x devices, both the VDD Monitor and the VDD Monitor reset source must be enabled to write or erase Flash without generating a Flash Error Device Reset.

On C8051F93x-C8051F92x devices, both the VDD Monitor and the VDD Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the VDD Monitor and enable the VDD Monitor as a reset source inside the functions that write and erase Flash memory. The VDD Monitor enable instructions should be placed just after the instruction to set PSWE to a '1', but before the Flash write or erase operation instruction.

- 5. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a '1'. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

# 17. Voltage Regulator (VREG0)

C8051F93x-C8051F92x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD/DC+ supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters sleep mode and remains enabled when the device enters suspend mode. See Section "14. Power Management" on page 159 for complete details about low power modes.

#### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 1       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                                                                      |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 5   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                                                                                                                                          |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to save approximately 80 $\mu$ A of supply current in all non-Sleep power modes. If disabled then re-enabled, the precision oscillator bias requires 4 $\mu$ s of settling time. |

| 3:1 | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 000b. Write = Don't care.                                                                                                                                                                                                                                                                                                    |

| 0   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

#### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 66 for detailed Voltage Regulator Electrical Specifications.

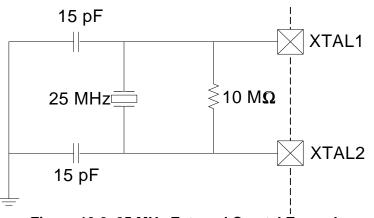

Figure 19.2. 25 MHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

When using an external crystal, the external oscillator drive circuit must be configured by software for *Crystal Oscillator Mode* or *Crystal Oscillator Mode with divide by 2 stage*. The divide by 2 stage ensures that the clock derived from the external oscillator has a duty cycle of 50%. The External Oscillator Frequency Control value (XFCN) must also be specified based on the crystal frequency. The selection should be based on Table 19.1. For example, a 25 MHz crystal requires an XFCN setting of 111b.

| XFCN | Crystal Frequency     | Bias Current | Typical Supply Current<br>(VDD = 2.4 V) |

|------|-----------------------|--------------|-----------------------------------------|

| 000  | f ≤ 20 kHz            | 0.5 µA       | 3.0 µA, f = 32.768 kHz                  |

| 001  | 20 kHz < f ≤ 58 kHz   | 1.5 µA       | 4.8 µA, f = 32.768 kHz                  |

| 010  | 58 kHz < f ≤ 155 kHz  | 4.8 µA       | 9.6 µA, f = 32.768 kHz                  |

| 011  | 155 kHz < f ≤ 415 kHz | 14 µA        | 28 µA, f = 400 kHz                      |

| 100  | 415 kHz < f ≤ 1.1 MHz | 40 µA        | 71 µA, f = 400 kHz                      |

| 101  | 1.1 MHz < f ≤ 3.1 MHz | 120 µA       | 193 µA, f = 400 kHz                     |

| 110  | 3.1 MHz < f ≤ 8.2 MHz | 550 µA       | 940 µA, f = 8 MHz                       |

| 111  | 8.2 MHz < f ≤ 25 MHz  | 2.6 mA       | 3.9 mA, f = 25 MHz                      |

Table 19.1. Recommended XFCN Settings for Crystal Mode

When the crystal oscillator is first enabled, the external oscillator valid detector allows software to determine when the external system clock has stabilized. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure for starting the crystal is:

- 1. Configure XTAL1 and XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD  $\geq$  1.

- 4. Switch the system clock to the external oscillator.

#### 20.2.5. Missing SmaRTClock Detector

The missing SmaRTClock detector is a one-shot circuit enabled by setting MCLKEN (RTC0CN.6) to 1. When the SmaRTClock Missing Clock Detector is enabled, OSCFAIL (RTC0CN.5) is set by hardware if SmaRTClock oscillator remains high or low for more than 100  $\mu$ s.

A SmaRTClock Missing Clock detector timeout can trigger an interrupt, wake the device from a low power mode, or reset the device. See Section "12. Interrupt Handler" on page 136, Section "14. Power Management" on page 159, and Section "18. Reset Sources" on page 184 for more information.

**Note:** The SmaRTClock Missing Clock Detector should be disabled when making changes to the oscillator settings in RTC0XCN.

#### 20.2.6. SmaRTClock Oscillator Crystal Valid Detector

The SmaRTClock oscillator crystal valid detector is an oscillation amplitude detector circuit used during crystal startup to determine when oscillation has started and is nearly stable. The output of this detector can be read from the CLKVLD bit (RTX0XCN.4).

#### Notes:

- The CLKVLD bit has a blanking interval of 2 ms. During the first 2 ms after turning on the crystal oscillator, the output of CLKVLD is not valid.

- This SmaRTClock crystal valid detector (CLKVLD) is not intended for detecting an oscillator failure. The missing SmaRTClock detector (CLKFAIL) should be used for this purpose.

#### 20.3. SmaRTClock Timer and Alarm Function

The SmaRTClock timer is a 32-bit counter that, when running (RTC0TR = 1), is incremented every SmaRTClock oscillator cycle. The timer has an alarm function that can be set to generate an interrupt, wake the device from a low power mode, or reset the device at a specific time. See Section "12. Interrupt Handler" on page 136, Section "14. Power Management" on page 159, and Section "18. Reset Sources" on page 184 for more information.

The SmaRTClock timer includes an Auto Reset feature, which automatically resets the timer to zero one SmaRTClock cycle after an alarm occurs. When using Auto Reset, the Alarm match value should always be set to 1 count less than the desired match value. Auto Reset can be enabled by writing a 1 to ALRM (RTC0CN.2).

#### 20.3.1. Setting and Reading the SmaRTClock Timer Value

The 32-bit SmaRTClock timer can be set or read using the six CAPTUREn internal registers. Note that the timer does not need to be stopped before reading or setting its value. The following steps can be used to set the timer value:

- 1. Write the desired 32-bit set value to the CAPTUREn registers.

- 2. Write 1 to RTC0SET. This will transfer the contents of the CAPTUREn registers to the SmaRT-Clock timer.

- 3. Operation is complete when RTC0SET is cleared to 0 by hardware.

The following steps can be used to read the current timer value:

- 1. Write 1 to RTC0CAP. This will transfer the contents of the timer to the CAPTUREn registers.

- 2. Poll RTC0CAP until it is cleared to 0 by hardware.

- 3. A snapshot of the timer value can be read from the CAPTUREn registers

# 26. Programmable Counter Array

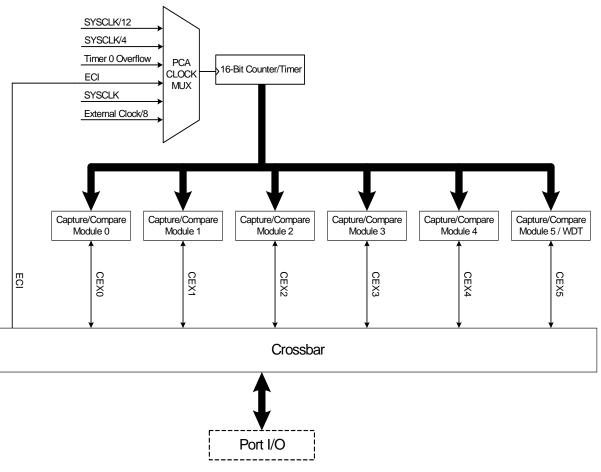

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 308). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram