Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 15x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f931-g-gmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 3.5. QFN-24 Package Marking Diagram

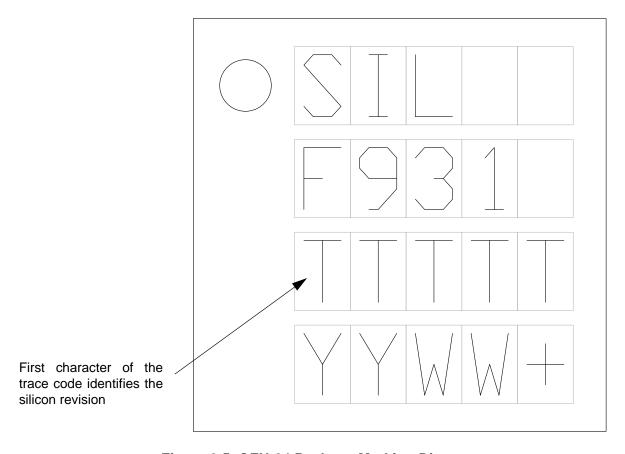

### 5.6. Temperature Sensor

An on-chip temperature sensor is included on the C8051F93x-C8051F92x which can be directly accessed via the ADC multiplexer in single-ended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should select the temperature sensor. The temperature sensor transfer function is shown in Figure 5.8. The output voltage (V<sub>TEMP</sub>) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 5.15. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 4.9 for the slope and offset parameters of the temperature sensor.

**Important Note**: Before switching the ADC multiplexer from another channel to the temperature sensor, the ADC mux should select the 'Ground' channel as an intermediate step. The intermediate 'Ground' channel selection step will discharge any voltage on the ADC sampling capacitor from the previous channel selection. This will prevent the possibility of a high voltage (> 2V) being presented to the temperature sensor circuit, which can otherwise impact its long-term reliability.

Figure 5.8. Temperature Sensor Transfer Function

### 5.8. External Voltage References

To use an external voltage reference, REFSL[1:0] should be set to 00 and the internal 1.68 V precision reference should be disabled by setting REFOE to 0. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

#### 5.9. Internal Voltage References

For applications requiring the maximum number of port I/O pins, or very short VREF turn-on time, the 1.65 V high-speed reference will be the best internal reference option to choose. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high speed internal reference will be automatically enabled/disabled on an as-needed basis by ADC0.

For applications requiring the highest absolute accuracy, the 1.68 V precision voltage reference will be the best internal reference option to choose. The 1.68 V precision reference may be enabled and selected by setting REFOE to 1 and REFSL[1:0] to 00. An external capacitor of at least 0.1  $\mu$ F is recommended when using the precision voltage reference.

In applications that leave the precision internal oscillator always running, there is no additional power required to use the precision voltage reference. In all other applications, using the high speed reference will result in lower overall power consumption due to its minimal startup time and the fact that it remains in a low power state when an ADC conversion is not taking place.

Note: When using the precision internal oscillator as the system clock source, the precision voltage reference should not be enabled from a disabled state. To use the precision oscillator and the precision voltage reference simultaneously, the precision voltage reference should be enabled first and allowed to settle to its final value (charging the external capacitor) before the precision oscillator is started and selected as the system clock.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage (V<sub>DD</sub>/DC+) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 5.10. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 during both the tracking/sampling and the conversion periods is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. This pin should be connected to the ground terminal of any external sensors sampled by ADC0. If an external voltage reference is used, the P0.1/AGND pin should be connected to the ground of the external reference and its associated decoupling capacitor. If the 1.68 V precision internal reference is used, then P0.1/AGND should be connected to the ground terminal of its external decoupling capacitor. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when sampling the internal temperature sensor, the internal chip ground is always used for the sampling operation, regardless of the setting of the REFGND bit. Similarly, whenever the internal 1.65 V high-speed reference is selected, the internal chip ground is always used during the conversion period, regardless of the setting of the REFGND bit.

#### 5.11. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data. See Section "5.6. Temperature Sensor" on page 86 for details on temperature sensor characteristics when it is enabled.

## SFR Definition 12.4. EIP1: Extended Interrupt Priority 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1      | 0     |

|-------|-----|------|------|-------|-------|--------|--------|-------|

| Name  | PT3 | PCP1 | PCP0 | PPCA0 | PADC0 | PWADC0 | PRTC0A | PSMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W    | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0      | 0     |

SFR Page = All Pages; SFR Address = 0xF6

| Bit | Name   | Function                                                                                                                                                                                                                                                         |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PT3    | Timer 3 Interrupt Priority Control.  This bit sets the priority of the Timer 3 interrupt. 0: Timer 3 interrupts set to low priority level. 1: Timer 3 interrupts set to high priority level.                                                                     |

| 6   | PCP1   | Comparator1 (CP1) Interrupt Priority Control.  This bit sets the priority of the CP1 interrupt.  0: CP1 interrupt set to low priority level.  1: CP1 interrupt set to high priority level.                                                                       |

| 5   | PCP0   | Comparator0 (CP0) Interrupt Priority Control.  This bit sets the priority of the CP0 interrupt.  0: CP0 interrupt set to low priority level.  1: CP0 interrupt set to high priority level.                                                                       |

| 4   | PPCA0  | Programmable Counter Array (PCA0) Interrupt Priority Control.  This bit sets the priority of the PCA0 interrupt.  0: PCA0 interrupt set to low priority level.  1: PCA0 interrupt set to high priority level.                                                    |

| 3   | PADC0  | ADC0 Conversion Complete Interrupt Priority Control.  This bit sets the priority of the ADC0 Conversion Complete interrupt.  0: ADC0 Conversion Complete interrupt set to low priority level.  1: ADC0 Conversion Complete interrupt set to high priority level. |

| 2   | PWADC0 | ADC0 Window Comparator Interrupt Priority Control.  This bit sets the priority of the ADC0 Window interrupt.  0: ADC0 Window interrupt set to low priority level.  1: ADC0 Window interrupt set to high priority level.                                          |

| 1   | PRTC0A | SmaRTClock Alarm Interrupt Priority Control.  This bit sets the priority of the SmaRTClock Alarm interrupt.  0: SmaRTClock Alarm interrupt set to low priority level.  1: SmaRTClock Alarm interrupt set to high priority level.                                 |

| 0   | PSMB0  | SMBus (SMB0) Interrupt Priority Control. This bit sets the priority of the SMB0 interrupt. 0: SMB0 interrupt set to low priority level. 1: SMB0 interrupt set to high priority level.                                                                            |

185

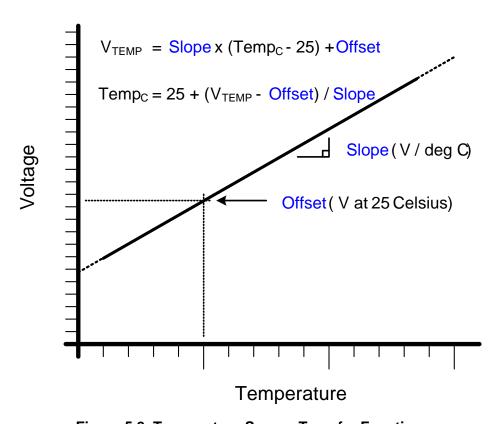

## 18.1. Power-On (VBAT Supply Monitor) Reset

During power-up, the device is held in a reset state and the RST pin is high-impedance with the weak pull-up either on or off until  $V_{BAT}$  settles above  $V_{POR}$ . An additional delay occurs before the device is released from reset; the delay decreases as the  $V_{BAT}$  ramp time increases ( $V_{BAT}$  ramp time is defined as how fast  $V_{BAT}$  ramps from 0 V to  $V_{POR}$ ). Figure 18.3 plots the power-on and  $V_{DD}$  monitor reset timing. For valid ramp times (less than 3 ms), the power-on reset delay ( $T_{PORDelay}$ ) is typically 3 ms ( $V_{BAT} = 0.9 \text{ V}$ ), 7 ms ( $V_{BAT} = 1.8 \text{ V}$ ), or 15 ms ( $V_{BAT} = 3.6 \text{ V}$ ).

**Note:** The maximum  $V_{DD}$  ramp time is 3 ms; slower ramp times may cause the device to be released from reset before  $V_{BAT}$  reaches the  $V_{POR}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The contents of internal data memory should be assumed to be undefined after a power-on reset.

Figure 18.2. Power-Fail Reset Timing Diagram

### SFR Definition 18.2. RSTSRC: Reset Source

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name  | RTC0RE | FERROR | C0RSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R/W    | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | Varies |

SFR Page = 0x0; SFR Address = 0xEF.

| Bit | Name   | Description                                                          | Write                                                                                                                                        | Read                                                                                     |

|-----|--------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 7   | RTC0RE | SmaRTClock Reset Enable and Flag                                     | 0: Disable SmaRTClock as a reset source. 1: Enable SmaRTClock as a reset source.                                                             | Set to 1 if SmaRTClock<br>alarm or oscillator fail<br>caused the last reset.             |

| 6   | FERROR | Flash Error Reset Flag.                                              | N/A                                                                                                                                          | Set to 1 if Flash read/write/erase error caused the last reset.                          |

| 5   | C0RSEF | Comparator0 Reset Enable and Flag.                                   | 0: Disable Comparator0 as a reset source. 1: Enable Comparator0 as a reset source.                                                           | Set to 1 if Comparator0 caused the last reset.                                           |

| 4   | SWRSF  | Software Reset Force and Flag.                                       | Writing a 1 forces a system reset.                                                                                                           | Set to 1 if last reset was caused by a write to SWRSF.                                   |

| 3   | WDTRSF | Watchdog Timer Reset Flag.                                           | N/A                                                                                                                                          | Set to 1 if Watchdog Timer overflow caused the last reset.                               |

| 2   | MCDRSF | Missing Clock Detector (MCD) Enable and Flag.                        | 0: Disable the MCD. 1: Enable the MCD. The MCD triggers a reset if a missing clock condition is detected.                                    | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                  |

| 1   | PORSF  | Power-On / Power-Fail<br>Reset Flag, and Power-Fail<br>Reset Enable. | 0: Disable the VDD/DC+<br>Supply Monitor as a reset<br>source.<br>1: Enable the VDD/DC+<br>Supply Monitor as a reset<br>source. <sup>3</sup> | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs. <sup>2</sup> |

| 0   | PINRSF | HW Pin Reset Flag.                                                   | N/A                                                                                                                                          | Set to 1 if RST pin caused the last reset.                                               |

#### Notes:

- 1. It is safe to use read-modify-write operations (ORL, ANL, etc.) to enable or disable specific interrupt sources.

- 2. If PORSF read back 1, the value read from all other bits in this register are indeterminate.

- 3. Writing a 1 to PORSF before the VDD/DC+ Supply Monitor is stabilized may generate a system reset.

#### 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Registers

The SmaRTClock internal registers can be read and written using RTC0ADR and RTC0DAT. The RTC0ADR register selects the SmaRTClock internal register that will be targeted by subsequent reads or writes. Recommended instruction timing is provided in this section. If the recommended instruction timing is not followed, then BUSY (RTC0ADR.7) should be checked prior to each read or write operation to make sure the SmaRTClock Interface is not busy performing the previous read or write operation. A SmaRTClock Write operation is initiated by writing to the RTC0DAT register. Below is an example of writing to a SmaRTClock internal register.

- 1. Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommended instruction timing.

- 2. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

- 3. Write 0x00 to RTC0DAT. This operation writes 0x00 to the internal RTC0CN register.

A SmaRTClock Read operation is initiated by setting the SmaRTClock Interface Busy bit. This transfers the contents of the internal register selected by RTC0ADR to RTC0DAT. The transferred data will remain in RTC0DAT until the next read or write operation. Below is an example of reading a SmaRTClock internal register.

- Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommended instruction timing.

- 2. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

- 3. Write 1 to BUSY. This initiates the transfer of data from RTC0CN to RTC0DAT.

- 4. Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommend instruction timing.

- 5. Read data from RTC0DAT. This data is a copy of the RTC0CN register.

Note: The RTC0ADR and RTC0DAT registers will retain their state upon a device reset.

#### 20.1.3. RTC0ADR Short Strobe Feature

Reads and writes to indirect SmaRTClock registers normally take 7 system clock cycles. To minimize the indirect register access time, the Short Strobe feature decreases the read and write access time to 6 system clocks. The Short Strobe feature is automatically enabled on reset and can be manually enabled/disabled using the SHORT (RTC0ADR.4) control bit.

Recommended Instruction Timing for a single register read with short strobe enabled:

```

mov RTCOADR, #095h

nop

nop

nop

mov A, RTCODAT

```

Recommended Instruction Timing for a single register write with short strobe enabled:

```

mov RTC0ADR, #095h

mov RTC0DAT, #000h

nop

```

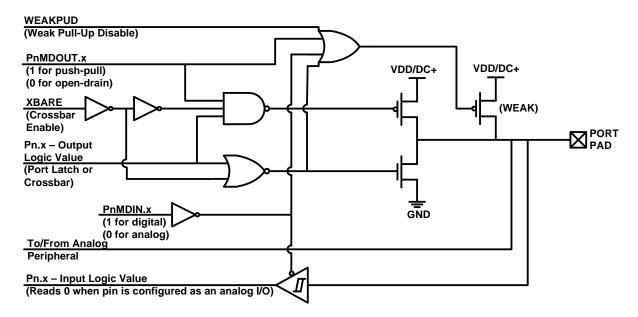

#### 21.1. Port I/O Modes of Operation

Port pins P0.0–P2.6 use the Port I/O cell shown in Figure 21.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a digital high impedance state with weak pull-ups enabled.

#### 21.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, external oscillator input/output, or AGND, VREF, or Current Reference output should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup and digital receiver are disabled. In most cases, software should also disable the digital output drivers. Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 21.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD/DC+ or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD/DC+ supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user must ensure that digital I/O are always internally or externally pulled or driven to a valid logic state. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 21.2. Port I/O Cell Block Diagram

SILICON LAR

#### 21.1.3. Interfacing Port I/O to 5 V and 3.3 V Logic

All Port I/O configured for digital, open-drain operation are capable of interfacing to digital logic operating at a supply voltage higher than 4.5 V and less than 5.25 V. When the supply voltage is in the range of 1.8 to 2.2 V, the I/O may also interface to digital logic operating between 3.0 to 3.6 V if the input signal frequency is less than 12.5 MHz or less than 25 MHz if the signal rise time (10% to 90%) is less than 1.2 ns. When operating at a supply voltage above 2.2 V, the device should not interface to 3.3 V logic; however, interfacing to 5 V logic is permitted. An external pull-up resistor to the higher supply voltage is typically required for most systems.

#### **Important Notes:**

- When interfacing to a signal that is between 4.5 and 5.25 V, the maximum clock frequency that may be input on a GPIO pin is 12.5 MHz. The exception to this rule is when routing an external CMOS clock to P0.3, in which case, a signal up to 25 MHz is valid as long as the rise time (10% to 90%) is shorter than 1.8 ns.

- When the supply voltage is less than 2.2 V and interfacing to a signal that is between 3.0 and 3.6 V, the maximum clock frequency that may be input on a GPIO pin is 3.125 MHz. The exception to this rule is when routing an external CMOS clock to P0.3, in which case, a signal up to 25 MHz is valued as long as the rise time (10% to 90%) is shorter than 1.2 ns.

- In a multi-voltage interface, the external pull-up resistor should be sized to allow a current of at least 150 μA to flow into the Port pin when the supply voltage is between (VDD/DC+ plus 0.4 V) and (VDD/DC+ plus 1.0 V). Once the Port pad voltage increases beyond this range, the current flowing into the Port pin is minimal.

These guidelines only apply to multi-voltage interfaces. Port I/Os may always interface to digital logic operating at the same supply voltage.

#### 21.1.4. Increasing Port I/O Drive Strength

Port I/O output drivers support a high and low drive strength; the default is low drive strength. The drive strength of a Port I/O can be configured using the PnDRV registers. See Section "4. Electrical Characteristics" on page 45 for the difference in output drive strength between the two modes.

#### 21.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P2.6 can be assigned to various analog, digital, and external interrupt functions. The Port pins assuaged to analog functions should be configured for analog I/O and Port pins assuaged to digital or external interrupt functions should be configured for digital I/O.

### 21.2.1. Assigning Port I/O Pins to Analog Functions

Table 21.1 shows all available analog functions that need Port I/O assignments. Port pins selected for these analog functions should have their digital drivers disabled (PnMDOUT.n = 0 and Port Latch = 1) and their corresponding bit in PnSKIP set to 1. This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 21.1 shows the potential mapping of Port I/O to each analog function.

Table 21.1. Port I/O Assignment for Analog Functions

| Analog Function   | Potentially<br>Assignable Port Pins | SFR(s) used for<br>Assignment |  |

|-------------------|-------------------------------------|-------------------------------|--|

| ADC Input         | P0.0-P2.6                           | ADC0MX, PnSKIP                |  |

| Comparator0 Input | P0.0-P2.6                           | CPT0MX, PnSKIP                |  |

#### 21.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital functions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 21.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

Table 21.2. Port I/O Assignment for Digital Functions

| Digital Function                                                                                                           | Potentially Assignable Port Pins                                                                                                                                                                         | SFR(s) used for<br>Assignment |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| UART0, SPI1, SPI0, SMBus,<br>CP0 and CP1 Outputs, Sys-<br>tem Clock Output, PCA0,<br>Timer0 and Timer1 External<br>Inputs. | Any Port pin available for assignment by the Crossbar. This includes P0.0–P2.6 pins which have their PnSKIP bit set to 0.  Note: The Crossbar will always assign UART0 and SPI1 pins to fixed locations. | XBR0, XBR1, XBR2              |

| Any pin used for GPIO                                                                                                      | P0.0-P2.6                                                                                                                                                                                                | POSKIP, P1SKIP,<br>P2SKIP     |

| External Memory Interface                                                                                                  | P1.0–P2.6                                                                                                                                                                                                | P1SKIP, P2SKIP<br>EMI0CF      |

#### 21.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital even capture functions cannot be used on pins configured for analog I/O. Table 21.3 shows all available external digital event capture functions.

Table 21.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function     | Potentially Assignable Port Pins                                                      | SFR(s) used for<br>Assignment  |

|----------------------|---------------------------------------------------------------------------------------|--------------------------------|

| External Interrupt 0 | P0.0-P0.7                                                                             | IT01CF                         |

| External Interrupt 1 | P0.0-P0.7                                                                             | IT01CF                         |

| Port Match           | P0.0–P1.7  Note: On C8051F931/21 devices Port Match is not available on P1.6 or P1.7. | POMASK, POMAT<br>P1MASK, P1MAT |

## SFR Definition 21.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA5

| Bit   | Name                                            | Function                                                                                                                                                                                           |  |  |  |  |  |

|-------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P1DRV[7:0]                                      | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                    |  |  |  |  |  |

|       |                                                 | Configures digital I/O Port cells to high or low output drive strength.  0: Corresponding P1.n Output has low output drive strength.  1: Corresponding P1.n Output has high output drive strength. |  |  |  |  |  |

| Note: | : Pin P1.7 is only available in 32-pin devices. |                                                                                                                                                                                                    |  |  |  |  |  |

### SFR Definition 21.18. P2: Port2

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P2[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = All Pages; SFR Address = 0xA0; Bit-Addressable

| Bit     | Name                                                       | Description                                                                                                               | Write                                                              | Read |  |  |  |  |  |

|---------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|--|--|--|--|--|

| 7:0     | P2[7:0]                                                    | Port 2 Data.  Sets the Port latch logic value or reads the Port pin logic state in Port cells configured for digital I/O. | Set output latch to logic LOW.     Set output latch to logic HIGH. | LOW. |  |  |  |  |  |

| Note: F | Note: Pins P2.0-P2.6 are only available in 32-pin devices. |                                                                                                                           |                                                                    |      |  |  |  |  |  |

Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled (EHACK = 0)

|                                               | Valu             | es l                        | Rea                         | d   |                                                                                                                                                                        |                                                            |      | lues<br>Vrit   |                        | tus<br>ected                   |   |   |

|-----------------------------------------------|------------------|-----------------------------|-----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|----------------|------------------------|--------------------------------|---|---|

| Mode                                          | Status<br>Vector | ACKRQ                       | ARBLOST                     | ACK | Current SMbus State                                                                                                                                                    | Typical Response Options                                   | STA  | STO            | ACK                    | Next Status<br>Vector Expected |   |   |

| ır                                            |                  | 0                           | 0                           | 0   | A slave byte was transmitted; NACK received.                                                                                                                           | No action required (expecting STOP condition).             | 0    | 0              | Х                      | 0001                           |   |   |

| smitte                                        | 0100             | 0                           | 0                           | 1   | A slave byte was transmitted; ACK received.                                                                                                                            | Load SMB0DAT with next data byte to transmit.              | 0    | 0              | Х                      | 0100                           |   |   |

| Slave Transmitter                             |                  | 0                           | 1                           | Х   | A Slave byte was transmitted; error detected.                                                                                                                          | No action required (expecting Master to end transfer).     | 0    | 0              | Х                      | 0001                           |   |   |

| Slav                                          | 0101             | 0                           | Х                           | Х   | An illegal STOP or bus error was detected while a Slave Transmission was in progress.                                                                                  | Clear STO.                                                 | 0    | 0              | Х                      | -                              |   |   |

|                                               |                  |                             |                             |     | A slave address + R/W was received; ACK requested.  If Read, Load SMB0DAT with data byte; ACK received address  NACK received address.  If Write, Acknowledge received | If Write, Acknowledge received address                     | 0    | 0              | 1                      | 0000                           |   |   |

|                                               |                  | 1                           | 0                           | Х   |                                                                                                                                                                        | 0                                                          | 1    | 0100           |                        |                                |   |   |

|                                               | 0010             |                             |                             |     |                                                                                                                                                                        | NACK received address.                                     | 0    | 0              | 0                      | -                              |   |   |

|                                               |                  | 1                           |                             |     |                                                                                                                                                                        | If Write, Acknowledge received address                     | 0    | 0              | 1                      | 0000                           |   |   |

| iver                                          |                  |                             | 1                           | X   | Lost arbitration as master; slave address + R/W received;                                                                                                              | If Read, Load SMB0DAT with data byte; ACK received address | 0    | 0              | 1                      | 0100                           |   |   |

| эээ                                           |                  |                             |                             |     |                                                                                                                                                                        |                                                            |      | ACK requested. | NACK received address. | 0                              | 0 | 0 |

| Slave Receiver                                |                  |                             |                             |     |                                                                                                                                                                        | Reschedule failed transfer;<br>NACK received address.      | 1    | 0              | 0                      | 1110                           |   |   |

| S                                             | 0001             | 0                           | 0                           | х   | A STOP was detected while addressed as a Slave Transmitter or Slave Receiver.                                                                                          | Clear STO.                                                 | 0    | 0              | Х                      | -                              |   |   |

|                                               |                  | 1                           | 1                           | Х   | Lost arbitration while attempting a STOP.                                                                                                                              | No action required (transfer complete/aborted).            | 0    | 0              | 0                      | -                              |   |   |

|                                               | 0000             | 1                           | 0                           | Х   | A slave byte was received;<br>ACK requested.                                                                                                                           | Acknowledge received byte;<br>Read SMB0DAT.                | 0    | 0              | 1                      | 0000                           |   |   |

|                                               |                  |                             |                             |     | ACK requested.                                                                                                                                                         | NACK received byte.                                        | 0    | 0              | 0                      | -                              |   |   |

| on                                            | 0010             | 0                           | 1                           | Х   | Lost arbitration while attempt-                                                                                                                                        | Abort failed transfer.                                     | 0    | 0              | Х                      | -                              |   |   |

| Error Condition                               | 0010             |                             |                             |     | ing a repeated START.                                                                                                                                                  | Reschedule failed transfer.                                | 1    | 0              | Χ                      | 1110                           |   |   |

| Co                                            | 0001             | 0                           | 1                           | Х   | Lost arbitration due to a                                                                                                                                              | Abort failed transfer.                                     | 0    | 0              | Х                      | -                              |   |   |

| rror                                          |                  |                             |                             |     | detected STOP.                                                                                                                                                         | Reschedule failed transfer.                                | 1    | 0              | Χ                      | 1110                           |   |   |

| sr<br>E                                       | 0000             | 1                           | 1                           | Х   | Lost arbitration while transmit-                                                                                                                                       | Abort failed transfer.                                     | 0    | 0              | 0                      | -                              |   |   |

| 9 0000 1 1 X Lost arbitration ting a data byt |                  | ting a data byte as master. | Reschedule failed transfer. | 1   | 0                                                                                                                                                                      | 0                                                          | 1110 |                |                        |                                |   |   |

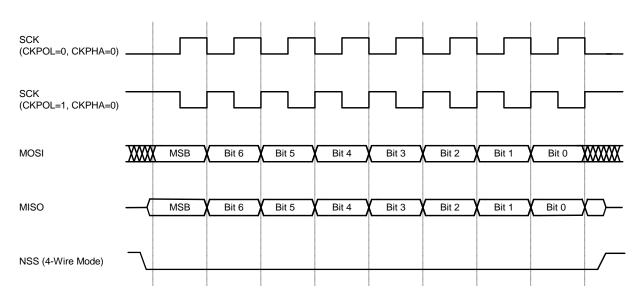

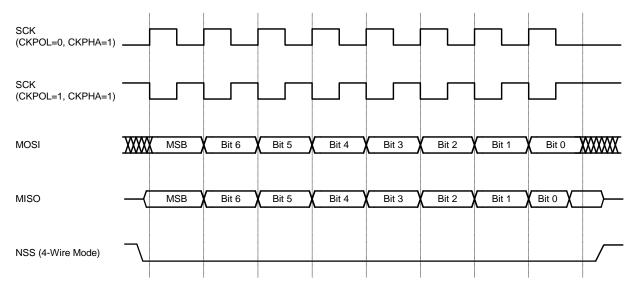

#### 24.2. SPI Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPIn is placed in master mode by setting the Master Enable flag (MSTENn, SPInCN.6). Writing a byte of data to the SPIn data register (SPInDAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPIn master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIFn (SPInCN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPIn master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPInDAT.

When configured as a master, SPIn can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPIn when another master is accessing the bus. When NSS is pulled low in this mode, MSTENn (SPInCN.6) and SPIENn (SPInCN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODFn, SPInCN.5 = 1). Mode Fault will generate an interrupt if enabled. SPIn must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSnMD1 (SPInCN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSnMD0 (SPInCN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 24.6. Slave Mode Data/Clock Timing (CKPHA = 0)

Figure 24.7. Slave Mode Data/Clock Timing (CKPHA = 1)

## 24.6. SPI Special Function Registers

SPI0 and SPI1 are accessed and controlled through four special function registers (8 registers total) in the system controller: SPInCN Control Register, SPInDAT Data Register, SPInCFG Configuration Register, and SPInCKR Clock Rate Register. The special function registers related to the operation of the SPI0 and SPI1 Bus are described in the following figures.

# SFR Definition 25.16. TMR3L: Timer 3 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | TMR3L[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

## SFR Page = 0x0; SFR Address = 0x94

| Bit | Name       | Function                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                             |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

## SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR3H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### SFR Page = 0x0; SFR Address = 0x95

| Bi  | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |

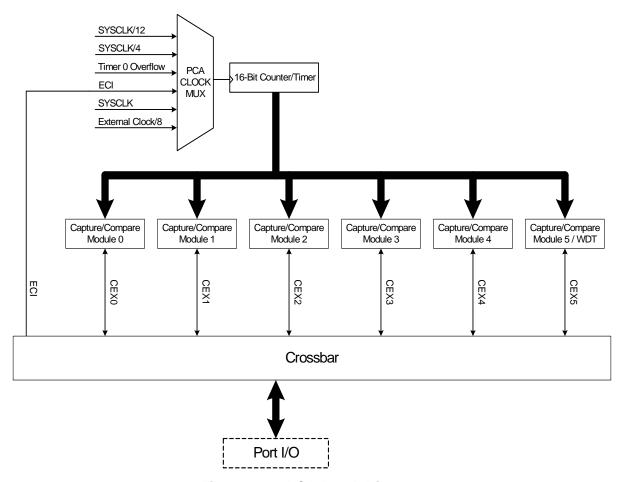

## 26. Programmable Counter Array

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 308). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. **Access to certain PCA registers is restricted while WDT mode is enabled**. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram

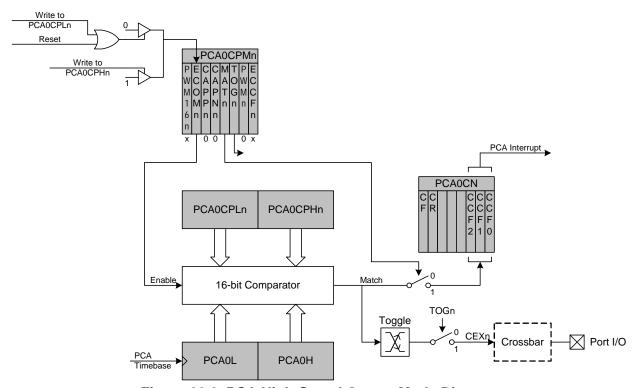

#### 26.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 26.6. PCA High-Speed Output Mode Diagram

## SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte

| Bit   | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|-----------|-----|-----|-----|-----|-----|-----|--|

| Name  |     | PCA0[7:0] |     |     |     |     |     |     |  |

| Туре  | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xF9

| Е | 3it | Name      | Function                                                                     |

|---|-----|-----------|------------------------------------------------------------------------------|

| 7 | ':0 | PCA0[7:0] | PCA Counter/Timer Low Byte.                                                  |

|   |     |           | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |

**Note:** When the WDTE bit is set to 1, the PCA0L register cannot be modified by software. To change the contents of the PCA0L register, the Watchdog Timer must first be disabled.

## SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xFA

| Bit | Name       | Function                                                                                                                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PCA0[15:8] | PCA Counter/Timer High Byte.                                                                                                                                                                                                                  |

|     |            | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer. Reads of this register will read the contents of a "snapshot" register, whose contents are updated only when the contents of PCA0L are read (see Section 26.1). |

**Note:** When the WDTE bit is set to 1, the PCA0H register cannot be modified by software. To change the contents of the PCA0H register, the Watchdog Timer must first be disabled.