Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k40-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>REGISTER 3</b>                 | -13: R      | EVISIO          | N ID: REVI       | SION ID RE | GISTER          |         |          |       |

|-----------------------------------|-------------|-----------------|------------------|------------|-----------------|---------|----------|-------|

| R                                 | F           | R               | R                | R          | R               | R       | R        | R     |

| 1                                 | 0           | )               | 1                | 0          |                 | MJR     | REV<5:2> |       |

| bit 15                            |             |                 |                  |            | ·               |         |          | bit 8 |

|                                   |             |                 |                  |            |                 |         |          |       |

| R                                 | F           | 2               | R                | R          | R               | R       | R        | R     |

| MJRR                              | MJRREV<1:0> |                 |                  |            | MNRRI           | EV<5:0> |          |       |

| bit 7                             |             |                 |                  |            |                 |         |          | bit 0 |

| Legend:                           |             |                 |                  |            |                 |         |          |       |

| R = Readable bit '1' = Bit is set |             | t               | 0' = Bit is clea | ared       | x = Bit is unkr | nown    |          |       |

| bit 15-12                         | Read a      | <b>s</b> '1010' |                  |            |                 |         |          |       |

bit 10 12

These bits are fixed with value '1010' for all devices in this family.

bit 11-6

MJRREV<5:0>: Major Revision ID bits

These bits are used to identify a major revision. A major revision is indicated by an all-layer revision (A0, B0, C0, etc.).

Revision A = 6 'b00\_0000

bit 5-0

MNRREV<5:0>: Minor Revision ID bits

bit 5-0 **MNRREV<5:0>:** Minor Revision ID bits These bits are used to identify a minor revision.

# PIC18(L)F24/25K40

| U-0                                     | U-0                 | R/W-0/0                                                                | R/W-0/0 | R/W-0/0                            | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |

|-----------------------------------------|---------------------|------------------------------------------------------------------------|---------|------------------------------------|------------------|----------------|--------------|--|--|--|

| _                                       | —                   |                                                                        |         | HFTU                               | N<5:0>           |                |              |  |  |  |

| bit 7                                   |                     |                                                                        |         |                                    |                  |                | bit C        |  |  |  |

| Legend:                                 |                     |                                                                        |         |                                    |                  |                |              |  |  |  |

| R = Readab                              | ole bit             | W = Writable                                                           | bit     | U = Unimplemented bit, read as '0' |                  |                |              |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                     |                                                                        | nown    | -n/n = Value a                     | at POR and BC    | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |                     |                                                                        | ared    |                                    |                  |                |              |  |  |  |

| bit 5-0                                 | 01 1111 =<br>•<br>• | >: HFINTOSC F<br>Maximum freque<br>Center frequenc<br>(default value). | ency    | -                                  | g at the calibra | ted frequency  |              |  |  |  |

| U-0                                   | R/W-0/0                       | R/W-0/0                    | U-0          | U-0                                                   | R/W-0/0          | R/W-0/0  | R/W-0/0              |  |  |  |  |

|---------------------------------------|-------------------------------|----------------------------|--------------|-------------------------------------------------------|------------------|----------|----------------------|--|--|--|--|

| _                                     | DACMD                         | ADCMD                      | _            | _                                                     | CMP2MD           | CMP1MD   | ZCDMD <sup>(1)</sup> |  |  |  |  |

| bit 7                                 | •                             |                            |              |                                                       |                  |          | bit 0                |  |  |  |  |

|                                       |                               |                            |              |                                                       |                  |          |                      |  |  |  |  |

| Legend:                               |                               |                            |              |                                                       |                  |          |                      |  |  |  |  |

| R = Reada                             | ble bit                       | W = Writable I             | oit          | U = Unimplen                                          | nented bit, read | 1 as '0' |                      |  |  |  |  |

| u = Bit is u                          | nchanged                      | x = Bit is unkn            | own          | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |                      |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |                               |                            | ared         | q = Value dep                                         | ends on condit   | tion     |                      |  |  |  |  |

|                                       |                               |                            |              |                                                       |                  |          |                      |  |  |  |  |

| bit 7                                 | Unimplemer                    | Unimplemented: Read as '0' |              |                                                       |                  |          |                      |  |  |  |  |

| bit 6                                 | DACMD: Dis                    | able DAC bit               |              |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | dule disabled              |              |                                                       |                  |          |                      |  |  |  |  |

|                                       | 0 = DAC mo                    | dule enabled               |              |                                                       |                  |          |                      |  |  |  |  |

| bit 5                                 | ADCMD: Dis                    | able ADC bit               |              |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | dule disabled              |              |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | dule enabled               |              |                                                       |                  |          |                      |  |  |  |  |

| bit 4-3                               | Unimplemer                    | nted: Read as '0           | )'           |                                                       |                  |          |                      |  |  |  |  |

| bit 2                                 | CMP2MD: D                     | isable Compara             | tor CMP2 bit |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | nodule disabled            |              |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | nodule enabled             |              |                                                       |                  |          |                      |  |  |  |  |

| bit 1                                 | CMP1MD: D                     | isable Compara             | tor CMP1 bit |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | nodule disabled            |              |                                                       |                  |          |                      |  |  |  |  |

|                                       |                               | nodule enabled             |              |                                                       |                  |          |                      |  |  |  |  |

| bit 0                                 | ZCDMD: Dis                    | able Zero-Cross            | Detect modu  | le bit <sup>(1)</sup>                                 |                  |          |                      |  |  |  |  |

|                                       | 1 = ZCD mod                   | dule disabled              |              |                                                       |                  |          |                      |  |  |  |  |

|                                       | 0 = ZCD mod                   | dule enabled               |              |                                                       |                  |          |                      |  |  |  |  |

| Note 1                                | Subject to $\overline{7CD}$ h |                            | J            |                                                       |                  |          |                      |  |  |  |  |

#### REGISTER 7-3: PMD2: PMD CONTROL REGISTER 2

**Note 1:** Subject to ZCD bit in CONFIG2H.

| Address | Name      | Bit 7  | Bit 6                                    | Bit 5      | Bit 4   | Bit 3    | Bit 2      | Bit 1      | Bit 0    | <u>Value on</u><br>POR, BOR |  |

|---------|-----------|--------|------------------------------------------|------------|---------|----------|------------|------------|----------|-----------------------------|--|

| F74h    | CRCDATL   |        | ·                                        | -          | DATA    | A<7:0>   |            | •          | •        | xxxxxxx                     |  |

| F73h    | ADFLTRH   |        |                                          |            | ADFLTF  | RH<15:8> |            |            |          | xxxxxxxx                    |  |

| F72h    | ADFLTRL   |        |                                          |            | ADFLT   | RL<7:0>  |            |            |          | xxxxxxx                     |  |

| F71h    | ADACCH    |        |                                          |            | ADACC   | H<15:8>  |            |            |          | xxxxxxxx                    |  |

| F70h    | ADACCL    |        |                                          |            | ADAC    | CL<7:0>  |            |            |          | xxxxxxxx                    |  |

| F6Fh    | ADERRH    |        |                                          |            | ADERF   | RH<15:8> |            |            |          | 00000000                    |  |

| F6Eh    | ADERRL    |        |                                          |            | ADER    | RL<7:0>  |            |            |          | 00000000                    |  |

| F6Dh    | ADUTHH    |        |                                          |            | ADUTH   | IH<15:8> |            |            |          | 00000000                    |  |

| F6Ch    | ADUTHL    |        |                                          |            | ADUT    | HL<7:0>  |            |            |          | 00000000                    |  |

| F6Bh    | ADLTHH    |        |                                          |            | ADLTH   | H<15:8>  |            |            |          | 00000000                    |  |

| F6Ah    | ADLTHL    |        |                                          |            | ADLTH   | HL<7:0>  |            |            |          | 00000000                    |  |

| F69h    | ADSTPTH   |        |                                          |            | ADSTP   | TH<15:8> |            |            |          | 00000000                    |  |

| F68h    | ADSTPTL   |        |                                          |            | ADSTF   | PTL<7:0> |            |            |          | 00000000                    |  |

| F67h    | ADCNT     |        | ADCNT<7:0>                               |            |         |          |            |            |          |                             |  |

| F66h    | ADRPT     |        | ADRPT<7:0>                               |            |         |          |            |            |          |                             |  |

| F65h    | ADSTAT    | ADAOV  | ADAOV ADUTHR ADLTHR ADMATH - ADSTAT<2:0> |            |         |          |            |            |          |                             |  |

| F64h    | ADRESH    |        |                                          |            | ADRE    | SH<7:0>  |            |            |          | 00000000                    |  |

| F63h    | ADRESL    |        |                                          |            | ADRE    | SL<7:0>  |            |            |          | 00000000                    |  |

| F62h    | ADPREVH   |        |                                          |            | ADPRE   | VH<15:8> |            |            |          | 00000000                    |  |

| F61h    | ADPREVL   |        |                                          |            | ADPRE   | VL<7:0>  |            |            |          | 00000000                    |  |

| F60h    | ADCON0    | ADON   | ADCONT                                   | —          | ADSC    | —        | ADFM       | —          | ADGO     | 00-000-0                    |  |

| F5Fh    | ADPCH     | —      | _                                        |            |         | ADPO     | CH<5:0>    |            |          | 000000                      |  |

| F5Eh    | ADPRE     |        | •                                        |            | ADPR    | E<7:0>   |            |            |          | 00000000                    |  |

| F5Dh    | ADCAP     | —      | _                                        | _          |         |          | ADCAP<4:0> |            |          | 00000                       |  |

| F5Ch    | ADACQ     |        |                                          |            | ADAC    | Q<7:0>   |            |            |          | 00000000                    |  |

| F5Bh    | ADCON3    | —      |                                          | ADCALC<2:0 | >       | ADSOI    |            | ADTMD<2:0> | >        | -0000000                    |  |

| F5Ah    | ADCON2    | ADPSIS |                                          | ADCRS<2:0> | >       | ADACLR   |            | ADMD<2:0>  |          | 00000000                    |  |

| F59h    | ADCON1    | ADPPOL | ADIPEN                                   | ADGPOL     | _       | —        | _          | —          | ADDSEN   | 0000                        |  |

| F58h    | ADREF     | —      | _                                        | _          | ADNREF  | —        | _          | ADPF       | REF<1:0> | 0-00                        |  |

| F57h    | ADCLK     | _      | _                                        |            |         | ADC      | S<5:0>     |            |          | 000000                      |  |

| F56h    | ADACT     | —      | _                                        | -          |         |          | ADACT<4:0> |            |          | 00000                       |  |

| F55h    | MDCARH    | —      | -                                        | -          | —       | —        |            | CHS<2:0>   |          | 000                         |  |

| F54h    | MDCARL    | —      | -                                        | -          | —       | —        |            | CLS<2:0>   |          | 000                         |  |

| F53h    | MDSRC     | —      | -                                        | -          | —       |          | SRCS       | 8<3:0>     |          | 0000                        |  |

| F52h    | MDCON1    | _      | —                                        | CHPOL      | CHSYNC  |          | _          | CLPOL      | CLSYNC   | 0000                        |  |

| F51h    | MDCON0    | EN     | —                                        | Ουτ        | OPOL    | —        | —          | —          | MDBIT    | 0-000                       |  |

| F50h    | SCANTRIG  | _      | —                                        | -          | _       |          | TSEL       | .<3:0>     |          | 0000                        |  |

| F4Fh    | SCANCON0  | SCANEN | SCANGO                                   | BUSY       | INVALID | INTM     | _          | MOD        | E<1:0>   | 00000-00                    |  |

| F4Eh    | SCANHADRU | —      | _                                        |            |         | HADF     | R<21:16>   |            |          | 111111                      |  |

# TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

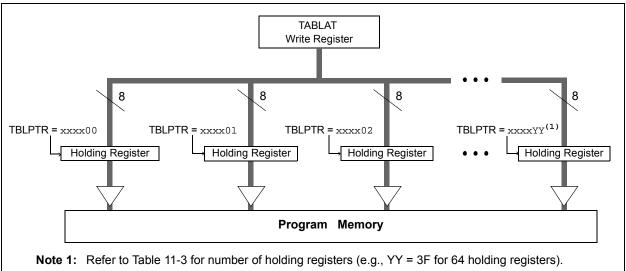

# 11.1.6.1 Program Flash Memory Write Sequence

The sequence of events for programming an internal program memory location should be:

- 1. Read appropriate number of bytes into RAM. Refer to Table 11-2 for Write latch size.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- Write the n-byte block into the holding registers with auto-increment. Refer to Table 11-2 for Write latch size.

- 7. Set NVMREG<1:0> bits to point to program memory.

- 8. Clear FREE bit and set WREN bit in NVMCON1 register.

- 9. Disable interrupts.

- 10. Execute the unlock sequence (see Section 11.1.4 "NVM Unlock Sequence").

- 11. WR bit is set in NVMCON1 register.

- 12. The CPU will stall for the duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 11-4.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

# 12.0 8x8 HARDWARE MULTIPLIER

#### 12.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 12-1.

#### 12.2 Operation

Example 12-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 12-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 12-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

# EXAMPLE 12-2: 8x8 SIGNED MULTIPLY

|       |          | 1. | JOHNE          |

|-------|----------|----|----------------|

| MOVF  | ARG1, W  |    |                |

| MULWF | ARG2     | ;  | ARG1 * ARG2 -> |

|       |          | ;  | PRODH:PRODL    |

| BTFSC | ARG2, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG1         |

| MOVF  | ARG2, W  |    |                |

| BTFSC | ARG1, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG2         |

|       |          |    |                |

|                |                           | Program           | Cycles |          | Tir      | ne       |               |

|----------------|---------------------------|-------------------|--------|----------|----------|----------|---------------|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz       |

| 8x8 unsigned   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μ <b>s</b> |

|                | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs          |

| 9v9 signad     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs         |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μ <b>s</b>  |

| 16v16 uppigpod | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs        |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs         |

| 16x16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs        |

| 16x16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs         |

#### TABLE 12-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

# 14.0 INTERRUPTS

The PIC18(L)F2x/4xK40 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high or low priority level. The high priority interrupt vector is at 0008h and the low priority interrupt vector is at 0018h. A high priority interrupt event will interrupt a low priority interrupt that may be in progress.

The registers for controlling interrupt operation are:

- INTCON

- PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, PIR7

- PIE1, PIE2, PIE3, PIE4, PIE5, PIE6, PIE7

- IPR1, IPR2, IPR3, IPR4, IPR5, IPR6, IPR7

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

## 14.1 Mid-Range Compatibility

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> microcontroller mid-range devices. In Compatibility mode, the interrupt priority bits of the IPRx registers have no effect. The PEIE/GIEL bit of the INTCON register is the global interrupt enable for the peripherals. The PEIE/GIEL bit disables only the peripheral interrupt sources and enables the peripheral interrupt sources when the GIE/GIEH bit is also set. The GIE/GIEH bit of the INTCON register is the global interrupt enable which enables all non-peripheral interrupt sources and disables all interrupt sources, including the peripherals. All interrupts branch to address 0008h in Compatibility mode.

#### 14.2 Interrupt Priority

The interrupt priority feature is enabled by setting the IPEN bit of the INTCON register. When interrupt priority is enabled the GIE/GIEH and PEIE/GIEL Global Interrupt Enable bits of Compatibility mode are replaced by the GIEH high priority, and GIEL low priority, global interrupt enables. When the IPEN bit is set, the GEIH bit of the INTCON register enables all interrupts which have their associated bit in the IPRx register set. When the GEIH bit is cleared, then all interrupt sources including those selected as low priority in the IPRx register are disabled.

When both GIEH and GIEL bits are set, all interrupts selected as low priority sources are enabled.

A high priority interrupt will vector immediately to address 00 0008h and a low priority interrupt will vector to address 00 0018h.

#### 14.3 Interrupt Response

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. The GIE/GIEH bit is the Global Interrupt Enable when the IPEN bit is cleared. When the IPEN bit is set, enabling interrupt priority levels, the GIEH bit is the high priority Global Interrupt Enable and the GIEL bit is the low priority Global Interrupt Enable. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits in the INTCONx and PIRx registers. The interrupt flag bits must be cleared by software before re-enabling interrupts to avoid repeating the same interrupt.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE/GIEH bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the Interrupt-on-change pins, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one-cycle or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bits or the Global Interrupt Enable bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

# 14.8 Register Definitions: Interrupt Control

| R/W-0/0               | R/W-0/0                                                                                              | R/W-0/0                                                                                           | U-0                                                 | U-0                                      | R/W-1/1          | R/W-1/1           | R/W-1/1       |

|-----------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------|------------------|-------------------|---------------|

| GIE/GIEH              | PEIE/GIEL                                                                                            | IPEN                                                                                              | _                                                   | -                                        | INT2EDG          | INT1EDG           | INT0EDG       |

| bit 7                 |                                                                                                      |                                                                                                   |                                                     | <b>I</b>                                 |                  | I                 | bit (         |

|                       |                                                                                                      |                                                                                                   |                                                     |                                          |                  |                   |               |

| Legend:               |                                                                                                      |                                                                                                   |                                                     |                                          |                  |                   |               |

| R = Readable          | e bit                                                                                                | W = Writable                                                                                      | bit                                                 | U = Unimple                              | mented bit, read | 1 as '0'          |               |

| -n = Value at         | POR                                                                                                  | '1' = Bit is set                                                                                  |                                                     | '0' = Bit is cle                         | eared            | x = Bit is unki   | nown          |

| bit 7                 | <u>If IPEN = 1</u> :<br>1 = En<br>0 = Dis                                                            | lobal Interrupt I<br>ables all unma<br>sables all interr                                          | sked interrup                                       | ts and cleared                           | by hardware for  | high-priority in  | terrupts only |

|                       |                                                                                                      | ables all unmas<br>ables all interru                                                              |                                                     | ts and cleared                           | by hardware for  | all interrupts    |               |

| bit 6                 | <u>If IPEN = 1</u> :<br>1 = En<br>0 = Dis<br><u>If IPEN = 0</u> :<br>1 = En                          | Peripheral Intern<br>ables all low-pr<br>sables all low-p<br>ables all unmas<br>sables all peripl | iority interrup<br>riority interrup<br>sked periphe | ots and cleared<br>ots<br>ral interrupts | by hardware fo   | r low-priority in | terrupts only |

| bit 5                 | 1 = Enable                                                                                           | pt Priority Enab<br>priority levels o<br>priority levels o                                        | n interrupts                                        |                                          |                  |                   |               |

| bit 4-3               | Unimplemen                                                                                           | ted: Read as 'd                                                                                   | )'                                                  |                                          |                  |                   |               |

| bit 2                 | 1 = Interrup                                                                                         | tternal Interrup<br>t on rising edge<br>t on falling edge                                         | e of INT2 pin                                       | ect bit                                  |                  |                   |               |

| bit 1                 | 1 = Interrup                                                                                         | tternal Interrupt<br>t on rising edge<br>t on falling edge                                        | e of INT1 pin                                       |                                          |                  |                   |               |

| bit 0                 | 1 = Interrup                                                                                         | tternal Interrup<br>t on rising edge<br>t on falling edge                                         | e of INT0 pin                                       |                                          |                  |                   |               |

| cc<br>its<br>er<br>th | terrupt flag bits a<br>ondition occurs, r<br>corresponding<br>nable bit. User s<br>e appropriate int | egardless of the<br>enable bit or the<br>software should<br>errupt flag bits                      | e state of<br>ne global<br>d ensure<br>are clear    |                                          |                  |                   |               |

prior to enabling an interrupt. This feature

allows for software polling.

## **15.4 Register Definitions: Port Control**

| R/W-x/u                        | R/W-x/u | R/W-x/u                           | R/W-x/u | R/W-x/u                         | R/W-x/u          | R/W-x/u  | R/W-x/u |

|--------------------------------|---------|-----------------------------------|---------|---------------------------------|------------------|----------|---------|

| Rx7                            | Rx6     | Rx5                               | Rx4     | Rx3                             | Rx2              | Rx1      | Rx0     |

| bit 7                          | •       |                                   |         | •                               |                  |          | bit     |

| Legend:                        |         |                                   |         |                                 |                  |          |         |

| <b>Legend:</b><br>R = Readable | bit     | W = Writable                      | bit     | U = Unimplen                    | nented bit, read | d as '0' |         |

| •                              | bit     | W = Writable<br>'0' = Bit is clea |         | U = Unimplen<br>x = Bit is unkr | ,                | d as '0' |         |

bit 7-0 **Rx<7:0>:** Rx7:Rx0 Port I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

#### TABLE 15-2: PORT REGISTERS

| Name  | Bit 7              | Bit 6              | Bit 5 | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

|-------|--------------------|--------------------|-------|-------|--------------------|-------|-------|-------|

| PORTA | RA7                | RA6                | RA5   | RA4   | RA3                | RA2   | RA1   | RA0   |

| PORTB | RB7 <sup>(1)</sup> | RB6 <sup>(1)</sup> | RB5   | RB4   | RB3                | RB2   | RB1   | RB0   |

| PORTC | RC7                | RC6                | RC5   | RC4   | RC3                | RC2   | RC1   | RC0   |

| PORTE | _                  | _                  | _     | _     | RE3 <sup>(2)</sup> |       | _     | —     |

**Note 1:** Bits RB6 and RB7 read '1' while in Debug mode.

2: Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled).

#### 21.5.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the FMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Select the timer clock source to be as FOSC/4 using the TxCLKCON register. This is required for correct operation of the PWM module.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 21.5.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

#### 21.5.4 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 21-1.

#### EQUATION 21-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

Note: The Timer postscaler (see Section 20.4 "Timer2 Interrupt") is not used in the determination of the PWM frequency.

| U-0                                    | U-0                                    | R-x               | U-0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------------------------------|----------------------------------------|-------------------|-----------|----------------|------------------|------------------|--------------|

|                                        |                                        | IN                |           | POLD           | POLC             | POLB             | POLA         |

| bit 7                                  |                                        |                   |           |                |                  |                  | bit 0        |

| Legend:                                |                                        |                   |           |                |                  |                  |              |

| R = Readable                           | e bit                                  | W = Writable      | bit       | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is uncl                        | hanged                                 | x = Bit is unkr   | nown      | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set                       |                                        | '0' = Bit is clea | ared      | q = Value de   | pends on condit  | ion              |              |

|                                        |                                        |                   |           |                |                  |                  |              |

| bit 7-6                                | •                                      | ted: Read as '    |           |                |                  |                  |              |

| bit 5                                  | IN: CWG Inp                            | ut Value bit (rea | ad-only)  |                |                  |                  |              |

| bit 4                                  | Unimplemen                             | ted: Read as '    | 0'        |                |                  |                  |              |

| bit 3                                  | POLD: CWG                              | 1D Output Pola    | arity bit |                |                  |                  |              |

|                                        | •                                      | tput is inverted  |           |                |                  |                  |              |

|                                        | 0 = Signal ou                          | tput is normal p  | olarity   |                |                  |                  |              |

| bit 2                                  |                                        | 1C Output Pola    | •         |                |                  |                  |              |

|                                        | •                                      | tput is inverted  |           |                |                  |                  |              |

|                                        | 0 = Signal output is normal polarity   |                   |           |                |                  |                  |              |

| bit 1                                  | POLB: CWG1B Output Polarity bit        |                   |           |                |                  |                  |              |

|                                        | 1 = Signal output is inverted polarity |                   |           |                |                  |                  |              |

|                                        | 0 = Signal output is normal polarity   |                   |           |                |                  |                  |              |

| bit 0                                  |                                        |                   |           |                |                  |                  |              |

| 1 = Signal output is inverted polarity |                                        |                   |           |                |                  |                  |              |

|                                        | 0 = Signal output is normal polarity   |                   |           |                |                  |                  |              |

#### REGISTER 24-2: CWG1CON1: CWG CONTROL REGISTER 1

# 25.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- Programmable Modulator Data

- · Modulated Output Polarity Select

- Peripheral Module Disable, which provides the ability to place the DSM module in the lowest power consumption mode

Figure 25-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

| <br>98<br>Caraceusi                              | ×                |                      |                            |                                                     |                                       |                     |                                           |                       |                   |                                        |                                        |

|--------------------------------------------------|------------------|----------------------|----------------------------|-----------------------------------------------------|---------------------------------------|---------------------|-------------------------------------------|-----------------------|-------------------|----------------------------------------|----------------------------------------|

|                                                  | ·<br>·<br>·      |                      |                            |                                                     |                                       |                     |                                           |                       |                   |                                        | :                                      |

| CKE = 0)<br>SCK<br>(CKF = 1<br>CKE = 0)          | :<br>            |                      |                            |                                                     | · · · · · · · · · · · · · · · · · · · |                     |                                           |                       | 5<br>5<br>5       |                                        | ······································ |

| - 2488 (* 27)<br>99088830<br>9386236926<br>14388 | ;<br>;<br>;<br>; |                      | 2<br>2<br>2<br>2<br>2<br>2 | 2<br>2<br>2<br>2<br>2<br>2                          | 2<br>2<br>3<br>3                      |                     | generation<br>2<br>2<br>2<br>2<br>2       | 5<br>6<br>6<br>5<br>5 | <pre></pre>       | <<br>:<br>:<br>:                       | • • • • • •                            |

| - 39240                                          |                  |                      |                            | X 88 8                                              | X 333 4.<br>,                         | X 88.3              | X 33.2                                    | X 223 3               | X                 | :<br>                                  | ····t <sub>y</sub>                     |

| 909                                              | ·<br>·<br>·<br>: |                      | ;<br>,                     | ;<br>aad <i>                                   </i> | ,<br>,                                | ;<br>,ac.////////// | ;<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                       |                   | ////////////////////////////////////// | :                                      |

| inguit<br>Sampia                                 | 5<br>            | , (10.<br>. (10.<br> | ;<br>;<br>;<br>;<br>;      | . //.<br>                                           | . 49<br>                              | . //p<br>. //p      | , <i>1</i> 9.<br>                         | . <i>4</i> 4-         |                   |                                        |                                        |

| SSPXP<br>Interrupt<br>Plag                       | :<br>:<br>:      | ·<br>·<br>·          |                            |                                                     |                                       |                     | -<br>                                     | -<br>                 | <pre></pre>       | ·<br>·<br>·                            |                                        |

| 932933 85<br>352733327                           | ·<br>·<br>·<br>· | ·<br>·<br>·<br>·     | *<br>2<br>2<br>2           | ,<br>5<br>,<br>,                                    | s<br>s<br>s<br>s                      |                     | *<br>2<br>2<br>2<br>2                     | -<br>5<br>5<br>       | 5 5<br>5 5<br>5 5 | ,<br>//p.                              |                                        |

| Valle Culleur<br>detection active                |                  |                      |                            |                                                     | *****                                 |                     |                                           |                       | ******            |                                        |                                        |

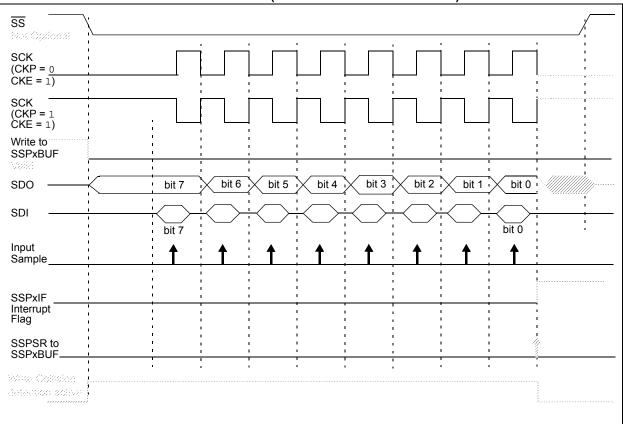

#### FIGURE 26-8: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

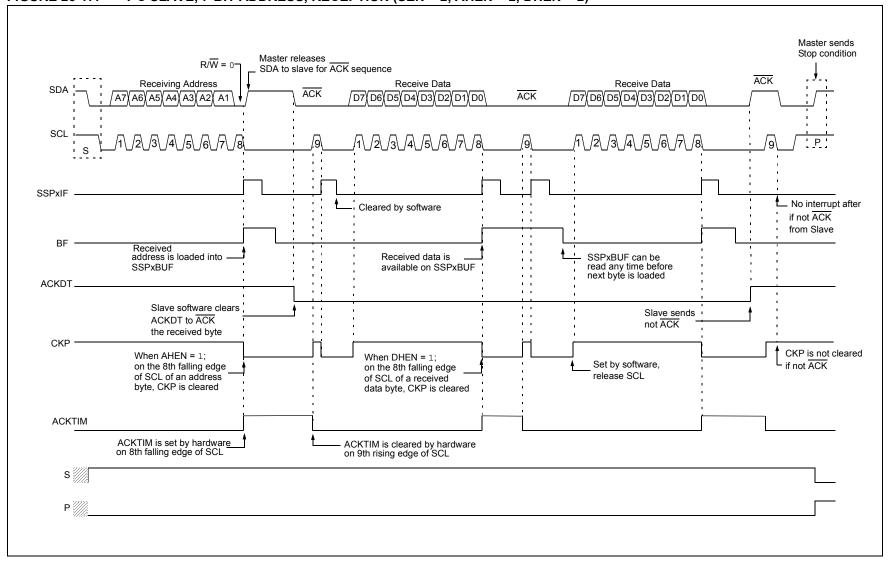

## FIGURE 26-17: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 1, DHEN = 1)

PIC18(L)F24/25K40

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

#### 26.10.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

#### 26.10.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

The WCOL bit must be cleared by software before the next transmission.

## 26.10.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

26.10.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

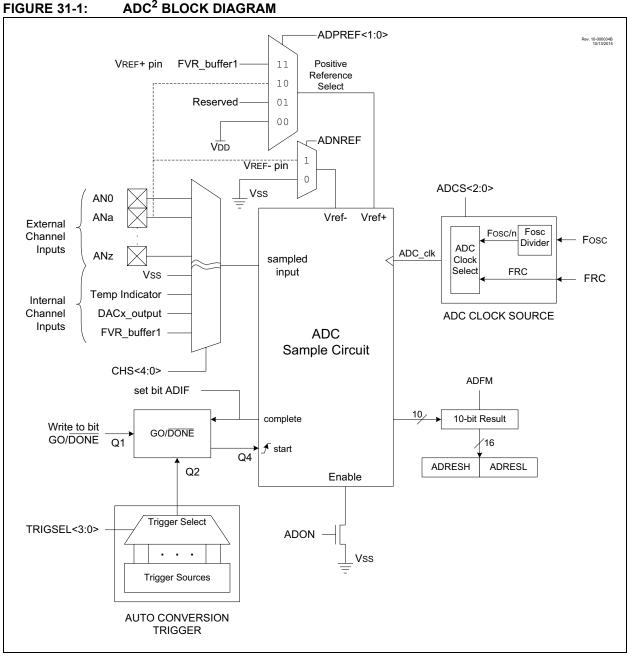

ADC<sup>2</sup> BLOCK DIAGRAM

| U-0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W/HC-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|-------------|---------|----------|---------|------------|---------|

| -       |         | ADCALC<2:0> |         | ADSOI    |         | ADTMD<2:0> |         |

| bit 7   |         |             |         |          |         |            | bit 0   |

|         |         |             |         |          |         |            |         |

| Legend: |         |             |         |          |         |            |         |

| J. J |                      |                                                       |

|------------------------------------------|----------------------|-------------------------------------------------------|

| R = Readable bit                         | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged                     | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                         | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 ADCALC<2:0>: ADC Error Calculation Mode Select bits

|        | Action During                    | 1st Precharge Stage                                 |                                                              |

|--------|----------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| ADCALC | ADDSEN = 0<br>Single-Sample Mode | ADDSEN = 1 CVD<br>Double-Sample Mode <sup>(1)</sup> | Application                                                  |

| 111    | Reserved                         | Reserved                                            | Reserved                                                     |

| 110    | Reserved                         | Reserved                                            | Reserved                                                     |

| 101    | ADLFTR-ADSTPT ADFLTR-ADSTPT      |                                                     | Average/filtered value vs. setpoint                          |

| 100    | ADPREV-ADFLTR                    | ADPREV-ADFLTR                                       | First derivative of filtered value <sup>(3)</sup> (negative) |

| 011    | Reserved                         | Reserved                                            | Reserved                                                     |

| 010    | ADRES-ADFLTR                     | (ADRES-ADPREV)-ADFLTR                               | Actual result vs.<br>averaged/filtered value                 |

| 001    | ADRES-ADSTPT                     | (ADRES-ADPREV)-ADSTPT                               | Actual result vs.setpoint                                    |

| 000    | ADRES-ADPREV                     | ADRES-ADPREV                                        | First derivative of single measurement <sup>(2)</sup>        |

|        |                                  |                                                     | Actual CVD result in CVD mode <sup>(2)</sup>                 |

bit 3 ADSOI: ADC Stop-on-Interrupt bit

#### If ADCONT = 1:

- 1 = ADGO is cleared when the threshold conditions are met, otherwise the conversion is retriggered

- 0 = ADGO is not cleared by hardware, must be cleared by software to stop retriggers

#### bit 2-0 ADTMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ADERR>ADUTH

- 101 = Interrupt if ADERR≤ADUTH

- 100 = Interrupt if ADERR<ADLTH or ADERR>ADUTH

- 011 = Interrupt if ADERR>ADLTH and ADERR<ADUTH

- 010 = Interrupt if ADERR≥ADLTH

- 001 = Interrupt if ADERR<ADLTH

- 000 = Never interrupt

- Note 1: When ADPSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Table 31-3.

- 2: When ADPSIS = 0

- 3: When ADPSIS = 1.

-n/n = Value at POR and BOR/Value at all other Resets

#### REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x          | R-x              | R-x    | R-x   |

|------------------|-----|------------------|------|--------------|------------------|--------|-------|

|                  |     |                  | ADER | R<7:0>       |                  |        |       |

| bit 7            |     |                  |      |              |                  |        | bit 0 |

|                  |     |                  |      |              |                  |        |       |

| Legend:          |     |                  |      |              |                  |        |       |

| R = Readable bit |     | W = Writable bit |      | U = Unimpler | nented bit, reac | as '0' |       |

| '1' = Bit is set | '0' = Bit is cleared                                                                          |

|------------------|-----------------------------------------------------------------------------------------------|

|                  |                                                                                               |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB Lower byte of ADC Setpoint Error calculation is determined |

bit 7-0 **ADERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 23-1 for more details.

#### REGISTER 31-28: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<15:8> |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<15:8>**: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

|            |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<7:0>**: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2016-2017 Microchip Technology Inc.

u = Bit is unchanged

# PIC18(L)F24/25K40

| RRN                         | ICF                                                                                                              | Rotate F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Right f (No                                                                               | Carry)                          |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|--|--|

| Synta                       | ax:                                                                                                              | RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RRNCF f {,d {,a}}                                                                         |                                 |  |  |

| Operands:                   |                                                                                                                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                           |                                 |  |  |

| Oper                        | ation:                                                                                                           | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $(f) \rightarrow dest,$<br>$(f<0>) \rightarrow dest<7>$                                   |                                 |  |  |

| Status Affected: N, Z       |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |                                 |  |  |

| Encoding:                   |                                                                                                                  | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00da                                                                                      | ffff ffff                       |  |  |

| Desc                        | ription:                                                                                                         | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected (default), overriding the BSR<br>value. If 'a' is '1', then the bank will be<br>selected as per the BSR value.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                                                                                           |                                 |  |  |

|                             |                                                                                                                  | eral Offse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | et Mode" for                                                                              | details.                        |  |  |

| 10/0 55                     |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | et Mode" for                                                                              | details.                        |  |  |

| Word                        |                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | et Mode" for                                                                              | details.                        |  |  |

| Cycle                       | es:                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | et Mode" for                                                                              | details.                        |  |  |

| Cycle                       | es:<br>cycle Activity:                                                                                           | 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | et Mode" for<br>► regi                                                                    | tetails.                        |  |  |

| Cycle                       | es:                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | et Mode" for                                                                              | details.<br>ster f              |  |  |