#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k40-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                      |                                                                                        |                |     |                                    |     |     | 1       |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------|-----|------------------------------------|-----|-----|---------|--|

| U-0                                                                  | U-0                                                                                    | U-0            | U-0 | U-0                                | U-0 | U-0 | R/W-0/0 |  |

| —                                                                    |                                                                                        | —              |     | —                                  | —   |     | DSMMD   |  |

| bit 7 bit 0                                                          |                                                                                        |                |     |                                    |     |     |         |  |

|                                                                      |                                                                                        |                |     |                                    |     |     |         |  |

| Legend:                                                              |                                                                                        |                |     |                                    |     |     |         |  |

| R = Readable                                                         | bit                                                                                    | W = Writable I | oit | U = Unimplemented bit, read as '0' |     |     |         |  |

| u = Bit is unch                                                      | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other |                |     | ther Resets                        |     |     |         |  |

| '1' = Bit is set '0' = Bit is cleared q = Value depends on condition |                                                                                        |                |     |                                    |     |     |         |  |

#### REGISTER 7-6: PMD5: PMD CONTROL REGISTER 5

| bit 7-1 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 0 DSMMD: Disable Data Signal Modulator bit

1 = DSM module disabled

0 = DSM module enabled

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH PMD

| Name | Bit 7  | Bit 6   | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------|--------|---------|--------|---------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD | FVRMD   | HLVDMD | CRCMD   | SCANMD | NVMMD  | CLKRMD | IOCMD  | 64                  |

| PMD1 | _      | TMR6MD  | TMR5MD | TMR4MD  | TMR3MD | TMR2MD | TMR1MD | TMR0MD | 65                  |

| PMD2 | _      | DACMD   | ADCMD  | —       | —      | CMP2MD | CMP1MD | ZCDMD  | 66                  |

| PMD3 | _      | _       | _      | _       | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 67                  |

| PMD4 | _      | UART1MD | _      | MSSP1MD | _      | _      | _      | CWG1MD | 68                  |

| PMD5 | —      | _       | _      | —       | _      | _      | _      | DSMMD  | 69                  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the PMD.

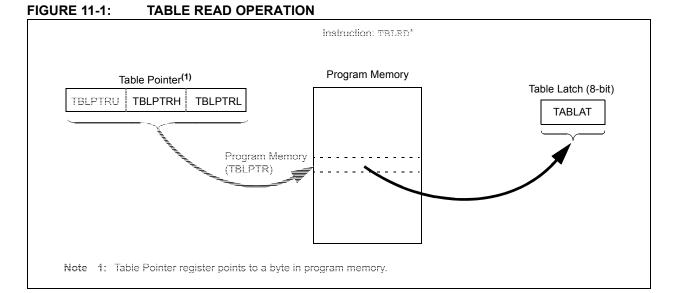

#### 11.1.1 TABLE READS AND TABLE WRITES

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is eight bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 11-1 shows the operation of a table read.

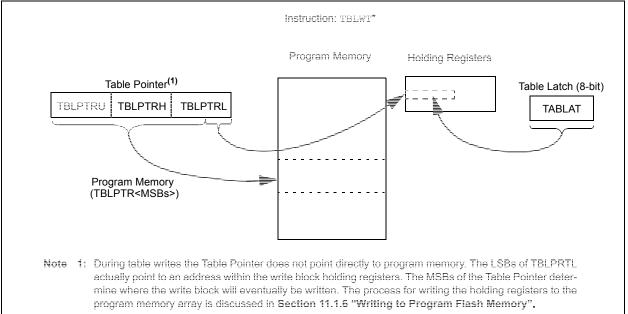

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 11.1.6 "Writing to Program Flash Memory"**. Figure 11-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

### FIGURE 11-2: TABLE WRITE OPERATION

| U-0                                | U-0                                               | U-0             | U-0       | U-0                                     | U-0              | R/W-0/0 | R/W-0/0 |

|------------------------------------|---------------------------------------------------|-----------------|-----------|-----------------------------------------|------------------|---------|---------|

| _                                  | —                                                 | —               | —         | _                                       | —                | CCP2IE  | CCP1IE  |

| bit 7                              |                                                   |                 |           |                                         |                  |         | bit 0   |

|                                    |                                                   |                 |           |                                         |                  |         |         |

| Legend:                            |                                                   |                 |           |                                         |                  |         |         |

| R = Readable bit W = Writable bit  |                                                   |                 |           | U = Unimpler                            | nented bit, read | as '0'  |         |

| -n = Value at POR '1' = Bit is set |                                                   |                 |           | '0' = Bit is cleared x = Bit is unknown |                  |         |         |

|                                    |                                                   |                 |           |                                         |                  |         |         |

| bit 7-2                            | Unimplemen                                        | ted: Read as '  | 0'        |                                         |                  |         |         |

| bit 1                              | -                                                 |                 |           |                                         |                  |         |         |

| bit 0                              | <b>CCP1IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | CP1 Interrupt E | nable bit |                                         |                  |         |         |

#### REGISTER 14-16: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

| R/W-0/0         | R/W-0/0                                                                                          | R/W-0/0          | U-0    | U-0              | U-0              | U-0             | R/W-0/0 |

|-----------------|--------------------------------------------------------------------------------------------------|------------------|--------|------------------|------------------|-----------------|---------|

| SCANIE          | CRCIE                                                                                            | NVMIE            | —      | —                | —                | —               | CWG1IE  |

| bit 7           | -                                                                                                |                  |        | •                |                  |                 | bit 0   |

|                 |                                                                                                  |                  |        |                  |                  |                 |         |

| Legend:         |                                                                                                  |                  |        |                  |                  |                 |         |

| R = Readable    | bit                                                                                              | W = Writable     | bit    | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at F | POR                                                                                              | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7           | <ul> <li>SCANIE: SCAN Interrupt Enable bit</li> <li>1 = Enabled</li> <li>0 = Disabled</li> </ul> |                  |        |                  |                  |                 |         |

| bit 6           |                                                                                                  | Interrupt Enab   | le bit |                  |                  |                 |         |

| bit 5           | <b>NVMIE:</b> NVM<br>1 = Enabled<br>0 = Disabled                                                 | Interrupt Enab   | le bit |                  |                  |                 |         |

| bit 4-1         | Unimplemen                                                                                       | ted: Read as '   | כ'     |                  |                  |                 |         |

| bit 0           | -                                                                                                | /G Interrupt En  |        |                  |                  |                 |         |

#### REGISTER 14-17: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|---------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   |        | —      | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIE0   | _        | —         | TMR0IE | IOCIE  | _      | INT2IE  | INT1IE  | INT0IE  | 175                 |

| PIE1   | OSCFIE   | CSWIE     | _      | _      | —      | _       | ADTIE   | ADIE    | 176                 |

| PIE2   | HLVDIE   | ZCDIE     | _      |        | _      | _       | C2IE    | C1IE    | 177                 |

| PIE3   | _        | _         | RC1IE  | TX1IE  | —      | _       | BCL1IE  | SSP1IE  | 178                 |

| PIE4   | _        | —         | TMR6IE | TMR5IE | TMR4IE | TMR3IE  | TMR2IE  | TMR1IE  | 179                 |

| PIE5   |          | _         | _      | _      | _      | TMR5GIE | TMR3GIE | TMR1GIE | 180                 |

| PIE6   | —        | _         | —      | _      | —      | —       | CCP2IE  | CCP1IE  | 181                 |

| PIE7   | SCANIE   | CRCIE     | NVMIE  | _      | —      | _       | _       | CWG1IE  | 182                 |

| PIR0   |          | _         | TMR0IF | IOCIF  | _      | INT2IF  | INT1IF  | INTOIF  | 167                 |

| PIR1   | OSCFIF   | CSWIF     | —      | _      | —      | _       | ADTIF   | ADIF    | 168                 |

| PIR2   | HLVDIF   | ZCDIF     | —      | _      | —      | —       | C2IF    | C1IF    | 169                 |

| PIR3   | —        | _         | RC1IF  | TX1IF  | —      | _       | BCL1IF  | SSP1IF  | 170                 |

| PIR4   |          | _         | TMR6IF | TMR5IF | TMR4IF | TMR3IF  | TMR2IF  | TMR1IF  | 171                 |

| PIR5   | _        | _         | —      | _      | —      | TMR5GIF | TMR3GIF | TMR1GIF | 172                 |

| PIR6   | _        | _         | —      | _      | —      | _       | CCP2IF  | CCP1IF  | 173                 |

| PIR7   | SCANIF   | CRCIF     | NVMIF  | _      | —      | _       | _       | CWG1IF  | 174                 |

| IPR0   |          | _         | TMR0IP | IOCIP  | _      | INT2IP  | INT1IP  | INT0IP  | 183                 |

| IPR1   | OSCFIP   | CSWIP     | —      | _      | —      | _       | ADTIP   | ADIP    | 184                 |

| IPR2   | HLVDIP   | ZCDIP     | —      | _      | —      | —       | C2IP    | C1IP    | 185                 |

| IPR3   | —        | —         | RC1IP  | TX1IP  | —      | —       | BCL1IP  | SSP1IP  | 186                 |

| IPR4   | —        | —         | TMR6IP | TMR5IP | TMR4IP | TMR3IP  | TMR2IP  | TMR1IP  | 187                 |

| IPR5   | —        | —         | —      | _      | —      | TMR5GIP | TMR3GIP | TMR1GIP | 188                 |

| IPR6   | —        | —         | —      | —      | —      | —       | CCP2IP  | CCP1IP  | 189                 |

| IPR7   | SCANIP   | CRCIP     | NVMIP  | _      | —      | —       | —       | CWG1IP  | 190                 |

| TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS | TABLE 14-1: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|-------------------------------------------------------------|-------------|-------------------------------------------------|

|-------------------------------------------------------------|-------------|-------------------------------------------------|

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Interrupts.

#### REGISTER 19-3: TMRxCLK: TIMERx CLOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |  |

|-------|-----|-----|-----|---------|---------|---------|---------|--|

| —     | —   |     | —   | CS<3:0> |         |         |         |  |

| bit 7 |     |     |     |         |         |         | bit 0   |  |

|       |     |     |     |         |         |         |         |  |

| Legend:           |                  |                       |               |  |

|-------------------|------------------|-----------------------|---------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | u = unchanged |  |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 **CS<3:0>:** Timerx Clock Source Selection bits

| cs        | Timer1             | Timer3             | Timer5             |

|-----------|--------------------|--------------------|--------------------|

| 03        | Clock Source       | Clock Source       | Clock Source       |

| 1111-1100 | Reserved           | Reserved           | Reserved           |

| 1011      | TMR5 overflow      | TMR5 overflow      | Reserved           |

| 1010      | TMR3 overflow      | Reserved           | TMR3 overflow      |

| 1001      | Reserved           | TMR1 overflow      | TMR1 overflow      |

| 1000      | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      |

| 0111      | CLKREF             | CLKREF             | CLKREF             |

| 0110      | SOSC               | SOSC               | SOSC               |

| 0101      | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) |

| 0100      | LFINTOSC           | LFINTOSC           | LFINTOSC           |

| 0011      | HFINTOSC           | HFINTOSC           | HFINTOSC           |

| 0010      | Fosc               | Fosc               | Fosc               |

| 0001      | Fosc/4             | Fosc/4             | Fosc/4             |

| 0000      | T1CKIPPS           | T3CKIPPS           | T5CKIPPS           |

| Name     | Bit 7    | Bit 6        | Bit 5          | Bit 4                    | Bit 3              | Bit 2        | Bit 1   | Bit 0   | Reset<br>Values<br>on<br>Page |

|----------|----------|--------------|----------------|--------------------------|--------------------|--------------|---------|---------|-------------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL    | IPEN           | _                        | _                  | INT2EDG      | INT1EDG | INT0EDG | 166                           |

| PIE4     | _        | _            | TMR6IE         | TMR5IE                   | TMR4IE             | TMR3IE       | TMR2IE  | TMR1IE  | 179                           |

| PIE5     | _        | _            | _              | _                        | _                  | TMR5GIE      | TMR3GIE | TMR1GIE | 180                           |

| PIR4     | _        | _            | TMR6IF         | TMR5IF                   | TMR4IF             | TMR3IF       | TMR2IF  | TMR1IF  | 170                           |

| PIR5     | _        | _            | _              | _                        | _                  | TMR5GIF      | TMR3GIF | TMR1GIF | 171                           |

| IPR4     | _        | _            | TMR6IP         | TMR5IP                   | TMR4IP             | TMR3IP       | TMR2IP  | TMR1IP  | 187                           |

| IPR5     | _        | _            | _              | _                        | _                  | TMR5GIP      | TMR3GIP | TMR1GIP | 188                           |

| PMD1     | _        | TMR6MD       | TMR5MD         | TMR4MD                   | TMR3MD             | TMR2MD       | TMR1MD  | TMR0MD  | 65                            |

| T1CON    | _        | _            | CKPS           | CKPS<1:0> — SYNC RD16 ON |                    |              |         |         | 223                           |

| T1GCON   | GE       | GPOL         | GTM            | GSPM                     | GO/DONE            | GVAL         | _       | _       | 224                           |

| T3CON    | _        | _            | CKPS           | <1:0>                    | _                  | SYNC         | RD16    | ON      | 223                           |

| T3GCON   | GE       | GPOL         | GTM            | GSPM                     | GO/DONE            | GVAL         | _       | _       | 224                           |

| T5CON    | —        | _            | CKPS           | <1:0>                    | —                  | SYNC         | RD16    | ON      | 223                           |

| T5GCON   | GE       | GPOL         | GTM            | GSPM                     | GO/DONE            | GVAL         | -       | _       | 224                           |

| TMR1H    |          | Holding Regi | ster for the N | lost Significa           | ant Byte of the 16 | 6-bit TMR1 R | egister |         | 227                           |

| TMR1L    |          | L            | east Significa | ant Byte of th           | ne 16-bit TMR1 F   | Register     |         |         | 227                           |

| TMR3H    |          | Holding Regi | ster for the M | lost Significa           | ant Byte of the 16 | 6-bit TMR3 R | egister |         | 227                           |

| TMR3L    |          | L            | east Significa | ant Byte of th           | ne 16-bit TMR3 F   | Register     |         |         | 227                           |

| TMR5H    |          | Holding Regi | ster for the N | lost Significa           | ant Byte of the 16 | 6-bit TMR5 R | egister |         | 227                           |

| TMR5L    |          | L            | east Significa | ant Byte of th           | ne 16-bit TMR5 F   | Register     |         |         | 227                           |

| T1CKIPPS | —        | _            |                |                          | T1C                | KIPPS<4:0>   | 1       |         | 211                           |

| T1GPPS   | —        | _            |                |                          | T1                 | GPPS<4:0>    |         |         | 211                           |

| T3CKIPPS | _        | _            | _              |                          | ТЗС                | KIPPS<4:0>   |         |         | 211                           |

| T3GPPS   |          | _            | _              |                          | Т3                 | GPPS<4:0>    |         |         | 211                           |

| T5CKIPPS |          | _            | _              |                          | T5C                | KIPPS<4:0>   |         |         | 211                           |

| T5GPPS   |          | _            | _              |                          | T5                 | GPPS<4:0>    |         |         | 211                           |

#### TABLE 19-4: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by TIMER1/3/5.

### 23.0 ZERO-CROSS DETECTION (ZCD) MODULE

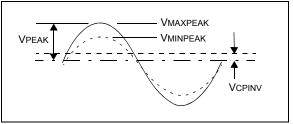

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 23-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

### 23.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 23-1 and Figure 23-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

#### EQUATION 23-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 23-1: EXTERNAL VOLTAGE

| U-0              | U-0         | R/W-0/0                                                                                                           | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|------------------|--------------|--|--|

| _                | _           | AS5E                                                                                                              | AS4E          | AS3E             | AS2E             | AS1E             | AS0E         |  |  |

| bit 7            |             |                                                                                                                   |               |                  |                  |                  | bit 0        |  |  |

|                  |             |                                                                                                                   |               |                  |                  |                  |              |  |  |

| Legend:          |             |                                                                                                                   |               |                  |                  |                  |              |  |  |

| R = Readable     | e bit       | W = Writable                                                                                                      | bit           | U = Unimpler     | mented bit, read | l as '0'         |              |  |  |

| u = Bit is uncl  | hanged      | x = Bit is unkr                                                                                                   | iown          | -n/n = Value     | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is set |             | '0' = Bit is clea                                                                                                 | ared          | q = Value de     | pends on condit  | ion              |              |  |  |

|                  |             |                                                                                                                   |               |                  |                  |                  |              |  |  |

| bit 7-6          | Unimplemer  | nted Read as '0                                                                                                   | ,             |                  |                  |                  |              |  |  |

| bit 5            | AS5E: CWG   | Auto-shutdown                                                                                                     | Source 5 (CM  | MP2 OUT) Ena     | ıble bit         |                  |              |  |  |

|                  |             | utdown for CM                                                                                                     |               |                  |                  |                  |              |  |  |

|                  | 0 = Auto-sh | utdown for CM                                                                                                     | P2 OUT is dis | abled            |                  |                  |              |  |  |

| bit 4            | AS4E: CWG   | Auto-shutdown                                                                                                     | Source 4 (CN  | /IP1 OUT) Ena    | ible bit         |                  |              |  |  |

|                  |             | utdown for CM                                                                                                     |               |                  |                  |                  |              |  |  |

|                  |             | utdown for CM                                                                                                     |               |                  |                  |                  |              |  |  |

| bit 3            |             | Auto-shutdown                                                                                                     |               |                  | ed) Enable bit   |                  |              |  |  |

|                  |             | utdown for TMF                                                                                                    |               |                  |                  |                  |              |  |  |

|                  |             | utdown for TMF                                                                                                    | —             |                  |                  |                  |              |  |  |

| bit 2            |             | Auto-shutdown                                                                                                     | · ·           | _                | ed) Enable bit   |                  |              |  |  |

|                  |             | utdown for TMF<br>utdown for TMF                                                                                  |               |                  |                  |                  |              |  |  |

|                  |             |                                                                                                                   | —             |                  |                  |                  |              |  |  |

| bit 1            |             | AS1E: CWG Auto-shutdown Source 1 (TMR2_Postscaled) Enable bit<br>1 = Auto-shutdown for TMR2 Postscaled is enabled |               |                  |                  |                  |              |  |  |

|                  |             | iutdown for TMF                                                                                                   |               |                  |                  |                  |              |  |  |

| bit 0            |             |                                                                                                                   |               |                  |                  | blo bit          |              |  |  |

|                  |             |                                                                                                                   | •             | in selected by C | CWG1PPS) Ena     |                  |              |  |  |

|                  | 1 = Autoch  | utdown for CW                                                                                                     | C1DDQ Din in  | anablad          |                  |                  |              |  |  |

## REGISTER 24-7: CWG1AS1: CWG AUTO-SHUTDOWN CONTROL REGISTER 1

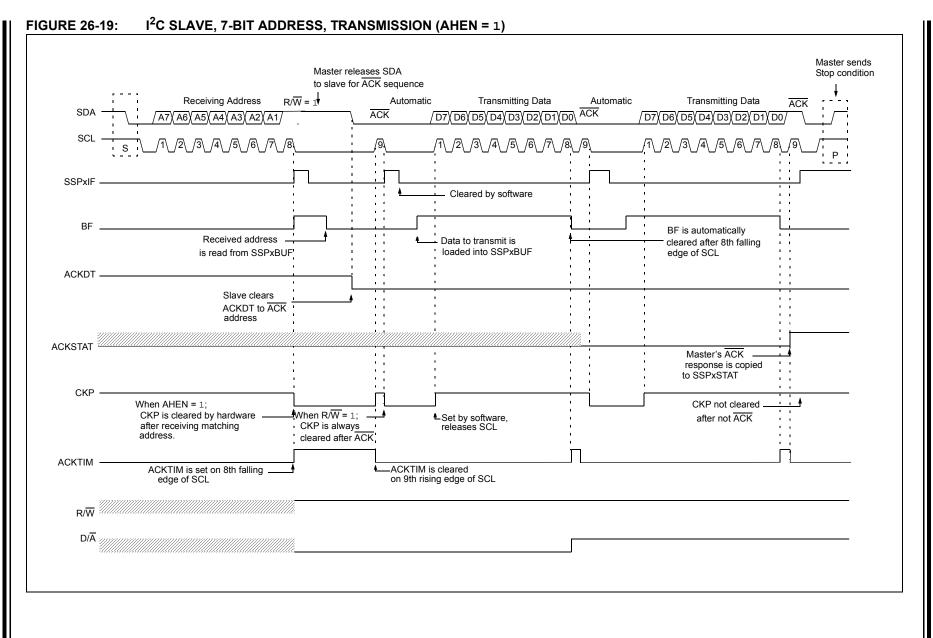

#### 26.8.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

### 26.9 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of the SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 26.9.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 26-5) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register affects the address matching process. See **Section 26.9.9** "**SSP Mask Register**" for more information.

#### 26.9.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 26.9.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 26.9.2 SLAVE RECEPTION

When the R/W bit of a matching received address byte is clear, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 26-3.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 26.9.6.2 "10-bit Addressing Mode"** for more detail.

#### 26.9.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 26.9.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 26.9.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 26.9.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 26-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

Note 1: If the master ACKs the clock will be stretched.

ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

| FIGURE 27-12:                                       | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                               |

|-----------------------------------------------------|-------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)         | X     bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7 |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                         |

| SREN bit                                            | ·0,                                                                     |

| RCxIF bit<br>(Interrupt) ———<br>Read<br>RCxREG ———— |                                                                         |

|                                                     | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0.  |

## TABLE 27-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7    | Bit 6                                  | Bit 5   | Bit 4       | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|----------------------------------------|---------|-------------|---------------|-------------|---------|---------|---------------------|

| ANSELB   | ANSELB7  | ANSELB6                                | ANSELB5 | ANSELB4     | ANSELB3       | ANSELB2     | ANSELB1 | ANSELB0 | 199                 |

| ANSELC   | ANSELC7  | ANSELC6                                | ANSELC5 | ANSELC4     | ANSELC3       | ANSELC2     | ANSELC1 | ANSELC0 | 199                 |

| BAUDxCON | ABDOVF   | RCIDL                                  | _       | SCKP        | BRG16         | _           | WUE     | ABDEN   | 389                 |

| INTCON   | GIE/GIEH | PEIE/GIEL                              | IPEN    | —           | _             | INT2EDG     | INT1EDG | INT0EDG | 166                 |

| PIE3     | _        | _                                      | RC1IE   | TX1IE       | —             | —           | BCL1IE  | SSP1IE  | 178                 |

| PIR3     |          | —                                      | RC1IF   | TX1IF       | —             | —           | BCL1IF  | SSP1IF  | 170                 |

| IPR3     | _        | —                                      | RC1IP   | TX1IP       | —             | _           | BCL1IP  | SSP1IP  | 186                 |

| RCxREG   |          |                                        | EUS     | ARTx Receiv | e Data Regis  | ter         |         |         | 393*                |

| RCxSTA   | SPEN     | RX9                                    | SREN    | CREN        | ADDEN         | FERR        | OERR    | RX9D    | 388                 |

| RxyPPS   | _        | _                                      | _       |             | F             | RxyPPS<4:0> |         |         | 213                 |

| RXxPPS   | _        | —                                      | _       | RXPPS<4:0>  |               |             |         |         | 211                 |

| SPxBRGH  |          | EUSARTx Baud Rate Generator, High Byte |         |             |               |             |         |         | 398*                |

| SPxBRGL  |          |                                        | EUSART  | x Baud Rate | Generator, Lo | ow Byte     |         |         | 398*                |

| TXxSTA   | CSRC     | TX9                                    | TXEN    | SYNC        | SENDB         | BRGH        | TRMT    | TX9D    | 387                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

## 27.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 27.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCxREG register. If the RCxIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 27.5.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CKx and DTx pins (if applicable).

- 3. If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCxIF bit will be set when reception is complete. An interrupt will be generated if the RCxIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

| Name     | Bit 7    | Bit 6     | Bit 5 | Bit 4       | Bit 3         | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|-------|-------------|---------------|------------|---------|---------|---------------------|

| BAUDxCON | ABDOVF   | RCIDL     |       | SCKP        | BRG16         | —          | WUE     | ABDEN   | 389                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN  | _           | _             | INT2EDG    | INT1EDG | INT0EDG | 166                 |

| PIE3     | _        | —         | RC1IE | TX1IE       | _             | _          | BCL1IE  | SSP1IE  | 178                 |

| PIR3     | _        | —         | RC1IF | TX1IF       | _             | _          | BCL1IF  | SSP1IF  | 170                 |

| IPR3     | -        | —         | RC1IP | TX1IP       | _             | _          | BCL1IP  | SSP1IP  | 186                 |

| RCxREG   |          |           | EUS   | ART Receive | e Data Regist | er         |         |         | 393*                |

| RCxSTA   | SPEN     | RX9       | SREN  | CREN        | ADDEN         | FERR       | OERR    | RX9D    | 388                 |

| RxyPPS   | -        | —         | _     |             | RxyPPS<4:0>   |            |         |         |                     |

| RXxPPS   | _        | —         | _     |             |               | RXPPS<4:0> | •       |         | 211                 |

| TXxSTA   | CSRC     | TX9       | TXEN  | SYNC        | SENDB         | BRGH       | TRMT    | TX9D    | 387                 |

## TABLE 27-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

|                  | R/W-x/x |                   | R/W-x/x |                | R/W-x/x          |                |              |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/x          | R/W-X/X | R/W-x/x           | R/W-X/X | R/W-x/x        | R/W-X/X          | R/W-x/x        | R/W-x/x      |

|                  |         |                   | ADUTH   | H<15:8>        |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable b    | bit     | U = Unimpler   | nented bit, read | 1 as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ired    |                |                  |                |              |

#### REGISTER 31-30: ADUTHH: ADC UPPER THRESHOLD HIGH BYTE REGISTER

bit 7-0 **ADUTH<15:8>**: ADC Upper Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-31: ADUTHL: ADC UPPER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADUTH   | 1<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADUTH<7:0>**: ADC Upper Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

### 32.0 COMPARATOR MODULE

**Note:** The PIC18(L)F24/25K40 devices have two comparators. Therefore, all information in this section refers to both C1 and C2.

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution.

The analog comparator module includes the following features:

- Programmable input selection

- Programmable output polarity

- Rising/falling output edge interrupts

- Wake-up from Sleep

- CWG Auto-shutdown source

- Selectable voltage reference

- ADC Auto-trigger

- TMR1/3/5 Gate

- TMR2/4/6 Reset

- CCP Capture Mode Input

- DSM Modulator Source

- Input and Window signal to Signal Measurement

Timer

#### 32.1 Comparator Overview

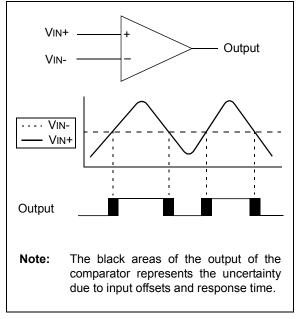

A single comparator is shown in Figure 32-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

| ΒZ          |                                                    | Branch if                                                                                                                                                                                                                                                                            | Zero                                                 |                 |  |  |  |  |

|-------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------|--|--|--|--|

| Synta       | ax:                                                | BZ n                                                                                                                                                                                                                                                                                 |                                                      |                 |  |  |  |  |

| Oper        | ands:                                              | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                         | $-128 \le n \le 127$                                 |                 |  |  |  |  |

| Operation:  |                                                    |                                                                                                                                                                                                                                                                                      | if ZERO bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |                 |  |  |  |  |

| Statu       | is Affected:                                       | None                                                                                                                                                                                                                                                                                 |                                                      |                 |  |  |  |  |

| Encoding:   |                                                    | 1110                                                                                                                                                                                                                                                                                 | 0000 nnr                                             | in nnnn         |  |  |  |  |

| Desc        | ription:                                           | If the ZERO bit is '1', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |                                                      |                 |  |  |  |  |

| Word        | ds:                                                | 1                                                                                                                                                                                                                                                                                    |                                                      |                 |  |  |  |  |

| Cycle       | es:                                                | 1(2)                                                                                                                                                                                                                                                                                 |                                                      |                 |  |  |  |  |

|             | ycle Activity:<br>imp:                             |                                                                                                                                                                                                                                                                                      |                                                      |                 |  |  |  |  |

|             | Q1                                                 | Q2                                                                                                                                                                                                                                                                                   | Q3                                                   | Q4              |  |  |  |  |

|             | Decode                                             | Read literal<br>'n'                                                                                                                                                                                                                                                                  | Process<br>Data                                      | Write to PC     |  |  |  |  |

|             | No<br>operation                                    | No<br>operation                                                                                                                                                                                                                                                                      | No<br>operation                                      | No<br>operation |  |  |  |  |

| lf No       | o Jump:                                            |                                                                                                                                                                                                                                                                                      |                                                      |                 |  |  |  |  |

|             | Q1                                                 | Q2                                                                                                                                                                                                                                                                                   | Q3                                                   | Q4              |  |  |  |  |

|             | Decode                                             | Read literal<br>'n'                                                                                                                                                                                                                                                                  | Process<br>Data                                      | No<br>operation |  |  |  |  |

| <u>Exan</u> | Before Instruc<br>PC                               | = ad                                                                                                                                                                                                                                                                                 | BZ Jump<br>dress (HERE)                              |                 |  |  |  |  |

|             | After Instructio<br>If ZERO<br>PC<br>If ZERO<br>PC | = 1;<br>= ad<br>= 0;                                                                                                                                                                                                                                                                 | dress (Jump)<br>dress (HERE                          |                 |  |  |  |  |

| CALL                                                | Subroutin                                                                                                                                                             |                                                                                                                              |                                                                                         |                                                                                                                                  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                             | CALL k {,                                                                                                                                                             | s}                                                                                                                           |                                                                                         |                                                                                                                                  |  |

| Operands:                                           | $0 \le k \le 1048575$<br>s $\in$ [0,1]                                                                                                                                |                                                                                                                              |                                                                                         |                                                                                                                                  |  |

| Operation:                                          | $\begin{array}{l} (PC) + 4 \rightarrow \\ k \rightarrow PC < 20 \\ \text{if } s = 1 \\ (W) \rightarrow WS \\ (Status) \rightarrow \\ (BSR) \rightarrow B \end{array}$ | ):1>,<br>,<br>STATUS                                                                                                         | S,                                                                                      |                                                                                                                                  |  |

| Status Affected:                                    | None                                                                                                                                                                  |                                                                                                                              |                                                                                         |                                                                                                                                  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                          | 110s<br>k <sub>19</sub> kkk                                                                                                  | k <sub>7</sub> kk<br>kkkł                                                               |                                                                                                                                  |  |

|                                                     | memory rai<br>(PC + 4) is                                                                                                                                             |                                                                                                                              |                                                                                         |                                                                                                                                  |  |

|                                                     | stack. If 's'<br>registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                                   | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |  |

| Words:                                              | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value                                                                                                 | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |  |

| Words:<br>Cycles:                                   | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                                                    | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |  |

|                                                     | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2                                                                               | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |  |

| Cycles:                                             | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2                                                                               | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, Statu<br>ushed in<br>register<br>S. If 's'<br>ult). Th<br>ded intu<br>nstructio      | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |  |

| Cycles:<br>Q Cycle Activity:                        | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2                                                                     | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir                                   | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded intr<br>astructions<br>PC to<br>sk | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>o PC<20:<br>on.                                                      |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>No  | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,                                  | = 1, the <sup>1</sup><br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSHF<br>stac | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded into<br>astructions<br>PC to<br>ck | us and BS<br>nto their<br>'s, WS,<br>= 0, no<br>nen, the<br>o PC<20:<br>on.<br>Q4<br>Read liter<br>'k'<19:82<br>Write to F<br>No |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode        | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,                                  | = 1, the <sup>1</sup><br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSHF<br>stac | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded into<br>astructions<br>PC to<br>ck | us and BS<br>nto their<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20:<br>on.<br>Q4<br>Read liter<br>'k'<19:82<br>Write to F       |  |

|    |             | (,                                     |                                                        |

|----|-------------|----------------------------------------|--------------------------------------------------------|

| on |             |                                        |                                                        |

| =  |             |                                        |                                                        |

| =  | address     | (HERE +                                | 4)                                                     |

| =  | W           |                                        |                                                        |

| =  | BSR         |                                        |                                                        |

| S= | Status      |                                        |                                                        |

|    | =<br>=<br>= | = address<br>= address<br>= W<br>= BSR | = address (THERE)<br>= address (HERE +<br>= W<br>= BSR |

| CPF         | SGT              | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f with W, sk                                             | ip if f > W |  |  |  |  |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------|--|--|--|--|

| Synta       | ax:              | CPFSGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f {,a}                                                   |             |  |  |  |  |

| ,           | ands:            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0-1                                                      |             |  |  |  |  |

| Oper        | ation:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (f) – (W),<br>skip if (f) > (W)<br>(unsigned comparison) |             |  |  |  |  |

| Statu       | s Affected:      | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ompanson)                                                |             |  |  |  |  |

| Enco        | ding:            | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 010a fff                                                 | f ffff      |  |  |  |  |

|             | ription:         | Compares the contents of data memory<br>location 'f' to the contents of the W by<br>performing an unsigned subtraction.<br>If the contents of 'f' are greater than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit- |                                                          |             |  |  |  |  |