Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k40t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|               | 5                                                                                 |                                                                                                                                             | •                                                     | , .                                                       |                 |                |       |  |

|---------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|-----------------|----------------|-------|--|

| R/W-1         | R/W-1                                                                             | R/W-1                                                                                                                                       | U-1                                                   | U-1                                                       | U-1             | R/W-1          | R/W-1 |  |

| BOREN<1:0>    |                                                                                   | LPBOREN                                                                                                                                     | —                                                     | —                                                         |                 | PWRTE          | MCLRE |  |

| bit 7         |                                                                                   |                                                                                                                                             |                                                       |                                                           |                 |                | bit 0 |  |

|               |                                                                                   |                                                                                                                                             |                                                       |                                                           |                 |                |       |  |

| Legend:       |                                                                                   |                                                                                                                                             |                                                       |                                                           |                 |                |       |  |

| R = Readabl   | e bit                                                                             | W = Writable b                                                                                                                              | it                                                    | U = Unimple                                               | mented bit, rea | ad as '1'      |       |  |

| -n = Value fo | r blank device                                                                    | '1' = Bit is set                                                                                                                            |                                                       | '0' = Bit is cle                                          | eared           | x = Bit is unk | nown  |  |

|               |                                                                                   |                                                                                                                                             |                                                       |                                                           |                 |                |       |  |

| bit 7-6       | When enabled<br>11 = Brown-o<br>10 = Brown-o<br>01 = Brown-o                      | : Brown-out Res<br>d, Brown-out Res<br>out Reset enabled<br>out Reset enabled<br>out Reset enabled<br>out Reset disable                     | et Voltage<br>d, SBOREN<br>d while run<br>d according | (VBOR) is set by<br>N bit is ignored<br>ning, disabled in | -               | REN is ignored |       |  |

| bit 5         | 1 = Low-Power                                                                     | ow-Power BOR I<br>wer Brown-out R<br>wer Brown-out R                                                                                        | eset is disa                                          |                                                           |                 |                |       |  |

| bit 4-2       | Unimplement                                                                       | ted: Read as '1'                                                                                                                            |                                                       |                                                           |                 |                |       |  |

| bit 1         | <b>PWRTE</b> : Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled |                                                                                                                                             |                                                       |                                                           |                 |                |       |  |

| bit 0         | $\frac{If LVP = 1}{RE3 pin fu}$ $\frac{If LVP = 0}{1 = MCLF}$                     | ter Clear ( $\overline{MCLR}$<br>nction is $\overline{MCLR}$<br>$\overline{R}$ pin is $\overline{MCLR}$<br>$\overline{R}$ pin function is p |                                                       |                                                           |                 |                |       |  |

#### REGISTER 3-3: Configuration Word 2L (30 0002h): Supervisor

# 5.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

#### 5.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

# 5.2 Programmable Clock Divider

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 5-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- · Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

# 5.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

Note: The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

# 5.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

| Address | Name     | Bit 7                                                                      | Bit 6            | Bit 5            | Bit 4              | Bit 3          | Bit 2           | Bit 1           | Bit 0             | <u>Value on</u><br>POR, BOR |

|---------|----------|----------------------------------------------------------------------------|------------------|------------------|--------------------|----------------|-----------------|-----------------|-------------------|-----------------------------|

| FE2h    | FSR1H    | _                                                                          | —                | -                | _                  | Indirec        | xxxx            |                 |                   |                             |

| FE1h    | FSR1L    |                                                                            | L                | Indirec          | t Data Memory      | Address Point  | er 1 Low        |                 |                   | xxxxxxxx                    |

| FE0h    | BSR      | —                                                                          | _                | _                | —                  |                | Bank Sele       | ct Register     |                   | 0000                        |

| FDFh    | INDF2    | Uses contents                                                              | of FSR0 to ad    | dress data me    | emory – value o    | f FSR2 not cha | anged (not a ph | ysical register | .)                |                             |

| FDEh    | POSTINC2 | Uses contents                                                              | of FSR0 to ad    | dress data me    | emory – value o    | f FSR2 post-in | cremented (not  | a physical reg  | gister)           |                             |

| FDDh    | POSTDEC2 | Uses contents                                                              | of FSR0 to ad    | dress data me    | emory – value o    | f FSR2 post-de | ecremented (no  | t a physical re | egister)          |                             |

| FDCh    | PREINC2  | Uses contents                                                              | of FSR0 to ad    | dress data me    | emory – value o    | f FSR2 pre-inc | remented (not a | a physical reg  | ister)            |                             |

| FDBh    | PLUSW2   | Uses contents<br>FSR0 offset by                                            |                  | dress data me    | emory – value o    | f FSR2 pre-inc | remented (not a | a physical reg  | ister) – value of |                             |

| FDAh    | FSR2H    | —                                                                          | —                | —                | —                  | Indirec        | t Data Memory   | Address Poin    | ter 2 High        | xxxx                        |

| FD9h    | FSR2L    |                                                                            |                  | Indirec          | t Data Memory      | Address Point  | er 2 Low        |                 |                   | xxxxxxxx                    |

| FD8h    | STATUS   | _                                                                          | TO               | PD               | Ν                  | OV             | Z               | DC              | С                 | -1100000                    |

| FD7h    | PCON0    | STKOVF                                                                     | STKUNF           | WDTWV            | RWDT               | RMCLR          | RI              | POR             | BOR               | 0011110q                    |

| FD6h    | T0CON1   |                                                                            | T0CS<2:0>        |                  | T0ASYNC            |                | 00000000        |                 |                   |                             |

| FD5h    | T0CON0   | T0EN                                                                       | —                | TOOUT            | T016BIT            |                |                 | 0-000000        |                   |                             |

| FD4h    | TMR0H    | Holding Register for the Most Significant Byte of the 16-bit TMR0 Register |                  |                  |                    |                |                 |                 |                   |                             |

| FD3h    | TMR0L    | Holding Registe                                                            | er for the Least | Significant Byt  | e of the 16-bit T  | MR0 Register   |                 |                 |                   | 00000000                    |

| FD2h    | T1CLK    | —                                                                          | —                | _                | —                  |                |                 | 0000            |                   |                             |

| FD1h    | T1GATE   | _                                                                          | —                | _                | _                  |                | GSS             | <3:0>           |                   | 0000                        |

| FD0h    | T1GCON   | GE                                                                         | GPOL             | GTM              | GSPM               | GO/DONE        | GVAL            | —               | _                 | 00000x                      |

| FCFh    | T1CON    | —                                                                          | —                | CKP              | S<1:0>             | —              | SYNC            | RD16            | ON                | 00-000                      |

| FCEh    | TMR1H    | Holding Registe                                                            | er for the Most  | Significant Byte | e of the 16-bit TM | MR1 Register   |                 |                 |                   | 00000000                    |

| FCDh    | TMR1L    | Holding Registe                                                            | er for the Least | Significant Byt  | e of the 16-bit T  | MR1 Register   |                 |                 |                   | 00000000                    |

| FCCh    | T3CLK    | _                                                                          | —                | —                | _                  |                | CS<             | <3:0>           |                   | 0000                        |

| FCBh    | T3GATE   | _                                                                          | —                | -                | _                  |                | GSS             | <3:0>           |                   | 0000                        |

| FCAh    | T3GCON   | GE                                                                         | GPOL             | GTM              | GSPM               | GO/DONE        | GVAL            | —               | _                 | x00000                      |

| FC9h    | T3CON    | —                                                                          | —                | CKP              | S<1:0>             | _              | SYNC            | RD16            | ON                | 00-000                      |

| FC8h    | TMR3H    | Holding Registe                                                            | er for the Most  | Significant Byte | e of the 16-bit TM | MR3 Register   | 1               |                 |                   | 00000000                    |

| FC7h    | TMR3L    | Holding Registe                                                            | er for the Least | Significant Byt  | e of the 16-bit T  | MR3 Register   |                 |                 |                   | 00000000                    |

| FC6h    | TMR5CLK  | _                                                                          | —                | —                | —                  |                | CS<             | <3:0>           |                   | 0000                        |

| FC5h    | T5GATE   | —                                                                          | —                | —                | —                  |                | GSS             | <3:0>           |                   | 0000                        |

| FC4h    | T5GCON   | GE                                                                         | GPOL             | GTM              | GSPM               | GO/DONE        | GVAL            | _               | _                 | x00000                      |

| FC3h    | T5CON    | —                                                                          | —                | CKP              | S<1:0>             | —              | SYNC            | RD16            | ON                | 00-000                      |

| FC2h    | TMR5H    | Holding Registe                                                            | er for the Most  | Significant Byte | e of the 16-bit TM | MR5 Register   | 1               | 1               | 1                 | 00000000                    |

Legend: x = unknown, u = unchanged, ---= unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

#### 10.4.5 STATUS REGISTER

The STATUS register, shown in Register 10-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in **Section 35.0 "Instruction Set Summary"** and Table 35-3.

Note: The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

| IABLE II V.        |                                             |  |  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|--|--|

| Example            | Operation on Table Pointer                  |  |  |  |  |  |  |  |

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |  |  |  |

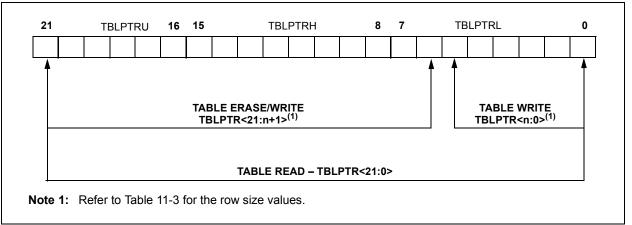

### TABLE 11-3: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

#### **FIGURE 11-3**:

TABLE POINTER BOUNDARIES BASED ON OPERATION

# PIC18(L)F24/25K40

# 13.9 Program Memory Scan Configuration

If desired, the program memory scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the scanner to work with the CRC you need to perform the following steps:

- 1. Set the Enable bit in both the CRCCON0 and SCANCON0 registers. If they get disabled, all internal states of the scanner and the CRC are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 13.11 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 13.11.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- 5. The CRCGO bit must be set before setting the SCANGO bit. Setting the SCANGO bit starts the scan. Both CRCEN and CRCGO bits must be enabled to use the scanner. When either of these bits are disabled, the scan aborts and the INVALID bit SCANCON0 is set. The scanner will wait for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

# 13.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

# 13.11 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 13-2.

# 13.11.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute. The CPU is held in its current state until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware endconditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

# 13.11.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

### 13.11.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

### 13.11.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

| Name      | Bit 7      | Bit 6       | Bit 5  | Bit 4   | Bit 3  | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |  |

|-----------|------------|-------------|--------|---------|--------|----------|---------|---------|---------------------|--|

| CRCACCH   |            |             |        | ACC     | <15:8> |          |         |         | 148                 |  |

| CRCACCL   |            |             |        |         | <7:0>  |          |         |         | 149                 |  |

| CRCCON0   | EN         | GO          | BUSY   | ACCM    | _      | _        | SHIFTM  | FULL    | 147                 |  |

| CRCCON1   |            | DLEN<       | 3:0>   |         |        | PLE      | V<3:0>  |         | 147                 |  |

| CRCDATH   |            |             |        | DATA    | <15:8> |          |         |         | 148                 |  |

| CRCDATL   |            |             |        | DATA    | <7:0>  |          |         |         | 148                 |  |

| CRCSHIFTH |            | SHIFT<15:8> |        |         |        |          |         |         |                     |  |

| CRCSHIFTL | SHIFT<7:0> |             |        |         |        |          |         |         |                     |  |

| CRCXORH   | X<15:8>    |             |        |         |        |          |         |         | 150                 |  |

| CRCXORL   | X<7:1> —   |             |        |         |        |          |         |         | 150                 |  |

| PMD0      | SYSCMD     | FVRMD       | HLVDMD | CRCMD   | SCANMD | NVMMD    | CLKRMD  | IOCMD   | 64                  |  |

| SCANCON0  | SCANEN     | SCANGO      | BUSY   | INVALID | INTM   | _        | MODE    | <1:0>   | 151                 |  |

| SCANHADRU | —          | _           |        |         | HADF   | R<21:16> |         |         | 153                 |  |

| SCANHADRH |            |             |        | HADR    | <15:8> |          |         |         | 154                 |  |

| SCANHADRL |            |             |        | HADF    | R<7:0> |          |         |         | 154                 |  |

| SCANLADRU | —          | —           |        |         | LADF   | ₹<21:16> |         |         | 152                 |  |

| SCANLADRH |            |             |        | LADR    | <15:8> |          |         |         | 152                 |  |

| SCANLADRL |            |             |        | LADF    | R<7:0> |          |         |         | 153                 |  |

| SCANTRIG  | _          | _           |        | _       |        | TSEL     | <3:0>   |         | 155                 |  |

| INTCON    | GIE/GIEH   | PEIE/GIEL   | IPEN   | _       | —      | INT2EDG  | INT1EDG | INT0EDG | 166                 |  |

| PIR7      | SCANIF     | CRCIF       | NVMIF  | —       | —      | —        | _       | CWG1IF  | 174                 |  |

| PIE7      | SCANIE     | CRCIE       | NVMIE  |         | —      | —        |         | CWG1IE  | 182                 |  |

| IPR7      | SCANIP     | CRCIP       | NVMIP  | _       | _      | _        | _       | CWG1IP  | 190                 |  |

| TABLE 13-5: | SUMMARY OF REGISTERS ASSOCIATED WITH CRC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

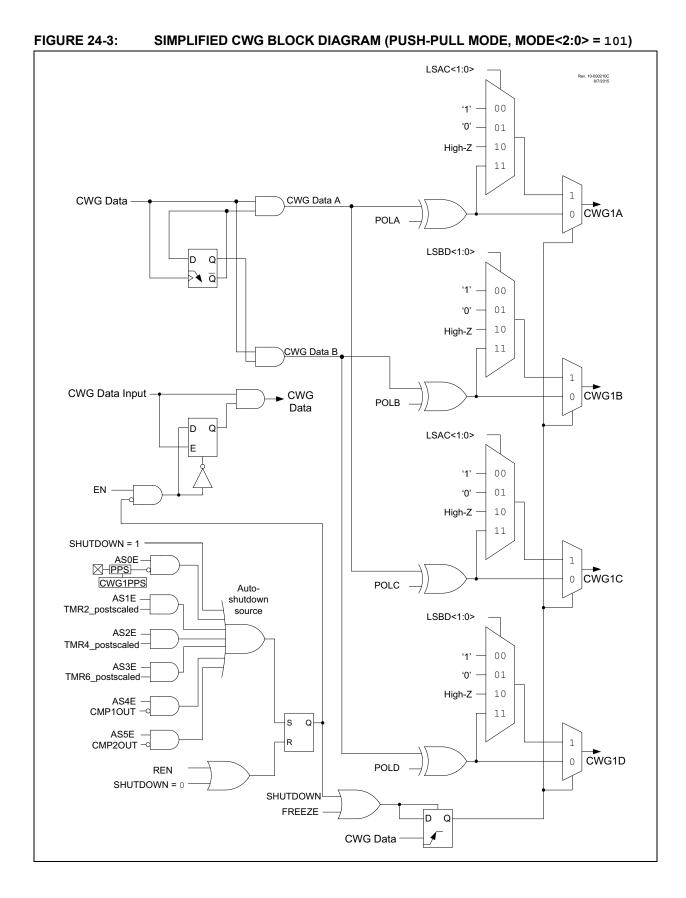

| U-0                                  | U-0           | R-x                                    | U-0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|--------------------------------------|---------------|----------------------------------------|-----------|----------------|------------------|------------------|--------------|--|--|--|--|

|                                      |               | IN                                     |           | POLD           | POLC             | POLB             | POLA         |  |  |  |  |

| bit 7                                |               |                                        |           |                |                  |                  | bit 0        |  |  |  |  |

| Legend:                              |               |                                        |           |                |                  |                  |              |  |  |  |  |

| R = Readable                         | e bit         | W = Writable                           | bit       | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |  |  |

| u = Bit is uncl                      | hanged        | x = Bit is unkr                        | nown      | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is set                     |               | '0' = Bit is clea                      | ared      | q = Value de   | pends on condit  | ion              |              |  |  |  |  |

|                                      |               |                                        |           |                |                  |                  |              |  |  |  |  |

| bit 7-6                              | •             | ted: Read as '                         |           |                |                  |                  |              |  |  |  |  |

| bit 5                                | IN: CWG Inp   | ut Value bit (rea                      | ad-only)  |                |                  |                  |              |  |  |  |  |

| bit 4                                | Unimplemen    | ted: Read as '                         | 0'        |                |                  |                  |              |  |  |  |  |

| bit 3                                | POLD: CWG     | 1D Output Pola                         | arity bit |                |                  |                  |              |  |  |  |  |

|                                      | •             | tput is inverted                       |           |                |                  |                  |              |  |  |  |  |

|                                      | 0 = Signal ou | tput is normal p                       | olarity   |                |                  |                  |              |  |  |  |  |

| bit 2                                |               | 1C Output Pola                         | •         |                |                  |                  |              |  |  |  |  |

|                                      | •             | 1 = Signal output is inverted polarity |           |                |                  |                  |              |  |  |  |  |

|                                      |               | tput is normal p                       |           |                |                  |                  |              |  |  |  |  |

| bit 1                                |               | 1B Output Pola                         | -         |                |                  |                  |              |  |  |  |  |

|                                      | -             | tput is inverted                       | •         |                |                  |                  |              |  |  |  |  |

| 0 = Signal output is normal polarity |               |                                        |           |                |                  |                  |              |  |  |  |  |

| bit 0                                |               | 1A Output Pola                         | 5         |                |                  |                  |              |  |  |  |  |

|                                      | •             | tput is inverted                       |           |                |                  |                  |              |  |  |  |  |

|                                      | 0 = Signai ou | tput is normal p                       | bolanty   |                |                  |                  |              |  |  |  |  |

# REGISTER 24-2: CWG1CON1: CWG CONTROL REGISTER 1

| U-0              | U-0       | U-0               | U-0  | U-0                                                   | R/W-0/0                 | R/W-0/0 | R/W-0/0 |  |  |

|------------------|-----------|-------------------|------|-------------------------------------------------------|-------------------------|---------|---------|--|--|

| _                | —         | —                 | —    | —                                                     | CHS<2:0> <sup>(1)</sup> |         |         |  |  |

| bit 7            |           |                   |      |                                                       |                         |         | bit 0   |  |  |

|                  |           |                   |      |                                                       |                         |         |         |  |  |

| Legend:          |           |                   |      |                                                       |                         |         |         |  |  |

| R = Readable I   | oit       | W = Writable      | bit  | U = Unimplemented bit, read as '0'                    |                         |         |         |  |  |

| u = Bit is uncha | anged     | x = Bit is unkn   | iown | -n/n = Value at POR and BOR/Value at all other Resets |                         |         |         |  |  |

| '1' = Bit is set |           | '0' = Bit is clea | ared |                                                       |                         |         |         |  |  |

|                  |           |                   |      |                                                       |                         |         |         |  |  |

| bit 7-3          | Unimpleme | nted: Read as 'o  | י)   |                                                       |                         |         |         |  |  |

| DIT 7-3 | Unimplemented: Read as 10"                      |

|---------|-------------------------------------------------|

| bit 2-0 | CHS<2:0>: Modulator Carrier High Selection bits |

|         | See Table 25-2 for signal list                  |

#### REGISTER 25-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0                 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|-------------------------|---------|

| —     | —   |     | _   | —   |         | CLS<2:0> <sup>(1)</sup> |         |

| bit 7 |     |     |     |     |         |                         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 CLS<2:0>: Modulator Carrier Low Input Selection bits See Table 25-2 for signal list

#### TABLE 25-2: MDCARH/MDCARL SELECTION MUX CONNECTIONS

|         | MDCARH |                           |          |   | MDCARL                    |  |  |  |

|---------|--------|---------------------------|----------|---|---------------------------|--|--|--|

| CHS<2:0 | )>     | Connection                | CLS<2:0> |   | Connection                |  |  |  |

| 111     | 7      | PWM4 OUT                  | 111      | 7 | PWM4 OUT                  |  |  |  |

| 110     | 6      | PWM3 OUT                  | 110      | 6 | PWM3 OUT                  |  |  |  |

| 101     | 5      | CCP2 OUT                  | 101      | 5 | CCP2 OUT                  |  |  |  |

| 100     | 4      | CCP1 OUT                  | 100      | 4 | CCP1 OUT                  |  |  |  |

| 011     | 3      | CLKREF output             | 011      | 3 | CLKREF output             |  |  |  |

| 010     | 2      | HFINTOSC                  | 010      | 2 | HFINTOSC                  |  |  |  |

| 001     | 1      | FOSC (system clock)       | 001      | 1 | FOSC (system clock)       |  |  |  |

| 000     | 0      | Pin selected by MDCARHPPS | 000      | 0 | Pin selected by MDCARLPPS |  |  |  |

© 2016-2017 Microchip Technology Inc.

#### **REGISTER 26-4:** SSPxBUF: MSSP DATA BUFFER REGISTER

| R/W-x            | R/W-x | R/W-x              | R/W-x | R/W-x                                            | R/W-x | R/W-x | R/W-x       |  |

|------------------|-------|--------------------|-------|--------------------------------------------------|-------|-------|-------------|--|

|                  |       |                    | BUF   | =<7:0>                                           |       |       |             |  |

| bit 7            |       |                    |       |                                                  |       |       | bit 0       |  |

|                  |       |                    |       |                                                  |       |       |             |  |

| Legend:          |       |                    |       |                                                  |       |       |             |  |

| R = Readable I   | bit   | W = Writable bit   |       | U = Unimplemented bit, read as '0                |       |       | as 'O'      |  |

| u = Bit is uncha | anged | x = Bit is unknown |       | -n/n = Value at POR and BOR/Value at all other F |       |       | ther Resets |  |

| '1' = Bit is set |       | '0' = Bit is clea  | red   |                                                  |       |       |             |  |

bit 7-0 BUF<7:0>: MSSP Buffer bits

#### REGISTER 26-5: SSPxADD: MSSP ADDRESS REGISTER (SPI MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | ADD<  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode: SPI mode

bit 7-0 Baud Rate Clock Divider bits SCK/SCL pin clock period = ((SSPxADD<7:0> + 1) \*4)/Fosc

© 2016-2017 Microchip Technology Inc.

PIC18(L)F24/25K40

# 27.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 27.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCxREG register. If the RCxIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 27.5.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CKx and DTx pins (if applicable).

- 3. If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCxIF bit will be set when reception is complete. An interrupt will be generated if the RCxIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

| Name     | Bit 7    | Bit 6     | Bit 5 | Bit 4       | Bit 3                     | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|-------|-------------|---------------------------|---------|---------|---------|---------------------|

| BAUDxCON | ABDOVF   | RCIDL     |       | SCKP        | BRG16                     | —       | WUE     | ABDEN   | 389                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN  | _           | _                         | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIE3     | _        | —         | RC1IE | TX1IE       | _                         | _       | BCL1IE  | SSP1IE  | 178                 |

| PIR3     | _        | —         | RC1IF | TX1IF       | _                         | _       | BCL1IF  | SSP1IF  | 170                 |

| IPR3     | -        | —         | RC1IP | TX1IP       | _                         | _       | BCL1IP  | SSP1IP  | 186                 |

| RCxREG   |          |           | EUS   | ART Receive | e Data Regist             | er      |         |         | 393*                |

| RCxSTA   | SPEN     | RX9       | SREN  | CREN        | ADDEN                     | FERR    | OERR    | RX9D    | 388                 |

| RxyPPS   | -        | —         | _     | RxyPPS<4:0> |                           |         |         |         | 213                 |

| RXxPPS   | _        | —         | _     | RXPPS<4:0>  |                           |         |         | 211     |                     |

| TXxSTA   | CSRC     | TX9       | TXEN  | SYNC        | SYNC SENDB BRGH TRMT TX9D |         |         |         | 387                 |

# TABLE 27-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

# 28.3 Register Definitions: FVR Control

| R/W-0/0         | R-q/q                                     | R/W-0/0                                                                                | R/W-0/0                                                    | R/W-0/0                              | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|-------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------|------------------|------------------|--------------|

| FVREN           | FVRRDY <sup>(1)</sup>                     | TSEN <sup>(3)</sup>                                                                    | TSRNG <sup>(3)</sup>                                       | CDAF                                 | /R<1:0>          | ADFV             | R<1:0>       |

| bit 7           | •                                         |                                                                                        |                                                            |                                      |                  |                  | bit (        |

|                 |                                           |                                                                                        |                                                            |                                      |                  |                  |              |

| Legend:         |                                           |                                                                                        |                                                            |                                      |                  |                  |              |

| R = Readabl     | e bit                                     | W = Writable                                                                           | bit                                                        | U = Unimpler                         | nented bit, read | l as '0'         |              |

| u = Bit is unc  | changed                                   | x = Bit is unk                                                                         | nown                                                       | -n/n = Value a                       | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | t                                         | '0' = Bit is cle                                                                       | ared                                                       | q = Value dep                        | pends on condit  | ion              |              |

| bit 7           | 1 Fixed Vo                                | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                     | e is enabled                                               | bit                                  |                  |                  |              |

| bit 6           | 1 = Fixed Vo                              | ed Voltage Re<br>Itage Referenc<br>Itage Referenc                                      | e output is rea                                            | -                                    | enabled          |                  |              |

| bit 5           | 1 = Tempera                               | erature Indicato<br>ture Indicator i<br>ture Indicator i                               | s enabled                                                  | )                                    |                  |                  |              |

| bit 4           | 1 = VOUT = V                              | perature Indica<br>/DD - 4VT (Higł<br>/DD - 2VT (Low                                   | n Range)                                                   | lection bit <sup>(3)</sup>           |                  |                  |              |

| bit 3-2         | 11 = Compar<br>10 = Compar<br>01 = Compar | D>: Comparato<br>ator FVR Buffe<br>ator FVR Buffe<br>ator FVR Buffe<br>ator FVR Buffe  | er Gain is 4x, (4<br>er Gain is 2x, (2<br>er Gain is 1x, ( | 2.048V) <sup>(2)</sup>               | bits             |                  |              |

| bit 1-0         | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV | : ADC FVR Bu<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer is off | is 4x, (4.096V<br>is 2x, (2.048V                           | ) <sup>(2)</sup><br>) <sup>(2)</sup> |                  |                  |              |

|                 | VRRDY is always<br>ixed Voltage Refe      |                                                                                        | cannot exceed                                              | Vdd.                                 |                  |                  |              |

| REGISTER 28-1. | FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER |

|----------------|--------------------------------------------------|

| REGISTER 20-1. | FURGON. FIXED VOLTAGE REFERENCE CONTROL REGISTER |

2: Fixed Voltage Reference output cannot exceed VDD.

3: See Section 29.0 "Temperature Indicator Module" for additional information.

| -        |       | -      |       |       |       | 1          |       | -      |                  |

|----------|-------|--------|-------|-------|-------|------------|-------|--------|------------------|

| Name     | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0  | Register on page |

| FVRCON   | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0>    | ADFV  | R<1:0> | 417              |

| ADCON0   | ADON  | ADCONT | _     | ADCS  |       | ADFM       | _     | ADGO   | 441              |

| CMxNCH   | _     | _      | _     | —     |       | CxNCH<2:0> |       | 463    |                  |

| CMxPCH   | —     | —      | _     | —     | _     | CxPCH<2:0> |       | 464    |                  |

| DAC1CON1 |       |        | _     |       |       | DAC1R<4    | :0>   |        | 423              |

### TABLE 28-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

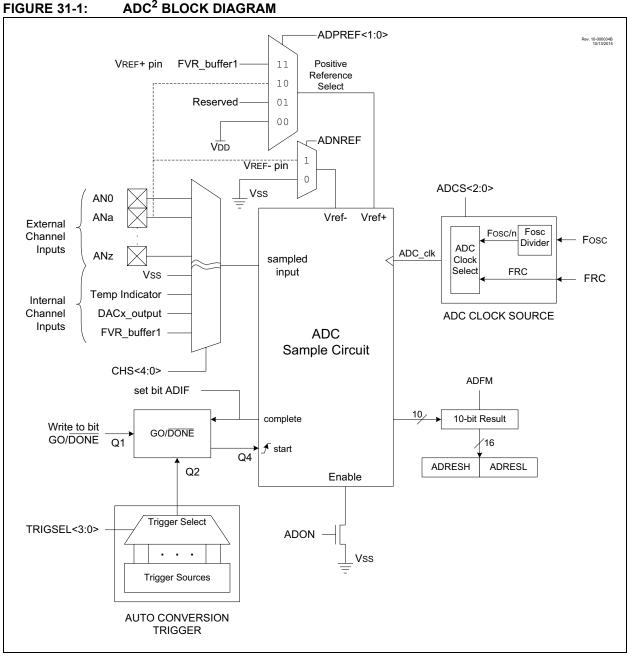

ADC<sup>2</sup> BLOCK DIAGRAM

# PIC18(L)F24/25K40

| SUBLW                                                             | Subtract                     | Subtract W from literal  |         |            |  |  |

|-------------------------------------------------------------------|------------------------------|--------------------------|---------|------------|--|--|

| Syntax:                                                           | SUBLW I                      | K                        |         |            |  |  |

| Operands:                                                         | $0 \le k \le 25$             | 5                        |         |            |  |  |

| Operation:                                                        | $k-(W) \rightarrow$          | W                        |         |            |  |  |

| Status Affected:                                                  | N, OV, C,                    | DC, Z                    |         |            |  |  |

| Encoding:                                                         | 0000                         | 1000                     | kkkk    | kkkk       |  |  |

| Description                                                       | W is subtr<br>literal 'k'. 1 |                          |         |            |  |  |

| Words:                                                            | 1                            |                          |         |            |  |  |

| Cycles:                                                           | 1                            |                          |         |            |  |  |

| Q Cycle Activity:                                                 |                              |                          |         |            |  |  |

| Q1                                                                | Q2                           | Q3                       |         | Q4         |  |  |

| Decode                                                            | Read<br>literal 'k'          | Proce<br>Data            |         | /rite to W |  |  |

| Example 1:                                                        | SUBLW (                      | )2h                      |         |            |  |  |

| Before Instruct<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 01h<br>= ?<br>n<br>= 01h   | esult is po              | ositive |            |  |  |

| Example 2:                                                        | SUBLW (                      | )2h                      |         |            |  |  |

| Before Instruct<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 02h<br>= ?<br>n<br>= 00h   | esult is ze              | ro      |            |  |  |

| Example 3:                                                        | SUBLW (                      | )2h                      |         |            |  |  |

| Before Instruct<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 03h<br>= ?<br>n<br>= FFh;( | 2's compl<br>esult is ne |         |            |  |  |

| SUBWF                                                                                   | Subtract                                                                                                                                                                                                                    | W from f                                                                                                                                                                                                                                                                                         |                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                 | SUBWF                                                                                                                                                                                                                       | f {,d {,a}}                                                                                                                                                                                                                                                                                      |                                                                                                                                                    |

| Operands:                                                                               | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                |                                                                                                                                                    |

| Operation:                                                                              | (f) – (W) –                                                                                                                                                                                                                 | → dest                                                                                                                                                                                                                                                                                           |                                                                                                                                                    |

| Status Affected:                                                                        | N, OV, C,                                                                                                                                                                                                                   | DC, Z                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |

| Encoding:                                                                               | 0101                                                                                                                                                                                                                        | 11da fff                                                                                                                                                                                                                                                                                         | f ffff                                                                                                                                             |

| Description:                                                                            | compleme<br>result is st<br>result is st<br>(default).<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0' a<br>set is enat<br>operates in<br>Addressin<br>$f \le 95$ (5Fh<br><b>35.2.3 "By</b><br>ented Inst | V from register<br>ant method). If<br>ored in W. If 'd<br>ored back in re<br>the Access Ba<br>f 'a' is '1', the I<br>ne GPR bank.<br>and the extend-<br>bled, this instru-<br>n Indexed Liter<br>g mode whene<br>1). See Section<br>te-Oriented an<br><b>ructions in Ind</b><br>de" for details. | d' is '0', the<br>l' is '1', the<br>egister 'f'<br>ank is<br>BSR is used<br>ed instruction<br>action<br>ral Offset<br>ever<br>n<br><b>Bit-Ori-</b> |

| Words:                                                                                  | 1                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

| Cycles:                                                                                 | 1                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

| Q Cycle Activity:                                                                       |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

| Q1                                                                                      | Q2                                                                                                                                                                                                                          | Q3                                                                                                                                                                                                                                                                                               | Q4                                                                                                                                                 |

| Decode                                                                                  | Read<br>register 'f'                                                                                                                                                                                                        | Process<br>Data                                                                                                                                                                                                                                                                                  | Write to destination                                                                                                                               |

| Example 1:                                                                              | SUBWF                                                                                                                                                                                                                       | REG, 1, 0                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

| Before Instruct<br>REG<br>W<br>C<br>After Instructio<br>REG<br>W<br>C<br>Z              | = 3<br>= 2<br>= ?<br>m<br>= 1<br>= 2                                                                                                                                                                                        | esult is positive                                                                                                                                                                                                                                                                                | 3                                                                                                                                                  |

| N                                                                                       | = 0                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

| Example 2:<br>Before Instruct                                                           | SUBWF                                                                                                                                                                                                                       | REG, 0, 0                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

| After Instruction<br>REG<br>W<br>C<br>After Instruction<br>REG<br>W<br>C<br>C<br>Z<br>N | = 2<br>= 2<br>= ?<br>on<br>= 2<br>= 0                                                                                                                                                                                       | esult is zero                                                                                                                                                                                                                                                                                    |                                                                                                                                                    |

| Example 3:                                                                              | - U<br>SUBWF                                                                                                                                                                                                                | REG, 1, 0                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

| Before Instruct<br>REG<br>W<br>C<br>After Instructio                                    | tion<br>= 1<br>= 2<br>= ?                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

| REG<br>W                                                                                | = FFh ;(2<br>= 2                                                                                                                                                                                                            | 's complement                                                                                                                                                                                                                                                                                    | t)                                                                                                                                                 |

| C<br>Z<br>N                                                                             |                                                                                                                                                                                                                             | esult is negativ                                                                                                                                                                                                                                                                                 | e                                                                                                                                                  |

| <b>TABLE 37-23</b> : | SPI MODE REQUIREMENTS |

|----------------------|-----------------------|

|----------------------|-----------------------|

| Standard     | Standard Operating Conditions (unless otherwise stated) |                                                                       |              |      |      |       |                                  |  |  |  |  |

|--------------|---------------------------------------------------------|-----------------------------------------------------------------------|--------------|------|------|-------|----------------------------------|--|--|--|--|

| Param<br>No. | Symbol                                                  | Characteristic                                                        | Min.         | Тур† | Max. | Units | Conditions                       |  |  |  |  |

| SP70*        | TssL2scH,<br>TssL2scL                                   | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | 2.25*Tcy     | —    | _    | ns    |                                  |  |  |  |  |

| SP71*        | TscH                                                    | SCK input high time (Slave mode)                                      | Tcy + 20     |      | _    | ns    |                                  |  |  |  |  |

| SP72*        | TscL                                                    | SCK input low time (Slave mode)                                       | Tcy + 20     | _    | _    | ns    |                                  |  |  |  |  |

| SP73*        | TDIV2scH,<br>TDIV2scL                                   | Setup time of SDI data input to SCK edge                              | 100          | —    | —    | ns    |                                  |  |  |  |  |

| SP74*        | TscH2dlL,<br>TscL2dlL                                   | Hold time of SDI data input to SCK edge                               | 100          | —    | —    | ns    |                                  |  |  |  |  |

| SP75*        | TDOR                                                    | SDO data output rise time                                             |              | 10   | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

|              |                                                         |                                                                       |              | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

| SP76*        | TdoF                                                    | SDO data output fall time                                             |              | 10   | 25   | ns    |                                  |  |  |  |  |

| SP77*        | TssH2doZ                                                | SS↑ to SDO output high-impedance                                      | 10           |      | 50   | ns    |                                  |  |  |  |  |

| SP78*        | TscR                                                    | SCK output rise time<br>(Master mode)                                 |              | 10   | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

|              |                                                         |                                                                       |              | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

| SP79*        | TscF                                                    | SCK output fall time (Master mode)                                    |              | 10   | 25   | ns    |                                  |  |  |  |  |

| SP80*        | TscH2doV,<br>TscL2doV                                   | SDO data output valid after SCK edge                                  |              |      | 50   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

|              |                                                         |                                                                       |              | _    | 145  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |  |  |  |

| SP81*        | TDOV2scH,<br>TDOV2scL                                   | SDO data output setup to SCK edge                                     | 1 Tcy        | _    | —    | ns    |                                  |  |  |  |  |

| SP82*        | TssL2doV                                                | SDO data output valid after $\overline{SS}\downarrow$ edge            | _            | _    | 50   | ns    |                                  |  |  |  |  |

| SP83*        | TscH2ssH,<br>TscL2ssH                                   | SS ↑ after SCK edge                                                   | 1.5 Tcy + 40 | —    | —    | ns    |                                  |  |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

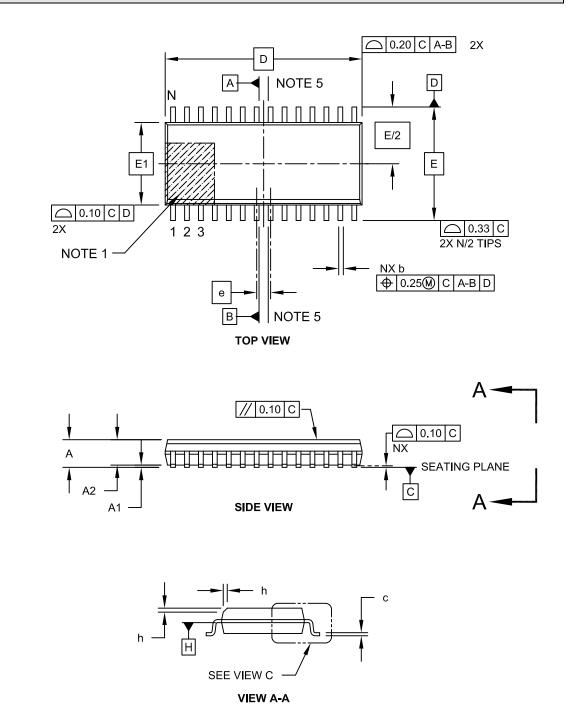

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

© 2016-2017 Microchip Technology Inc.

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

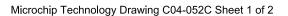

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS     |      |      |      |  |

|--------------------------|-----------------|------|------|------|--|

| Dimensior                | MIN             | NOM  | MAX  |      |  |

| Contact Pitch            | itch E 1.27 BSC |      |      |      |  |

| Contact Pad Spacing      | С               |      | 9.40 |      |  |

| Contact Pad Width (X28)  | Х               |      |      | 0.60 |  |

| Contact Pad Length (X28) | Y               |      |      | 2.00 |  |

| Distance Between Pads    | Gx              | 0.67 |      |      |  |

| Distance Between Pads    | G               | 7.40 |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A