Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k40t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Digital Peripherals (Continued)**

- · Programmable CRC with Memory Scan:

- Reliable data/program memory monitoring for Fail-Safe operation (e.g., Class B)

- Calculate CRC over any portion of Flash or EEPROM

- High-speed or background operation

- Hardware Limit Timer (TMR2/4/6+HLT):

- Hardware monitoring and Fault detection

- · Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Data Signal Modulator (DSM)

## **Analog Peripherals**

- 10-Bit Analog-to-Digital Converter with Computation (ADC<sup>2</sup>):

- 24 external channels

- Conversion available during Sleep

- Four internal analog channels

- Internal and external trigger options

- Automated math functions on input signals:

- averaging, filter calculations, oversampling and threshold comparison

- Hardware Capacitive Voltage Divider (CVD) Support:

- 8-bit precharge timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- · Zero-Cross Detect (ZCD):

- Detect when AC signal on pin crosses ground

- 5-Bit Digital-to-Analog Converter (DAC):

- Output available externally

- Programmable 5-bit voltage (% of VDD)

- Internal connections to comparators, Fixed Voltage Reference and ADC

- Two Comparators (CMP):

- Four external inputs

- External output via PPS

- Fixed Voltage Reference (FVR) module:

- 1.024V, 2.048V and 4.096V output levels

## **Clocking Structure**

- High-Precision Internal Oscillator Block (HFINTOSC):

- Selectable frequency range up to 64 MHz

- ±1% at calibration

- 32 kHz Low-Power Internal Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- · External Oscillator Block:

- Three crystal/resonator modes

- 4x PLL with external sources

- · Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- · Oscillator Start-up Timer (OST)

## **Programming/Debug Features**

- · In-Circuit Debug Integrated On-Chip

- In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

### 6.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- · Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

Note:

The PIC18LF2x/4xK40 devices do not have a configurable Low-Power Sleep mode. PIC18LF2x/4xK40 devices are unregulated and are always in the lowest power state when in Sleep, with no wake-up time penalty. These devices have a lower maximum VDD and I/O voltage than the PIC18F2x/4xK40. See **Section 37.0 "Electrical Specifications"** for more information.

#### 6.2.4 IDLE MODE

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

Note:

If <u>CLKOUTEN</u> is enabled (<u>CLKOUTEN</u> = 0, Configuration Word 1H), the output will continue operating while in Idle.

### 6.2.4.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can reenter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

### 6.2.4.2 Idle and WWDT

When in Idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Note:

The WDT can bring the device out of Idle, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

# 6.3 Peripheral Operation in Power Saving Modes

All selected clock sources and the peripherals running off them are active in both IDLE and DOZE mode. Only in Sleep mode, both the Fosc and Fosc/4 clocks are unavailable. All the other clock sources are active, if enabled manually or through peripheral clock selection before the part enters Sleep.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, roll-overs of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

## 10.6.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 10.7 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

# 10.7.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

# 10.7.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 10-7.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 35.2.1** "Extended Instruction Syntax".

TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|---------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   | _      | _      | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIE0   | _        | _         | TMR0IE | IOCIE  | _      | INT2IE  | INT1IE  | INT0IE  | 175                 |

| PIE1   | OSCFIE   | CSWIE     | _      | _      | _      | _       | ADTIE   | ADIE    | 176                 |

| PIE2   | HLVDIE   | ZCDIE     | _      | _      | _      | _       | C2IE    | C1IE    | 177                 |

| PIE3   | _        | _         | RC1IE  | TX1IE  | _      | _       | BCL1IE  | SSP1IE  | 178                 |

| PIE4   | _        | _         | TMR6IE | TMR5IE | TMR4IE | TMR3IE  | TMR2IE  | TMR1IE  | 179                 |

| PIE5   | _        | _         | _      | _      | _      | TMR5GIE | TMR3GIE | TMR1GIE | 180                 |

| PIE6   | _        | _         | _      | _      | _      | _       | CCP2IE  | CCP1IE  | 181                 |

| PIE7   | SCANIE   | CRCIE     | NVMIE  | _      | _      | _       | _       | CWG1IE  | 182                 |

| PIR0   | _        | _         | TMR0IF | IOCIF  | _      | INT2IF  | INT1IF  | INT0IF  | 167                 |

| PIR1   | OSCFIF   | CSWIF     | _      | _      | _      | _       | ADTIF   | ADIF    | 168                 |

| PIR2   | HLVDIF   | ZCDIF     | _      | _      | _      | _       | C2IF    | C1IF    | 169                 |

| PIR3   | _        | _         | RC1IF  | TX1IF  | _      | _       | BCL1IF  | SSP1IF  | 170                 |

| PIR4   | _        | _         | TMR6IF | TMR5IF | TMR4IF | TMR3IF  | TMR2IF  | TMR1IF  | 171                 |

| PIR5   | _        | _         | _      | _      | _      | TMR5GIF | TMR3GIF | TMR1GIF | 172                 |

| PIR6   | _        | _         | _      | _      | _      | _       | CCP2IF  | CCP1IF  | 173                 |

| PIR7   | SCANIF   | CRCIF     | NVMIF  | _      | _      | _       | _       | CWG1IF  | 174                 |

| IPR0   | _        | _         | TMR0IP | IOCIP  | _      | INT2IP  | INT1IP  | INT0IP  | 183                 |

| IPR1   | OSCFIP   | CSWIP     | _      | _      | _      | _       | ADTIP   | ADIP    | 184                 |

| IPR2   | HLVDIP   | ZCDIP     | _      | _      | _      | _       | C2IP    | C1IP    | 185                 |

| IPR3   | _        | _         | RC1IP  | TX1IP  | _      | _       | BCL1IP  | SSP1IP  | 186                 |

| IPR4   | _        | _         | TMR6IP | TMR5IP | TMR4IP | TMR3IP  | TMR2IP  | TMR1IP  | 187                 |

| IPR5   | _        | _         | _      | _      | _      | TMR5GIP | TMR3GIP | TMR1GIP | 188                 |

| IPR6   | _        | _         | _      | _      | -      | _       | CCP2IP  | CCP1IP  | 189                 |

| IPR7   | SCANIP   | CRCIP     | NVMIP  | _      | _      | _       | _       | CWG1IP  | 190                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for Interrupts.

**TABLE 16-1: IOC REGISTERS**

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|-----------------------|--------|--------|--------|

| IOCAP | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3                | IOCAP2 | IOCAP1 | IOCAP0 |

| IOCAN | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3                | IOCAN2 | IOCAN1 | IOCAN0 |

| IOCAF | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3                | IOCAF2 | IOCAF1 | IOCAF0 |

| IOCBP | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3                | IOCBP2 | IOCBP1 | IOCBP0 |

| IOCBN | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3                | IOCBN2 | IOCBN1 | IOCBN0 |

| IOCBF | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3                | IOCBF2 | IOCBF1 | IOCBF0 |

| IOCCP | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3                | IOCCP2 | IOCCP1 | IOCCP0 |

| IOCCN | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3                | IOCCN2 | IOCCN1 | IOCCN0 |

| IOCCF | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3                | IOCCF2 | IOCCF1 | IOCCF0 |

| IOCEP | _      | _      | _      | _      | IOCEP3 <sup>(1)</sup> | _      | _      | _      |

| IOCEN |        | _      | _      | _      | IOCEN3 <sup>(1)</sup> | _      | -      | _      |

| IOCEF | _      | _      | _      | _      | IOCEF3 <sup>(1)</sup> | _      | _      | _      |

Note 1: If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC on RE3 is not available.

TABLE 16-2: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   | _      | _      | INT2EDG | INT1EDG | INT0EDG | 166              |

| IOCxF  | IOCxF7   | IOCxF6    | IOCxF5 | IOCxF4 | IOCxF3 | IOCxF2  | IOCxF1  | IOCxF0  | 206              |

| IOCxN  | IOCxN7   | IOCxN6    | IOCxN5 | IOCxN4 | IOCxN3 | IOCxN2  | IOCxN1  | IOCxN0  | 206              |

| IOCxP  | IOCxP7   | IOCxP6    | IOCxP5 | IOCxP4 | IOCxP3 | IOCxP2  | IOCxP1  | IOCxP0  | 206              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

## 20.4 Timer2 Interrupt

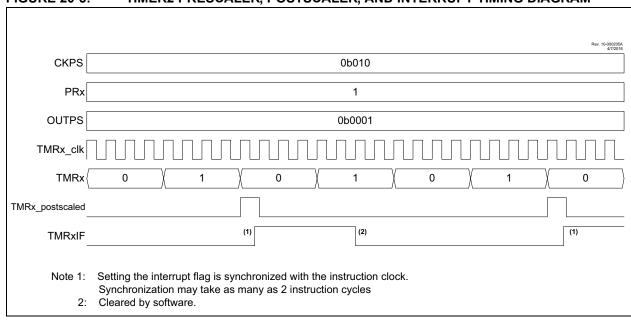

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 20-3.

FIGURE 20-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

| Name     | Bit 7    | Bit 6                                       | Bit 5     | Bit 4       | Bit 3       | Bit 2       | Bit 1   | Bit 0   | Register on Page |

|----------|----------|---------------------------------------------|-----------|-------------|-------------|-------------|---------|---------|------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL                                   | IPEN      | -           | _           | INT2EDG     | INT1EDG | INT0EDG | 166              |

| PIE6     | _        | -                                           | _         | _           | _           | _           | CCP2IE  | CCP1IE  | 181              |

| PIR6     | _        | _                                           | _         | _           | _           | _           | CCP2IF  | CCP1IF  | 173              |

| IPR6     | _        |                                             |           | _           | _           | _           | CCP2IP  | CCP1IP  | 189              |

| PMD3     | _        | _                                           |           | _           | PWM4MD      | PWM3MD      | CCP2MD  | CCP1MD  | 67               |

| CCPxCON  | EN       | _                                           | OUT       | FMT         |             | MODE        | E<3:0>  |         | 262              |

| CCPxCAP  | ı        | -                                           | ı         | ı           | _           | 1           | CTS<    | <1:0>   | 265              |

| CCPRxL   |          |                                             |           |             | CCPRx<7:0>  |             |         |         | 265              |

| CCPRxH   |          |                                             |           | (           | CCPRx<15:8> |             |         |         | 266              |

| CCPTMRS  | P4TSE    | P4TSEL<1:0> P3TSEL<1:0> C2TSEL<1:0> C1TSEL< |           | P3TSEL<1:0> |             | L<1:0>      | 264     |         |                  |

| CCPxPPS  | ı        | -                                           | ı         |             |             | CCPxPPS<4:0 | >       |         | 211              |

| RxyPPS   | _        | -                                           | _         |             |             | RxyPPS<4:0> | •       |         | 213              |

| T1CON    | _        | -                                           | T1CKP     | S<1:0>      | _           | T1SYNC      | T1RD16  | TMR10N  | 223              |

| T1GCON   | TMR1GE   | T1GPOL                                      | T1GTM     | T1GSPM      | T1GO/DONE   | T1GVAL      | _       | _       | 224              |

| T1CLK    | 1        | -                                           | 1         | ı           |             | CS<         | :3:0>   |         | 225              |

| T1GATE   | _        | -                                           | _         | _           |             | GSS         | <3:0>   |         | 226              |

| TMR1L    | TMR1L7   | TMR1L6                                      | TMR1L5    | TMR1L4      | TMR1L3      | TMR1L2      | TMR1L1  | TMR1L0  | 227              |

| TMR1H    | TMR1H7   | TMR1H6                                      | TMR1H5    | TMR1H4      | TMR1H3      | TMR1H2      | TMR1H1  | TMR1H0  | 227              |

| TMR2     |          |                                             |           |             | TMR2<7:0>   |             |         |         | 238*             |

| T2PR     |          |                                             |           |             | PR2<7:0>    |             |         |         | 238*             |

| T2CON    | ON       |                                             | CKPS<2:0> |             |             | OUTP        | S<3:0>  |         | 256              |

| T2HLT    | PSYNC    | CPOL                                        | CSYNC     |             |             | MODE<4:0>   |         |         | 257              |

| T2CLKCON |          |                                             |           | _           | CS<3:0>     |             |         |         | 258              |

| T2RST    | _        | _                                           | _         | _           |             | RSEL        | .<3:0>  |         | 259              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

<sup>\*</sup> Not a physical register.

## **EQUATION 23-2: R-C CALCULATIONS**

VPEAK = External voltage source peak voltage

f = External voltage source frequency

C = Series capacitor

R = Series resistor

V<sub>c</sub> = Peak capacitor voltage

Φ = Capacitor induced zero crossing phase advance in radians

$T_{\Phi}\,$  = Time ZC event occurs before actual zero crossing

$$Z = \frac{VPEAK}{3 \times 10^{-4}}$$

$$XC = \frac{1}{2\pi fC}$$

$$R = \sqrt{Z^2 - Xc^2}$$

$$VC = XC(3 \times 10^{-4})$$

$$\Phi = \operatorname{Tan}^{-1}\left(\frac{XC}{R}\right)$$

$$T\Phi = \frac{\Phi}{2\pi f}$$

## **EXAMPLE 23-1: R-C CALCULATIONS**

VRMS = 120

VPEAK = VRMS \* $\sqrt{2}$  = 169.7

f = 60 Hz

$C = 0.1 \, \mu F$

$$Z = \frac{V_{PEAK}}{3 \times 10^{-4}} = \frac{169.7}{3 \times 10^{-4}} = 565.7 \text{k}\Omega$$

$$X_{C} = \frac{1}{2\pi fC} = \frac{1}{(2\pi \times 60 \times 1 \times 10^{-7})} = 26.53 \text{k}\Omega$$

$$R = \sqrt{(Z^2 \times XC^2)} = 565.1k\Omega$$

(computed)

$$R = 560k\Omega \text{ (used)}$$

$$ZR = \sqrt{R^2 + Xc^2} = 560.6k\Omega$$

(using actual resistor)

IPEAK =

$$\frac{VPEAK}{ZR} = 302.7 \times 10^{-6}$$

$$VC = XC \times Ipeak = 8.0V$$

$$\Phi = \operatorname{Tan}^{-1}\left(\frac{XC}{R}\right) = 0.047 \text{ radians}$$

$$T\Phi = \frac{\Phi}{2\pi f} = 125.6 \mu s$$

# 23.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 23-3.

## **EQUATION 23-3: ZCD EVENT OFFSET**

When External Voltage Source is relative to Vss:

$$Toffset = \frac{asin\left(\frac{VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$Toffset = \frac{asin\left(\frac{VDD - VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 23-4.

#### **EQUATION 23-4: ZCD PULL-UP/DOWN**

When External Signal is relative to Vss:

$$RPULLUP = \frac{RSERIES(VPULLUP - VCPINV)}{VCPINV}$$

When External Signal is relative to VDD:

$$RPULLDOWN = \frac{RSERIES(VCPINV)}{(VDD - VCPINV)}$$

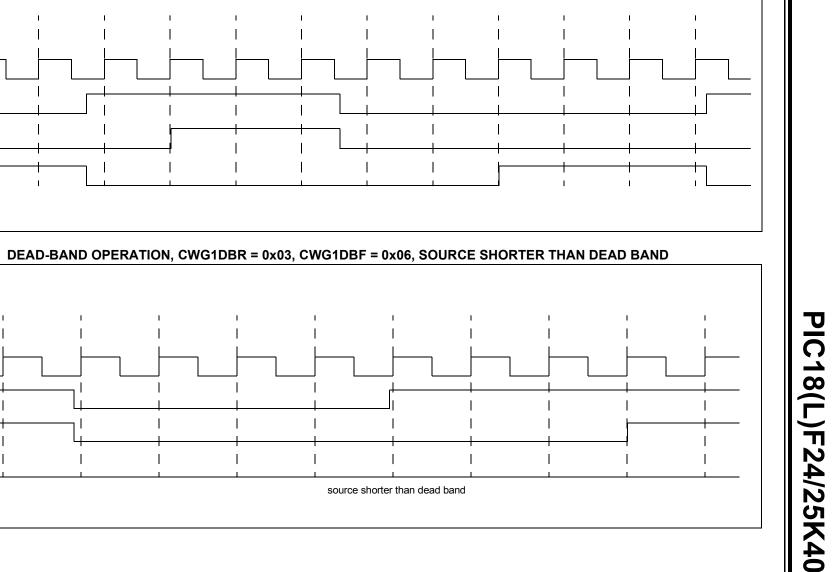

FIGURE 24-12:

cwg\_clock

Input Source

CWGxA

CWGxB

FIGURE 24-13:

cwg\_clock

Input Source

**CWGxA**

CWGxB

DEAD-BAND OPERATION, CWG1DBR = 0x01, CWG1DBF = 0x02

# REGISTER 24-2: CWG1CON1: CWG CONTROL REGISTER 1

| U-0   | U-0 | R-x | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | IN  | _   | POLD    | POLC    | POLB    | POLA    |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 5   | IN: CWG Input Value bit (read-only)    |

| bit 4   | Unimplemented: Read as '0'             |

| bit 3   | POLD: CWG1D Output Polarity bit        |

|         | 1 = Signal output is inverted polarity |

|         | 0 = Signal output is normal polarity   |

| bit 2   | POLC: CWG1C Output Polarity bit        |

|         | 1 = Signal output is inverted polarity |

|         | 0 = Signal output is normal polarity   |

| bit 1   | POLB: CWG1B Output Polarity bit        |

|         | 1 = Signal output is inverted polarity |

|         | 0 = Signal output is normal polarity   |

| bit 0   | POLA: CWG1A Output Polarity bit        |

|         | 1 = Signal output is inverted polarity |

|         | 0 = Signal output is normal polarity   |

### REGISTER 24-3: CWG1CLKCON: CWG1 CLOCK INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-----|---------|

| _     | _   | _   | _   | _   | _   |     | CS      |

| bit 7 |     |     |     |     |     |     | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-1 **Unimplemented:** Read as '0'

bit 0 CS: CWG Clock Source Selection Select bits

| cs | Clock Source                              |

|----|-------------------------------------------|

| 1  | HFINTOSC (remains operating during Sleep) |

| 0  | Fosc                                      |

### REGISTER 24-4: CWG1ISM: CWGx INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | _   | _   |         | ISM<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-3 **Unimplemented** Read as '0'

bit 2-0 ISM<2:0>: CWG Data Input Selection Multiplexer Select bits

| ISM<2:0> | Input Source            |

|----------|-------------------------|

| 111      | DSM OUT                 |

| 110      | CMP2 OUT                |

| 101      | CMP1 OUT                |

| 100      | PWM4 OUT                |

| 011      | PWM3 OUT                |

| 010      | CCP2 OUT                |

| 001      | CCP1 OUT                |

| 000      | Pin selected by CWG1PPS |

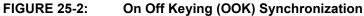

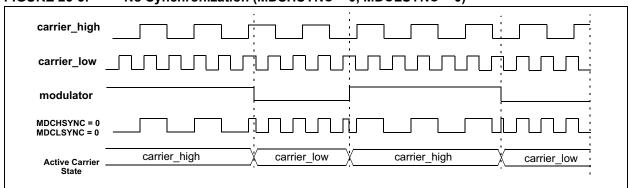

## FIGURE 25-3: No Synchronization (MDSHSYNC = 0, MDCLSYNC = 0)

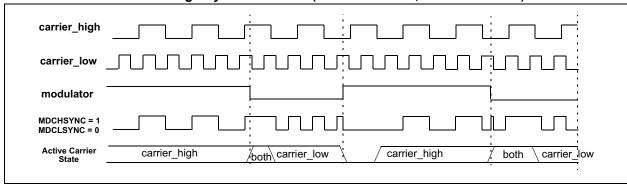

## FIGURE 25-4: Carrier High Synchronization (MDSHSYNC = 1, MDCLSYNC = 0)

# 26.8 I<sup>2</sup>C Mode Operation

All MSSP  $I^2C$  communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external  $I^2C$  devices.

#### 26.8.1 BYTE FORMAT

All communication in I<sup>2</sup>C is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

# 26.8.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

### 26.8.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

- **Note 1:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

- 2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPxDATPPS registers. The SCL input is selected with the SSPxCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

### 26.8.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

### TABLE 26-2: I<sup>2</sup>C BUS TERMS

| TERM                | Description                                                                                                                                                                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                      |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                       |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                            |

| Slave               | The device addressed by the master.                                                                                                                                                 |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                   |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                 |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                              |

| Idle                | No master is controlling the bus, and both SDA and SCL lines are high.                                                                                                              |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                        |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                        |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                 |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                |

| Read Request        | Master sends an address byte with the R/W bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                       |

| Bus Collision       | Any time the SDA line is sampled low by the module while it is outputting and expected high state.                                                                                  |

# 27.1 Register Definitions: EUSART Control

### REGISTER 27-1: TXxSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0 | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-1/1 | R/W-0/0 |

|--------|---------|---------------------|---------|---------|---------|-------|---------|

| CSRC   | TX9     | TXEN <sup>(1)</sup> | SYNC    | SENDB   | BRGH    | TRMT  | TX9D    |

| bit 7  |         |                     |         |         |         |       | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 **TX9:** 9-bit Transmit Enable bit

1 = Selects 9-bit transmission0 = Selects 8-bit transmission

bit 5 **TXEN:** Transmit Enable bit<sup>(1)</sup>

1 = Transmit enabled 0 = Transmit disabled

bit 4 SYNC: EUSART Mode Select bit

1 = Synchronous mode0 = Asynchronous mode

bit 3 SENDB: Send Break Character bit

Asynchronous mode:

1 = Send Sync Break on next transmission (cleared by hardware upon completion)

0 = Sync Break transmission disabled or completed

Synchronous mode:

Don't care

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed, if BRG16 = 1, baud rate is baudclk/4; else baudclk/16

0 = Low speed

Synchronous mode:

Unused in this mode

bit 1 **TRMT:** Transmit Shift Register Status bit

1 = TSR empty 0 = TSR full

bit 0 **TX9D:** Ninth bit of Transmit Data

Can be address/data bit or a parity bit.

Note 1: SREN/CREN bits of RCxSTA (Register 27-2) override TXEN in Sync mode.

### REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

| R-x   | R-x        | R-x | R-x | R-x | R-x | R-x | R-x   |

|-------|------------|-----|-----|-----|-----|-----|-------|

|       | ADERR<7:0> |     |     |     |     |     |       |

| bit 7 |            |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 23-1 for more details.

#### REGISTER 31-28: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<15:8> |         |         |         |         |         |         |         |

| bit 7       |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<15:8>**: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

## REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<7:0>  |         |         |         |         |         |         |         |

| bit 7 bit ( |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<7:0>**: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

## 32.4 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 37-15 for more information.

## 32.5 Timer1/3/5 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1/3/5. See **Section 19.8 "Timer1/3/5 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

# 32.5.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the SYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 32-2) and the Timer1 Block Diagram (Figure 19-1) for more information.

## 32.6 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- · EN and POL bits of the CMxCON0 register

- · CxIE bit of the PIE2 register

- INTP bit of the CMxCON1 register (for a rising edge detection)

- INTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

Note:

Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxEN bit of the CMxCON0 register.

# 32.7 Comparator Positive Input Selection

Configuring the PCH<2:0> bits of the CMxPCH register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN0+, CxIN1+ analog pin

- · DAC output

- FVR (Fixed Voltage Reference)

- · AVss (Ground)

See Section 28.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxEN = 0), all comparator inputs are disabled.

# 32.8 Comparator Negative Input Selection

The NCH<2:0> bits of the CMxNCH register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN0-, CxIN1-, CxIN2-, CxIN3- analog pin

- FVR (Fixed Voltage Reference)

- · Analog Ground

Note:

To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

# 33.10 Register Definitions: HLVD Control

Long bit name prefixes for the HLVD peripheral is shown in Table 33-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

## **TABLE 33-1:**

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| HLVD       | HLVD            |

### REGISTER 33-1: HLVDCON1: LOW-VOLTAGE DETECT CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   |         | SEL     | <3:0>   |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared u = Bit is unchanged

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **SEL<3:0>:** High/Low Voltage Detection Limit Selection bits

| SEL<3:0> | Typical Voltage |

|----------|-----------------|

| 1111     | Reserved        |

| 1110     | 4.63V           |

| 1101     | 4.32V           |

| 1100     | 4.12V           |

| 1011     | 3.91V           |

| 1010     | 3.71V           |

| 1001     | 3.60V           |

| 1000     | 3.4V            |

| 0111     | 3.09V           |

| 0110     | 2.88V           |

| 0101     | 2.78V           |

| 0100     | 2.57V           |

| 0011     | 2.47V           |

| 0010     | 2.26V           |

| 0001     | 2.06V           |

| 0000     | 1.85V           |

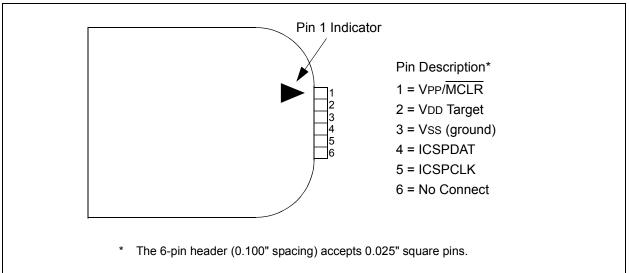

FIGURE 34-2: PICkit™ PROGRAMMER STYLE CONNECTOR INTERFACE

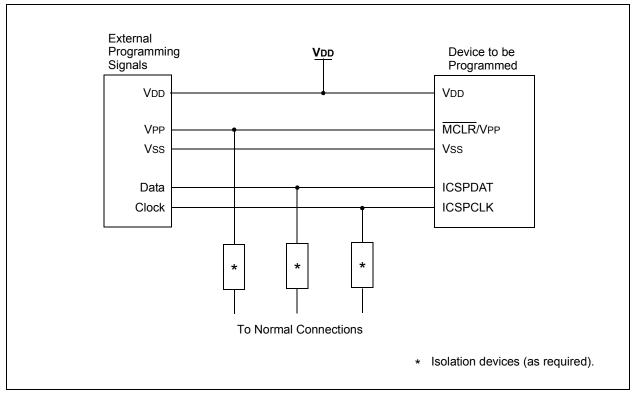

FIGURE 34-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

# 37.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:

$\begin{array}{ll} \text{Operating Voltage:} & \text{VDDMIN} \leq \text{VDD} \leq \text{VDDMAX} \\ \text{Operating Temperature:} & \text{Ta\_MIN} \leq \text{Ta} \leq \text{Ta\_MAX} \end{array}$

## VDD — Operating Supply Voltage<sup>(1)</sup>

PIC18LF24/25K40

| FIG TOLF24/25R4U                         |   |

|------------------------------------------|---|

| VDDMIN (Fosc ≤ 16 MHz)+1.8               | / |

| VDDMIN (Fosc ≤ 32 MHz)+2.5               | / |

| VDDMIN (Fosc ≤ 64 MHz)+3.0\              | / |

| VDDMAX                                   | / |

| PIC18F24/25K40                           |   |

| VDDMIN (Fosc ≤ 16 MHz)+2.3               | / |

| VDDMIN (Fosc ≤ 32 MHz)+2.5               | / |

| VDDMIN (Fosc ≤ 64 MHz)+3.0'              | / |

| VDDMAX                                   | / |

| TA — Operating Ambient Temperature Range |   |

| Industrial Temperature                   |   |

| TA_MIN40°0                               | 2 |

| Ta_max+85°0                              | 2 |

| Extended Temperature                     |   |

| TA_MIN40°0                               |   |

| TA_MAX+125°C                             | 2 |

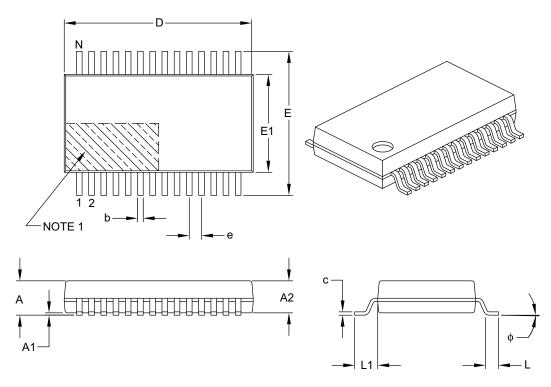

# 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |       |       |

|--------------------------|-------|-------------|-------|-------|

| Dimension Limits         |       | MIN         | NOM   | MAX   |

| Number of Pins           | N     | 28          |       |       |

| Pitch                    | е     | 0.65 BSC    |       |       |

| Overall Height           | Α     | _           | _     | 2.00  |

| Molded Package Thickness | A2    | 1.65        | 1.75  | 1.85  |

| Standoff                 | A1    | 0.05        | _     | _     |

| Overall Width            | Е     | 7.40        | 7.80  | 8.20  |

| Molded Package Width     | E1    | 5.00        | 5.30  | 5.60  |

| Overall Length           | D     | 9.90        | 10.20 | 10.50 |

| Foot Length              | L     | 0.55        | 0.75  | 0.95  |

| Footprint                | L1    | 1.25 REF    |       |       |

| Lead Thickness           | С     | 0.09        | _     | 0.25  |

| Foot Angle               | ф     | 0°          | 4°    | 8°    |

| Lead Width               | b     | 0.22        | _     | 0.38  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- $2. \ \ Dimensions \ D \ and \ E1 \ do \ not include \ mold \ flash \ or \ protrusions. \ Mold \ flash \ or \ protrusions \ shall \ not \ exceed \ 0.20 \ mm \ per \ side.$

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B