Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k40-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: DEVICE FEATURES

| Features                                                                         | PIC18(L)F24K40                                                                                     | PIC18(L)F25K40                                                          |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| Program Memory (Bytes)                                                           | 16384                                                                                              | 32768                                                                   |  |  |  |

| Program Memory (Instructions)                                                    | 8192                                                                                               | 16384                                                                   |  |  |  |

| Data Memory (Bytes)                                                              | 1024                                                                                               | 2048                                                                    |  |  |  |

| Data EEPROM Memory (Bytes)                                                       | 256                                                                                                | 256                                                                     |  |  |  |

| I/O Ports                                                                        | A,B,C,E <sup>(1)</sup>                                                                             | A,B,C,E <sup>(1)</sup>                                                  |  |  |  |

| Capture/Compare/PWM Modules (CCP)                                                | 2                                                                                                  | 2                                                                       |  |  |  |

| 10-Bit Pulse-Width Modulator (PWM)                                               | 2                                                                                                  | 2                                                                       |  |  |  |

| 10-Bit Analog-to-Digital Module (ADC <sup>2</sup> ) with Computation Accelerator | 4 internal<br>24 external                                                                          | 4 internal<br>24 external                                               |  |  |  |

| Packages                                                                         | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN                            | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN |  |  |  |

| Interrupt Sources                                                                | 36                                                                                                 |                                                                         |  |  |  |

| Timers (16-/8-bit)                                                               | 4/3                                                                                                |                                                                         |  |  |  |

| Serial Communications                                                            | 1 MSSP,<br>1 EUSART                                                                                |                                                                         |  |  |  |

| Enhanced Complementary Waveform Generator (ECWG)                                 |                                                                                                    | 1                                                                       |  |  |  |

| Zero-Cross Detect (ZCD)                                                          | 1                                                                                                  |                                                                         |  |  |  |

| Data Signal Modulator (DSM)                                                      | 1                                                                                                  |                                                                         |  |  |  |

| Peripheral Pin Select (PPS)                                                      | Yes                                                                                                |                                                                         |  |  |  |

| Peripheral Module Disable (PMD)                                                  | Yes                                                                                                |                                                                         |  |  |  |

| 16-bit CRC with NVMSCAN                                                          | Yes                                                                                                |                                                                         |  |  |  |

| Programmable High/Low-Voltage Detect (HLVD)                                      | Yes                                                                                                |                                                                         |  |  |  |

| Programmable Brown-out Reset (BOR)                                               | Y                                                                                                  | es                                                                      |  |  |  |

| Resets (and Delays)                                                              | POR, BOR,<br>RESET Instruction,<br>Stack Overflow,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR, WDT |                                                                         |  |  |  |

| Instruction Set                                                                  | 75 Instructions;<br>83 with Extended Instruction Set enabled                                       |                                                                         |  |  |  |

| Operating Frequency                                                              | DC – 6                                                                                             | 64 MHz                                                                  |  |  |  |

**Note 1:** PORTE contains the single RE3 input-only pin.

# 4.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 4.1 Overview

The oscillator module has multiple clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 (Register 3-1) determine the type of oscillator that will be used when the device runs after Reset, including when it is first powered up.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 100 kHz)

- 2. ECM External Clock Medium Power mode (100 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 8 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 4-1). Multiple device clock frequencies may be derived from these clock sources.

| Address | Name       | Bit 7    | Bit 6  | Bit 5      | Bit 4  | Bit 3    | Bit 2      | Bit 1       | Bit 0   | <u>Value on</u><br>POR, BOR |

|---------|------------|----------|--------|------------|--------|----------|------------|-------------|---------|-----------------------------|

| F4Dh    | SCANHADRH  |          |        |            | HADF   | R<15:8>  |            |             |         | 11111111                    |

| F4Ch    | SCANHADRL  |          |        |            | HAD    | R<7:0>   |            |             |         | 11111111                    |

| F4Bh    | SCANLADRU  | _        | _      |            |        | LADR     | <21:16>    |             |         | 000000                      |

| F4Ah    | SCANLADRH  |          |        | LADR<15:8> |        |          |            |             |         | 00000000                    |

| F49h    | SCANLADRL  |          |        |            | LAD    | R<7:0>   |            |             |         | 00000000                    |

| F48h    | CWG1STR    | OVRD     | OVRC   | OVRB       | OVRA   | STRD     | STRC       | STRB        | STRA    | 00000000                    |

| F47h    | CWG1AS1    | _        | _      | AS5E       | AS4E   | AS3E     | AS2E       | AS1E        | AS0E    | 000000                      |

| F46h    | CWG1AS0    | SHUTDOWN | REN    | LSBE       | D<1:0> | LSAC     | C<1:0>     | —           | —       | 000101                      |

| F45h    | CWG1CON1   | _        | _      | IN         | —      | POLD     | POLC       | POLB        | POLA    | x-0000                      |

| F44h    | CWG1CON0   | EN       | LD     | _          | _      | -        |            | MODE<2:0>   |         | 00000                       |

| F43h    | CWG1DBF    | _        | _      |            |        | DBF      | <5:0>      |             |         | 000000                      |

| F42h    | CWG1DBR    | _        | _      |            |        | DBF      | R<5:0>     |             |         | 000000                      |

| F41h    | CWG1ISM    | _        | _      | —          | —      | -        |            | ISM<2:0>    |         | 000                         |

| F40h    | CWG1CLKCON | _        | _      | _          | _      | —        | —          | _           | CS      | 0                           |

| F3Fh    | CLKRCLK    | _        | _      | _          | _      | _        | (          | LKRxCLK<2:  | 0>      | 000                         |

| F3Eh    | CLKRCON    | CLKREN   | _      | _          | CLKRE  | C<1:0>   |            | CLKRDIV<2:0 | >       | 010000                      |

| F3Dh    | CMOUT      | _        | _      | _          | _      | _        | _          | MC2OUT      | MC1OUT  | 00                          |

| F3Ch    | CM1PCH     | _        | _      | _          | _      | _        |            | PCH<2:0>    |         | 000                         |

| F3Bh    | CM1NCH     | _        | _      | _          | _      | _        | NCH<2:0>   |             | 000     |                             |

| F3Ah    | CM1CON1    | _        | _      | _          | _      | _        | _          | INTP        | INTN    | 100                         |

| F39h    | CM1CON0    | EN       | OUT    | _          | POL    | _        | _          | HYS         | SYNC    | 00-000                      |

| F38h    | CM2PCH     | —        | _      | _          | _      | _        |            | C2PCH<2:0>  | •       | 000                         |

| F37h    | CM2NCH     | _        | _      | _          | _      | _        |            | C2NCH<2:0>  | >       | 000                         |

| F36h    | CM2CON1    | _        | _      | _          | _      | _        | _          | INTP        | INTN    | 100                         |

| F35h    | CM2CON0    | EN       | OUT    | _          | POL    | _        | _          | HYS         | SYNC    | 00-000                      |

| F34h    | DAC1CON1   | —        | _      |            |        |          | DAC1R<4:0> |             |         | xxxxx                       |

| F33h    | DAC1CON0   | EN       | _      | OE1        | OE2    | PSS      | <1:0>      | _           | NSS     | 0-0000-0                    |

| F32h    | ZCDCON     | SEN      | _      | OUT        | POL    | _        | —          | INTP        | INTN    | 0-x000                      |

| F31h    | FVRCON     | FVREN    | FVRRDY | TSEN       | TSRNG  | CDAF     | /R<1:0>    | ADF\        | /R<1:0> | 0x000000                    |

| F30h    | HLVDCON1   | _        | —      | _          | _      |          | HLVDS      | EL<3:0>     |         | 0000                        |

| F2Fh    | HLVDCON0   | EN       | _      | OUT        | RDY    | -        | -          | INTH        | INTL    | 0-xx00                      |

| F2Eh    | —          |          |        |            | Unimp  | lemented |            |             | 1       | _                           |

| F2Dh    | WPUE       | —        | —      | -          | —      | WPUE3    | —          | —           | —       | 1                           |

| F2Ch    | —          |          |        |            | Unimp  | lemented |            | 1           | 1       | _                           |

| F2Bh    | —          |          |        |            | Unimp  | lemented |            |             |         | _                           |

| F2Ah    | INLVLE     | —        | _      | _          | —      | INLVLE3  | —          | —           | —       | 1                           |

| F29h    | IOCEP      | _        | _      | _          | _      | IOCEP3   | _          | _           | _       | 0                           |

| F28h    | IOCEN      | _        | _      | _          | _      | IOCEN3   | _          | _           | _       | 0                           |

| F27h    | IOCEF      | _        | _      | _          | _      | IOCEF3   | _          | _           | _       | 0                           |

#### TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

#### 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

#### 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6 and PIR7).

### 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6 and PIE7). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

### 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6 and IPR7). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### 20.7 Register Definitions: Timer2/4/6 Control

Long bit name prefixes for the Timer2/4/6 peripherals are shown in Table 20-2. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information. **TABLE 20-2:**

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer2     | T2              |

| Timer4     | T4              |

| Timer6     | Т6              |

| Name     | Bit 7    | Bit 6     | Bit 5       | Bit 4       | Bit 3  | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|-------------|-------------|--------|------------|---------|---------|---------------------|

| CCPTMRS  | P4TSE    | L<1:0>    | P3TSE       | L<1:0>      | C2TSE  | L<1:0>     | C1TSE   | :L<1:0> | 280                 |

| PWM3CON  | EN       | _         | OUT         | POL         | _      | —          | _       | —       | 279                 |

| PWM3DCH  |          |           |             | DC<7        | :0>    |            |         |         | 281                 |

| PWM3DCL  | DC<      | 9:8>>     | _           | _           | _      | —          | _       | _       | 281                 |

| PWM4CON  | EN       | _         | OUT         | POL         | —      | _          | _       | _       | 279                 |

| PWM4DCH  |          |           |             | DC<7        | :0>    |            |         |         | 281                 |

| PWM4DCL  | DC<      | <9:8>     | _           | _           | _      | —          | _       | _       | 281                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN        | _           | —      | INT2EDG    | INT1EDG | INT0EDG | 166                 |

| PIE4     | _        | _         | TMR6IE      | TMR5IE      | TMR4IE | TMR3IE     | TMR2IE  | TMR1IE  | 179                 |

| PIR4     | _        | _         | TMR6IF      | TMR5IF      | TMR4IF | TMR3IF     | TMR2IF  | TMR1IF  | 171                 |

| IPR4     | _        | _         | TMR6IP      | TMR5IP      | TMR4IP | TMR3IP     | TMR2IP  | TMR1IP  | 187                 |

| RxyPPS   | _        | _         | _           | RxyPPS<4:0> |        |            |         | 213     |                     |

| TMR2     |          |           |             | TMR2<       | 7:0>   |            |         |         | 238*                |

| PR2      |          |           |             | PR2<7       | /:0>   |            |         |         | 238*                |

| T2CON    | T2ON     |           | T2CKPS<2:0> |             |        | T2OUTF     | PS<3:0> |         | 256                 |

| T2HLT    | T2PSYNC  | T2CPOL    | T2CSYNC     |             | T      | 2MODE<4:0> | •       |         | 257                 |

| T2CLKCON | _        | _         | _           | — T2CS<3:0> |        |            |         | 258     |                     |

| T2RST    | _        | —         | —           | —           |        | T2RSE      | L<3:0>  |         | 259                 |

| PMD3     |          | _         | _           |             | PWM4MD | PWM3MD     | CCP2MD  | CCP1MD  | 67                  |

#### TABLE 22-4: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM. \* Not a physical location.

| U-0                               | U-0               | U-0                                         | R/W-0/0                                            | R/W-0/0                                                                      | R/W-0/0                                                                                                                                                 | R/W-0/0                                                                                                                                                                              |  |  |

|-----------------------------------|-------------------|---------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                   | —                 | _                                           |                                                    | SRCS                                                                         | <3:0>                                                                                                                                                   |                                                                                                                                                                                      |  |  |

| •                                 |                   |                                             |                                                    |                                                                              |                                                                                                                                                         | bit 0                                                                                                                                                                                |  |  |

|                                   |                   |                                             |                                                    |                                                                              |                                                                                                                                                         |                                                                                                                                                                                      |  |  |

|                                   |                   |                                             |                                                    |                                                                              |                                                                                                                                                         |                                                                                                                                                                                      |  |  |

| R = Readable bit W = Writable bit |                   |                                             |                                                    | U = Unimplemented bit, read as '0'                                           |                                                                                                                                                         |                                                                                                                                                                                      |  |  |

| anged                             | x = Bit is unkn   | own                                         | -n/n = Value at POR and BOR/Value at all other Res |                                                                              |                                                                                                                                                         | ther Resets                                                                                                                                                                          |  |  |

|                                   | '0' = Bit is clea | ared                                        |                                                    |                                                                              |                                                                                                                                                         |                                                                                                                                                                                      |  |  |

|                                   | _                 | bit W = Writable I<br>anged x = Bit is unkn | bit W = Writable bit                               | bit W = Writable bit U = Unimpler<br>anged x = Bit is unknown -n/n = Value a | —     —     —     SRCS       bit     W = Writable bit     U = Unimplemented bit, read       anged     x = Bit is unknown     -n/n = Value at POR and BO | —     —     —     SRCS<3:0>       bit     W = Writable bit     U = Unimplemented bit, read as '0'       anged     x = Bit is unknown     -n/n = Value at POR and BOR/Value at all or |  |  |

#### REGISTER 25-5: MDSRC: MODULATION SOURCE CONTROL REGISTER

bit 7-4 Unimplemented: Read as '0'

bit 3-0 SRCS<3:0>: Modulator Source Selection bits See Table 25-3 for signal list

# TABLE 25-3:MDSRC SELECTION MUX<br/>CONNECTIONS

| MDSRCS<3:0> |    | Connection               |

|-------------|----|--------------------------|

| 1011-11     | 11 | Reserved                 |

| 1010        | 10 | MSSP1 - SDO              |

| 1001        | 9  | EUSART TX (TX/CK output) |

| 1000        | 8  | EUSART RX (DT output)    |

| 0111        | 7  | CMP2 OUT                 |

| 0110        | 6  | CMP1 OUT                 |

| 0101        | 5  | PWM4 OUT                 |

| 0100        | 4  | PWM3 OUT                 |

| 0011        | 3  | CCP2 OUT                 |

| 0010        | 2  | CCP1 OUT                 |

| 0001        | 1  | MDBIT                    |

| 0000        | 0  | Pin selected by MDSRCPPS |

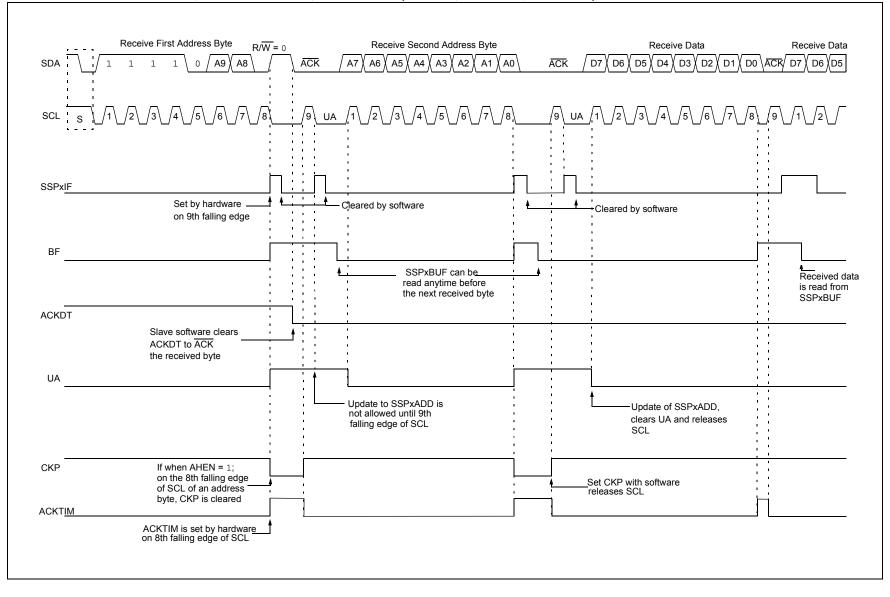

#### FIGURE 26-21: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0)

PIC18(L)F24/25K40

### 26.10 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: Master mode suspends Start/Stop detection when sending the Start/Stop condition by means of the SEN/PEN control bits. The SSPxIF bit is set at the end of the Start/Stop generation when hardware clears the control bit.

#### 26.10.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 26.11 "Baud Rate Generator"** for more detail.

#### 26.10.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 26-25).

### 27.2 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 27-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 27.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 27-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 27.2.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TXx/CKx I/O pin as an output. If the TXx/CKx pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 27.2.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one Tcy immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 27.2.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 27.5.1.2 "Clock Polarity**".

#### 27.2.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

### 31.0 ANALOG-TO-DIGITAL CONVERTER WITH COMPUTATION (ADC<sup>2</sup>) MODULE

The Analog-to-Digital Converter with Computation  $(ADC^2)$  allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair).

Additionally, the following features are provided within the ADC module:

- 8-bit Acquisition Timer

- Hardware Capacitive Voltage Divider (CVD) support:

- 8-bit precharge timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- · Automatic repeat and sequencing:

- Automated double sample conversion for CVD

- Two sets of result registers (Result and Previous result)

- Auto-conversion trigger

- Internal retrigger

- Computation features:

- Averaging and low-pass filter functions

- Reference comparison

- 2-level threshold comparison

- Selectable interrupts

Figure 31-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion and upon threshold comparison. These interrupts can be used to wake-up the device from Sleep.

| NEGF             | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operands:        | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operation:       | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Encoding:        | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  | complement. The result is placed in the data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| O Cycle Activity |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NOF       | •              | No Operation  |              |            |     |              |

|-----------|----------------|---------------|--------------|------------|-----|--------------|

| Synta     | ax:            | NOP           |              |            |     |              |

| Oper      | ands:          | None          |              |            |     |              |

| Oper      | ation:         | No operation  |              |            |     |              |

| Statu     | s Affected:    | None          |              |            |     |              |

| Encoding: |                | 0000<br>1111  | 0000<br>xxxx | 000<br>xxx | -   | 0000<br>xxxx |

| Desc      | ription:       | No operation. |              |            |     |              |

| Word      | ls:            | 1             |              |            |     |              |

| Cycle     | es:            | 1             |              |            |     |              |

| QC        | ycle Activity: |               |              |            |     |              |

|           | Q1             | Q2            | Q            | Q3         |     | Q4           |

|           | Decode         | No            |              | No         |     | No           |

|           |                | operation     | opera        | tion       | ope | ration       |

Example:

None.

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

> Before Instruction REG = 0011 1010 [3Ah] After Instruction REG = 1100 0110 [C6h]

© 2016-2017 Microchip Technology Inc.

#### 35.2.2 EXTENDED INSTRUCTION SET

| ADD   | FSR            | Add Lite                                | Add Literal to FSR                                                          |      |                 |  |  |  |

|-------|----------------|-----------------------------------------|-----------------------------------------------------------------------------|------|-----------------|--|--|--|

| Synta | ax:            | ADDFSR                                  | ADDFSR f, k                                                                 |      |                 |  |  |  |

| Oper  | ands:          | $0 \le k \le 63$<br>f $\in$ [ 0, 1, 2 ] |                                                                             |      |                 |  |  |  |

| Oper  | ation:         | FSR(f) + k                              | $x \rightarrow FSR($                                                        | f)   |                 |  |  |  |

| Statu | s Affected:    | None                                    |                                                                             |      |                 |  |  |  |

| Enco  | ding:          | 1110                                    | 1000                                                                        | ffkk | kkkk            |  |  |  |

| Desc  | ription:       |                                         | The 6-bit literal 'k' is added to the contents of the FSR specified by 'f'. |      |                 |  |  |  |

| Word  | ls:            | 1                                       | 1                                                                           |      |                 |  |  |  |

| Cycle | es:            | 1                                       |                                                                             |      |                 |  |  |  |

| QC    | ycle Activity: |                                         |                                                                             |      |                 |  |  |  |

|       | Q1             | Q2                                      | Q3                                                                          |      | Q4              |  |  |  |

|       | Decode         | Read<br>literal 'k'                     | Proce<br>Data                                                               |      | Write to<br>FSR |  |  |  |

|       |                |                                         |                                                                             |      |                 |  |  |  |

| Example: | ADDFSR | 2, | 23h |

|----------|--------|----|-----|

| Before Instru  | ction |       |

|----------------|-------|-------|

| FSR2           | =     | 03FFh |

| After Instruct | ion   |       |

| FSR2           | =     | 0422h |

| ADDULNK           | Add Literal to FSR2 and Return                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:           | ADDULNK k                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Operands:         | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Operation:        | $FSR2 + k \rightarrow FSR2$ ,                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                   | $(TOS) \rightarrow PC$                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Encoding:         | 1110 1000 11kk kkkk                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Description:      | The 6-bit literal 'k' is added to the<br>contents of FSR2. A RETURN is then<br>executed by loading the PC with the<br>TOS.<br>The instruction takes two cycles to<br>execute; a NOP is performed during<br>the second cycle.<br>This may be thought of as a special<br>case of the ADDFSR instruction,<br>where f = 3 (binary '11'); it operates<br>only on FSR2. |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| O Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

Q Cycle Activity:

| Q1        | Q2          | Q3        | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

Example: ADDULNK 23h

| Before Instruction |     |       |  |  |  |  |  |

|--------------------|-----|-------|--|--|--|--|--|

| FSR2               | =   | 03FFh |  |  |  |  |  |

| PC                 | =   | 0100h |  |  |  |  |  |

| After Instruct     | ion |       |  |  |  |  |  |

| FSR2               | =   | 0422h |  |  |  |  |  |

| PC                 | =   | (TOS) |  |  |  |  |  |

|                    |     |       |  |  |  |  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

| CALLW                                             | Subroutir                                                                                                                            | ne Call Using                                                                                                                                                                          | Using WREG MOVSF                                                                                                       |               | ′SF                                                                                                                      | Move Indexed to f                                                                                                                                                 |                                                                                                                                                                                                               |                                                                                                                                                               |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                           | CALLW                                                                                                                                |                                                                                                                                                                                        |                                                                                                                        | Synta         | IX:                                                                                                                      | MOVSF                                                                                                                                                             | [z <sub>s</sub> ], f <sub>d</sub>                                                                                                                                                                             |                                                                                                                                                               |  |

| Operands:                                         | None                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                        | Operation     | ands:                                                                                                                    | $0 \le z_s \le 12$                                                                                                                                                | 27                                                                                                                                                                                                            |                                                                                                                                                               |  |

| Operation:                                        | $(PC + 2) \rightarrow$                                                                                                               |                                                                                                                                                                                        |                                                                                                                        |               |                                                                                                                          | $0 \le f_d \le 40$                                                                                                                                                |                                                                                                                                                                                                               |                                                                                                                                                               |  |

|                                                   | $(W) \rightarrow PCL$<br>(PCLATH) -                                                                                                  |                                                                                                                                                                                        |                                                                                                                        | Operation     |                                                                                                                          | ((FSR2) +                                                                                                                                                         | $z_s) \rightarrow f_d$                                                                                                                                                                                        |                                                                                                                                                               |  |

|                                                   | (PCLATU) -                                                                                                                           |                                                                                                                                                                                        |                                                                                                                        |               | s Affected:                                                                                                              | None                                                                                                                                                              |                                                                                                                                                                                                               |                                                                                                                                                               |  |

| Status Affected:                                  | None                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                        | Enco<br>1st w | ding:<br>ord (source)                                                                                                    | 1110                                                                                                                                                              | 1011 Oz                                                                                                                                                                                                       | zz zzzz <sub>s</sub>                                                                                                                                          |  |

| Encoding:                                         | 0000                                                                                                                                 | 0000 000                                                                                                                                                                               | 01 0100                                                                                                                |               | vord (destin.)                                                                                                           | 1111                                                                                                                                                              |                                                                                                                                                                                                               | ff ffffd                                                                                                                                                      |  |

| Description                                       | pushed ont<br>contents of<br>existing val<br>contents of<br>latched into<br>respectively<br>executed as<br>new next in<br>Unlike CAL | turn address (<br>o the return sta<br>W are written<br>ue is discarded<br>PCLATH and<br>PCH and PCI<br>y. The second<br>s a NOP instruction is fet<br>L, there is no<br>Status or BSR. | ack. Next, the<br>to PCL; the<br>d. Then, the<br>PCLATU are<br>J,<br>cycle is<br>ction while the<br>ched.<br>option to | Desc          | ription:                                                                                                                 | moved to<br>actual add<br>determine<br>offset 'z <sub>s</sub> ' i<br>FSR2. The<br>register is<br>'f <sub>d</sub> ' in the s<br>can be an<br>space (00<br>The MOVS | nts of the sound<br>destination reg<br>ress of the sound<br>d by adding the<br>n the first word<br>a address of th<br>specified by th<br>econd word. B<br>ywhere in the 4<br>Dh to FFFh).<br>F instruction ca | ister 'f <sub>d</sub> '. The<br>ince register is<br>e 7-bit literal<br>to the value of<br>e destination<br>e 12-bit literal<br>oth addresses<br>096-byte data |  |

| Words:                                            | 1                                                                                                                                    |                                                                                                                                                                                        |                                                                                                                        |               |                                                                                                                          | PCL, TOS<br>destination                                                                                                                                           | U, TOSH or TO                                                                                                                                                                                                 | OSL as the                                                                                                                                                    |  |

| Cycles:                                           | 2                                                                                                                                    |                                                                                                                                                                                        |                                                                                                                        |               |                                                                                                                          |                                                                                                                                                                   | tant source ad                                                                                                                                                                                                | dress points t                                                                                                                                                |  |

| Q Cycle Activity:                                 |                                                                                                                                      |                                                                                                                                                                                        |                                                                                                                        |               |                                                                                                                          |                                                                                                                                                                   | addressing re<br>ned will be 00                                                                                                                                                                               | •                                                                                                                                                             |  |

| Q1                                                | Q2                                                                                                                                   | Q3                                                                                                                                                                                     | Q4                                                                                                                     | Word          | e.                                                                                                                       | 2                                                                                                                                                                 |                                                                                                                                                                                                               | 1.                                                                                                                                                            |  |

| Decode                                            | Read<br>WREG                                                                                                                         | PUSH PC to<br>stack                                                                                                                                                                    | No<br>operation                                                                                                        | Cycle         |                                                                                                                          | 2                                                                                                                                                                 |                                                                                                                                                                                                               |                                                                                                                                                               |  |

| No                                                | No                                                                                                                                   | No                                                                                                                                                                                     | No                                                                                                                     |               | cle Activity:                                                                                                            | -                                                                                                                                                                 |                                                                                                                                                                                                               |                                                                                                                                                               |  |

| operation                                         | operation                                                                                                                            | operation                                                                                                                                                                              | operation                                                                                                              | <u> </u>      | Q1                                                                                                                       | Q2                                                                                                                                                                | Q3                                                                                                                                                                                                            | Q4                                                                                                                                                            |  |

|                                                   |                                                                                                                                      |                                                                                                                                                                                        |                                                                                                                        |               | Decode                                                                                                                   | Determine                                                                                                                                                         | Determine                                                                                                                                                                                                     | Read                                                                                                                                                          |  |

| Example:                                          | HERE                                                                                                                                 | CALLW                                                                                                                                                                                  |                                                                                                                        |               | Decede                                                                                                                   | source add                                                                                                                                                        | -                                                                                                                                                                                                             | source reg                                                                                                                                                    |  |