Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k40-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

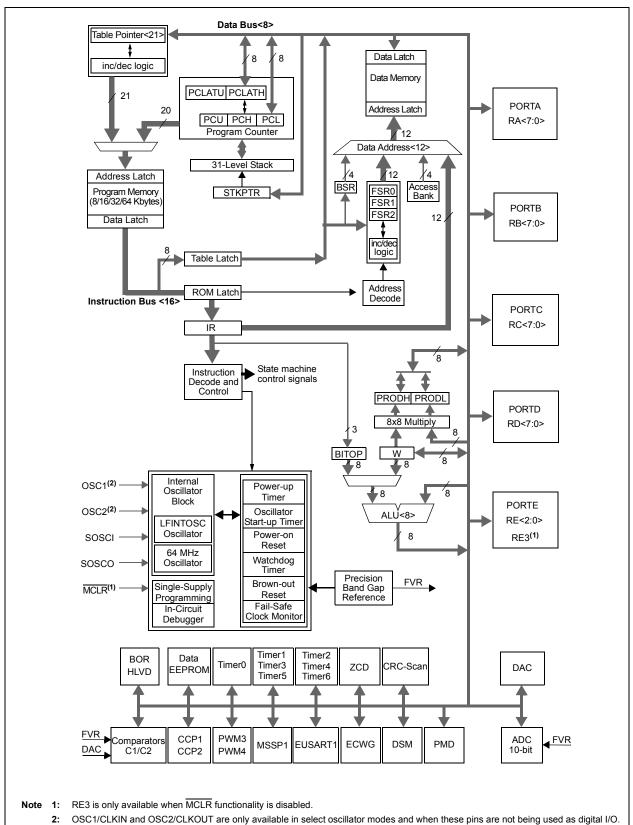

#### FIGURE 1-1: PIC18(L)F24/25K40 FAMILY BLOCK DIAGRAM

2: OSC1/CLKIN and OSC2/CLKOUT are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional information.

# 4.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL/M/H and Secondary Oscillator).

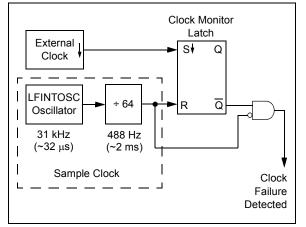

FIGURE 4-9: FSCM BLOCK DIAGRAM

# 4.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

### 4.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM overwrites the COSC bits to select HFINTOSC (3'b110). The frequency of HFINTOSC would be determined by the previous state of the HFFRQ bits and the NDIV/CDIV bits. The bit flag OSCFIF of the PIR1 register is set. Setting this flag will generate an interrupt if the OSCFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

## 4.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator or PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSCFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSCFIF flag will again become set by hardware.

### 9.2 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE<1:0> Configuration bits.

If WDTE = 2'blx, then the clock source will be enabled depending on the WDTCCS<2:0> Configuration bits.

If WDTE = 2'b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the WDTCS bits in the WDTCON1 register.

Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 37.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

#### 9.3 WWDT Operating Modes

The Windowed Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.3.1 WWDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WWDT is always on.

WWDT protection is active during Sleep.

#### 9.3.2 WWDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WWDT is on, except in Sleep.

WWDT protection is not active during Sleep.

#### 9.3.3 WWDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WWDT is controlled by the SEN bit of the WDTCON0 register.

WWDT protection is unchanged by Sleep. See Table 9-1 for more details.

| TABLE 9-1: | WWDT OPERATING MODES |

|------------|----------------------|

|------------|----------------------|

| WDTE<1:0> | SEN | Device<br>Mode | WWDT<br>Mode |

|-----------|-----|----------------|--------------|

| 11        | Х   | Х              | Active       |

| 1.0       | 37  | Awake          | Active       |

| 10        | Х   | Sleep          | Disabled     |

| 01        | 1   | Х              | Active       |

| UL        | 0   | Х              | Disabled     |

| 00        | Х   | Х              | Disabled     |

#### 9.4 Time-out Period

If the WDTCPS<4:0> Configuration bits default to 5 'b11111, then the WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). If any value other than the default value is assigned to WDTCPS<4:0> Configuration bits, then the timer period will be based on the WDTCPS<4:0> bits in the CONFIG3L register. After a Reset, the default time-out period is 2s.

#### 9.5 Watchdog Window

The Windowed Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 9-2 for an example.

The window size is controlled by the WINDOW<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

The five Most Significant bits of the WDTTMR register are used to determine whether the window is open, as defined by the WINDOW<2:0> bits of the WDTCON1 register.

In the event of a window violation, a Reset will be generated and the WDTWV bit of the PCON0 register will be cleared. This bit is set by a POR or can be set in firmware.

### 9.6 Clearing the WWDT

The WWDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- Device enters Sleep

- Exit Sleep by Interrupt

- WWDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1

registers

#### 9.6.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation regardless of whether the window is open or not.

See Table 9-2 for more information.

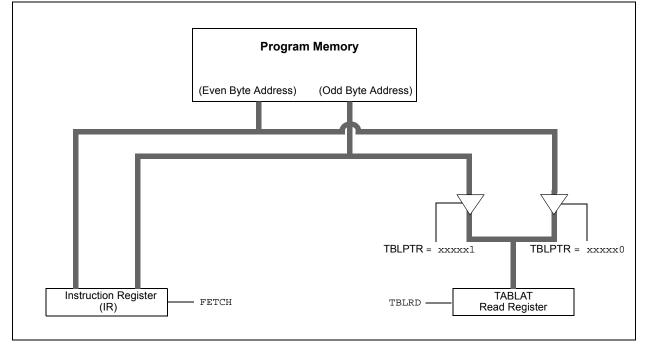

#### 11.1.3 READING THE PROGRAM FLASH MEMORY

The TBLRD instruction retrieves data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The CPU operation is suspended during the read, and it resumes immediately after. From the user point of view, TABLAT is valid in the next instruction cycle.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 11-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 11-4: READS FROM PROGRAM FLASH MEMORY

#### EXAMPLE 11-1: READING A PROGRAM FLASH MEMORY WORD

| MOVLW   | CODE_ADDR_UPPER                                                                  | ;                                                                                                                                                                            | Load TBLPTR with the base                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF   | TBLPTRU                                                                          | ;                                                                                                                                                                            | address of the word                                                                                                                                                                    |

| MOVLW   | CODE_ADDR_HIGH                                                                   |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVWF   | TBLPTRH                                                                          |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVLW   | CODE_ADDR_LOW                                                                    |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVWF   | TBLPTRL                                                                          |                                                                                                                                                                              |                                                                                                                                                                                        |

|         |                                                                                  |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+ |                                                                                  | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVF    | TABLAT, W                                                                        | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVWF   | WORD_EVEN                                                                        |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+ |                                                                                  | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVFW   | TABLAT, W                                                                        | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVF    | WORD ODD                                                                         |                                                                                                                                                                              |                                                                                                                                                                                        |

|         | MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>TBLRD*+<br>MOVF<br>TBLRD*+<br>MOVFW | MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+<br>MOVF TABLAT, W<br>MOVWF WORD_EVEN<br>TBLRD*+<br>MOVFW TABLAT, W | MOVWF TBLPTRU ;<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+ ;<br>MOVF TABLAT, W ;<br>MOVWF WORD_EVEN<br>TBLRD*+ ;<br>MOVFW TABLAT, W ; |

| R/W-0/0         | R/W-0/0                                          | R/W-0/0          | U-0      | U-0              | U-0              | U-0             | R/W-0/0 |

|-----------------|--------------------------------------------------|------------------|----------|------------------|------------------|-----------------|---------|

| SCANIE          | CRCIE                                            | NVMIE            | —        | —                | —                | —               | CWG1IE  |

| bit 7           | -                                                |                  |          | •                |                  |                 | bit 0   |

|                 |                                                  |                  |          |                  |                  |                 |         |

| Legend:         |                                                  |                  |          |                  |                  |                 |         |

| R = Readable    | bit                                              | W = Writable     | bit      | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at F | POR                                              | '1' = Bit is set |          | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7           | SCANIE: SC/<br>1 = Enabled<br>0 = Disabled       | AN Interrupt Er  | able bit |                  |                  |                 |         |

| bit 6           |                                                  | Interrupt Enab   | le bit   |                  |                  |                 |         |

| bit 5           | <b>NVMIE:</b> NVM<br>1 = Enabled<br>0 = Disabled | Interrupt Enab   | le bit   |                  |                  |                 |         |

| bit 4-1         | Unimplemen                                       | ted: Read as '   | כ'       |                  |                  |                 |         |

| bit 0           | -                                                | /G Interrupt En  |          |                  |                  |                 |         |

# REGISTER 14-17: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

#### 15.2.5 SLEW RATE CONTROL

The SLRCONx register (Register 15-7) controls the slew rate option for each port pin. Slew rate for each port pin can be controlled independently. When an SLRCONx bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONx bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 15.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 15-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-8 for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 15.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 15-5) controls the individual weak pull-ups for each port pin.

### 15.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins that are common between 28-pin and 40/44-pin devices. For further details about the IOC module refer to **Section 16.0 "Interrupt-on-Change**".

### 15.3 PORTE Registers

#### EXAMPLE 15-2: INITIALIZING PORTE

| CLRF  | PORTE  | ; | Initialize PORTE by   |

|-------|--------|---|-----------------------|

|       |        | ; | clearing output       |

|       |        | ; | data latches          |

| CLRF  | LATE   | ; | Alternate method      |

|       |        | ; | to clear output       |

|       |        | ; | data latches          |

| CLRF  | ANSELE | ; | Configure analog pins |

|       |        | ; | for digital only      |

| MOVLW | 05h    | ; | Value used to         |

|       |        | ; | initialize data       |

|       |        | ; | direction             |

| MOVWF | TRISE  | ; | Set RE<0> as input    |

|       |        | ; | RE<1> as output       |

|       |        | ; | RE<2> as input        |

|       |        |   |                       |

### 15.3.1 PORTE ON 28-PIN DEVICES

For PIC18(L)F2xK40 devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In this case, PORTE is a single bit, inputonly port comprised of RE3 only. The pin operates as previously described. RE3 in PORTE register is a readonly bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

#### 15.3.2 RE3 WEAK PULL-UP

The port RE3 pin has an individually controlled weak internal pull-up. When set, the WPUE3 bit enables the RE3 pin pull-up. When the RE3 port pin is configured as MCLR, (CONFIG2L, MCLRE = 1 and CONFIG4H, LVP = 0), or configured for Low-Voltage Programming, (MCLRE = x and LVP = 1), the pull-up is always enabled and the WPUE3 bit has no effect.

#### 15.3.3 INTERRUPT-ON-CHANGE

The interrupt-on-change feature is available only on the RE3 pin for all devices. For further details refer to **Section 14.11 "Interrupt-on-Change"**.

| R/W-1/1                               | R/W-1/1     | R/W-1/1            | R/W-1/1     | R/W-1/1      | R/W-1/1          | R/W-1/1  | R/W-1/1 |

|---------------------------------------|-------------|--------------------|-------------|--------------|------------------|----------|---------|

| INLVLx7                               | INLVLx6     | INLVLx5            | INLVLx4     | INLVLx3      | INLVLx2          | INLVLx1  | INLVLx0 |

| bit 7                                 |             |                    |             |              |                  |          | bit 0   |

|                                       |             |                    |             |              |                  |          |         |

| Legend:                               |             |                    |             |              |                  |          |         |

| R = Readable                          | bit         | W = Writable       | bit         | U = Unimplen | nented bit, read | 1 as '0' |         |

| '1' = Bit is set '0' = Bit is cleared |             | x = Bit is unknown |             |              |                  |          |         |

| -n/n = Value at                       | POR and BOI | R/Value at all o   | ther Resets |              |                  |          |         |

#### REGISTER 15-8: INLVLx: INPUT LEVEL CONTROL REGISTER

bit 7-0

- INLVLx<7:0>: Input Level Select on Pins Rx<7:0>, respectively

- 1 = ST input used for port reads and interrupt-on-change

- 0 = TTL input used for port reads and interrupt-on-change

#### TABLE 15-9: INPUT LEVEL PORT REGISTERS

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0   |

|--------|---------|---------|---------|------------------------|------------------------|------------------------|------------------------|---------|

| INLVLA | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4                | INLVLA3                | INLVLA2                | INLVLA1                | INLVLA0 |

| INLVLB | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4                | INLVLB3                | INLVLB2 <sup>(1)</sup> | INLVLB1 <sup>(1)</sup> | INLVLB0 |

| INLVLC | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 <sup>(1)</sup> | INLVLC3 <sup>(1)</sup> | INLVLC2                | INLVLC1                | INLVLC0 |

| INLVLE | —       | —       | —       | —                      | INLVLE3                | —                      | _                      | _       |

**Note 1:** Pins read the  $I^2C$  ST inputs when MSSP inputs select these pins, and  $I^2C$  mode is enabled.

#### 20.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 20-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| Rev. 10.000 1988<br>5/30/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TMRx_ers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| PRx 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| $TMRx \left( \begin{array}{c} 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 3 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2$ |  |

| TMRx_postscaled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWM Duty   3     Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

# 20.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

### 21.5.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the FMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Select the timer clock source to be as FOSC/4 using the TxCLKCON register. This is required for correct operation of the PWM module.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### 21.5.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

# 21.5.4 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 21-1.

# EQUATION 21-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

Note: The Timer postscaler (see Section 20.4 "Timer2 Interrupt") is not used in the determination of the PWM frequency.

| Name     | Bit 7       | Bit 6     | Bit 5     | Bit 4                         | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|-------------|-----------|-----------|-------------------------------|---------------|-------------|---------|---------|---------------------|

| INTCON   | GIE/GIEH    | PEIE/GIEL | IPEN      | —                             | _             | INT2EDG     | INT1EDG | INT0EDG | 166                 |

| PIE6     | _           | _         | _         | _                             | _             | _           | CCP2IE  | CCP1IE  | 181                 |

| PIR6     | _           | _         | _         | _                             | _             | _           | CCP2IF  | CCP1IF  | 173                 |

| IPR6     | _           | _         | -         | —                             | _             | _           | CCP2IP  | CCP1IP  | 189                 |

| PMD3     | _           | _         | _         | —                             | PWM4MD        | PWM3MD      | CCP2MD  | CCP1MD  | 67                  |

| CCPxCON  | EN          | _         | OUT       | FMT                           | FMT MODE<3:0> |             |         |         | 262                 |

| CCPxCAP  | _           | _         | —         | _                             | —             | —           | CTS<    | <1:0>   | 265                 |

| CCPRxL   | CCPRx<7:0>  |           |           |                               |               |             |         |         | 265                 |

| CCPRxH   | CCPRx<15:8> |           |           |                               |               |             |         | 266     |                     |

| CCPTMRS  | P4TSE       | L<1:0>    | P3TSE     | <1:0> C2TSEL<1:0> C1TSEL<1:0> |               |             |         |         | 264                 |

| CCPxPPS  |             | _         |           |                               | CCPxPPS<4:0>  |             |         |         |                     |

| RxyPPS   |             |           |           |                               |               | RxyPPS<4:0> |         |         | 213                 |

| T1CON    |             |           | T1CKP     | S<1:0>                        | _             | T1SYNC      | T1RD16  | TMR10N  | 223                 |

| T1GCON   | TMR1GE      | T1GPOL    | T1GTM     | T1GSPM                        | T1GO/DONE     | T1GVAL      |         | —       | 224                 |

| T1CLK    |             |           |           | —                             |               | CS<         | :3:0>   |         | 225                 |

| T1GATE   |             |           |           | —                             |               | GSS         | <3:0>   |         | 226                 |

| TMR1L    | TMR1L7      | TMR1L6    | TMR1L5    | TMR1L4                        | TMR1L3        | TMR1L2      | TMR1L1  | TMR1L0  | 227                 |

| TMR1H    | TMR1H7      | TMR1H6    | TMR1H5    | TMR1H4                        | TMR1H3        | TMR1H2      | TMR1H1  | TMR1H0  | 227                 |

| TMR2     |             |           |           |                               | TMR2<7:0>     |             |         |         | 238*                |

| T2PR     |             |           |           |                               | PR2<7:0>      |             |         |         | 238*                |

| T2CON    | ON          |           | CKPS<2:0> |                               |               | OUTP        | S<3:0>  |         | 256                 |

| T2HLT    | PSYNC       | CPOL      | CSYNC     |                               |               | MODE<4:0>   |         |         | 257                 |

| T2CLKCON | _           | _         | _         | _                             |               | CS<         | :3:0>   |         | 258                 |

| T2RST    | _           | _         | _         | _                             |               | RSEL        | .<3:0>  |         | 259                 |

### TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

Not a physical register.

#### 22.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note 1 below.

- Select the timer clock source to be as Fosc/4 using the TxCLKCON register. This is required for correct operation of the PWM module.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the T2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR4 register is set. See note below.

- Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the desired pin PPS control bits.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

# 22.1.10 SETUP FOR PWM OPERATION TO OTHER DEVICE PERIPHERALS

The following steps should be taken when configuring the module for PWM operation to be used by other device peripherals:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note 1 below.

- Select the timer clock source to be as Fosc/4 using the TxCLKCON register. This is required for correct operation of the PWM module.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the T2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR4 register is set. See Note 1 below.

- 7. Configure the PWM module by loading the PWMxCON register with the appropriate values.

Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

# 23.0 ZERO-CROSS DETECTION (ZCD) MODULE

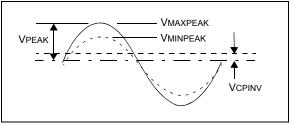

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 23-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

# 23.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 23-1 and Figure 23-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

# EQUATION 23-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 23-1: EXTERNAL VOLTAGE

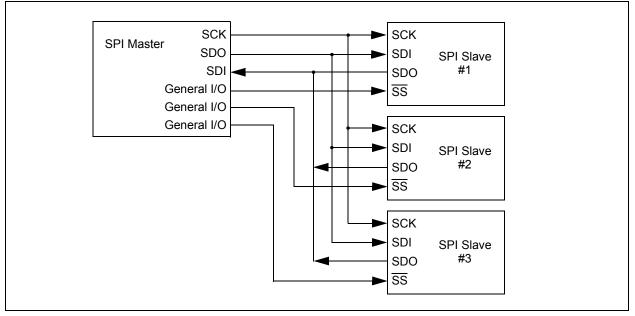

# 26.3 SPI Mode Registers

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 26.11 "Baud Rate Generator"**.

SSPSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPxBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPSR.

© 2016-2017 Microchip Technology Inc.

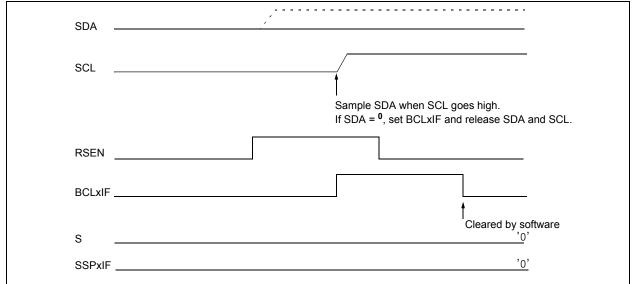

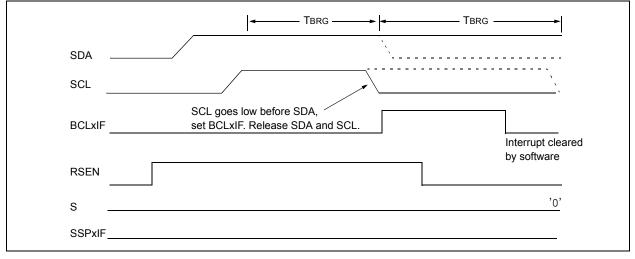

# 26.10.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 26-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 26-37.

If, at the end of the BRG time out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 26-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

# 27.2 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 27-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 27.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 27-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 27.2.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TXx/CKx I/O pin as an output. If the TXx/CKx pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 27.2.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one Tcy immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 27.2.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 27.5.1.2 "Clock Polarity**".

#### 27.2.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

#### 27.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDxCON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPxBRG begins counting up using the BRG counter clock as shown in Figure 27-6. The fifth rising edge will occur on the RXx pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPxBRGH, SPxBRGL register pair, the ABDEN bit is automatically cleared and the RCxIF interrupt flag is set. The value in the RCxREG needs to be read to clear the RCxIF interrupt. RCxREG content should be discarded. When calibrating for modes that do not use the SPxBRGH register the user can verify that the SPxBRGL register did not overflow by checking for 00h in the SPxBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 27-6. During ABD, both the SPxBRGH and SPxBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPxBRGH and SPxBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 27.4.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPxBRGH:SPxBRGL register pair.

#### TABLE 27-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 1     | 1    | Fosc/4            | Fosc/32          |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 0     | 0    | Fosc/64           | Fosc/512         |

**Note:** During the ABD sequence, SPxBRGL and SPxBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

### FIGURE 27-6: AUTOMATIC BAUD RATE CALIBRATION

| BRG Value                | XXXXh         | <u>χ 0000h</u>   | L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L L | 001Ch<br>Edge #5         |

|--------------------------|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| RXx pin                  |               | Star             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | stop bit                 |

| BRG Clock                |               | huuuuu           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ;<br>Aununnaraurannannan |

|                          | Set by User — | 1                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Auto Cleared             |

| ABDEN bit                | . (           | ]                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ,<br>,<br>,              |

| RCIDL                    |               | 1<br>1<br>1<br>1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | i<br><del>i</del>        |

| RCxIF bit<br>(Interrupt) |               | ·                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| Read<br>RCxREG           |               | 1<br>1<br>1      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

| SPxBRGL                  |               | 1<br>1<br>1      | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1Ch                      |

| SPxBRGH                  |               | •                | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00h                      |

### FIGURE 27-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| :<br>              |                       | :<br>//////////////////////////////////// | :<br>//////////////////////////////////// | :<br>//////////////////////////////////// | Cipoteste<br>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | asin sa Ganer Presi<br>111111111111111111111111111111111111 | 3 66 ŞEC 56 G<br>   | 53,7;<br>[[[[]]][[]][[[]][[]][[]][[]][[]][[]][[ |  |

|--------------------|-----------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|---------------------|-------------------------------------------------|--|

| 1.302<br>          | :                     | :<br>:<br>                                | : 4447746<br>: 5<br>:                     |                                           | <br>······<br>;<br>;                            |                                                             |                     |                                                 |  |

| - 280 (390 99)<br> |                       |                                           |                                           |                                           | 2<br>2<br>2                                     |                                                             | r tij<br>Geografier | · · · · · · · · · · · · · · · · · · ·           |  |

| 1 1255-0           | sos ery soosse i inni | N.,                                       |                                           |                                           | <br>                                            | ng gana                                                     |                     | - Auto Oleared                                  |  |

© 2016-2017 Microchip Technology Inc.

| R/W-0/0         | U-0                                                                                                                                         | R-x                                                                   | R-x          | U-0              | U-0              | R/W-0/0         | R/W-0/0 |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|------------------|------------------|-----------------|---------|--|--|--|

| EN              | -                                                                                                                                           | OUT                                                                   | RDY          | —                | —                | INTH            | INTL    |  |  |  |

| bit 7           |                                                                                                                                             |                                                                       |              |                  |                  |                 | bit C   |  |  |  |

| Legend:         |                                                                                                                                             |                                                                       |              |                  |                  |                 |         |  |  |  |

| R = Readable    | bit                                                                                                                                         | W = Writable                                                          | bit          | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |

| -n = Value at F | POR                                                                                                                                         | '1' = Bit is set                                                      |              | '0' = Bit is cle |                  | x = Bit is unki | nown    |  |  |  |

|                 |                                                                                                                                             |                                                                       |              |                  |                  |                 |         |  |  |  |

| bit 7           | EN: High/Low-voltage Detect Power Enable bit                                                                                                |                                                                       |              |                  |                  |                 |         |  |  |  |

|                 |                                                                                                                                             |                                                                       |              |                  |                  |                 |         |  |  |  |

| bit 6           | Unimplement                                                                                                                                 | ted: Read as '(                                                       | )'           |                  |                  |                 |         |  |  |  |

| bit 5           | OUT: HLVD Comparator Output bit                                                                                                             |                                                                       |              |                  |                  |                 |         |  |  |  |

|                 | 1 = Voltage $\leq$ selected detection limit (HLVDL<3:0>)                                                                                    |                                                                       |              |                  |                  |                 |         |  |  |  |

|                 | •                                                                                                                                           | $0 = \text{Voltage} \ge \text{selected detection limit (HLVDL<3:0>)}$ |              |                  |                  |                 |         |  |  |  |

| bit 4           | RDY: Band Gap Reference Voltages Stable Status Flag bit                                                                                     |                                                                       |              |                  |                  |                 |         |  |  |  |

|                 | <ul> <li>1 = Indicates HLVD Module is ready and output is stable</li> <li>0 = Indicates HLVD Module is not ready</li> </ul>                 |                                                                       |              |                  |                  |                 |         |  |  |  |

| bit 3-2         |                                                                                                                                             |                                                                       |              |                  |                  |                 |         |  |  |  |

|                 | •                                                                                                                                           | ted: Read as '(                                                       |              |                  |                  |                 |         |  |  |  |

| bit 1           |                                                                                                                                             | INTH: HLVD Positive going (High Voltage) Interrupt Enable             |              |                  |                  |                 |         |  |  |  |

|                 | <ul> <li>1 = HLVDIF will be set when voltage ≥ selected detection limit (HLVDSEL&lt;3:0&gt;)</li> <li>0 = HLVDIF will not be set</li> </ul> |                                                                       |              |                  |                  |                 |         |  |  |  |

| bit 0           | • • • • • • • • • • • • • • • • • • • •                                                                                                     |                                                                       | (Low Voltage | ) Interrupt Ena  | ble              |                 |         |  |  |  |

|                 |                                                                                                                                             | will be set whe                                                       |              | , ,              | ion limit (HLVD  | SEL<3:0>)       |         |  |  |  |

# REGISTER 33-2: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| TABLE 33-2: F | REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE |

|---------------|----------------------------------------------------------|

|---------------|----------------------------------------------------------|

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4 | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|--------|-------|----------|---------|---------|---------|---------------------|

| HLVDCON0 | EN       | -         | OUT    | RDY   | -        | -       | INTH    | INTL    | 476                 |

| HLVDCON1 | _        | -         | -      | -     | SEL<3:0> |         |         | 475     |                     |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN   | -     | -        | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIR2     | HLVDIF   | ZCDIF     | -      | -     | -        | -       | C2IF    | C1IF    | 169                 |

| PIE2     | HLVDIE   | ZCDIE     | -      | -     | -        | -       | C2IE    | C1IE    | 177                 |

| IPR2     | HLVDIP   | ZCDIP     | -      | -     | -        | -       | C2IP    | C1IP    | 185                 |

| PMD0     | SYSCMD   | FVRMD     | HLVDMD | CRCMD | SCANMD   | NVMMD   | CLKRMD  | IOCMD   | 64                  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

# PIC18(L)F24/25K40

| BRA          | <b>\</b>                                               | Unconditional Branch                                                                                                                                                                                          |                                          |             |  |  |  |  |